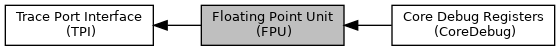

Type definitions for the Floating Point Unit (FPU) More...

Modules | |

| Core Debug Registers (CoreDebug) | |

| Type definitions for the Core Debug Registers. | |

Detailed Description

Type definitions for the Floating Point Unit (FPU)

Macro Definition Documentation

◆ FPU_FPCAR_ADDRESS_Msk [1/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1345 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCAR_ADDRESS_Msk [2/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1359 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCAR_ADDRESS_Msk [3/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1359 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCAR_ADDRESS_Msk [4/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1359 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCAR_ADDRESS_Msk [5/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1359 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCAR_ADDRESS_Msk [6/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1359 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCAR_ADDRESS_Msk [7/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1565 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCAR_ADDRESS_Msk [8/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1565 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCAR_ADDRESS_Msk [9/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1565 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCAR_ADDRESS_Msk [10/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1565 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCAR_ADDRESS_Msk [11/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1568 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCAR_ADDRESS_Msk [12/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1568 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCAR_ADDRESS_Msk [13/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1654 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCAR_ADDRESS_Msk [14/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1729 of file core_cm35p.h.

◆ FPU_FPCAR_ADDRESS_Msk [15/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1729 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCAR_ADDRESS_Msk [16/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1749 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCAR_ADDRESS_Msk [17/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1749 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCAR_ADDRESS_Msk [18/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1749 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCAR_ADDRESS_Msk [19/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1810 of file core_armv81mml.h.

◆ FPU_FPCAR_ADDRESS_Msk [20/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1824 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCAR_ADDRESS_Msk [21/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1824 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCAR_ADDRESS_Msk [22/22]

| #define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) |

FPCAR: ADDRESS bit Mask

Definition at line 1824 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCAR_ADDRESS_Pos [1/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1344 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCAR_ADDRESS_Pos [2/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1358 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCAR_ADDRESS_Pos [3/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1358 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCAR_ADDRESS_Pos [4/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1358 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCAR_ADDRESS_Pos [5/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1358 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCAR_ADDRESS_Pos [6/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1358 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCAR_ADDRESS_Pos [7/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1564 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCAR_ADDRESS_Pos [8/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1564 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCAR_ADDRESS_Pos [9/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1564 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCAR_ADDRESS_Pos [10/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1564 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCAR_ADDRESS_Pos [11/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1567 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCAR_ADDRESS_Pos [12/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1567 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCAR_ADDRESS_Pos [13/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1653 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCAR_ADDRESS_Pos [14/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1728 of file core_cm35p.h.

◆ FPU_FPCAR_ADDRESS_Pos [15/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1728 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCAR_ADDRESS_Pos [16/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1748 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCAR_ADDRESS_Pos [17/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1748 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCAR_ADDRESS_Pos [18/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1748 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCAR_ADDRESS_Pos [19/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1809 of file core_armv81mml.h.

◆ FPU_FPCAR_ADDRESS_Pos [20/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1823 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCAR_ADDRESS_Pos [21/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1823 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCAR_ADDRESS_Pos [22/22]

| #define FPU_FPCAR_ADDRESS_Pos 3U |

FPCAR: ADDRESS bit Position

Definition at line 1823 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_ASPEN_Msk [1/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1317 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_ASPEN_Msk [2/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1331 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_ASPEN_Msk [3/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1331 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_ASPEN_Msk [4/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1331 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_ASPEN_Msk [5/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1331 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_ASPEN_Msk [6/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1331 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_ASPEN_Msk [7/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1537 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_ASPEN_Msk [8/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1537 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_ASPEN_Msk [9/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1537 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_ASPEN_Msk [10/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1537 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_ASPEN_Msk [11/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1540 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_ASPEN_Msk [12/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1540 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCCR_ASPEN_Msk [13/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1602 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_ASPEN_Msk [14/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1677 of file core_cm35p.h.

◆ FPU_FPCCR_ASPEN_Msk [15/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1677 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_ASPEN_Msk [16/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1697 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_ASPEN_Msk [17/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1697 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_ASPEN_Msk [18/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1697 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_ASPEN_Msk [19/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1758 of file core_armv81mml.h.

◆ FPU_FPCCR_ASPEN_Msk [20/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1772 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_ASPEN_Msk [21/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1772 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_ASPEN_Msk [22/22]

| #define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) |

FPCCR: ASPEN bit Mask

Definition at line 1772 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_ASPEN_Pos [1/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1316 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_ASPEN_Pos [2/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1330 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_ASPEN_Pos [3/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1330 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_ASPEN_Pos [4/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1330 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_ASPEN_Pos [5/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1330 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_ASPEN_Pos [6/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1330 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_ASPEN_Pos [7/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1536 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_ASPEN_Pos [8/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1536 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_ASPEN_Pos [9/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1536 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_ASPEN_Pos [10/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1536 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_ASPEN_Pos [11/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1539 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_ASPEN_Pos [12/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1539 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCCR_ASPEN_Pos [13/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1601 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_ASPEN_Pos [14/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1676 of file core_cm35p.h.

◆ FPU_FPCCR_ASPEN_Pos [15/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1676 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_ASPEN_Pos [16/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1696 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_ASPEN_Pos [17/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1696 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_ASPEN_Pos [18/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1696 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_ASPEN_Pos [19/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1757 of file core_armv81mml.h.

◆ FPU_FPCCR_ASPEN_Pos [20/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1771 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_ASPEN_Pos [21/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1771 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_ASPEN_Pos [22/22]

| #define FPU_FPCCR_ASPEN_Pos 31U |

FPCCR: ASPEN bit Position

Definition at line 1771 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_BFRDY_Msk [1/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1326 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_BFRDY_Msk [2/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1340 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_BFRDY_Msk [3/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1340 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_BFRDY_Msk [4/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1340 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_BFRDY_Msk [5/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1340 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_BFRDY_Msk [6/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1340 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_BFRDY_Msk [7/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1546 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_BFRDY_Msk [8/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1546 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_BFRDY_Msk [9/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1546 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_BFRDY_Msk [10/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1546 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_BFRDY_Msk [11/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1549 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_BFRDY_Msk [12/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1549 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCCR_BFRDY_Msk [13/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1632 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_BFRDY_Msk [14/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1707 of file core_cm35p.h.

◆ FPU_FPCCR_BFRDY_Msk [15/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1707 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_BFRDY_Msk [16/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1727 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_BFRDY_Msk [17/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1727 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_BFRDY_Msk [18/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1727 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_BFRDY_Msk [19/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1788 of file core_armv81mml.h.

◆ FPU_FPCCR_BFRDY_Msk [20/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1802 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_BFRDY_Msk [21/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1802 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_BFRDY_Msk [22/22]

| #define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) |

FPCCR: BFRDY bit Mask

Definition at line 1802 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_BFRDY_Pos [1/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1325 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_BFRDY_Pos [2/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1339 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_BFRDY_Pos [3/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1339 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_BFRDY_Pos [4/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1339 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_BFRDY_Pos [5/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1339 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_BFRDY_Pos [6/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1339 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_BFRDY_Pos [7/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1545 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_BFRDY_Pos [8/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1545 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_BFRDY_Pos [9/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1545 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_BFRDY_Pos [10/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1545 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_BFRDY_Pos [11/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1548 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_BFRDY_Pos [12/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1548 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCCR_BFRDY_Pos [13/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1631 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_BFRDY_Pos [14/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1706 of file core_cm35p.h.

◆ FPU_FPCCR_BFRDY_Pos [15/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1706 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_BFRDY_Pos [16/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1726 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_BFRDY_Pos [17/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1726 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_BFRDY_Pos [18/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1726 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_BFRDY_Pos [19/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1787 of file core_armv81mml.h.

◆ FPU_FPCCR_BFRDY_Pos [20/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1801 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_BFRDY_Pos [21/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1801 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_BFRDY_Pos [22/22]

| #define FPU_FPCCR_BFRDY_Pos 6U |

FPCCR: BFRDY Position

Definition at line 1801 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRET_Msk [1/10]

| #define FPU_FPCCR_CLRONRET_Msk (1UL << FPU_FPCCR_CLRONRET_Pos) |

FPCCR: CLRONRET bit Mask

Definition at line 1611 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRET_Msk [2/10]

| #define FPU_FPCCR_CLRONRET_Msk (1UL << FPU_FPCCR_CLRONRET_Pos) |

FPCCR: CLRONRET bit Mask

Definition at line 1686 of file core_cm35p.h.

◆ FPU_FPCCR_CLRONRET_Msk [3/10]

| #define FPU_FPCCR_CLRONRET_Msk (1UL << FPU_FPCCR_CLRONRET_Pos) |

FPCCR: CLRONRET bit Mask

Definition at line 1686 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRET_Msk [4/10]

| #define FPU_FPCCR_CLRONRET_Msk (1UL << FPU_FPCCR_CLRONRET_Pos) |

FPCCR: CLRONRET bit Mask

Definition at line 1706 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRET_Msk [5/10]

| #define FPU_FPCCR_CLRONRET_Msk (1UL << FPU_FPCCR_CLRONRET_Pos) |

FPCCR: CLRONRET bit Mask

Definition at line 1706 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRET_Msk [6/10]

| #define FPU_FPCCR_CLRONRET_Msk (1UL << FPU_FPCCR_CLRONRET_Pos) |

FPCCR: CLRONRET bit Mask

Definition at line 1706 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRET_Msk [7/10]

| #define FPU_FPCCR_CLRONRET_Msk (1UL << FPU_FPCCR_CLRONRET_Pos) |

FPCCR: CLRONRET bit Mask

Definition at line 1767 of file core_armv81mml.h.

◆ FPU_FPCCR_CLRONRET_Msk [8/10]

| #define FPU_FPCCR_CLRONRET_Msk (1UL << FPU_FPCCR_CLRONRET_Pos) |

FPCCR: CLRONRET bit Mask

Definition at line 1781 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRET_Msk [9/10]

| #define FPU_FPCCR_CLRONRET_Msk (1UL << FPU_FPCCR_CLRONRET_Pos) |

FPCCR: CLRONRET bit Mask

Definition at line 1781 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRET_Msk [10/10]

| #define FPU_FPCCR_CLRONRET_Msk (1UL << FPU_FPCCR_CLRONRET_Pos) |

FPCCR: CLRONRET bit Mask

Definition at line 1781 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRET_Pos [1/10]

| #define FPU_FPCCR_CLRONRET_Pos 28U |

FPCCR: CLRONRET Position

Definition at line 1610 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRET_Pos [2/10]

| #define FPU_FPCCR_CLRONRET_Pos 28U |

FPCCR: CLRONRET Position

Definition at line 1685 of file core_cm35p.h.

◆ FPU_FPCCR_CLRONRET_Pos [3/10]

| #define FPU_FPCCR_CLRONRET_Pos 28U |

FPCCR: CLRONRET Position

Definition at line 1685 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRET_Pos [4/10]

| #define FPU_FPCCR_CLRONRET_Pos 28U |

FPCCR: CLRONRET Position

Definition at line 1705 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRET_Pos [5/10]

| #define FPU_FPCCR_CLRONRET_Pos 28U |

FPCCR: CLRONRET Position

Definition at line 1705 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRET_Pos [6/10]

| #define FPU_FPCCR_CLRONRET_Pos 28U |

FPCCR: CLRONRET Position

Definition at line 1705 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRET_Pos [7/10]

| #define FPU_FPCCR_CLRONRET_Pos 28U |

FPCCR: CLRONRET Position

Definition at line 1766 of file core_armv81mml.h.

◆ FPU_FPCCR_CLRONRET_Pos [8/10]

| #define FPU_FPCCR_CLRONRET_Pos 28U |

FPCCR: CLRONRET Position

Definition at line 1780 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRET_Pos [9/10]

| #define FPU_FPCCR_CLRONRET_Pos 28U |

FPCCR: CLRONRET Position

Definition at line 1780 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRET_Pos [10/10]

| #define FPU_FPCCR_CLRONRET_Pos 28U |

FPCCR: CLRONRET Position

Definition at line 1780 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRETS_Msk [1/10]

| #define FPU_FPCCR_CLRONRETS_Msk (1UL << FPU_FPCCR_CLRONRETS_Pos) |

FPCCR: CLRONRETS bit Mask

Definition at line 1614 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRETS_Msk [2/10]

| #define FPU_FPCCR_CLRONRETS_Msk (1UL << FPU_FPCCR_CLRONRETS_Pos) |

FPCCR: CLRONRETS bit Mask

Definition at line 1689 of file core_cm35p.h.

◆ FPU_FPCCR_CLRONRETS_Msk [3/10]

| #define FPU_FPCCR_CLRONRETS_Msk (1UL << FPU_FPCCR_CLRONRETS_Pos) |

FPCCR: CLRONRETS bit Mask

Definition at line 1689 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRETS_Msk [4/10]

| #define FPU_FPCCR_CLRONRETS_Msk (1UL << FPU_FPCCR_CLRONRETS_Pos) |

FPCCR: CLRONRETS bit Mask

Definition at line 1709 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRETS_Msk [5/10]

| #define FPU_FPCCR_CLRONRETS_Msk (1UL << FPU_FPCCR_CLRONRETS_Pos) |

FPCCR: CLRONRETS bit Mask

Definition at line 1709 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRETS_Msk [6/10]

| #define FPU_FPCCR_CLRONRETS_Msk (1UL << FPU_FPCCR_CLRONRETS_Pos) |

FPCCR: CLRONRETS bit Mask

Definition at line 1709 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRETS_Msk [7/10]

| #define FPU_FPCCR_CLRONRETS_Msk (1UL << FPU_FPCCR_CLRONRETS_Pos) |

FPCCR: CLRONRETS bit Mask

Definition at line 1770 of file core_armv81mml.h.

◆ FPU_FPCCR_CLRONRETS_Msk [8/10]

| #define FPU_FPCCR_CLRONRETS_Msk (1UL << FPU_FPCCR_CLRONRETS_Pos) |

FPCCR: CLRONRETS bit Mask

Definition at line 1784 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRETS_Msk [9/10]

| #define FPU_FPCCR_CLRONRETS_Msk (1UL << FPU_FPCCR_CLRONRETS_Pos) |

FPCCR: CLRONRETS bit Mask

Definition at line 1784 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRETS_Msk [10/10]

| #define FPU_FPCCR_CLRONRETS_Msk (1UL << FPU_FPCCR_CLRONRETS_Pos) |

FPCCR: CLRONRETS bit Mask

Definition at line 1784 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRETS_Pos [1/10]

| #define FPU_FPCCR_CLRONRETS_Pos 27U |

FPCCR: CLRONRETS Position

Definition at line 1613 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRETS_Pos [2/10]

| #define FPU_FPCCR_CLRONRETS_Pos 27U |

FPCCR: CLRONRETS Position

Definition at line 1688 of file core_cm35p.h.

◆ FPU_FPCCR_CLRONRETS_Pos [3/10]

| #define FPU_FPCCR_CLRONRETS_Pos 27U |

FPCCR: CLRONRETS Position

Definition at line 1688 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRETS_Pos [4/10]

| #define FPU_FPCCR_CLRONRETS_Pos 27U |

FPCCR: CLRONRETS Position

Definition at line 1708 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRETS_Pos [5/10]

| #define FPU_FPCCR_CLRONRETS_Pos 27U |

FPCCR: CLRONRETS Position

Definition at line 1708 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRETS_Pos [6/10]

| #define FPU_FPCCR_CLRONRETS_Pos 27U |

FPCCR: CLRONRETS Position

Definition at line 1708 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_CLRONRETS_Pos [7/10]

| #define FPU_FPCCR_CLRONRETS_Pos 27U |

FPCCR: CLRONRETS Position

Definition at line 1769 of file core_armv81mml.h.

◆ FPU_FPCCR_CLRONRETS_Pos [8/10]

| #define FPU_FPCCR_CLRONRETS_Pos 27U |

FPCCR: CLRONRETS Position

Definition at line 1783 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRETS_Pos [9/10]

| #define FPU_FPCCR_CLRONRETS_Pos 27U |

FPCCR: CLRONRETS Position

Definition at line 1783 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_CLRONRETS_Pos [10/10]

| #define FPU_FPCCR_CLRONRETS_Pos 27U |

FPCCR: CLRONRETS Position

Definition at line 1783 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_HFRDY_Msk [1/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1332 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_HFRDY_Msk [2/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1346 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_HFRDY_Msk [3/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1346 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_HFRDY_Msk [4/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1346 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_HFRDY_Msk [5/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1346 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_HFRDY_Msk [6/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1346 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_HFRDY_Msk [7/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1552 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_HFRDY_Msk [8/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1552 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_HFRDY_Msk [9/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1552 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_HFRDY_Msk [10/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1552 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_HFRDY_Msk [11/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1555 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_HFRDY_Msk [12/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1555 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCCR_HFRDY_Msk [13/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1638 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_HFRDY_Msk [14/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1713 of file core_cm35p.h.

◆ FPU_FPCCR_HFRDY_Msk [15/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1713 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_HFRDY_Msk [16/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1733 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_HFRDY_Msk [17/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1733 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_HFRDY_Msk [18/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1733 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_HFRDY_Msk [19/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1794 of file core_armv81mml.h.

◆ FPU_FPCCR_HFRDY_Msk [20/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1808 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_HFRDY_Msk [21/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1808 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_HFRDY_Msk [22/22]

| #define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) |

FPCCR: HFRDY bit Mask

Definition at line 1808 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_HFRDY_Pos [1/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1331 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_HFRDY_Pos [2/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1345 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_HFRDY_Pos [3/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1345 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_HFRDY_Pos [4/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1345 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_HFRDY_Pos [5/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1345 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_HFRDY_Pos [6/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1345 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_HFRDY_Pos [7/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1551 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_HFRDY_Pos [8/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1551 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_HFRDY_Pos [9/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1551 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_HFRDY_Pos [10/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1551 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_HFRDY_Pos [11/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1554 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_HFRDY_Pos [12/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1554 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCCR_HFRDY_Pos [13/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1637 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_HFRDY_Pos [14/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1712 of file core_cm35p.h.

◆ FPU_FPCCR_HFRDY_Pos [15/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1712 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_HFRDY_Pos [16/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1732 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_HFRDY_Pos [17/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1732 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_HFRDY_Pos [18/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1732 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_HFRDY_Pos [19/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1793 of file core_armv81mml.h.

◆ FPU_FPCCR_HFRDY_Pos [20/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1807 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_HFRDY_Pos [21/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1807 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_HFRDY_Pos [22/22]

| #define FPU_FPCCR_HFRDY_Pos 4U |

FPCCR: HFRDY Position

Definition at line 1807 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPACT_Msk [1/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1341 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPACT_Msk [2/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1355 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPACT_Msk [3/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1355 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPACT_Msk [4/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1355 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPACT_Msk [5/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1355 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPACT_Msk [6/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1355 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPACT_Msk [7/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1561 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPACT_Msk [8/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1561 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPACT_Msk [9/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1561 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPACT_Msk [10/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1561 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPACT_Msk [11/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1564 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPACT_Msk [12/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1564 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCCR_LSPACT_Msk [13/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1650 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPACT_Msk [14/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1725 of file core_cm35p.h.

◆ FPU_FPCCR_LSPACT_Msk [15/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1725 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPACT_Msk [16/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1745 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPACT_Msk [17/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1745 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPACT_Msk [18/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1745 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPACT_Msk [19/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1806 of file core_armv81mml.h.

◆ FPU_FPCCR_LSPACT_Msk [20/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1820 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPACT_Msk [21/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1820 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPACT_Msk [22/22]

| #define FPU_FPCCR_LSPACT_Msk (1UL /*<< FPU_FPCCR_LSPACT_Pos*/) |

FPCCR: Lazy state preservation active bit Mask

Definition at line 1820 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPACT_Pos [1/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1340 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPACT_Pos [2/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1354 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPACT_Pos [3/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1354 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPACT_Pos [4/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1354 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPACT_Pos [5/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1354 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPACT_Pos [6/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1354 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPACT_Pos [7/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1560 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPACT_Pos [8/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1560 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPACT_Pos [9/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1560 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPACT_Pos [10/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1560 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPACT_Pos [11/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1563 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCCR_LSPACT_Pos [12/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1563 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPACT_Pos [13/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1649 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPACT_Pos [14/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1724 of file core_cm35p.h.

◆ FPU_FPCCR_LSPACT_Pos [15/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1724 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPACT_Pos [16/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1744 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPACT_Pos [17/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1744 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPACT_Pos [18/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1744 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPACT_Pos [19/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1805 of file core_armv81mml.h.

◆ FPU_FPCCR_LSPACT_Pos [20/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1819 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPACT_Pos [21/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1819 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPACT_Pos [22/22]

| #define FPU_FPCCR_LSPACT_Pos 0U |

FPCCR: Lazy state preservation active bit Position

Definition at line 1819 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPEN_Msk [1/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1320 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPEN_Msk [2/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1334 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPEN_Msk [3/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1334 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPEN_Msk [4/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1334 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPEN_Msk [5/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1334 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPEN_Msk [6/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1334 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPEN_Msk [7/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1540 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPEN_Msk [8/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1540 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPEN_Msk [9/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1540 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPEN_Msk [10/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1540 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPEN_Msk [11/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1543 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCCR_LSPEN_Msk [12/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1543 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPEN_Msk [13/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1605 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPEN_Msk [14/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1680 of file core_cm35p.h.

◆ FPU_FPCCR_LSPEN_Msk [15/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1680 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPEN_Msk [16/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1700 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPEN_Msk [17/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1700 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPEN_Msk [18/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1700 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPEN_Msk [19/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1761 of file core_armv81mml.h.

◆ FPU_FPCCR_LSPEN_Msk [20/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1775 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPEN_Msk [21/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1775 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPEN_Msk [22/22]

| #define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) |

FPCCR: LSPEN bit Mask

Definition at line 1775 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPEN_Pos [1/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1319 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPEN_Pos [2/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1333 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPEN_Pos [3/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1333 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPEN_Pos [4/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1333 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPEN_Pos [5/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1333 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPEN_Pos [6/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1333 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_LSPEN_Pos [7/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1539 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPEN_Pos [8/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1539 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPEN_Pos [9/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1539 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPEN_Pos [10/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1539 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPEN_Pos [11/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1542 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_LSPEN_Pos [12/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1542 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCCR_LSPEN_Pos [13/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1604 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPEN_Pos [14/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1679 of file core_cm35p.h.

◆ FPU_FPCCR_LSPEN_Pos [15/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1679 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPEN_Pos [16/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1699 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPEN_Pos [17/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1699 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPEN_Pos [18/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1699 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPEN_Pos [19/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1760 of file core_armv81mml.h.

◆ FPU_FPCCR_LSPEN_Pos [20/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1774 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPEN_Pos [21/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1774 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPEN_Pos [22/22]

| #define FPU_FPCCR_LSPEN_Pos 30U |

FPCCR: LSPEN Position

Definition at line 1774 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPENS_Msk [1/10]

| #define FPU_FPCCR_LSPENS_Msk (1UL << FPU_FPCCR_LSPENS_Pos) |

FPCCR: LSPENS bit Mask

Definition at line 1608 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPENS_Msk [2/10]

| #define FPU_FPCCR_LSPENS_Msk (1UL << FPU_FPCCR_LSPENS_Pos) |

FPCCR: LSPENS bit Mask

Definition at line 1683 of file core_cm35p.h.

◆ FPU_FPCCR_LSPENS_Msk [3/10]

| #define FPU_FPCCR_LSPENS_Msk (1UL << FPU_FPCCR_LSPENS_Pos) |

FPCCR: LSPENS bit Mask

Definition at line 1683 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPENS_Msk [4/10]

| #define FPU_FPCCR_LSPENS_Msk (1UL << FPU_FPCCR_LSPENS_Pos) |

FPCCR: LSPENS bit Mask

Definition at line 1703 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPENS_Msk [5/10]

| #define FPU_FPCCR_LSPENS_Msk (1UL << FPU_FPCCR_LSPENS_Pos) |

FPCCR: LSPENS bit Mask

Definition at line 1703 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPENS_Msk [6/10]

| #define FPU_FPCCR_LSPENS_Msk (1UL << FPU_FPCCR_LSPENS_Pos) |

FPCCR: LSPENS bit Mask

Definition at line 1703 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPENS_Msk [7/10]

| #define FPU_FPCCR_LSPENS_Msk (1UL << FPU_FPCCR_LSPENS_Pos) |

FPCCR: LSPENS bit Mask

Definition at line 1764 of file core_armv81mml.h.

◆ FPU_FPCCR_LSPENS_Msk [8/10]

| #define FPU_FPCCR_LSPENS_Msk (1UL << FPU_FPCCR_LSPENS_Pos) |

FPCCR: LSPENS bit Mask

Definition at line 1778 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPENS_Msk [9/10]

| #define FPU_FPCCR_LSPENS_Msk (1UL << FPU_FPCCR_LSPENS_Pos) |

FPCCR: LSPENS bit Mask

Definition at line 1778 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPENS_Msk [10/10]

| #define FPU_FPCCR_LSPENS_Msk (1UL << FPU_FPCCR_LSPENS_Pos) |

FPCCR: LSPENS bit Mask

Definition at line 1778 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPENS_Pos [1/10]

| #define FPU_FPCCR_LSPENS_Pos 29U |

FPCCR: LSPENS Position

Definition at line 1607 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPENS_Pos [2/10]

| #define FPU_FPCCR_LSPENS_Pos 29U |

FPCCR: LSPENS Position

Definition at line 1682 of file core_cm35p.h.

◆ FPU_FPCCR_LSPENS_Pos [3/10]

| #define FPU_FPCCR_LSPENS_Pos 29U |

FPCCR: LSPENS Position

Definition at line 1682 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPENS_Pos [4/10]

| #define FPU_FPCCR_LSPENS_Pos 29U |

FPCCR: LSPENS Position

Definition at line 1702 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPENS_Pos [5/10]

| #define FPU_FPCCR_LSPENS_Pos 29U |

FPCCR: LSPENS Position

Definition at line 1702 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPENS_Pos [6/10]

| #define FPU_FPCCR_LSPENS_Pos 29U |

FPCCR: LSPENS Position

Definition at line 1702 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_LSPENS_Pos [7/10]

| #define FPU_FPCCR_LSPENS_Pos 29U |

FPCCR: LSPENS Position

Definition at line 1763 of file core_armv81mml.h.

◆ FPU_FPCCR_LSPENS_Pos [8/10]

| #define FPU_FPCCR_LSPENS_Pos 29U |

FPCCR: LSPENS Position

Definition at line 1777 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPENS_Pos [9/10]

| #define FPU_FPCCR_LSPENS_Pos 29U |

FPCCR: LSPENS Position

Definition at line 1777 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_LSPENS_Pos [10/10]

| #define FPU_FPCCR_LSPENS_Pos 29U |

FPCCR: LSPENS Position

Definition at line 1777 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_MMRDY_Msk [1/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1329 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_MMRDY_Msk [2/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1343 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_MMRDY_Msk [3/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1343 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_MMRDY_Msk [4/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1343 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_MMRDY_Msk [5/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1343 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_MMRDY_Msk [6/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1343 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_MMRDY_Msk [7/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1549 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_MMRDY_Msk [8/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1549 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_MMRDY_Msk [9/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1549 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_MMRDY_Msk [10/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1549 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_MMRDY_Msk [11/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1552 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_MMRDY_Msk [12/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1552 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCCR_MMRDY_Msk [13/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1635 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_MMRDY_Msk [14/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1710 of file core_cm35p.h.

◆ FPU_FPCCR_MMRDY_Msk [15/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1710 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_MMRDY_Msk [16/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1730 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_MMRDY_Msk [17/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1730 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_MMRDY_Msk [18/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1730 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_MMRDY_Msk [19/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1791 of file core_armv81mml.h.

◆ FPU_FPCCR_MMRDY_Msk [20/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1805 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_MMRDY_Msk [21/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1805 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_MMRDY_Msk [22/22]

| #define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) |

FPCCR: MMRDY bit Mask

Definition at line 1805 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_MMRDY_Pos [1/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1328 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_MMRDY_Pos [2/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1342 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_MMRDY_Pos [3/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1342 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_MMRDY_Pos [4/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1342 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_MMRDY_Pos [5/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1342 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_MMRDY_Pos [6/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1342 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_FPCCR_MMRDY_Pos [7/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1548 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_MMRDY_Pos [8/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1548 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_MMRDY_Pos [9/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1548 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_MMRDY_Pos [10/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1548 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_MMRDY_Pos [11/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1551 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_FPCCR_MMRDY_Pos [12/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1551 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_FPCCR_MMRDY_Pos [13/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1634 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_FPCCR_MMRDY_Pos [14/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1709 of file core_cm35p.h.

◆ FPU_FPCCR_MMRDY_Pos [15/22]

| #define FPU_FPCCR_MMRDY_Pos 5U |

FPCCR: MMRDY Position

Definition at line 1709 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_FPCCR_MMRDY_Pos [16/22]