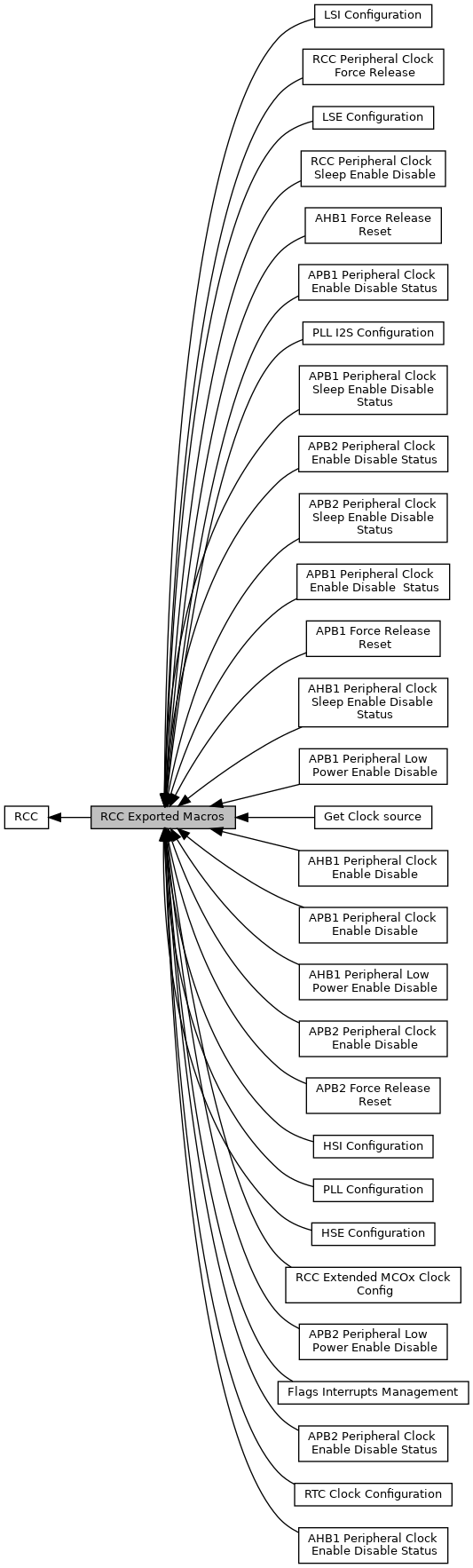

Modules | |

| AHB1 Peripheral Clock Enable Disable | |

| Enable or disable the AHB1 peripheral clock. | |

| AHB1 Peripheral Clock Enable Disable Status | |

| Get the enable or disable status of the AHB1 peripheral clock. | |

| APB1 Peripheral Clock Enable Disable | |

| Enable or disable the Low Speed APB (APB1) peripheral clock. | |

| APB1 Peripheral Clock Enable Disable Status | |

| Get the enable or disable status of the APB1 peripheral clock. | |

| APB2 Peripheral Clock Enable Disable | |

| Enable or disable the High Speed APB (APB2) peripheral clock. | |

| APB2 Peripheral Clock Enable Disable Status | |

| Get the enable or disable status of the APB2 peripheral clock. | |

| AHB1 Force Release Reset | |

| Force or release AHB1 peripheral reset. | |

| APB1 Force Release Reset | |

| Force or release APB1 peripheral reset. | |

| APB2 Force Release Reset | |

| Force or release APB2 peripheral reset. | |

| AHB1 Peripheral Low Power Enable Disable | |

| Enable or disable the AHB1 peripheral clock during Low Power (Sleep) mode. | |

| APB1 Peripheral Low Power Enable Disable | |

| Enable or disable the APB1 peripheral clock during Low Power (Sleep) mode. | |

| APB2 Peripheral Low Power Enable Disable | |

| Enable or disable the APB2 peripheral clock during Low Power (Sleep) mode. | |

| HSI Configuration | |

| LSI Configuration | |

| HSE Configuration | |

| LSE Configuration | |

| RTC Clock Configuration | |

| PLL Configuration | |

| Get Clock source | |

| RCC Extended MCOx Clock Config | |

| Flags Interrupts Management | |

| macros to manage the specified RCC Flags and interrupts. | |

| APB1 Peripheral Clock Enable Disable Status | |

| Get the enable or disable status of the APB1 peripheral clock. | |

| APB2 Peripheral Clock Enable Disable Status | |

| EGet the enable or disable status of the APB2 peripheral clock. | |

| RCC Peripheral Clock Force Release | |

| Force or release AHB peripheral reset. | |

| RCC Peripheral Clock Sleep Enable Disable | |

| AHB1 Peripheral Clock Sleep Enable Disable Status | |

| Get the enable or disable status of the AHB1 peripheral clock during Low Power (Sleep) mode. | |

| APB1 Peripheral Clock Sleep Enable Disable Status | |

| Get the enable or disable status of the APB1 peripheral clock during Low Power (Sleep) mode. | |

| APB2 Peripheral Clock Sleep Enable Disable Status | |

| Get the enable or disable status of the APB2 peripheral clock during Low Power (Sleep) mode. | |

| PLL I2S Configuration | |

Detailed Description

Macro Definition Documentation

◆ __HAL_RCC_ADC12_CLK_DISABLE [1/2]

| #define __HAL_RCC_ADC12_CLK_DISABLE | ( | ) | (RCC->AHB1ENR &= ~ (RCC_AHB1ENR_ADC12EN)) |

Definition at line 1078 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_CLK_DISABLE [2/2]

| #define __HAL_RCC_ADC12_CLK_DISABLE | ( | ) | (RCC->AHB1ENR &= ~ (RCC_AHB1ENR_ADC12EN)) |

Definition at line 1078 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_CLK_ENABLE [1/2]

| #define __HAL_RCC_ADC12_CLK_ENABLE | ( | ) |

Definition at line 988 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_CLK_ENABLE [2/2]

| #define __HAL_RCC_ADC12_CLK_ENABLE | ( | ) |

Definition at line 988 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_ADC12_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB1LPENR &= ~ (RCC_AHB1LPENR_ADC12LPEN)) |

Definition at line 5382 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_ADC12_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB1LPENR &= ~ (RCC_AHB1LPENR_ADC12LPEN)) |

Definition at line 5382 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_ADC12_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB1LPENR |= (RCC_AHB1LPENR_ADC12LPEN)) |

Definition at line 5359 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_ADC12_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB1LPENR |= (RCC_AHB1LPENR_ADC12LPEN)) |

Definition at line 5359 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_FORCE_RESET [1/2]

| #define __HAL_RCC_ADC12_FORCE_RESET | ( | ) | (RCC->AHB1RSTR |= (RCC_AHB1RSTR_ADC12RST)) |

Definition at line 4743 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_FORCE_RESET [2/2]

| #define __HAL_RCC_ADC12_FORCE_RESET | ( | ) | (RCC->AHB1RSTR |= (RCC_AHB1RSTR_ADC12RST)) |

Definition at line 4743 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_IS_CLK_DISABLED [1/2]

| #define __HAL_RCC_ADC12_IS_CLK_DISABLED | ( | ) | ((RCC->AHB1ENR & RCC_AHB1ENR_ADC12EN) == 0U) |

Definition at line 1126 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_IS_CLK_DISABLED [2/2]

| #define __HAL_RCC_ADC12_IS_CLK_DISABLED | ( | ) | ((RCC->AHB1ENR & RCC_AHB1ENR_ADC12EN) == 0U) |

Definition at line 1126 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_IS_CLK_ENABLED [1/2]

| #define __HAL_RCC_ADC12_IS_CLK_ENABLED | ( | ) | ((RCC->AHB1ENR & RCC_AHB1ENR_ADC12EN) != 0U) |

Definition at line 1105 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_IS_CLK_ENABLED [2/2]

| #define __HAL_RCC_ADC12_IS_CLK_ENABLED | ( | ) | ((RCC->AHB1ENR & RCC_AHB1ENR_ADC12EN) != 0U) |

Definition at line 1105 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_IS_CLK_SLEEP_DISABLED [1/2]

| #define __HAL_RCC_ADC12_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB1LPENR & (RCC_AHB1LPENR_ADC12LPEN)) == 0U) |

Definition at line 5435 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_IS_CLK_SLEEP_DISABLED [2/2]

| #define __HAL_RCC_ADC12_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB1LPENR & (RCC_AHB1LPENR_ADC12LPEN)) == 0U) |

Definition at line 5435 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_IS_CLK_SLEEP_ENABLED [1/2]

| #define __HAL_RCC_ADC12_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB1LPENR & (RCC_AHB1LPENR_ADC12LPEN)) != 0U) |

Definition at line 5412 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_IS_CLK_SLEEP_ENABLED [2/2]

| #define __HAL_RCC_ADC12_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB1LPENR & (RCC_AHB1LPENR_ADC12LPEN)) != 0U) |

Definition at line 5412 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_RELEASE_RESET [1/2]

| #define __HAL_RCC_ADC12_RELEASE_RESET | ( | ) | (RCC->AHB1RSTR &= ~ (RCC_AHB1RSTR_ADC12RST)) |

Definition at line 4761 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_ADC12_RELEASE_RESET [2/2]

| #define __HAL_RCC_ADC12_RELEASE_RESET | ( | ) | (RCC->AHB1RSTR &= ~ (RCC_AHB1RSTR_ADC12RST)) |

Definition at line 4761 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB1_FORCE_RESET [1/2]

| #define __HAL_RCC_AHB1_FORCE_RESET | ( | ) | (RCC->AHB1RSTR = 0x02008023U) /* Resets DMA1, DMA2, ADC12, ETHMAC and USB1OTG */ |

Force or release the AHB1 peripheral reset.

Definition at line 4739 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB1_FORCE_RESET [2/2]

| #define __HAL_RCC_AHB1_FORCE_RESET | ( | ) | (RCC->AHB1RSTR = 0x02008023U) /* Resets DMA1, DMA2, ADC12, ETHMAC and USB1OTG */ |

Force or release the AHB1 peripheral reset.

Definition at line 4739 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB1_RELEASE_RESET [1/2]

| #define __HAL_RCC_AHB1_RELEASE_RESET | ( | ) | (RCC->AHB1RSTR = 0x00U) |

Definition at line 4758 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB1_RELEASE_RESET [2/2]

| #define __HAL_RCC_AHB1_RELEASE_RESET | ( | ) | (RCC->AHB1RSTR = 0x00U) |

Definition at line 4758 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB2_FORCE_RESET [1/2]

| #define __HAL_RCC_AHB2_FORCE_RESET | ( | ) | (RCC->AHB2RSTR = 0x00030271U) /* Resets DCMI_PSSI, CRYPT, HASH, RNG, SDMMC2, FMAC and CORDIC */ |

Force or release the AHB2 peripheral reset.

Definition at line 4783 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB2_FORCE_RESET [2/2]

| #define __HAL_RCC_AHB2_FORCE_RESET | ( | ) | (RCC->AHB2RSTR = 0x00030271U) /* Resets DCMI_PSSI, CRYPT, HASH, RNG, SDMMC2, FMAC and CORDIC */ |

Force or release the AHB2 peripheral reset.

Definition at line 4783 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB2_RELEASE_RESET [1/2]

| #define __HAL_RCC_AHB2_RELEASE_RESET | ( | ) | (RCC->AHB2RSTR = 0x00U) |

Definition at line 4812 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB2_RELEASE_RESET [2/2]

| #define __HAL_RCC_AHB2_RELEASE_RESET | ( | ) | (RCC->AHB2RSTR = 0x00U) |

Definition at line 4812 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB3_FORCE_RESET [1/2]

| #define __HAL_RCC_AHB3_FORCE_RESET | ( | ) | (RCC->AHB3RSTR = 0x00E95011U) /* Resets MDMA, DMA2D, FMC, OSPI1, SDMMC1, OSPI2, IOMNGR, OTFD1, OTFD2 */ |

Enable or disable the AHB3 peripheral reset.

Definition at line 4669 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB3_FORCE_RESET [2/2]

| #define __HAL_RCC_AHB3_FORCE_RESET | ( | ) | (RCC->AHB3RSTR = 0x00E95011U) /* Resets MDMA, DMA2D, FMC, OSPI1, SDMMC1, OSPI2, IOMNGR, OTFD1, OTFD2 */ |

Enable or disable the AHB3 peripheral reset.

Definition at line 4669 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB3_RELEASE_RESET [1/2]

| #define __HAL_RCC_AHB3_RELEASE_RESET | ( | ) | (RCC->AHB3RSTR = 0x00) |

Definition at line 4700 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB3_RELEASE_RESET [2/2]

| #define __HAL_RCC_AHB3_RELEASE_RESET | ( | ) | (RCC->AHB3RSTR = 0x00) |

Definition at line 4700 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB4_FORCE_RESET [1/2]

| #define __HAL_RCC_AHB4_FORCE_RESET | ( | ) | (RCC->AHB4RSTR = 0x032806FFU) /* Resets GPIOA..GPIOH, GPIOJ, GPIOK, CRC, BDMA, ADC3 and HSEM */ |

Force or release the AHB4 peripheral reset.

Definition at line 4849 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB4_FORCE_RESET [2/2]

| #define __HAL_RCC_AHB4_FORCE_RESET | ( | ) | (RCC->AHB4RSTR = 0x032806FFU) /* Resets GPIOA..GPIOH, GPIOJ, GPIOK, CRC, BDMA, ADC3 and HSEM */ |

Force or release the AHB4 peripheral reset.

Definition at line 4849 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB4_RELEASE_RESET [1/2]

| #define __HAL_RCC_AHB4_RELEASE_RESET | ( | ) | (RCC->AHB4RSTR = 0x00U) |

Definition at line 4880 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHB4_RELEASE_RESET [2/2]

| #define __HAL_RCC_AHB4_RELEASE_RESET | ( | ) | (RCC->AHB4RSTR = 0x00U) |

Definition at line 4880 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_CLK_DISABLE [1/2]

| #define __HAL_RCC_AHBSRAM1_CLK_DISABLE | ( | ) | (RCC->AHB2ENR &= ~ (RCC_AHB2ENR_AHBSRAM1EN)) |

Definition at line 1316 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_CLK_DISABLE [2/2]

| #define __HAL_RCC_AHBSRAM1_CLK_DISABLE | ( | ) | (RCC->AHB2ENR &= ~ (RCC_AHB2ENR_AHBSRAM1EN)) |

Definition at line 1316 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_CLK_ENABLE [1/2]

| #define __HAL_RCC_AHBSRAM1_CLK_ENABLE | ( | ) |

Definition at line 1236 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_CLK_ENABLE [2/2]

| #define __HAL_RCC_AHBSRAM1_CLK_ENABLE | ( | ) |

Definition at line 1236 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_AHBSRAM1_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB2LPENR &= ~ (RCC_AHB2LPENR_AHBSRAM1LPEN)) |

Definition at line 5527 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_AHBSRAM1_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB2LPENR &= ~ (RCC_AHB2LPENR_AHBSRAM1LPEN)) |

Definition at line 5527 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_AHBSRAM1_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB2LPENR |= (RCC_AHB2LPENR_AHBSRAM1LPEN)) |

Definition at line 5490 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_AHBSRAM1_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB2LPENR |= (RCC_AHB2LPENR_AHBSRAM1LPEN)) |

Definition at line 5490 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_IS_CLK_DISABLED [1/2]

| #define __HAL_RCC_AHBSRAM1_IS_CLK_DISABLED | ( | ) | ((RCC->AHB2ENR & RCC_AHB2ENR_AHBSRAM1EN) == 0U) |

Definition at line 1402 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_IS_CLK_DISABLED [2/2]

| #define __HAL_RCC_AHBSRAM1_IS_CLK_DISABLED | ( | ) | ((RCC->AHB2ENR & RCC_AHB2ENR_AHBSRAM1EN) == 0U) |

Definition at line 1402 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_IS_CLK_ENABLED [1/2]

| #define __HAL_RCC_AHBSRAM1_IS_CLK_ENABLED | ( | ) | ((RCC->AHB2ENR & RCC_AHB2ENR_AHBSRAM1EN) != 0U) |

Definition at line 1362 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_IS_CLK_ENABLED [2/2]

| #define __HAL_RCC_AHBSRAM1_IS_CLK_ENABLED | ( | ) | ((RCC->AHB2ENR & RCC_AHB2ENR_AHBSRAM1EN) != 0U) |

Definition at line 1362 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_IS_CLK_SLEEP_DISABLED [1/2]

| #define __HAL_RCC_AHBSRAM1_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB2LPENR & (RCC_AHB2LPENR_AHBSRAM1LPEN)) == 0U) |

Definition at line 5608 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_IS_CLK_SLEEP_DISABLED [2/2]

| #define __HAL_RCC_AHBSRAM1_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB2LPENR & (RCC_AHB2LPENR_AHBSRAM1LPEN)) == 0U) |

Definition at line 5608 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_IS_CLK_SLEEP_ENABLED [1/2]

| #define __HAL_RCC_AHBSRAM1_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB2LPENR & (RCC_AHB2LPENR_AHBSRAM1LPEN)) != 0U) |

Definition at line 5571 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM1_IS_CLK_SLEEP_ENABLED [2/2]

| #define __HAL_RCC_AHBSRAM1_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB2LPENR & (RCC_AHB2LPENR_AHBSRAM1LPEN)) != 0U) |

Definition at line 5571 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_CLK_DISABLE [1/2]

| #define __HAL_RCC_AHBSRAM2_CLK_DISABLE | ( | ) | (RCC->AHB2ENR &= ~ (RCC_AHB2ENR_AHBSRAM2EN)) |

Definition at line 1321 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_CLK_DISABLE [2/2]

| #define __HAL_RCC_AHBSRAM2_CLK_DISABLE | ( | ) | (RCC->AHB2ENR &= ~ (RCC_AHB2ENR_AHBSRAM2EN)) |

Definition at line 1321 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_CLK_ENABLE [1/2]

| #define __HAL_RCC_AHBSRAM2_CLK_ENABLE | ( | ) |

Definition at line 1254 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_CLK_ENABLE [2/2]

| #define __HAL_RCC_AHBSRAM2_CLK_ENABLE | ( | ) |

Definition at line 1254 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_AHBSRAM2_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB2LPENR &= ~ (RCC_AHB2LPENR_AHBSRAM2LPEN)) |

Definition at line 5532 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_AHBSRAM2_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB2LPENR &= ~ (RCC_AHB2LPENR_AHBSRAM2LPEN)) |

Definition at line 5532 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_AHBSRAM2_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB2LPENR |= (RCC_AHB2LPENR_AHBSRAM2LPEN)) |

Definition at line 5495 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_AHBSRAM2_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB2LPENR |= (RCC_AHB2LPENR_AHBSRAM2LPEN)) |

Definition at line 5495 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_IS_CLK_DISABLED [1/2]

| #define __HAL_RCC_AHBSRAM2_IS_CLK_DISABLED | ( | ) | ((RCC->AHB2ENR & RCC_AHB2ENR_AHBSRAM2EN) == 0U) |

Definition at line 1407 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_IS_CLK_DISABLED [2/2]

| #define __HAL_RCC_AHBSRAM2_IS_CLK_DISABLED | ( | ) | ((RCC->AHB2ENR & RCC_AHB2ENR_AHBSRAM2EN) == 0U) |

Definition at line 1407 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_IS_CLK_ENABLED [1/2]

| #define __HAL_RCC_AHBSRAM2_IS_CLK_ENABLED | ( | ) | ((RCC->AHB2ENR & RCC_AHB2ENR_AHBSRAM2EN) != 0U) |

Definition at line 1367 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_IS_CLK_ENABLED [2/2]

| #define __HAL_RCC_AHBSRAM2_IS_CLK_ENABLED | ( | ) | ((RCC->AHB2ENR & RCC_AHB2ENR_AHBSRAM2EN) != 0U) |

Definition at line 1367 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_IS_CLK_SLEEP_DISABLED [1/2]

| #define __HAL_RCC_AHBSRAM2_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB2LPENR & (RCC_AHB2LPENR_AHBSRAM2LPEN)) == 0U) |

Definition at line 5613 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_IS_CLK_SLEEP_DISABLED [2/2]

| #define __HAL_RCC_AHBSRAM2_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB2LPENR & (RCC_AHB2LPENR_AHBSRAM2LPEN)) == 0U) |

Definition at line 5613 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_IS_CLK_SLEEP_ENABLED [1/2]

| #define __HAL_RCC_AHBSRAM2_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB2LPENR & (RCC_AHB2LPENR_AHBSRAM2LPEN)) != 0U) |

Definition at line 5576 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AHBSRAM2_IS_CLK_SLEEP_ENABLED [2/2]

| #define __HAL_RCC_AHBSRAM2_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB2LPENR & (RCC_AHB2LPENR_AHBSRAM2LPEN)) != 0U) |

Definition at line 5576 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB1H_FORCE_RESET [1/2]

| #define __HAL_RCC_APB1H_FORCE_RESET | ( | ) | (RCC->APB1HRSTR = 0x03000136U) /* Resets CRS, SWP, OPAMP, MDIOS, FDCAN, TIM23 and TIM24 */ |

Definition at line 4942 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB1H_FORCE_RESET [2/2]

| #define __HAL_RCC_APB1H_FORCE_RESET | ( | ) | (RCC->APB1HRSTR = 0x03000136U) /* Resets CRS, SWP, OPAMP, MDIOS, FDCAN, TIM23 and TIM24 */ |

Definition at line 4942 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB1H_RELEASE_RESET [1/2]

| #define __HAL_RCC_APB1H_RELEASE_RESET | ( | ) | (RCC->APB1HRSTR = 0x00U) |

Definition at line 4984 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB1H_RELEASE_RESET [2/2]

| #define __HAL_RCC_APB1H_RELEASE_RESET | ( | ) | (RCC->APB1HRSTR = 0x00U) |

Definition at line 4984 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB1L_FORCE_RESET [1/2]

| #define __HAL_RCC_APB1L_FORCE_RESET | ( | ) | (RCC->APB1LRSTR = 0xEAFFC3FFU) /* Resets TIM2..TIM7, TIM12..TIM14, LPTIM1, SPI2, SPI3, SPDIFRX, USART2, USART3, UART4, UART5, I2C1..I2C3, I2C5, CEC, DAC12, UART7 and UART8 */ |

Force or release the APB1 peripheral reset.

Definition at line 4937 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB1L_FORCE_RESET [2/2]

| #define __HAL_RCC_APB1L_FORCE_RESET | ( | ) | (RCC->APB1LRSTR = 0xEAFFC3FFU) /* Resets TIM2..TIM7, TIM12..TIM14, LPTIM1, SPI2, SPI3, SPDIFRX, USART2, USART3, UART4, UART5, I2C1..I2C3, I2C5, CEC, DAC12, UART7 and UART8 */ |

Force or release the APB1 peripheral reset.

Definition at line 4937 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB1L_RELEASE_RESET [1/2]

| #define __HAL_RCC_APB1L_RELEASE_RESET | ( | ) | (RCC->APB1LRSTR = 0x00U) |

Definition at line 4983 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB1L_RELEASE_RESET [2/2]

| #define __HAL_RCC_APB1L_RELEASE_RESET | ( | ) | (RCC->APB1LRSTR = 0x00U) |

Definition at line 4983 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB2_FORCE_RESET [1/2]

| #define __HAL_RCC_APB2_FORCE_RESET | ( | ) | (RCC->APB2RSTR = 0x405730F3U) /* Resets TIM1, TIM8, USART1, USART6, UART9, USART10, SPI1, SPI4, TIM15..TIM17, SPI5, SAI1 and DFSDM1 */ |

Force or release the APB2 peripheral reset.

Definition at line 5031 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB2_FORCE_RESET [2/2]

| #define __HAL_RCC_APB2_FORCE_RESET | ( | ) | (RCC->APB2RSTR = 0x405730F3U) /* Resets TIM1, TIM8, USART1, USART6, UART9, USART10, SPI1, SPI4, TIM15..TIM17, SPI5, SAI1 and DFSDM1 */ |

Force or release the APB2 peripheral reset.

Definition at line 5031 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB2_RELEASE_RESET [1/2]

| #define __HAL_RCC_APB2_RELEASE_RESET | ( | ) | (RCC->APB2RSTR = 0x00U) |

Definition at line 5061 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB2_RELEASE_RESET [2/2]

| #define __HAL_RCC_APB2_RELEASE_RESET | ( | ) | (RCC->APB2RSTR = 0x00U) |

Definition at line 5061 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB3_FORCE_RESET [1/2]

Force or release the APB3 peripheral reset.

Definition at line 4915 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB3_FORCE_RESET [2/2]

Force or release the APB3 peripheral reset.

Definition at line 4915 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB3_RELEASE_RESET [1/2]

| #define __HAL_RCC_APB3_RELEASE_RESET | ( | ) | (RCC->APB3RSTR = 0x00U) |

Definition at line 4924 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB3_RELEASE_RESET [2/2]

| #define __HAL_RCC_APB3_RELEASE_RESET | ( | ) | (RCC->APB3RSTR = 0x00U) |

Definition at line 4924 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB4_FORCE_RESET [1/2]

| #define __HAL_RCC_APB4_FORCE_RESET | ( | ) | (RCC->APB4RSTR = 0x0420DEAAU) /* Resets SYSCFG, LPUART1, SPI6, I2C4, LPTIM2..LPTIM5, COMP12, VREF, SAI4 and DTS */ |

Force or release the APB4 peripheral reset.

Definition at line 5098 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB4_FORCE_RESET [2/2]

| #define __HAL_RCC_APB4_FORCE_RESET | ( | ) | (RCC->APB4RSTR = 0x0420DEAAU) /* Resets SYSCFG, LPUART1, SPI6, I2C4, LPTIM2..LPTIM5, COMP12, VREF, SAI4 and DTS */ |

Force or release the APB4 peripheral reset.

Definition at line 5098 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB4_RELEASE_RESET [1/2]

| #define __HAL_RCC_APB4_RELEASE_RESET | ( | ) | (RCC->APB4RSTR = 0x00U) |

Definition at line 5127 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_APB4_RELEASE_RESET [2/2]

| #define __HAL_RCC_APB4_RELEASE_RESET | ( | ) | (RCC->APB4RSTR = 0x00U) |

Definition at line 5127 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AXISRAM1_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_AXISRAM1_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB3LPENR &= ~ (RCC_AHB3LPENR_AXISRAM1LPEN)) |

Definition at line 5251 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AXISRAM1_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_AXISRAM1_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB3LPENR &= ~ (RCC_AHB3LPENR_AXISRAM1LPEN)) |

Definition at line 5251 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AXISRAM1_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_AXISRAM1_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB3LPENR |= (RCC_AHB3LPENR_AXISRAM1LPEN)) |

Definition at line 5205 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AXISRAM1_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_AXISRAM1_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB3LPENR |= (RCC_AHB3LPENR_AXISRAM1LPEN)) |

Definition at line 5205 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AXISRAM1_IS_CLK_SLEEP_DISABLED [1/2]

| #define __HAL_RCC_AXISRAM1_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB3LPENR & RCC_AHB3LPENR_AXISRAML1PEN) == 0U) |

Definition at line 5347 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AXISRAM1_IS_CLK_SLEEP_DISABLED [2/2]

| #define __HAL_RCC_AXISRAM1_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB3LPENR & RCC_AHB3LPENR_AXISRAML1PEN) == 0U) |

Definition at line 5347 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AXISRAM1_IS_CLK_SLEEP_ENABLED [1/2]

| #define __HAL_RCC_AXISRAM1_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB3LPENR & RCC_AHB3LPENR_AXISRAM1LPEN) != 0U) |

Definition at line 5303 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_AXISRAM1_IS_CLK_SLEEP_ENABLED [2/2]

| #define __HAL_RCC_AXISRAM1_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB3LPENR & RCC_AHB3LPENR_AXISRAM1LPEN) != 0U) |

Definition at line 5303 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BACKUPRESET_FORCE [1/2]

| #define __HAL_RCC_BACKUPRESET_FORCE | ( | ) | SET_BIT(RCC->BDCR, RCC_BDCR_BDRST) |

Macros to force or release the Backup domain reset.

- Note

- This function resets the RTC peripheral (including the backup registers) and the RTC clock source selection in RCC_BDCR register.

- The BKPSRAM is not affected by this reset.

Definition at line 7504 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BACKUPRESET_FORCE [2/2]

| #define __HAL_RCC_BACKUPRESET_FORCE | ( | ) | SET_BIT(RCC->BDCR, RCC_BDCR_BDRST) |

Macros to force or release the Backup domain reset.

- Note

- This function resets the RTC peripheral (including the backup registers) and the RTC clock source selection in RCC_BDCR register.

- The BKPSRAM is not affected by this reset.

Definition at line 7507 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BACKUPRESET_RELEASE [1/2]

| #define __HAL_RCC_BACKUPRESET_RELEASE | ( | ) | CLEAR_BIT(RCC->BDCR, RCC_BDCR_BDRST) |

Definition at line 7505 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BACKUPRESET_RELEASE [2/2]

| #define __HAL_RCC_BACKUPRESET_RELEASE | ( | ) | CLEAR_BIT(RCC->BDCR, RCC_BDCR_BDRST) |

Definition at line 7508 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_CLK_DISABLE [1/2]

| #define __HAL_RCC_BDMA_CLK_DISABLE | ( | ) | (RCC->AHB4ENR) &= ~ (RCC_AHB4ENR_BDMAEN) |

Definition at line 1604 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_CLK_DISABLE [2/2]

| #define __HAL_RCC_BDMA_CLK_DISABLE | ( | ) | (RCC->AHB4ENR) &= ~ (RCC_AHB4ENR_BDMAEN) |

Definition at line 1604 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_CLK_ENABLE [1/2]

| #define __HAL_RCC_BDMA_CLK_ENABLE | ( | ) |

Definition at line 1536 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_CLK_ENABLE [2/2]

| #define __HAL_RCC_BDMA_CLK_ENABLE | ( | ) |

Definition at line 1536 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_BDMA_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB4LPENR) &= ~ (RCC_AHB4LPENR_BDMALPEN) |

Definition at line 5680 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_BDMA_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB4LPENR) &= ~ (RCC_AHB4LPENR_BDMALPEN) |

Definition at line 5680 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_BDMA_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB4LPENR) |= (RCC_AHB4LPENR_BDMALPEN) |

Definition at line 5647 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_BDMA_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB4LPENR) |= (RCC_AHB4LPENR_BDMALPEN) |

Definition at line 5647 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_FORCE_RESET [1/2]

| #define __HAL_RCC_BDMA_FORCE_RESET | ( | ) | (RCC->AHB4RSTR) |= (RCC_AHB4RSTR_BDMARST) |

Definition at line 4871 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_FORCE_RESET [2/2]

| #define __HAL_RCC_BDMA_FORCE_RESET | ( | ) | (RCC->AHB4RSTR) |= (RCC_AHB4RSTR_BDMARST) |

Definition at line 4871 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_IS_CLK_DISABLED [1/2]

| #define __HAL_RCC_BDMA_IS_CLK_DISABLED | ( | ) | ((RCC->AHB4ENR & RCC_AHB4ENR_BDMAEN) == 0U) |

Definition at line 1678 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_IS_CLK_DISABLED [2/2]

| #define __HAL_RCC_BDMA_IS_CLK_DISABLED | ( | ) | ((RCC->AHB4ENR & RCC_AHB4ENR_BDMAEN) == 0U) |

Definition at line 1678 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_IS_CLK_ENABLED [1/2]

| #define __HAL_RCC_BDMA_IS_CLK_ENABLED | ( | ) | ((RCC->AHB4ENR & RCC_AHB4ENR_BDMAEN) != 0U) |

Definition at line 1644 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_IS_CLK_ENABLED [2/2]

| #define __HAL_RCC_BDMA_IS_CLK_ENABLED | ( | ) | ((RCC->AHB4ENR & RCC_AHB4ENR_BDMAEN) != 0U) |

Definition at line 1644 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_IS_CLK_SLEEP_DISABLED [1/2]

| #define __HAL_RCC_BDMA_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB4LPENR & (RCC_AHB4LPENR_BDMALPEN)) == 0U) |

Definition at line 5754 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_IS_CLK_SLEEP_DISABLED [2/2]

| #define __HAL_RCC_BDMA_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB4LPENR & (RCC_AHB4LPENR_BDMALPEN)) == 0U) |

Definition at line 5754 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_IS_CLK_SLEEP_ENABLED [1/2]

| #define __HAL_RCC_BDMA_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB4LPENR & (RCC_AHB4LPENR_BDMALPEN)) != 0U) |

Definition at line 5721 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_IS_CLK_SLEEP_ENABLED [2/2]

| #define __HAL_RCC_BDMA_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB4LPENR & (RCC_AHB4LPENR_BDMALPEN)) != 0U) |

Definition at line 5721 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_RELEASE_RESET [1/2]

| #define __HAL_RCC_BDMA_RELEASE_RESET | ( | ) | (RCC->AHB4RSTR) &= ~ (RCC_AHB4RSTR_BDMARST) |

Definition at line 4901 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BDMA_RELEASE_RESET [2/2]

| #define __HAL_RCC_BDMA_RELEASE_RESET | ( | ) | (RCC->AHB4RSTR) &= ~ (RCC_AHB4RSTR_BDMARST) |

Definition at line 4901 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_CLK_DISABLE [1/2]

| #define __HAL_RCC_BKPRAM_CLK_DISABLE | ( | ) | (RCC->AHB4ENR) &= ~ (RCC_AHB4ENR_BKPRAMEN) |

Definition at line 1615 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_CLK_DISABLE [2/2]

| #define __HAL_RCC_BKPRAM_CLK_DISABLE | ( | ) | (RCC->AHB4ENR) &= ~ (RCC_AHB4ENR_BKPRAMEN) |

Definition at line 1615 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_CLK_ENABLE [1/2]

| #define __HAL_RCC_BKPRAM_CLK_ENABLE | ( | ) |

Definition at line 1575 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_CLK_ENABLE [2/2]

| #define __HAL_RCC_BKPRAM_CLK_ENABLE | ( | ) |

Definition at line 1575 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_BKPRAM_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB4LPENR) &= ~ (RCC_AHB4LPENR_BKPRAMLPEN) |

Definition at line 5685 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_BKPRAM_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB4LPENR) &= ~ (RCC_AHB4LPENR_BKPRAMLPEN) |

Definition at line 5685 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_BKPRAM_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB4LPENR) |= (RCC_AHB4LPENR_BKPRAMLPEN) |

Definition at line 5652 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_BKPRAM_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB4LPENR) |= (RCC_AHB4LPENR_BKPRAMLPEN) |

Definition at line 5652 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_IS_CLK_DISABLED [1/2]

| #define __HAL_RCC_BKPRAM_IS_CLK_DISABLED | ( | ) | ((RCC->AHB4ENR & RCC_AHB4ENR_BKPRAMEN) == 0U) |

Definition at line 1689 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_IS_CLK_DISABLED [2/2]

| #define __HAL_RCC_BKPRAM_IS_CLK_DISABLED | ( | ) | ((RCC->AHB4ENR & RCC_AHB4ENR_BKPRAMEN) == 0U) |

Definition at line 1689 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_IS_CLK_ENABLED [1/2]

| #define __HAL_RCC_BKPRAM_IS_CLK_ENABLED | ( | ) | ((RCC->AHB4ENR & RCC_AHB4ENR_BKPRAMEN) != 0U) |

Definition at line 1655 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_IS_CLK_ENABLED [2/2]

| #define __HAL_RCC_BKPRAM_IS_CLK_ENABLED | ( | ) | ((RCC->AHB4ENR & RCC_AHB4ENR_BKPRAMEN) != 0U) |

Definition at line 1655 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_IS_CLK_SLEEP_DISABLED [1/2]

| #define __HAL_RCC_BKPRAM_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB4LPENR & (RCC_AHB4LPENR_BKPRAMLPEN)) == 0U) |

Definition at line 5759 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_IS_CLK_SLEEP_DISABLED [2/2]

| #define __HAL_RCC_BKPRAM_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB4LPENR & (RCC_AHB4LPENR_BKPRAMLPEN)) == 0U) |

Definition at line 5759 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_IS_CLK_SLEEP_ENABLED [1/2]

| #define __HAL_RCC_BKPRAM_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB4LPENR & (RCC_AHB4LPENR_BKPRAMLPEN)) != 0U) |

Definition at line 5726 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_BKPRAM_IS_CLK_SLEEP_ENABLED [2/2]

| #define __HAL_RCC_BKPRAM_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB4LPENR & (RCC_AHB4LPENR_BKPRAMLPEN)) != 0U) |

Definition at line 5726 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_CLK_DISABLE [1/2]

| #define __HAL_RCC_CEC_CLK_DISABLE | ( | ) | (RCC->APB1LENR) &= ~ (RCC_APB1LENR_CECEN) |

Definition at line 2062 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_CLK_DISABLE [2/2]

| #define __HAL_RCC_CEC_CLK_DISABLE | ( | ) | (RCC->APB1LENR) &= ~ (RCC_APB1LENR_CECEN) |

Definition at line 2062 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_CLK_ENABLE [1/2]

| #define __HAL_RCC_CEC_CLK_ENABLE | ( | ) |

Definition at line 1942 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_CLK_ENABLE [2/2]

| #define __HAL_RCC_CEC_CLK_ENABLE | ( | ) |

Definition at line 1942 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_CEC_CLK_SLEEP_DISABLE | ( | ) | (RCC->APB1LLPENR) &= ~ (RCC_APB1LLPENR_CECLPEN) |

Definition at line 5896 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_CEC_CLK_SLEEP_DISABLE | ( | ) | (RCC->APB1LLPENR) &= ~ (RCC_APB1LLPENR_CECLPEN) |

Definition at line 5896 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_CEC_CLK_SLEEP_ENABLE | ( | ) | (RCC->APB1LLPENR) |= (RCC_APB1LLPENR_CECLPEN) |

Definition at line 5851 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_CEC_CLK_SLEEP_ENABLE | ( | ) | (RCC->APB1LLPENR) |= (RCC_APB1LLPENR_CECLPEN) |

Definition at line 5851 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_FORCE_RESET [1/2]

| #define __HAL_RCC_CEC_FORCE_RESET | ( | ) | (RCC->APB1LRSTR) |= (RCC_APB1LRSTR_CECRST) |

Definition at line 4967 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_FORCE_RESET [2/2]

| #define __HAL_RCC_CEC_FORCE_RESET | ( | ) | (RCC->APB1LRSTR) |= (RCC_APB1LRSTR_CECRST) |

Definition at line 4967 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_IS_CLK_DISABLED [1/2]

| #define __HAL_RCC_CEC_IS_CLK_DISABLED | ( | ) | ((RCC->APB1LENR & RCC_APB1LENR_CECEN) == 0U) |

Definition at line 2153 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_IS_CLK_DISABLED [2/2]

| #define __HAL_RCC_CEC_IS_CLK_DISABLED | ( | ) | ((RCC->APB1LENR & RCC_APB1LENR_CECEN) == 0U) |

Definition at line 2153 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_IS_CLK_ENABLED [1/2]

| #define __HAL_RCC_CEC_IS_CLK_ENABLED | ( | ) | ((RCC->APB1LENR & RCC_APB1LENR_CECEN) != 0U) |

Definition at line 2111 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_IS_CLK_ENABLED [2/2]

| #define __HAL_RCC_CEC_IS_CLK_ENABLED | ( | ) | ((RCC->APB1LENR & RCC_APB1LENR_CECEN) != 0U) |

Definition at line 2111 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_IS_CLK_SLEEP_DISABLED [1/2]

| #define __HAL_RCC_CEC_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->APB1LLPENR & (RCC_APB1LLPENR_CECLPEN)) == 0U) |

Definition at line 5988 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_IS_CLK_SLEEP_DISABLED [2/2]

| #define __HAL_RCC_CEC_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->APB1LLPENR & (RCC_APB1LLPENR_CECLPEN)) == 0U) |

Definition at line 5988 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_IS_CLK_SLEEP_ENABLED [1/2]

| #define __HAL_RCC_CEC_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->APB1LLPENR & (RCC_APB1LLPENR_CECLPEN)) != 0U) |

Definition at line 5946 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_IS_CLK_SLEEP_ENABLED [2/2]

| #define __HAL_RCC_CEC_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->APB1LLPENR & (RCC_APB1LLPENR_CECLPEN)) != 0U) |

Definition at line 5946 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_RELEASE_RESET [1/2]

| #define __HAL_RCC_CEC_RELEASE_RESET | ( | ) | (RCC->APB1LRSTR) &= ~ (RCC_APB1LRSTR_CECRST) |

Definition at line 5008 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CEC_RELEASE_RESET [2/2]

| #define __HAL_RCC_CEC_RELEASE_RESET | ( | ) | (RCC->APB1LRSTR) &= ~ (RCC_APB1LRSTR_CECRST) |

Definition at line 5008 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_CLK_DISABLE [1/2]

| #define __HAL_RCC_COMP12_CLK_DISABLE | ( | ) | (RCC->APB4ENR) &= ~ (RCC_APB4ENR_COMP12EN) |

Definition at line 2565 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_CLK_DISABLE [2/2]

| #define __HAL_RCC_COMP12_CLK_DISABLE | ( | ) | (RCC->APB4ENR) &= ~ (RCC_APB4ENR_COMP12EN) |

Definition at line 2565 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_CLK_ENABLE [1/2]

| #define __HAL_RCC_COMP12_CLK_ENABLE | ( | ) |

Definition at line 2496 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_CLK_ENABLE [2/2]

| #define __HAL_RCC_COMP12_CLK_ENABLE | ( | ) |

Definition at line 2496 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_COMP12_CLK_SLEEP_DISABLE | ( | ) | (RCC->APB4LPENR) &= ~ (RCC_APB4LPENR_COMP12LPEN) |

Definition at line 6182 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_COMP12_CLK_SLEEP_DISABLE | ( | ) | (RCC->APB4LPENR) &= ~ (RCC_APB4LPENR_COMP12LPEN) |

Definition at line 6182 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_COMP12_CLK_SLEEP_ENABLE | ( | ) | (RCC->APB4LPENR) |= (RCC_APB4LPENR_COMP12LPEN) |

Definition at line 6154 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_COMP12_CLK_SLEEP_ENABLE | ( | ) | (RCC->APB4LPENR) |= (RCC_APB4LPENR_COMP12LPEN) |

Definition at line 6154 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_FORCE_RESET [1/2]

| #define __HAL_RCC_COMP12_FORCE_RESET | ( | ) | (RCC->APB4RSTR) |= (RCC_APB4RSTR_COMP12RST) |

Definition at line 5115 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_FORCE_RESET [2/2]

| #define __HAL_RCC_COMP12_FORCE_RESET | ( | ) | (RCC->APB4RSTR) |= (RCC_APB4RSTR_COMP12RST) |

Definition at line 5115 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_IS_CLK_DISABLED [1/2]

| #define __HAL_RCC_COMP12_IS_CLK_DISABLED | ( | ) | ((RCC->APB4ENR & RCC_APB4ENR_COMP12EN) == 0U) |

Definition at line 2627 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_IS_CLK_DISABLED [2/2]

| #define __HAL_RCC_COMP12_IS_CLK_DISABLED | ( | ) | ((RCC->APB4ENR & RCC_APB4ENR_COMP12EN) == 0U) |

Definition at line 2627 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_IS_CLK_ENABLED [1/2]

| #define __HAL_RCC_COMP12_IS_CLK_ENABLED | ( | ) | ((RCC->APB4ENR & RCC_APB4ENR_COMP12EN) != 0U) |

Definition at line 2599 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_IS_CLK_ENABLED [2/2]

| #define __HAL_RCC_COMP12_IS_CLK_ENABLED | ( | ) | ((RCC->APB4ENR & RCC_APB4ENR_COMP12EN) != 0U) |

Definition at line 2599 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_IS_CLK_SLEEP_DISABLED [1/2]

| #define __HAL_RCC_COMP12_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->APB4LPENR & (RCC_APB4LPENR_COMP12LPEN)) == 0U) |

Definition at line 6246 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_IS_CLK_SLEEP_DISABLED [2/2]

| #define __HAL_RCC_COMP12_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->APB4LPENR & (RCC_APB4LPENR_COMP12LPEN)) == 0U) |

Definition at line 6246 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_IS_CLK_SLEEP_ENABLED [1/2]

| #define __HAL_RCC_COMP12_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->APB4LPENR & (RCC_APB4LPENR_COMP12LPEN)) != 0U) |

Definition at line 6218 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_IS_CLK_SLEEP_ENABLED [2/2]

| #define __HAL_RCC_COMP12_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->APB4LPENR & (RCC_APB4LPENR_COMP12LPEN)) != 0U) |

Definition at line 6218 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_RELEASE_RESET [1/2]

| #define __HAL_RCC_COMP12_RELEASE_RESET | ( | ) | (RCC->APB4RSTR) &= ~ (RCC_APB4RSTR_COMP12RST) |

Definition at line 5143 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_COMP12_RELEASE_RESET [2/2]

| #define __HAL_RCC_COMP12_RELEASE_RESET | ( | ) | (RCC->APB4RSTR) &= ~ (RCC_APB4RSTR_COMP12RST) |

Definition at line 5143 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_CLK_DISABLE [1/2]

| #define __HAL_RCC_CRS_CLK_DISABLE | ( | ) | (RCC->APB1HENR) &= ~ (RCC_APB1HENR_CRSEN) |

Definition at line 2066 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_CLK_DISABLE [2/2]

| #define __HAL_RCC_CRS_CLK_DISABLE | ( | ) | (RCC->APB1HENR) &= ~ (RCC_APB1HENR_CRSEN) |

Definition at line 2066 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_CLK_ENABLE [1/2]

| #define __HAL_RCC_CRS_CLK_ENABLE | ( | ) |

Definition at line 1974 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_CLK_ENABLE [2/2]

| #define __HAL_RCC_CRS_CLK_ENABLE | ( | ) |

Definition at line 1974 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_CRS_CLK_SLEEP_DISABLE | ( | ) | (RCC->APB1HLPENR) &= ~ (RCC_APB1HLPENR_CRSLPEN) |

Definition at line 5900 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_CRS_CLK_SLEEP_DISABLE | ( | ) | (RCC->APB1HLPENR) &= ~ (RCC_APB1HLPENR_CRSLPEN) |

Definition at line 5900 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_CRS_CLK_SLEEP_ENABLE | ( | ) | (RCC->APB1HLPENR) |= (RCC_APB1HLPENR_CRSLPEN) |

Definition at line 5855 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_CRS_CLK_SLEEP_ENABLE | ( | ) | (RCC->APB1HLPENR) |= (RCC_APB1HLPENR_CRSLPEN) |

Definition at line 5855 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_FORCE_RESET [1/2]

| #define __HAL_RCC_CRS_FORCE_RESET | ( | ) | (RCC->APB1HRSTR) |= (RCC_APB1HRSTR_CRSRST) |

Definition at line 4971 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_FORCE_RESET [2/2]

| #define __HAL_RCC_CRS_FORCE_RESET | ( | ) | (RCC->APB1HRSTR) |= (RCC_APB1HRSTR_CRSRST) |

Definition at line 4971 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_IS_CLK_DISABLED [1/2]

| #define __HAL_RCC_CRS_IS_CLK_DISABLED | ( | ) | ((RCC->APB1HENR & RCC_APB1HENR_CRSEN) == 0U) |

Definition at line 2157 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_IS_CLK_DISABLED [2/2]

| #define __HAL_RCC_CRS_IS_CLK_DISABLED | ( | ) | ((RCC->APB1HENR & RCC_APB1HENR_CRSEN) == 0U) |

Definition at line 2157 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_IS_CLK_ENABLED [1/2]

| #define __HAL_RCC_CRS_IS_CLK_ENABLED | ( | ) | ((RCC->APB1HENR & RCC_APB1HENR_CRSEN) != 0U) |

Definition at line 2115 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_IS_CLK_ENABLED [2/2]

| #define __HAL_RCC_CRS_IS_CLK_ENABLED | ( | ) | ((RCC->APB1HENR & RCC_APB1HENR_CRSEN) != 0U) |

Definition at line 2115 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_IS_CLK_SLEEP_DISABLED [1/2]

| #define __HAL_RCC_CRS_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->APB1HLPENR & (RCC_APB1HLPENR_CRSLPEN)) == 0U) |

Definition at line 5992 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_IS_CLK_SLEEP_DISABLED [2/2]

| #define __HAL_RCC_CRS_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->APB1HLPENR & (RCC_APB1HLPENR_CRSLPEN)) == 0U) |

Definition at line 5992 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_IS_CLK_SLEEP_ENABLED [1/2]

| #define __HAL_RCC_CRS_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->APB1HLPENR & (RCC_APB1HLPENR_CRSLPEN)) != 0U) |

Definition at line 5950 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_IS_CLK_SLEEP_ENABLED [2/2]

| #define __HAL_RCC_CRS_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->APB1HLPENR & (RCC_APB1HLPENR_CRSLPEN)) != 0U) |

Definition at line 5950 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_RELEASE_RESET [1/2]

| #define __HAL_RCC_CRS_RELEASE_RESET | ( | ) | (RCC->APB1HRSTR) &= ~ (RCC_APB1HRSTR_CRSRST) |

Definition at line 5012 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CRS_RELEASE_RESET [2/2]

| #define __HAL_RCC_CRS_RELEASE_RESET | ( | ) | (RCC->APB1HRSTR) &= ~ (RCC_APB1HRSTR_CRSRST) |

Definition at line 5012 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CSI_CALIBRATIONVALUE_ADJUST [1/2]

| #define __HAL_RCC_CSI_CALIBRATIONVALUE_ADJUST | ( | __CSICalibrationValue__ | ) |

Macro Adjusts the Internal oscillator (CSI) calibration value.

- Note

- The calibration is used to compensate for the variations in voltage and temperature that influence the frequency of the internal CSI RC.

- Parameters

-

<strong>CSICalibrationValue</strong> specifies the calibration trimming value. This parameter must be a number between 0 and 0x1F.

Definition at line 7266 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CSI_CALIBRATIONVALUE_ADJUST [2/2]

| #define __HAL_RCC_CSI_CALIBRATIONVALUE_ADJUST | ( | __CSICalibrationValue__ | ) |

Macro Adjusts the Internal oscillator (CSI) calibration value.

- Note

- The calibration is used to compensate for the variations in voltage and temperature that influence the frequency of the internal CSI RC.

- Parameters

-

<strong>CSICalibrationValue</strong> specifies the calibration trimming value. This parameter must be a number between 0 and 0x1F.

Definition at line 7266 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CSI_DISABLE [1/2]

| #define __HAL_RCC_CSI_DISABLE | ( | ) | CLEAR_BIT(RCC->CR, RCC_CR_CSION) |

Definition at line 7237 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CSI_DISABLE [2/2]

| #define __HAL_RCC_CSI_DISABLE | ( | ) | CLEAR_BIT(RCC->CR, RCC_CR_CSION) |

Definition at line 7237 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CSI_ENABLE [1/2]

| #define __HAL_RCC_CSI_ENABLE | ( | ) | SET_BIT(RCC->CR, RCC_CR_CSION) |

Macros to enable or disable the Internal oscillator (CSI).

- Note

- The CSI is stopped by hardware when entering STOP and STANDBY modes. It is used (enabled by hardware) as system clock source after start-up from Reset, wakeup from STOP and STANDBY mode, or in case of failure of the HSE used directly or indirectly as system clock (if the Clock Security System CSS is enabled).

- CSI can not be stopped if it is used as system clock source. In this case, you have to select another source of the system clock then stop the CSI.

- After enabling the CSI, the application software should wait on CSIRDY flag to be set indicating that CSI clock is stable and can be used as system clock source.

- When the CSI is stopped, CSIRDY flag goes low after 6 CSI oscillator clock cycles.

Definition at line 7236 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CSI_ENABLE [2/2]

| #define __HAL_RCC_CSI_ENABLE | ( | ) | SET_BIT(RCC->CR, RCC_CR_CSION) |

Macros to enable or disable the Internal oscillator (CSI).

- Note

- The CSI is stopped by hardware when entering STOP and STANDBY modes. It is used (enabled by hardware) as system clock source after start-up from Reset, wakeup from STOP and STANDBY mode, or in case of failure of the HSE used directly or indirectly as system clock (if the Clock Security System CSS is enabled).

- CSI can not be stopped if it is used as system clock source. In this case, you have to select another source of the system clock then stop the CSI.

- After enabling the CSI, the application software should wait on CSIRDY flag to be set indicating that CSI clock is stable and can be used as system clock source.

- When the CSI is stopped, CSIRDY flag goes low after 6 CSI oscillator clock cycles.

Definition at line 7236 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CSISTOP_DISABLE [1/2]

| #define __HAL_RCC_CSISTOP_DISABLE | ( | ) | CLEAR_BIT(RCC->CR, RCC_CR_CSIKERON) |

Definition at line 7282 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CSISTOP_DISABLE [2/2]

| #define __HAL_RCC_CSISTOP_DISABLE | ( | ) | CLEAR_BIT(RCC->CR, RCC_CR_CSIKERON) |

Definition at line 7282 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CSISTOP_ENABLE [1/2]

| #define __HAL_RCC_CSISTOP_ENABLE | ( | ) | SET_BIT(RCC->CR, RCC_CR_CSIKERON) |

Macros to enable or disable the force of the Low-power Internal oscillator (CSI) in STOP mode to be quickly available as kernel clock for USARTs and I2Cs.

- Note

- Keeping the CSI ON in STOP mode allows to avoid slowing down the communication speed because of the CSI start-up time.

- The enable of this function has not effect on the CSION bit. This parameter can be: ENABLE or DISABLE.

- Return values

-

None

Definition at line 7281 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_CSISTOP_ENABLE [2/2]

| #define __HAL_RCC_CSISTOP_ENABLE | ( | ) | SET_BIT(RCC->CR, RCC_CR_CSIKERON) |

Macros to enable or disable the force of the Low-power Internal oscillator (CSI) in STOP mode to be quickly available as kernel clock for USARTs and I2Cs.

- Note

- Keeping the CSI ON in STOP mode allows to avoid slowing down the communication speed because of the CSI start-up time.

- The enable of this function has not effect on the CSION bit. This parameter can be: ENABLE or DISABLE.

- Return values

-

None

Definition at line 7281 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_D1SRAM1_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_D1SRAM1_CLK_SLEEP_DISABLE __HAL_RCC_AXISRAM1_CLK_SLEEP_DISABLE /* For backward compatibility */ |

Definition at line 5252 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_D1SRAM1_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_D1SRAM1_CLK_SLEEP_DISABLE __HAL_RCC_AXISRAM1_CLK_SLEEP_DISABLE /* For backward compatibility */ |

Definition at line 5252 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_D1SRAM1_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_D1SRAM1_CLK_SLEEP_ENABLE __HAL_RCC_AXISRAM1_CLK_SLEEP_ENABLE /* For backward compatibility */ |

Definition at line 5206 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_D1SRAM1_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_D1SRAM1_CLK_SLEEP_ENABLE __HAL_RCC_AXISRAM1_CLK_SLEEP_ENABLE /* For backward compatibility */ |

Definition at line 5206 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_D3SRAM1_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_D3SRAM1_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB4LPENR &= ~ (RCC_AHB4LPENR_D3SRAM1LPEN)) |

Definition at line 5690 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_D3SRAM1_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_D3SRAM1_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB4LPENR &= ~ (RCC_AHB4LPENR_D3SRAM1LPEN)) |

Definition at line 5690 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_D3SRAM1_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_D3SRAM1_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB4LPENR |= (RCC_AHB4LPENR_D3SRAM1LPEN)) |

Definition at line 5657 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_D3SRAM1_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_D3SRAM1_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB4LPENR |= (RCC_AHB4LPENR_D3SRAM1LPEN)) |

Definition at line 5657 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_D3SRAM1_IS_CLK_SLEEP_DISABLED [1/2]

| #define __HAL_RCC_D3SRAM1_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB4LPENR & (RCC_AHB4LPENR_D3SRAM1LPEN)) == 0U) |

Definition at line 5764 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_D3SRAM1_IS_CLK_SLEEP_DISABLED [2/2]

| #define __HAL_RCC_D3SRAM1_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB4LPENR & (RCC_AHB4LPENR_D3SRAM1LPEN)) == 0U) |

Definition at line 5764 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_D3SRAM1_IS_CLK_SLEEP_ENABLED [1/2]

| #define __HAL_RCC_D3SRAM1_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB4LPENR & (RCC_AHB4LPENR_D3SRAM1LPEN)) != 0U) |

Definition at line 5731 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_D3SRAM1_IS_CLK_SLEEP_ENABLED [2/2]

| #define __HAL_RCC_D3SRAM1_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB4LPENR & (RCC_AHB4LPENR_D3SRAM1LPEN)) != 0U) |

Definition at line 5731 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_CLK_DISABLE [1/2]

| #define __HAL_RCC_DAC12_CLK_DISABLE | ( | ) | (RCC->APB1LENR) &= ~ (RCC_APB1LENR_DAC12EN) |

Definition at line 2063 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_CLK_DISABLE [2/2]

| #define __HAL_RCC_DAC12_CLK_DISABLE | ( | ) | (RCC->APB1LENR) &= ~ (RCC_APB1LENR_DAC12EN) |

Definition at line 2063 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_CLK_ENABLE [1/2]

| #define __HAL_RCC_DAC12_CLK_ENABLE | ( | ) |

Definition at line 1950 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_CLK_ENABLE [2/2]

| #define __HAL_RCC_DAC12_CLK_ENABLE | ( | ) |

Definition at line 1950 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_DAC12_CLK_SLEEP_DISABLE | ( | ) | (RCC->APB1LLPENR) &= ~ (RCC_APB1LLPENR_DAC12LPEN) |

Definition at line 5897 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_DAC12_CLK_SLEEP_DISABLE | ( | ) | (RCC->APB1LLPENR) &= ~ (RCC_APB1LLPENR_DAC12LPEN) |

Definition at line 5897 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_DAC12_CLK_SLEEP_ENABLE | ( | ) | (RCC->APB1LLPENR) |= (RCC_APB1LLPENR_DAC12LPEN) |

Definition at line 5852 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_DAC12_CLK_SLEEP_ENABLE | ( | ) | (RCC->APB1LLPENR) |= (RCC_APB1LLPENR_DAC12LPEN) |

Definition at line 5852 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_FORCE_RESET [1/2]

| #define __HAL_RCC_DAC12_FORCE_RESET | ( | ) | (RCC->APB1LRSTR) |= (RCC_APB1LRSTR_DAC12RST) |

Definition at line 4968 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_FORCE_RESET [2/2]

| #define __HAL_RCC_DAC12_FORCE_RESET | ( | ) | (RCC->APB1LRSTR) |= (RCC_APB1LRSTR_DAC12RST) |

Definition at line 4968 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_IS_CLK_DISABLED [1/2]

| #define __HAL_RCC_DAC12_IS_CLK_DISABLED | ( | ) | ((RCC->APB1LENR & RCC_APB1LENR_DAC12EN) == 0U) |

Definition at line 2154 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_IS_CLK_DISABLED [2/2]

| #define __HAL_RCC_DAC12_IS_CLK_DISABLED | ( | ) | ((RCC->APB1LENR & RCC_APB1LENR_DAC12EN) == 0U) |

Definition at line 2154 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_IS_CLK_ENABLED [1/2]

| #define __HAL_RCC_DAC12_IS_CLK_ENABLED | ( | ) | ((RCC->APB1LENR & RCC_APB1LENR_DAC12EN) != 0U) |

Definition at line 2112 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_IS_CLK_ENABLED [2/2]

| #define __HAL_RCC_DAC12_IS_CLK_ENABLED | ( | ) | ((RCC->APB1LENR & RCC_APB1LENR_DAC12EN) != 0U) |

Definition at line 2112 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_IS_CLK_SLEEP_DISABLED [1/2]

| #define __HAL_RCC_DAC12_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->APB1LLPENR & (RCC_APB1LLPENR_DAC12LPEN)) == 0U) |

Definition at line 5989 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_IS_CLK_SLEEP_DISABLED [2/2]

| #define __HAL_RCC_DAC12_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->APB1LLPENR & (RCC_APB1LLPENR_DAC12LPEN)) == 0U) |

Definition at line 5989 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_IS_CLK_SLEEP_ENABLED [1/2]

| #define __HAL_RCC_DAC12_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->APB1LLPENR & (RCC_APB1LLPENR_DAC12LPEN)) != 0U) |

Definition at line 5947 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_IS_CLK_SLEEP_ENABLED [2/2]

| #define __HAL_RCC_DAC12_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->APB1LLPENR & (RCC_APB1LLPENR_DAC12LPEN)) != 0U) |

Definition at line 5947 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_RELEASE_RESET [1/2]

| #define __HAL_RCC_DAC12_RELEASE_RESET | ( | ) | (RCC->APB1LRSTR) &= ~ (RCC_APB1LRSTR_DAC12RST) |

Definition at line 5009 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DAC12_RELEASE_RESET [2/2]

| #define __HAL_RCC_DAC12_RELEASE_RESET | ( | ) | (RCC->APB1LRSTR) &= ~ (RCC_APB1LRSTR_DAC12RST) |

Definition at line 5009 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_CLK_DISABLE [1/2]

| #define __HAL_RCC_DCMI_CLK_DISABLE | ( | ) | (RCC->AHB2ENR &= ~ (RCC_AHB2ENR_DCMIEN)) |

Definition at line 1297 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_CLK_DISABLE [2/2]

| #define __HAL_RCC_DCMI_CLK_DISABLE | ( | ) | (RCC->AHB2ENR &= ~ (RCC_AHB2ENR_DCMIEN)) |

Definition at line 1297 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_CLK_ENABLE [1/2]

| #define __HAL_RCC_DCMI_CLK_ENABLE | ( | ) |

Enable or disable the AHB2 peripheral clock.

- Note

- After reset, the peripheral clock (used for registers read/write access) is disabled and the application software has to enable this clock before using it.

Definition at line 1162 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_CLK_ENABLE [2/2]

| #define __HAL_RCC_DCMI_CLK_ENABLE | ( | ) |

Enable or disable the AHB2 peripheral clock.

- Note

- After reset, the peripheral clock (used for registers read/write access) is disabled and the application software has to enable this clock before using it.

Definition at line 1162 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_CLK_SLEEP_DISABLE [1/2]

| #define __HAL_RCC_DCMI_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB2LPENR &= ~ (RCC_AHB2LPENR_DCMILPEN)) |

Definition at line 5505 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_CLK_SLEEP_DISABLE [2/2]

| #define __HAL_RCC_DCMI_CLK_SLEEP_DISABLE | ( | ) | (RCC->AHB2LPENR &= ~ (RCC_AHB2LPENR_DCMILPEN)) |

Definition at line 5505 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_CLK_SLEEP_ENABLE [1/2]

| #define __HAL_RCC_DCMI_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB2LPENR |= (RCC_AHB2LPENR_DCMILPEN)) |

ENABLE or disable the AHB2 peripheral clock during Low Power (Sleep) mode.

- Note

- Peripheral clock gating in SLEEP mode can be used to further reduce power consumption.

- After wakeup from SLEEP mode, the peripheral clock is ENABLEd again.

- By default, all peripheral clocks are ENABLEd during SLEEP mode.

Definition at line 5468 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_CLK_SLEEP_ENABLE [2/2]

| #define __HAL_RCC_DCMI_CLK_SLEEP_ENABLE | ( | ) | (RCC->AHB2LPENR |= (RCC_AHB2LPENR_DCMILPEN)) |

ENABLE or disable the AHB2 peripheral clock during Low Power (Sleep) mode.

- Note

- Peripheral clock gating in SLEEP mode can be used to further reduce power consumption.

- After wakeup from SLEEP mode, the peripheral clock is ENABLEd again.

- By default, all peripheral clocks are ENABLEd during SLEEP mode.

Definition at line 5468 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_FORCE_RESET [1/2]

| #define __HAL_RCC_DCMI_FORCE_RESET | ( | ) | (RCC->AHB2RSTR |= (RCC_AHB2RSTR_DCMIRST)) |

Definition at line 4789 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_FORCE_RESET [2/2]

| #define __HAL_RCC_DCMI_FORCE_RESET | ( | ) | (RCC->AHB2RSTR |= (RCC_AHB2RSTR_DCMIRST)) |

Definition at line 4789 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_IS_CLK_DISABLED [1/2]

| #define __HAL_RCC_DCMI_IS_CLK_DISABLED | ( | ) | ((RCC->AHB2ENR & RCC_AHB2ENR_DCMIEN) == 0U) |

Definition at line 1383 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_IS_CLK_DISABLED [2/2]

| #define __HAL_RCC_DCMI_IS_CLK_DISABLED | ( | ) | ((RCC->AHB2ENR & RCC_AHB2ENR_DCMIEN) == 0U) |

Definition at line 1383 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_IS_CLK_ENABLED [1/2]

| #define __HAL_RCC_DCMI_IS_CLK_ENABLED | ( | ) | ((RCC->AHB2ENR & RCC_AHB2ENR_DCMIEN) != 0U) |

Get the enable or disable status of the AHB2 peripheral clock.

- Note

- After reset, the peripheral clock (used for registers read/write access) is disabled and the application software has to enable this clock before using it.

Definition at line 1343 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_IS_CLK_ENABLED [2/2]

| #define __HAL_RCC_DCMI_IS_CLK_ENABLED | ( | ) | ((RCC->AHB2ENR & RCC_AHB2ENR_DCMIEN) != 0U) |

Get the enable or disable status of the AHB2 peripheral clock.

- Note

- After reset, the peripheral clock (used for registers read/write access) is disabled and the application software has to enable this clock before using it.

Definition at line 1343 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_IS_CLK_SLEEP_DISABLED [1/2]

| #define __HAL_RCC_DCMI_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB2LPENR & (RCC_AHB2LPENR_DCMILPEN)) == 0U) |

Definition at line 5586 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_IS_CLK_SLEEP_DISABLED [2/2]

| #define __HAL_RCC_DCMI_IS_CLK_SLEEP_DISABLED | ( | ) | ((RCC->AHB2LPENR & (RCC_AHB2LPENR_DCMILPEN)) == 0U) |

Definition at line 5586 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_IS_CLK_SLEEP_ENABLED [1/2]

| #define __HAL_RCC_DCMI_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB2LPENR & (RCC_AHB2LPENR_DCMILPEN)) != 0U) |

Get the enable or disable status of the AHB2 peripheral clock during Low Poser (Sleep) mode.

- Note

- Peripheral clock gating in SLEEP mode can be used to further reduce power consumption.

- After wakeup from SLEEP mode, the peripheral clock is enabled again.

- By default, all peripheral clocks are enabled during SLEEP mode.

Definition at line 5549 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_IS_CLK_SLEEP_ENABLED [2/2]

| #define __HAL_RCC_DCMI_IS_CLK_SLEEP_ENABLED | ( | ) | ((RCC->AHB2LPENR & (RCC_AHB2LPENR_DCMILPEN)) != 0U) |

Get the enable or disable status of the AHB2 peripheral clock during Low Poser (Sleep) mode.

- Note

- Peripheral clock gating in SLEEP mode can be used to further reduce power consumption.

- After wakeup from SLEEP mode, the peripheral clock is enabled again.

- By default, all peripheral clocks are enabled during SLEEP mode.

Definition at line 5549 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_RELEASE_RESET [1/2]

| #define __HAL_RCC_DCMI_RELEASE_RESET | ( | ) | (RCC->AHB2RSTR &= ~ (RCC_AHB2RSTR_DCMIRST)) |

Definition at line 4817 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DCMI_RELEASE_RESET [2/2]

| #define __HAL_RCC_DCMI_RELEASE_RESET | ( | ) | (RCC->AHB2RSTR &= ~ (RCC_AHB2RSTR_DCMIRST)) |

Definition at line 4817 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DFSDM1_CLK_DISABLE [1/2]

| #define __HAL_RCC_DFSDM1_CLK_DISABLE | ( | ) | (RCC->APB2ENR) &= ~ (RCC_APB2ENR_DFSDM1EN) |

Definition at line 2345 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DFSDM1_CLK_DISABLE [2/2]

| #define __HAL_RCC_DFSDM1_CLK_DISABLE | ( | ) | (RCC->APB2ENR) &= ~ (RCC_APB2ENR_DFSDM1EN) |

Definition at line 2345 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc.h.

◆ __HAL_RCC_DFSDM1_CLK_ENABLE [1/2]

| #define __HAL_RCC_DFSDM1_CLK_ENABLE | ( | ) |