Header file of RCC HAL module. More...

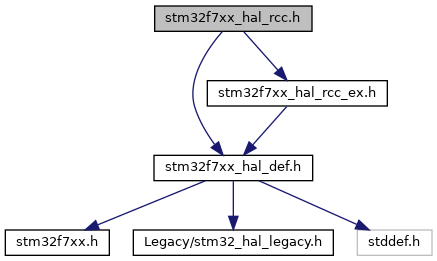

Include dependency graph for stm32f7xx_hal_rcc.h:

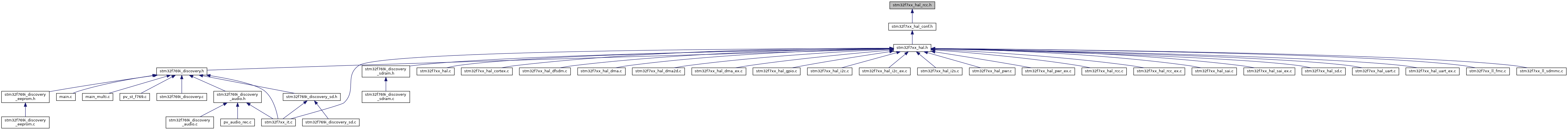

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | RCC_ClkInitTypeDef |

| RCC System, AHB and APB busses clock configuration structure definition. More... | |

| struct | RCC_OscInitTypeDef |

| RCC Internal/External Oscillator (HSE, HSI, LSE and LSI) configuration structure definition. More... | |

Macros | |

| #define | __HAL_RCC_AHB1_FORCE_RESET() (RCC->AHB1RSTR = 0xFFFFFFFFU) |

| #define | __HAL_RCC_AHB1_RELEASE_RESET() (RCC->AHB1RSTR = 0x00U) |

| #define | __HAL_RCC_APB1_FORCE_RESET() (RCC->APB1RSTR = 0xFFFFFFFFU) |

| #define | __HAL_RCC_APB1_RELEASE_RESET() (RCC->APB1RSTR = 0x00U) |

| #define | __HAL_RCC_APB2_FORCE_RESET() (RCC->APB2RSTR = 0xFFFFFFFFU) |

| #define | __HAL_RCC_APB2_RELEASE_RESET() (RCC->APB2RSTR = 0x00U) |

| #define | __HAL_RCC_BACKUPRESET_FORCE() (RCC->BDCR |= (RCC_BDCR_BDRST)) |

| Macros to force or release the Backup domain reset. More... | |

| #define | __HAL_RCC_BACKUPRESET_RELEASE() (RCC->BDCR &= ~(RCC_BDCR_BDRST)) |

| #define | __HAL_RCC_CLEAR_IT(__INTERRUPT__) (*(__IO uint8_t *) RCC_CIR_BYTE2_ADDRESS = (__INTERRUPT__)) |

| Clear the RCC's interrupt pending bits (Perform Byte access to RCC_CIR[23:16] bits to clear the selected interrupt pending bits. More... | |

| #define | __HAL_RCC_CLEAR_RESET_FLAGS() (RCC->CSR |= RCC_CSR_RMVF) |

| Set RMVF bit to clear the reset flags: RCC_FLAG_PINRST, RCC_FLAG_PORRST, RCC_FLAG_SFTRST, RCC_FLAG_IWDGRST, RCC_FLAG_WWDGRST and RCC_FLAG_LPWRRST. More... | |

| #define | __HAL_RCC_CRC_CLK_DISABLE() (RCC->AHB1ENR &= ~(RCC_AHB1ENR_CRCEN)) |

| #define | __HAL_RCC_CRC_CLK_ENABLE() |

| #define | __HAL_RCC_CRC_CLK_SLEEP_DISABLE() (RCC->AHB1LPENR &= ~(RCC_AHB1LPENR_CRCLPEN)) |

| #define | __HAL_RCC_CRC_CLK_SLEEP_ENABLE() (RCC->AHB1LPENR |= (RCC_AHB1LPENR_CRCLPEN)) |

| #define | __HAL_RCC_CRC_FORCE_RESET() (RCC->AHB1RSTR |= (RCC_AHB1RSTR_CRCRST)) |

| #define | __HAL_RCC_CRC_IS_CLK_DISABLED() ((RCC->AHB1ENR & (RCC_AHB1ENR_CRCEN)) == RESET) |

| #define | __HAL_RCC_CRC_IS_CLK_ENABLED() ((RCC->AHB1ENR & (RCC_AHB1ENR_CRCEN)) != RESET) |

| #define | __HAL_RCC_CRC_IS_CLK_SLEEP_DISABLED() ((RCC->AHB1LPENR & (RCC_AHB1LPENR_CRCLPEN)) == RESET) |

| #define | __HAL_RCC_CRC_IS_CLK_SLEEP_ENABLED() ((RCC->AHB1LPENR & (RCC_AHB1LPENR_CRCLPEN)) != RESET) |

| #define | __HAL_RCC_CRC_RELEASE_RESET() (RCC->AHB1RSTR &= ~(RCC_AHB1RSTR_CRCRST)) |

| #define | __HAL_RCC_DISABLE_IT(__INTERRUPT__) (*(__IO uint8_t *) RCC_CIR_BYTE1_ADDRESS &= (uint8_t)(~(__INTERRUPT__))) |

| Disable RCC interrupt (Perform Byte access to RCC_CIR[14:8] bits to disable the selected interrupts). More... | |

| #define | __HAL_RCC_DMA1_CLK_DISABLE() (RCC->AHB1ENR &= ~(RCC_AHB1ENR_DMA1EN)) |

| #define | __HAL_RCC_DMA1_CLK_ENABLE() |

| #define | __HAL_RCC_DMA1_CLK_SLEEP_DISABLE() (RCC->AHB1LPENR &= ~(RCC_AHB1LPENR_DMA1LPEN)) |

| #define | __HAL_RCC_DMA1_CLK_SLEEP_ENABLE() (RCC->AHB1LPENR |= (RCC_AHB1LPENR_DMA1LPEN)) |

| #define | __HAL_RCC_DMA1_FORCE_RESET() (RCC->AHB1RSTR |= (RCC_AHB1RSTR_DMA1RST)) |

| #define | __HAL_RCC_DMA1_IS_CLK_DISABLED() ((RCC->AHB1ENR & (RCC_AHB1ENR_DMA1EN)) == RESET) |

| #define | __HAL_RCC_DMA1_IS_CLK_ENABLED() ((RCC->AHB1ENR & (RCC_AHB1ENR_DMA1EN)) != RESET) |

| #define | __HAL_RCC_DMA1_IS_CLK_SLEEP_DISABLED() ((RCC->AHB1LPENR & (RCC_AHB1LPENR_DMA1LPEN)) == RESET) |

| #define | __HAL_RCC_DMA1_IS_CLK_SLEEP_ENABLED() ((RCC->AHB1LPENR & (RCC_AHB1LPENR_DMA1LPEN)) != RESET) |

| #define | __HAL_RCC_DMA1_RELEASE_RESET() (RCC->AHB1RSTR &= ~(RCC_AHB1RSTR_DMA1RST)) |

| #define | __HAL_RCC_ENABLE_IT(__INTERRUPT__) (*(__IO uint8_t *) RCC_CIR_BYTE1_ADDRESS |= (__INTERRUPT__)) |

| Enable RCC interrupt (Perform Byte access to RCC_CIR[14:8] bits to enable the selected interrupts). More... | |

| #define | __HAL_RCC_GET_FLAG(__FLAG__) (((((((__FLAG__) >> 5) == 1)? RCC->CR :((((__FLAG__) >> 5) == 2) ? RCC->BDCR :((((__FLAG__) >> 5) == 3)? RCC->CSR :RCC->CIR))) & ((uint32_t)1 << ((__FLAG__) & RCC_FLAG_MASK)))!= 0)? 1 : 0) |

| #define | __HAL_RCC_GET_IT(__INTERRUPT__) ((RCC->CIR & (__INTERRUPT__)) == (__INTERRUPT__)) |

| Check the RCC's interrupt has occurred or not. More... | |

| #define | __HAL_RCC_GET_PLL_OSCSOURCE() ((uint32_t)(RCC->PLLCFGR & RCC_PLLCFGR_PLLSRC)) |

| Macro to get the oscillator used as PLL clock source. More... | |

| #define | __HAL_RCC_GET_RTC_HSE_PRESCALER() (READ_BIT(RCC->CFGR, RCC_CFGR_RTCPRE) | RCC_BDCR_RTCSEL) |

| Get the RTC and HSE clock divider (RTCPRE). More... | |

| #define | __HAL_RCC_GET_RTC_SOURCE() (READ_BIT(RCC->BDCR, RCC_BDCR_RTCSEL)) |

| Macro to get the RTC clock source. More... | |

| #define | __HAL_RCC_GET_SYSCLK_SOURCE() (RCC->CFGR & RCC_CFGR_SWS) |

| Macro to get the clock source used as system clock. More... | |

| #define | __HAL_RCC_HSE_CONFIG(__STATE__) |

| Macro to configure the External High Speed oscillator (HSE). More... | |

| #define | __HAL_RCC_HSI_CALIBRATIONVALUE_ADJUST(__HSICALIBRATIONVALUE__) |

| Macro to adjust the Internal High Speed oscillator (HSI) calibration value. More... | |

| #define | __HAL_RCC_HSI_DISABLE() (RCC->CR &= ~(RCC_CR_HSION)) |

| #define | __HAL_RCC_HSI_ENABLE() (RCC->CR |= (RCC_CR_HSION)) |

| Macros to enable or disable the Internal High Speed oscillator (HSI). More... | |

| #define | __HAL_RCC_I2S_CONFIG(__SOURCE__) |

| Macro to configure the I2S clock source (I2SCLK). More... | |

| #define | __HAL_RCC_LSE_CONFIG(__STATE__) |

| Macro to configure the External Low Speed oscillator (LSE). More... | |

| #define | __HAL_RCC_LSEDRIVE_CONFIG(__RCC_LSEDRIVE__) (MODIFY_REG(RCC->BDCR, RCC_BDCR_LSEDRV, (uint32_t)(__RCC_LSEDRIVE__) )) |

| Macro to configures the External Low Speed oscillator (LSE) drive capability. More... | |

| #define | __HAL_RCC_LSI_DISABLE() (RCC->CSR &= ~(RCC_CSR_LSION)) |

| #define | __HAL_RCC_LSI_ENABLE() (RCC->CSR |= (RCC_CSR_LSION)) |

| Macros to enable or disable the Internal Low Speed oscillator (LSI). More... | |

| #define | __HAL_RCC_MCO1_CONFIG(__MCOCLKSOURCE__, __MCODIV__) MODIFY_REG(RCC->CFGR, (RCC_CFGR_MCO1 | RCC_CFGR_MCO1PRE), ((__MCOCLKSOURCE__) | (__MCODIV__))) |

| Macro to configure the MCO1 clock. More... | |

| #define | __HAL_RCC_MCO2_CONFIG(__MCOCLKSOURCE__, __MCODIV__) MODIFY_REG(RCC->CFGR, (RCC_CFGR_MCO2 | RCC_CFGR_MCO2PRE), ((__MCOCLKSOURCE__) | ((__MCODIV__) << 3))); |

| Macro to configure the MCO2 clock. More... | |

| #define | __HAL_RCC_PLL_DISABLE() CLEAR_BIT(RCC->CR, RCC_CR_PLLON) |

| #define | __HAL_RCC_PLL_ENABLE() SET_BIT(RCC->CR, RCC_CR_PLLON) |

| Macros to enable or disable the main PLL. More... | |

| #define | __HAL_RCC_PLL_PLLM_CONFIG(__PLLM__) MODIFY_REG(RCC->PLLCFGR, RCC_PLLCFGR_PLLM, (__PLLM__)) |

| Macro to configure the PLL multiplication factor. More... | |

| #define | __HAL_RCC_PLL_PLLSOURCE_CONFIG(__PLLSOURCE__) MODIFY_REG(RCC->PLLCFGR, RCC_PLLCFGR_PLLSRC, (__PLLSOURCE__)) |

| Macro to configure the PLL clock source. More... | |

| #define | __HAL_RCC_PLLI2S_DISABLE() (RCC->CR &= ~(RCC_CR_PLLI2SON)) |

| #define | __HAL_RCC_PLLI2S_ENABLE() (RCC->CR |= (RCC_CR_PLLI2SON)) |

| Macros to enable or disable the PLLI2S. More... | |

| #define | __HAL_RCC_PWR_CLK_DISABLE() (RCC->APB1ENR &= ~(RCC_APB1ENR_PWREN)) |

| #define | __HAL_RCC_PWR_CLK_ENABLE() |

| #define | __HAL_RCC_PWR_CLK_SLEEP_DISABLE() (RCC->APB1LPENR &= ~(RCC_APB1LPENR_PWRLPEN)) |

| #define | __HAL_RCC_PWR_CLK_SLEEP_ENABLE() (RCC->APB1LPENR |= (RCC_APB1LPENR_PWRLPEN)) |

| #define | __HAL_RCC_PWR_FORCE_RESET() (RCC->APB1RSTR |= (RCC_APB1RSTR_PWRRST)) |

| #define | __HAL_RCC_PWR_IS_CLK_DISABLED() ((RCC->APB1ENR & (RCC_APB1ENR_PWREN)) == RESET) |

| #define | __HAL_RCC_PWR_IS_CLK_ENABLED() ((RCC->APB1ENR & (RCC_APB1ENR_PWREN)) != RESET) |

| #define | __HAL_RCC_PWR_IS_CLK_SLEEP_DISABLED() ((RCC->APB1LPENR & (RCC_APB1LPENR_PWRLPEN)) == RESET) |

| #define | __HAL_RCC_PWR_IS_CLK_SLEEP_ENABLED() ((RCC->APB1LPENR & (RCC_APB1LPENR_PWRLPEN)) != RESET) |

| #define | __HAL_RCC_PWR_RELEASE_RESET() (RCC->APB1RSTR &= ~(RCC_APB1RSTR_PWRRST)) |

| #define | __HAL_RCC_RTC_CLKPRESCALER(__RTCCLKSource__) |

| Macros to configure the RTC clock (RTCCLK). More... | |

| #define | __HAL_RCC_RTC_CONFIG(__RTCCLKSource__) |

| #define | __HAL_RCC_RTC_DISABLE() (RCC->BDCR &= ~(RCC_BDCR_RTCEN)) |

| #define | __HAL_RCC_RTC_ENABLE() (RCC->BDCR |= (RCC_BDCR_RTCEN)) |

| Macros to enable or disable the RTC clock. More... | |

| #define | __HAL_RCC_SYSCFG_CLK_DISABLE() (RCC->APB2ENR &= ~(RCC_APB2ENR_SYSCFGEN)) |

| #define | __HAL_RCC_SYSCFG_CLK_ENABLE() |

| #define | __HAL_RCC_SYSCFG_CLK_SLEEP_DISABLE() (RCC->APB2LPENR &= ~(RCC_APB2LPENR_SYSCFGLPEN)) |

| #define | __HAL_RCC_SYSCFG_CLK_SLEEP_ENABLE() (RCC->APB2LPENR |= (RCC_APB2LPENR_SYSCFGLPEN)) |

| Enable or disable the APB2 peripheral clock during Low Power (Sleep) mode. More... | |

| #define | __HAL_RCC_SYSCFG_FORCE_RESET() (RCC->APB2RSTR |= (RCC_APB2RSTR_SYSCFGRST)) |

| #define | __HAL_RCC_SYSCFG_IS_CLK_DISABLED() ((RCC->APB2ENR & (RCC_APB2ENR_SYSCFGEN)) == RESET) |

| #define | __HAL_RCC_SYSCFG_IS_CLK_ENABLED() ((RCC->APB2ENR & (RCC_APB2ENR_SYSCFGEN)) != RESET) |

| #define | __HAL_RCC_SYSCFG_IS_CLK_SLEEP_DISABLED() ((RCC->APB2LPENR & (RCC_APB2LPENR_SYSCFGLPEN)) == RESET) |

| #define | __HAL_RCC_SYSCFG_IS_CLK_SLEEP_ENABLED() ((RCC->APB2LPENR & (RCC_APB2LPENR_SYSCFGLPEN)) != RESET) |

| #define | __HAL_RCC_SYSCFG_RELEASE_RESET() (RCC->APB2RSTR &= ~(RCC_APB2RSTR_SYSCFGRST)) |

| #define | __HAL_RCC_SYSCLK_CONFIG(__RCC_SYSCLKSOURCE__) MODIFY_REG(RCC->CFGR, RCC_CFGR_SW, (__RCC_SYSCLKSOURCE__)) |

| Macro to configure the system clock source. More... | |

| #define | __HAL_RCC_WWDG_CLK_DISABLE() (RCC->APB1ENR &= ~(RCC_APB1ENR_WWDGEN)) |

| #define | __HAL_RCC_WWDG_CLK_ENABLE() |

| #define | __HAL_RCC_WWDG_CLK_SLEEP_DISABLE() (RCC->APB1LPENR &= ~(RCC_APB1LPENR_WWDGLPEN)) |

| #define | __HAL_RCC_WWDG_CLK_SLEEP_ENABLE() (RCC->APB1LPENR |= (RCC_APB1LPENR_WWDGLPEN)) |

| Enable or disable the APB1 peripheral clock during Low Power (Sleep) mode. More... | |

| #define | __HAL_RCC_WWDG_FORCE_RESET() (RCC->APB1RSTR |= (RCC_APB1RSTR_WWDGRST)) |

| #define | __HAL_RCC_WWDG_IS_CLK_DISABLED() ((RCC->APB1ENR & (RCC_APB1ENR_WWDGEN)) == RESET) |

| #define | __HAL_RCC_WWDG_IS_CLK_ENABLED() ((RCC->APB1ENR & (RCC_APB1ENR_WWDGEN)) != RESET) |

| #define | __HAL_RCC_WWDG_IS_CLK_SLEEP_DISABLED() ((RCC->APB1LPENR & (RCC_APB1LPENR_WWDGLPEN)) == RESET) |

| #define | __HAL_RCC_WWDG_IS_CLK_SLEEP_ENABLED() ((RCC->APB1LPENR & (RCC_APB1LPENR_WWDGLPEN)) != RESET) |

| #define | __HAL_RCC_WWDG_RELEASE_RESET() (RCC->APB1RSTR &= ~(RCC_APB1RSTR_WWDGRST)) |

| #define | CLOCKSWITCH_TIMEOUT_VALUE ((uint32_t)5000) /* 5 s */ |

| #define | HSE_TIMEOUT_VALUE HSE_STARTUP_TIMEOUT |

| #define | HSI_TIMEOUT_VALUE ((uint32_t)2) /* 2 ms */ |

| #define | IS_RCC_CALIBRATION_VALUE(VALUE) ((VALUE) <= 0x1F) |

| #define | IS_RCC_CLOCKTYPE(CLK) ((1 <= (CLK)) && ((CLK) <= 15)) |

| #define | IS_RCC_HCLK(HCLK) |

| #define | IS_RCC_HSE(HSE) |

| #define | IS_RCC_HSI(HSI) (((HSI) == RCC_HSI_OFF) || ((HSI) == RCC_HSI_ON)) |

| #define | IS_RCC_LSE(LSE) |

| #define | IS_RCC_LSE_DRIVE(DRIVE) |

| #define | IS_RCC_LSI(LSI) (((LSI) == RCC_LSI_OFF) || ((LSI) == RCC_LSI_ON)) |

| #define | IS_RCC_MCO(MCOX) (((MCOX) == RCC_MCO1) || ((MCOX) == RCC_MCO2)) |

| #define | IS_RCC_MCO1SOURCE(SOURCE) |

| #define | IS_RCC_MCO2SOURCE(SOURCE) |

| #define | IS_RCC_MCODIV(DIV) |

| #define | IS_RCC_OSCILLATORTYPE(OSCILLATOR) ((OSCILLATOR) <= 15) |

| #define | IS_RCC_PCLK(PCLK) |

| #define | IS_RCC_PLL(PLL) (((PLL) == RCC_PLL_NONE) ||((PLL) == RCC_PLL_OFF) || ((PLL) == RCC_PLL_ON)) |

| #define | IS_RCC_PLLM_VALUE(VALUE) ((2 <= (VALUE)) && ((VALUE) <= 63)) |

| #define | IS_RCC_PLLN_VALUE(VALUE) ((50 <= (VALUE)) && ((VALUE) <= 432)) |

| #define | IS_RCC_PLLP_VALUE(VALUE) |

| #define | IS_RCC_PLLQ_VALUE(VALUE) ((2 <= (VALUE)) && ((VALUE) <= 15)) |

| #define | IS_RCC_PLLSOURCE(SOURCE) |

| #define | IS_RCC_RTCCLKSOURCE(SOURCE) |

| #define | IS_RCC_SYSCLKSOURCE(SOURCE) |

| #define | LSI_TIMEOUT_VALUE ((uint32_t)2) /* 2 ms */ |

| #define | PLL_TIMEOUT_VALUE ((uint32_t)2) /* 2 ms */ |

| #define | PLLI2S_TIMEOUT_VALUE 100U /* Timeout value fixed to 100 ms */ |

| #define | PLLSAI_TIMEOUT_VALUE 100U /* Timeout value fixed to 100 ms */ |

| #define | RCC_CIR_BYTE1_ADDRESS ((uint32_t)(RCC_BASE + 0x0C + 0x01)) |

| #define | RCC_CIR_BYTE2_ADDRESS ((uint32_t)(RCC_BASE + 0x0C + 0x02)) |

| #define | RCC_CLOCKTYPE_HCLK ((uint32_t)0x00000002U) |

| #define | RCC_CLOCKTYPE_PCLK1 ((uint32_t)0x00000004U) |

| #define | RCC_CLOCKTYPE_PCLK2 ((uint32_t)0x00000008U) |

| #define | RCC_CLOCKTYPE_SYSCLK ((uint32_t)0x00000001U) |

| #define | RCC_DBP_TIMEOUT_VALUE ((uint32_t)100) |

| #define | RCC_FLAG_BORRST ((uint8_t)0x79U) |

| #define | RCC_FLAG_HSERDY ((uint8_t)0x31U) |

| #define | RCC_FLAG_HSIRDY ((uint8_t)0x21U) |

| #define | RCC_FLAG_IWDGRST ((uint8_t)0x7DU) |

| #define | RCC_FLAG_LPWRRST ((uint8_t)0x7FU) |

| #define | RCC_FLAG_LSERDY ((uint8_t)0x41U) |

| #define | RCC_FLAG_LSIRDY ((uint8_t)0x61U) |

| #define | RCC_FLAG_MASK ((uint8_t)0x1F) |

| Check RCC flag is set or not. More... | |

| #define | RCC_FLAG_PINRST ((uint8_t)0x7AU) |

| #define | RCC_FLAG_PLLI2SRDY ((uint8_t)0x3BU) |

| #define | RCC_FLAG_PLLRDY ((uint8_t)0x39U) |

| #define | RCC_FLAG_PLLSAIRDY ((uint8_t)0x3CU) |

| #define | RCC_FLAG_PORRST ((uint8_t)0x7BU) |

| #define | RCC_FLAG_SFTRST ((uint8_t)0x7CU) |

| #define | RCC_FLAG_WWDGRST ((uint8_t)0x7EU) |

| #define | RCC_HCLK_DIV1 RCC_CFGR_PPRE1_DIV1 |

| #define | RCC_HCLK_DIV16 RCC_CFGR_PPRE1_DIV16 |

| #define | RCC_HCLK_DIV2 RCC_CFGR_PPRE1_DIV2 |

| #define | RCC_HCLK_DIV4 RCC_CFGR_PPRE1_DIV4 |

| #define | RCC_HCLK_DIV8 RCC_CFGR_PPRE1_DIV8 |

| #define | RCC_HSE_BYPASS ((uint32_t)(RCC_CR_HSEBYP | RCC_CR_HSEON)) |

| #define | RCC_HSE_OFF ((uint32_t)0x00000000U) |

| #define | RCC_HSE_ON RCC_CR_HSEON |

| #define | RCC_HSI_OFF ((uint32_t)0x00000000U) |

| #define | RCC_HSI_ON RCC_CR_HSION |

| #define | RCC_HSICALIBRATION_DEFAULT ((uint32_t)0x10U) /* Default HSI calibration trimming value */ |

| #define | RCC_IT_CSS ((uint8_t)0x80U) |

| #define | RCC_IT_HSERDY ((uint8_t)0x08U) |

| #define | RCC_IT_HSIRDY ((uint8_t)0x04U) |

| #define | RCC_IT_LSERDY ((uint8_t)0x02U) |

| #define | RCC_IT_LSIRDY ((uint8_t)0x01U) |

| #define | RCC_IT_PLLI2SRDY ((uint8_t)0x20U) |

| #define | RCC_IT_PLLRDY ((uint8_t)0x10U) |

| #define | RCC_IT_PLLSAIRDY ((uint8_t)0x40U) |

| #define | RCC_LSE_BYPASS ((uint32_t)(RCC_BDCR_LSEBYP | RCC_BDCR_LSEON)) |

| #define | RCC_LSE_OFF ((uint32_t)0x00000000U) |

| #define | RCC_LSE_ON RCC_BDCR_LSEON |

| #define | RCC_LSE_TIMEOUT_VALUE LSE_STARTUP_TIMEOUT |

| #define | RCC_LSEDRIVE_HIGH RCC_BDCR_LSEDRV |

| #define | RCC_LSEDRIVE_LOW ((uint32_t)0x00000000U) |

| #define | RCC_LSEDRIVE_MEDIUMHIGH RCC_BDCR_LSEDRV_0 |

| #define | RCC_LSEDRIVE_MEDIUMLOW RCC_BDCR_LSEDRV_1 |

| #define | RCC_LSI_OFF ((uint32_t)0x00000000U) |

| #define | RCC_LSI_ON RCC_CSR_LSION |

| #define | RCC_MCO1 ((uint32_t)0x00000000U) |

| #define | RCC_MCO1SOURCE_HSE RCC_CFGR_MCO1_1 |

| #define | RCC_MCO1SOURCE_HSI ((uint32_t)0x00000000U) |

| #define | RCC_MCO1SOURCE_LSE RCC_CFGR_MCO1_0 |

| #define | RCC_MCO1SOURCE_PLLCLK RCC_CFGR_MCO1 |

| #define | RCC_MCO2 ((uint32_t)0x00000001U) |

| #define | RCC_MCO2SOURCE_HSE RCC_CFGR_MCO2_1 |

| #define | RCC_MCO2SOURCE_PLLCLK RCC_CFGR_MCO2 |

| #define | RCC_MCO2SOURCE_PLLI2SCLK RCC_CFGR_MCO2_0 |

| #define | RCC_MCO2SOURCE_SYSCLK ((uint32_t)0x00000000U) |

| #define | RCC_MCODIV_1 ((uint32_t)0x00000000U) |

| #define | RCC_MCODIV_2 RCC_CFGR_MCO1PRE_2 |

| #define | RCC_MCODIV_3 ((uint32_t)RCC_CFGR_MCO1PRE_0 | RCC_CFGR_MCO1PRE_2) |

| #define | RCC_MCODIV_4 ((uint32_t)RCC_CFGR_MCO1PRE_1 | RCC_CFGR_MCO1PRE_2) |

| #define | RCC_MCODIV_5 RCC_CFGR_MCO1PRE |

| #define | RCC_OSCILLATORTYPE_HSE ((uint32_t)0x00000001U) |

| #define | RCC_OSCILLATORTYPE_HSI ((uint32_t)0x00000002U) |

| #define | RCC_OSCILLATORTYPE_LSE ((uint32_t)0x00000004U) |

| #define | RCC_OSCILLATORTYPE_LSI ((uint32_t)0x00000008U) |

| #define | RCC_OSCILLATORTYPE_NONE ((uint32_t)0x00000000U) |

| #define | RCC_PLL_NONE ((uint32_t)0x00000000U) |

| #define | RCC_PLL_OFF ((uint32_t)0x00000001U) |

| #define | RCC_PLL_ON ((uint32_t)0x00000002U) |

| #define | RCC_PLLP_DIV2 ((uint32_t)0x00000002U) |

| #define | RCC_PLLP_DIV4 ((uint32_t)0x00000004U) |

| #define | RCC_PLLP_DIV6 ((uint32_t)0x00000006U) |

| #define | RCC_PLLP_DIV8 ((uint32_t)0x00000008U) |

| #define | RCC_PLLSOURCE_HSE RCC_PLLCFGR_PLLSRC_HSE |

| #define | RCC_PLLSOURCE_HSI RCC_PLLCFGR_PLLSRC_HSI |

| #define | RCC_RTCCLKSOURCE_HSE_DIV10 ((uint32_t)0x000A0300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV11 ((uint32_t)0x000B0300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV12 ((uint32_t)0x000C0300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV13 ((uint32_t)0x000D0300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV14 ((uint32_t)0x000E0300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV15 ((uint32_t)0x000F0300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV16 ((uint32_t)0x00100300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV17 ((uint32_t)0x00110300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV18 ((uint32_t)0x00120300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV19 ((uint32_t)0x00130300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV2 ((uint32_t)0x00020300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV20 ((uint32_t)0x00140300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV21 ((uint32_t)0x00150300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV22 ((uint32_t)0x00160300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV23 ((uint32_t)0x00170300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV24 ((uint32_t)0x00180300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV25 ((uint32_t)0x00190300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV26 ((uint32_t)0x001A0300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV27 ((uint32_t)0x001B0300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV28 ((uint32_t)0x001C0300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV29 ((uint32_t)0x001D0300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV3 ((uint32_t)0x00030300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV30 ((uint32_t)0x001E0300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV31 ((uint32_t)0x001F0300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV4 ((uint32_t)0x00040300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV5 ((uint32_t)0x00050300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV6 ((uint32_t)0x00060300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV7 ((uint32_t)0x00070300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV8 ((uint32_t)0x00080300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIV9 ((uint32_t)0x00090300U) |

| #define | RCC_RTCCLKSOURCE_HSE_DIVX ((uint32_t)0x00000300U) |

| #define | RCC_RTCCLKSOURCE_LSE ((uint32_t)0x00000100U) |

| #define | RCC_RTCCLKSOURCE_LSI ((uint32_t)0x00000200U) |

| #define | RCC_RTCCLKSOURCE_NO_CLK ((uint32_t)0x00000000U) |

| #define | RCC_SYSCLK_DIV1 RCC_CFGR_HPRE_DIV1 |

| #define | RCC_SYSCLK_DIV128 RCC_CFGR_HPRE_DIV128 |

| #define | RCC_SYSCLK_DIV16 RCC_CFGR_HPRE_DIV16 |

| #define | RCC_SYSCLK_DIV2 RCC_CFGR_HPRE_DIV2 |

| #define | RCC_SYSCLK_DIV256 RCC_CFGR_HPRE_DIV256 |

| #define | RCC_SYSCLK_DIV4 RCC_CFGR_HPRE_DIV4 |

| #define | RCC_SYSCLK_DIV512 RCC_CFGR_HPRE_DIV512 |

| #define | RCC_SYSCLK_DIV64 RCC_CFGR_HPRE_DIV64 |

| #define | RCC_SYSCLK_DIV8 RCC_CFGR_HPRE_DIV8 |

| #define | RCC_SYSCLKSOURCE_HSE RCC_CFGR_SW_HSE |

| #define | RCC_SYSCLKSOURCE_HSI RCC_CFGR_SW_HSI |

| #define | RCC_SYSCLKSOURCE_PLLCLK RCC_CFGR_SW_PLL |

| #define | RCC_SYSCLKSOURCE_STATUS_HSE RCC_CFGR_SWS_HSE |

| #define | RCC_SYSCLKSOURCE_STATUS_HSI RCC_CFGR_SWS_HSI |

| #define | RCC_SYSCLKSOURCE_STATUS_PLLCLK RCC_CFGR_SWS_PLL |

Functions | |

| HAL_StatusTypeDef | HAL_RCC_ClockConfig (RCC_ClkInitTypeDef *RCC_ClkInitStruct, uint32_t FLatency) |

| void | HAL_RCC_CSSCallback (void) |

| HAL_StatusTypeDef | HAL_RCC_DeInit (void) |

| void | HAL_RCC_DisableCSS (void) |

| void | HAL_RCC_EnableCSS (void) |

| void | HAL_RCC_GetClockConfig (RCC_ClkInitTypeDef *RCC_ClkInitStruct, uint32_t *pFLatency) |

| uint32_t | HAL_RCC_GetHCLKFreq (void) |

| void | HAL_RCC_GetOscConfig (RCC_OscInitTypeDef *RCC_OscInitStruct) |

| uint32_t | HAL_RCC_GetPCLK1Freq (void) |

| uint32_t | HAL_RCC_GetPCLK2Freq (void) |

| uint32_t | HAL_RCC_GetSysClockFreq (void) |

| void | HAL_RCC_MCOConfig (uint32_t RCC_MCOx, uint32_t RCC_MCOSource, uint32_t RCC_MCODiv) |

| void | HAL_RCC_NMI_IRQHandler (void) |

| HAL_StatusTypeDef | HAL_RCC_OscConfig (RCC_OscInitTypeDef *RCC_OscInitStruct) |

Detailed Description

Header file of RCC HAL module.

- Attention

© Copyright (c) 2017 STMicroelectronics. All rights reserved.

This software component is licensed by ST under BSD 3-Clause license, the "License"; You may not use this file except in compliance with the License. You may obtain a copy of the License at: opensource.org/licenses/BSD-3-Clause

Definition in file stm32f7xx_hal_rcc.h.