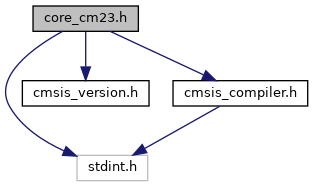

CMSIS Cortex-M23 Core Peripheral Access Layer Header File. More...

Go to the source code of this file.

Classes | |

| union | APSR_Type |

| Union type to access the Application Program Status Register (APSR). More... | |

| union | CONTROL_Type |

| Union type to access the Control Registers (CONTROL). More... | |

| struct | CoreDebug_Type |

| Structure type to access the Core Debug Register (CoreDebug). More... | |

| struct | DWT_Type |

| Structure type to access the Data Watchpoint and Trace Register (DWT). More... | |

| union | IPSR_Type |

| Union type to access the Interrupt Program Status Register (IPSR). More... | |

| struct | NVIC_Type |

| Structure type to access the Nested Vectored Interrupt Controller (NVIC). More... | |

| struct | SCB_Type |

| Structure type to access the System Control Block (SCB). More... | |

| struct | SysTick_Type |

| Structure type to access the System Timer (SysTick). More... | |

| struct | TPI_Type |

| Structure type to access the Trace Port Interface Register (TPI). More... | |

| union | xPSR_Type |

| Union type to access the Special-Purpose Program Status Registers (xPSR). More... | |

Detailed Description

CMSIS Cortex-M23 Core Peripheral Access Layer Header File.

- Version

- V5.0.7

- Date

- 22. June 2018

Definition in file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

Macro Definition Documentation

◆ __CM23_CMSIS_VERSION

| #define __CM23_CMSIS_VERSION |

- Deprecated:

- CMSIS HAL version number

Definition at line 68 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ __CM23_CMSIS_VERSION_MAIN

| #define __CM23_CMSIS_VERSION_MAIN (__CM_CMSIS_VERSION_MAIN) |

- Deprecated:

- [31:16] CMSIS HAL main version

Definition at line 66 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ __CM23_CMSIS_VERSION_SUB

| #define __CM23_CMSIS_VERSION_SUB (__CM_CMSIS_VERSION_SUB) |

- Deprecated:

- [15:0] CMSIS HAL sub version

Definition at line 67 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ __CORE_CM23_H_DEPENDANT

| #define __CORE_CM23_H_DEPENDANT |

Definition at line 127 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ __CORE_CM23_H_GENERIC

| #define __CORE_CM23_H_GENERIC |

Definition at line 32 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ __CORTEX_M

| #define __CORTEX_M (23U) |

Cortex-M Core

Definition at line 71 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ __FPU_USED

| #define __FPU_USED 0U |

__FPU_USED indicates whether an FPU is used or not. This core does not support an FPU at all

Definition at line 76 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ __I

| #define __I volatile const |

Defines 'read only' permissions

Definition at line 193 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ __IM

| #define __IM volatile const /*! Defines 'read only' structure member permissions */ |

Definition at line 199 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ __IO

| #define __IO volatile |

Defines 'read / write' permissions

Definition at line 196 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ __IOM

| #define __IOM volatile /*! Defines 'read / write' structure member permissions */ |

Definition at line 201 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ __O

| #define __O volatile |

Defines 'write only' permissions

Definition at line 195 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ __OM

| #define __OM volatile /*! Defines 'write only' structure member permissions */ |

Definition at line 200 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.