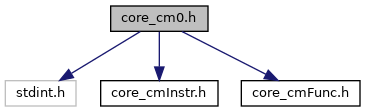

CMSIS Cortex-M0 Core Peripheral Access Layer Header File. More...

Go to the source code of this file.

Classes | |

| union | APSR_Type |

| Union type to access the Application Program Status Register (APSR). More... | |

| union | CONTROL_Type |

| Union type to access the Control Registers (CONTROL). More... | |

| union | IPSR_Type |

| Union type to access the Interrupt Program Status Register (IPSR). More... | |

| struct | NVIC_Type |

| Structure type to access the Nested Vectored Interrupt Controller (NVIC). More... | |

| struct | SCB_Type |

| Structure type to access the System Control Block (SCB). More... | |

| struct | SysTick_Type |

| Structure type to access the System Timer (SysTick). More... | |

| union | xPSR_Type |

| Union type to access the Special-Purpose Program Status Registers (xPSR). More... | |

Detailed Description

CMSIS Cortex-M0 Core Peripheral Access Layer Header File.

- Version

- V3.01

- Date

- 13. March 2012

- Note

- Copyright (C) 2009-2012 ARM Limited. All rights reserved.

- ARM Limited (ARM) is supplying this software for use with Cortex-M processor based microcontrollers. This file can be freely distributed within development tools that are supporting such ARM based processors.

- THIS SOFTWARE IS PROVIDED "AS IS". NO WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE APPLY TO THIS SOFTWARE. ARM SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.

Definition in file core_cm0.h.

Macro Definition Documentation

◆ __CM0_CMSIS_VERSION

| #define __CM0_CMSIS_VERSION |

CMSIS HAL version number

Definition at line 58 of file core_cm0.h.

◆ __CM0_CMSIS_VERSION_MAIN

| #define __CM0_CMSIS_VERSION_MAIN (0x03) |

[31:16] CMSIS HAL main version

Definition at line 56 of file core_cm0.h.

◆ __CM0_CMSIS_VERSION_SUB

| #define __CM0_CMSIS_VERSION_SUB (0x01) |

[15:0] CMSIS HAL sub version

Definition at line 57 of file core_cm0.h.

◆ __CORE_CM0_H_DEPENDANT

| #define __CORE_CM0_H_DEPENDANT |

Definition at line 120 of file core_cm0.h.

◆ __CORE_CM0_H_GENERIC

| #define __CORE_CM0_H_GENERIC |

Definition at line 32 of file core_cm0.h.

◆ __CORTEX_M

| #define __CORTEX_M (0x00) |

Cortex-M Core

Definition at line 61 of file core_cm0.h.

◆ __FPU_USED

| #define __FPU_USED 0 |

__FPU_USED indicates whether an FPU is used or not. This core does not support an FPU at all

Definition at line 88 of file core_cm0.h.

◆ __I

| #define __I volatile const |

Defines 'read only' permissions

Definition at line 151 of file core_cm0.h.

◆ __IO

| #define __IO volatile |

Defines 'read / write' permissions

Definition at line 154 of file core_cm0.h.

◆ __O

| #define __O volatile |

Defines 'write only' permissions

Definition at line 153 of file core_cm0.h.