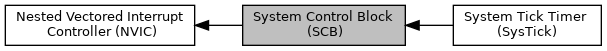

Type definitions for the System Control Block Registers. More...

Modules | |

| System Tick Timer (SysTick) | |

| Type definitions for the System Timer Registers. | |

Detailed Description

Type definitions for the System Control Block Registers.

Macro Definition Documentation

◆ SCB_AIRCR_ENDIANESS_Msk

| #define SCB_AIRCR_ENDIANESS_Msk (1UL << SCB_AIRCR_ENDIANESS_Pos) |

SCB AIRCR: ENDIANESS Mask

Definition at line 355 of file core_cm0.h.

◆ SCB_AIRCR_ENDIANESS_Pos

| #define SCB_AIRCR_ENDIANESS_Pos 15 |

SCB AIRCR: ENDIANESS Position

Definition at line 354 of file core_cm0.h.

◆ SCB_AIRCR_SYSRESETREQ_Msk

| #define SCB_AIRCR_SYSRESETREQ_Msk (1UL << SCB_AIRCR_SYSRESETREQ_Pos) |

SCB AIRCR: SYSRESETREQ Mask

Definition at line 358 of file core_cm0.h.

◆ SCB_AIRCR_SYSRESETREQ_Pos

| #define SCB_AIRCR_SYSRESETREQ_Pos 2 |

SCB AIRCR: SYSRESETREQ Position

Definition at line 357 of file core_cm0.h.

◆ SCB_AIRCR_VECTCLRACTIVE_Msk

| #define SCB_AIRCR_VECTCLRACTIVE_Msk (1UL << SCB_AIRCR_VECTCLRACTIVE_Pos) |

SCB AIRCR: VECTCLRACTIVE Mask

Definition at line 361 of file core_cm0.h.

◆ SCB_AIRCR_VECTCLRACTIVE_Pos

| #define SCB_AIRCR_VECTCLRACTIVE_Pos 1 |

SCB AIRCR: VECTCLRACTIVE Position

Definition at line 360 of file core_cm0.h.

◆ SCB_AIRCR_VECTKEY_Msk

| #define SCB_AIRCR_VECTKEY_Msk (0xFFFFUL << SCB_AIRCR_VECTKEY_Pos) |

SCB AIRCR: VECTKEY Mask

Definition at line 349 of file core_cm0.h.

◆ SCB_AIRCR_VECTKEY_Pos

| #define SCB_AIRCR_VECTKEY_Pos 16 |

SCB AIRCR: VECTKEY Position

Definition at line 348 of file core_cm0.h.

◆ SCB_AIRCR_VECTKEYSTAT_Msk

| #define SCB_AIRCR_VECTKEYSTAT_Msk (0xFFFFUL << SCB_AIRCR_VECTKEYSTAT_Pos) |

SCB AIRCR: VECTKEYSTAT Mask

Definition at line 352 of file core_cm0.h.

◆ SCB_AIRCR_VECTKEYSTAT_Pos

| #define SCB_AIRCR_VECTKEYSTAT_Pos 16 |

SCB AIRCR: VECTKEYSTAT Position

Definition at line 351 of file core_cm0.h.

◆ SCB_CCR_STKALIGN_Msk

| #define SCB_CCR_STKALIGN_Msk (1UL << SCB_CCR_STKALIGN_Pos) |

SCB CCR: STKALIGN Mask

Definition at line 375 of file core_cm0.h.

◆ SCB_CCR_STKALIGN_Pos

| #define SCB_CCR_STKALIGN_Pos 9 |

SCB CCR: STKALIGN Position

Definition at line 374 of file core_cm0.h.

◆ SCB_CCR_UNALIGN_TRP_Msk

| #define SCB_CCR_UNALIGN_TRP_Msk (1UL << SCB_CCR_UNALIGN_TRP_Pos) |

SCB CCR: UNALIGN_TRP Mask

Definition at line 378 of file core_cm0.h.

◆ SCB_CCR_UNALIGN_TRP_Pos

| #define SCB_CCR_UNALIGN_TRP_Pos 3 |

SCB CCR: UNALIGN_TRP Position

Definition at line 377 of file core_cm0.h.

◆ SCB_CPUID_ARCHITECTURE_Msk

| #define SCB_CPUID_ARCHITECTURE_Msk (0xFUL << SCB_CPUID_ARCHITECTURE_Pos) |

SCB CPUID: ARCHITECTURE Mask

Definition at line 311 of file core_cm0.h.

◆ SCB_CPUID_ARCHITECTURE_Pos

| #define SCB_CPUID_ARCHITECTURE_Pos 16 |

SCB CPUID: ARCHITECTURE Position

Definition at line 310 of file core_cm0.h.

◆ SCB_CPUID_IMPLEMENTER_Msk

| #define SCB_CPUID_IMPLEMENTER_Msk (0xFFUL << SCB_CPUID_IMPLEMENTER_Pos) |

SCB CPUID: IMPLEMENTER Mask

Definition at line 305 of file core_cm0.h.

◆ SCB_CPUID_IMPLEMENTER_Pos

| #define SCB_CPUID_IMPLEMENTER_Pos 24 |

SCB CPUID: IMPLEMENTER Position

Definition at line 304 of file core_cm0.h.

◆ SCB_CPUID_PARTNO_Msk

| #define SCB_CPUID_PARTNO_Msk (0xFFFUL << SCB_CPUID_PARTNO_Pos) |

SCB CPUID: PARTNO Mask

Definition at line 314 of file core_cm0.h.

◆ SCB_CPUID_PARTNO_Pos

| #define SCB_CPUID_PARTNO_Pos 4 |

SCB CPUID: PARTNO Position

Definition at line 313 of file core_cm0.h.

◆ SCB_CPUID_REVISION_Msk

| #define SCB_CPUID_REVISION_Msk (0xFUL << SCB_CPUID_REVISION_Pos) |

SCB CPUID: REVISION Mask

Definition at line 317 of file core_cm0.h.

◆ SCB_CPUID_REVISION_Pos

| #define SCB_CPUID_REVISION_Pos 0 |

SCB CPUID: REVISION Position

Definition at line 316 of file core_cm0.h.

◆ SCB_CPUID_VARIANT_Msk

| #define SCB_CPUID_VARIANT_Msk (0xFUL << SCB_CPUID_VARIANT_Pos) |

SCB CPUID: VARIANT Mask

Definition at line 308 of file core_cm0.h.

◆ SCB_CPUID_VARIANT_Pos

| #define SCB_CPUID_VARIANT_Pos 20 |

SCB CPUID: VARIANT Position

Definition at line 307 of file core_cm0.h.

◆ SCB_ICSR_ISRPENDING_Msk

| #define SCB_ICSR_ISRPENDING_Msk (1UL << SCB_ICSR_ISRPENDING_Pos) |

SCB ICSR: ISRPENDING Mask

Definition at line 339 of file core_cm0.h.

◆ SCB_ICSR_ISRPENDING_Pos

| #define SCB_ICSR_ISRPENDING_Pos 22 |

SCB ICSR: ISRPENDING Position

Definition at line 338 of file core_cm0.h.

◆ SCB_ICSR_ISRPREEMPT_Msk

| #define SCB_ICSR_ISRPREEMPT_Msk (1UL << SCB_ICSR_ISRPREEMPT_Pos) |

SCB ICSR: ISRPREEMPT Mask

Definition at line 336 of file core_cm0.h.

◆ SCB_ICSR_ISRPREEMPT_Pos

| #define SCB_ICSR_ISRPREEMPT_Pos 23 |

SCB ICSR: ISRPREEMPT Position

Definition at line 335 of file core_cm0.h.

◆ SCB_ICSR_NMIPENDSET_Msk

| #define SCB_ICSR_NMIPENDSET_Msk (1UL << SCB_ICSR_NMIPENDSET_Pos) |

SCB ICSR: NMIPENDSET Mask

Definition at line 321 of file core_cm0.h.

◆ SCB_ICSR_NMIPENDSET_Pos

| #define SCB_ICSR_NMIPENDSET_Pos 31 |

SCB ICSR: NMIPENDSET Position

Definition at line 320 of file core_cm0.h.

◆ SCB_ICSR_PENDSTCLR_Msk

| #define SCB_ICSR_PENDSTCLR_Msk (1UL << SCB_ICSR_PENDSTCLR_Pos) |

SCB ICSR: PENDSTCLR Mask

Definition at line 333 of file core_cm0.h.

◆ SCB_ICSR_PENDSTCLR_Pos

| #define SCB_ICSR_PENDSTCLR_Pos 25 |

SCB ICSR: PENDSTCLR Position

Definition at line 332 of file core_cm0.h.

◆ SCB_ICSR_PENDSTSET_Msk

| #define SCB_ICSR_PENDSTSET_Msk (1UL << SCB_ICSR_PENDSTSET_Pos) |

SCB ICSR: PENDSTSET Mask

Definition at line 330 of file core_cm0.h.

◆ SCB_ICSR_PENDSTSET_Pos

| #define SCB_ICSR_PENDSTSET_Pos 26 |

SCB ICSR: PENDSTSET Position

Definition at line 329 of file core_cm0.h.

◆ SCB_ICSR_PENDSVCLR_Msk

| #define SCB_ICSR_PENDSVCLR_Msk (1UL << SCB_ICSR_PENDSVCLR_Pos) |

SCB ICSR: PENDSVCLR Mask

Definition at line 327 of file core_cm0.h.

◆ SCB_ICSR_PENDSVCLR_Pos

| #define SCB_ICSR_PENDSVCLR_Pos 27 |

SCB ICSR: PENDSVCLR Position

Definition at line 326 of file core_cm0.h.

◆ SCB_ICSR_PENDSVSET_Msk

| #define SCB_ICSR_PENDSVSET_Msk (1UL << SCB_ICSR_PENDSVSET_Pos) |

SCB ICSR: PENDSVSET Mask

Definition at line 324 of file core_cm0.h.

◆ SCB_ICSR_PENDSVSET_Pos

| #define SCB_ICSR_PENDSVSET_Pos 28 |

SCB ICSR: PENDSVSET Position

Definition at line 323 of file core_cm0.h.

◆ SCB_ICSR_VECTACTIVE_Msk

| #define SCB_ICSR_VECTACTIVE_Msk (0x1FFUL << SCB_ICSR_VECTACTIVE_Pos) |

SCB ICSR: VECTACTIVE Mask

Definition at line 345 of file core_cm0.h.

◆ SCB_ICSR_VECTACTIVE_Pos

| #define SCB_ICSR_VECTACTIVE_Pos 0 |

SCB ICSR: VECTACTIVE Position

Definition at line 344 of file core_cm0.h.

◆ SCB_ICSR_VECTPENDING_Msk

| #define SCB_ICSR_VECTPENDING_Msk (0x1FFUL << SCB_ICSR_VECTPENDING_Pos) |

SCB ICSR: VECTPENDING Mask

Definition at line 342 of file core_cm0.h.

◆ SCB_ICSR_VECTPENDING_Pos

| #define SCB_ICSR_VECTPENDING_Pos 12 |

SCB ICSR: VECTPENDING Position

Definition at line 341 of file core_cm0.h.

◆ SCB_SCR_SEVONPEND_Msk

| #define SCB_SCR_SEVONPEND_Msk (1UL << SCB_SCR_SEVONPEND_Pos) |

SCB SCR: SEVONPEND Mask

Definition at line 365 of file core_cm0.h.

◆ SCB_SCR_SEVONPEND_Pos

| #define SCB_SCR_SEVONPEND_Pos 4 |

SCB SCR: SEVONPEND Position

Definition at line 364 of file core_cm0.h.

◆ SCB_SCR_SLEEPDEEP_Msk

| #define SCB_SCR_SLEEPDEEP_Msk (1UL << SCB_SCR_SLEEPDEEP_Pos) |

SCB SCR: SLEEPDEEP Mask

Definition at line 368 of file core_cm0.h.

◆ SCB_SCR_SLEEPDEEP_Pos

| #define SCB_SCR_SLEEPDEEP_Pos 2 |

SCB SCR: SLEEPDEEP Position

Definition at line 367 of file core_cm0.h.

◆ SCB_SCR_SLEEPONEXIT_Msk

| #define SCB_SCR_SLEEPONEXIT_Msk (1UL << SCB_SCR_SLEEPONEXIT_Pos) |

SCB SCR: SLEEPONEXIT Mask

Definition at line 371 of file core_cm0.h.

◆ SCB_SCR_SLEEPONEXIT_Pos

| #define SCB_SCR_SLEEPONEXIT_Pos 1 |

SCB SCR: SLEEPONEXIT Position

Definition at line 370 of file core_cm0.h.

◆ SCB_SHCSR_SVCALLPENDED_Msk

| #define SCB_SHCSR_SVCALLPENDED_Msk (1UL << SCB_SHCSR_SVCALLPENDED_Pos) |

SCB SHCSR: SVCALLPENDED Mask

Definition at line 382 of file core_cm0.h.

◆ SCB_SHCSR_SVCALLPENDED_Pos

| #define SCB_SHCSR_SVCALLPENDED_Pos 15 |

SCB SHCSR: SVCALLPENDED Position

Definition at line 381 of file core_cm0.h.