|

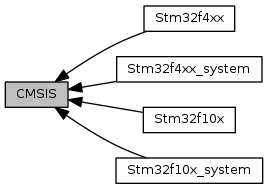

Modules | |

| Stm32f4xx_system | |

| Stm32f4xx | |

| Stm32f10x | |

| Stm32f10x_system | |

Detailed Description

Variable Documentation

| __IO uint32_t FLASH_TypeDef::ACR |

FLASH access control register, Address offset: 0x00

Definition at line 1133 of file stm32f4xx.h.

| __IO uint32_t GPIO_TypeDef::AFR[2] |

GPIO alternate function registers, Address offset: 0x20-0x24

Definition at line 1292 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::AHB1ENR |

RCC AHB1 peripheral clock register, Address offset: 0x30

Definition at line 1452 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::AHB1LPENR |

RCC AHB1 peripheral clock enable in low power mode register, Address offset: 0x50

Definition at line 1459 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::AHB1RSTR |

RCC AHB1 peripheral reset register, Address offset: 0x10

Definition at line 1445 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::AHB2ENR |

RCC AHB2 peripheral clock register, Address offset: 0x34

Definition at line 1453 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::AHB2LPENR |

RCC AHB2 peripheral clock enable in low power mode register, Address offset: 0x54

Definition at line 1460 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::AHB2RSTR |

RCC AHB2 peripheral reset register, Address offset: 0x14

Definition at line 1446 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::AHB3ENR |

RCC AHB3 peripheral clock register, Address offset: 0x38

Definition at line 1454 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::AHB3LPENR |

RCC AHB3 peripheral clock enable in low power mode register, Address offset: 0x58

Definition at line 1461 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::AHB3RSTR |

RCC AHB3 peripheral reset register, Address offset: 0x18

Definition at line 1447 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::ALRMAR |

RTC alarm A register, Address offset: 0x1C

Definition at line 1491 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::ALRMASSR |

RTC alarm A sub second register, Address offset: 0x44

Definition at line 1501 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::ALRMBR |

RTC alarm B register, Address offset: 0x20

Definition at line 1492 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::ALRMBSSR |

RTC alarm B sub second register, Address offset: 0x48

Definition at line 1502 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::AMTCR |

DMA2D AHB Master Timer Configuration Register, Address offset: 0x4C

Definition at line 950 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::APB1ENR |

RCC APB1 peripheral clock enable register, Address offset: 0x40

Definition at line 1456 of file stm32f4xx.h.

| __IO uint32_t DBGMCU_TypeDef::APB1FZ |

Debug MCU APB1 freeze register, Address offset: 0x08

Definition at line 880 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::APB1LPENR |

RCC APB1 peripheral clock enable in low power mode register, Address offset: 0x60

Definition at line 1463 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::APB1RSTR |

RCC APB1 peripheral reset register, Address offset: 0x20

Definition at line 1449 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::APB2ENR |

RCC APB2 peripheral clock enable register, Address offset: 0x44

Definition at line 1457 of file stm32f4xx.h.

| __IO uint32_t DBGMCU_TypeDef::APB2FZ |

Debug MCU APB2 freeze register, Address offset: 0x0C

Definition at line 881 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::APB2LPENR |

RCC APB2 peripheral clock enable in low power mode register, Address offset: 0x64

Definition at line 1464 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::APB2RSTR |

RCC APB2 peripheral reset register, Address offset: 0x24

Definition at line 1450 of file stm32f4xx.h.

| __IO uint32_t SDIO_TypeDef::ARG |

SDIO argument register, Address offset: 0x08

Definition at line 1556 of file stm32f4xx.h.

| __IO uint32_t TIM_TypeDef::ARR |

TIM auto-reload register, Address offset: 0x2C

Definition at line 1689 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::AWCR |

LTDC Active Width Configuration Register, Address offset: 0x10

Definition at line 1386 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::BCCR |

LTDC Background Color Configuration Register, Address offset: 0x2C

Definition at line 1392 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::BDCR |

RCC Backup domain control register, Address offset: 0x70

Definition at line 1466 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::BDTR |

TIM break and dead-time register, Address offset: 0x44

Definition at line 1696 of file stm32f4xx.h.

| __IO uint32_t LTDC_Layer_TypeDef::BFCR |

LTDC Layerx Blending Factors Configuration Register Address offset: 0xA0

Definition at line 1415 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::BGCLUT[256] |

DMA2D Background CLUT, Address offset:800-BFF

Definition at line 953 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::BGCMAR |

DMA2D Background CLUT Memory Address Register, Address offset: 0x30

Definition at line 943 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::BGCOLR |

DMA2D Background Color Register, Address offset: 0x28

Definition at line 941 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::BGMAR |

DMA2D Background Memory Address Register, Address offset: 0x14

Definition at line 936 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::BGOR |

DMA2D Background Offset Register, Address offset: 0x18

Definition at line 937 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::BGPFCCR |

DMA2D Background PFC Control Register, Address offset: 0x24

Definition at line 940 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP0R |

RTC backup register 1, Address offset: 0x50

Definition at line 1504 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP10R |

RTC backup register 10, Address offset: 0x78

Definition at line 1514 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP11R |

RTC backup register 11, Address offset: 0x7C

Definition at line 1515 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP12R |

RTC backup register 12, Address offset: 0x80

Definition at line 1516 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP13R |

RTC backup register 13, Address offset: 0x84

Definition at line 1517 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP14R |

RTC backup register 14, Address offset: 0x88

Definition at line 1518 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP15R |

RTC backup register 15, Address offset: 0x8C

Definition at line 1519 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP16R |

RTC backup register 16, Address offset: 0x90

Definition at line 1520 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP17R |

RTC backup register 17, Address offset: 0x94

Definition at line 1521 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP18R |

RTC backup register 18, Address offset: 0x98

Definition at line 1522 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP19R |

RTC backup register 19, Address offset: 0x9C

Definition at line 1523 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP1R |

RTC backup register 1, Address offset: 0x54

Definition at line 1505 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP2R |

RTC backup register 2, Address offset: 0x58

Definition at line 1506 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP3R |

RTC backup register 3, Address offset: 0x5C

Definition at line 1507 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP4R |

RTC backup register 4, Address offset: 0x60

Definition at line 1508 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP5R |

RTC backup register 5, Address offset: 0x64

Definition at line 1509 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP6R |

RTC backup register 6, Address offset: 0x68

Definition at line 1510 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP7R |

RTC backup register 7, Address offset: 0x6C

Definition at line 1511 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP8R |

RTC backup register 8, Address offset: 0x70

Definition at line 1512 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::BKP9R |

RTC backup register 9, Address offset: 0x74

Definition at line 1513 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::BPCR |

LTDC Back Porch Configuration Register, Address offset: 0x0C

Definition at line 1385 of file stm32f4xx.h.

| __IO uint16_t USART_TypeDef::BRR |

USART Baud rate register, Address offset: 0x08

Definition at line 1716 of file stm32f4xx.h.

| __IO uint16_t GPIO_TypeDef::BSRRH |

GPIO port bit set/reset high register, Address offset: 0x1A

Definition at line 1290 of file stm32f4xx.h.

| __IO uint16_t GPIO_TypeDef::BSRRL |

GPIO port bit set/reset low register, Address offset: 0x18

Definition at line 1289 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::BTR |

CAN bit timing register, Address offset: 0x1C

Definition at line 805 of file stm32f4xx.h.

| __IO uint32_t LTDC_Layer_TypeDef::CACR |

LTDC Layerx Constant Alpha Configuration Register Address offset: 0x98

Definition at line 1413 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::CALIBR |

RTC calibration register, Address offset: 0x18

Definition at line 1490 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::CALR |

RTC calibration register, Address offset: 0x3C

Definition at line 1499 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::CCER |

TIM capture/compare enable register, Address offset: 0x20

Definition at line 1684 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::CCMR1 |

TIM capture/compare mode register 1, Address offset: 0x18

Definition at line 1680 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::CCMR2 |

TIM capture/compare mode register 2, Address offset: 0x1C

Definition at line 1682 of file stm32f4xx.h.

| __IO uint32_t ADC_Common_TypeDef::CCR |

ADC common control register, Address offset: ADC1 base address + 0x304

Definition at line 752 of file stm32f4xx.h.

| __IO uint16_t I2C_TypeDef::CCR |

I2C Clock control register, Address offset: 0x1C

Definition at line 1336 of file stm32f4xx.h.

| __IO uint32_t TIM_TypeDef::CCR1 |

TIM capture/compare register 1, Address offset: 0x34

Definition at line 1692 of file stm32f4xx.h.

| __IO uint32_t TIM_TypeDef::CCR2 |

TIM capture/compare register 2, Address offset: 0x38

Definition at line 1693 of file stm32f4xx.h.

| __IO uint32_t TIM_TypeDef::CCR3 |

TIM capture/compare register 3, Address offset: 0x3C

Definition at line 1694 of file stm32f4xx.h.

| __IO uint32_t TIM_TypeDef::CCR4 |

TIM capture/compare register 4, Address offset: 0x40

Definition at line 1695 of file stm32f4xx.h.

| __IO uint32_t ADC_Common_TypeDef::CDR |

ADC common regular data register for dual AND triple modes, Address offset: ADC1 base address + 0x308

Definition at line 753 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::CDSR |

LTDC Current Display Status Register, Address offset: 0x48

Definition at line 1399 of file stm32f4xx.h.

| __IO uint32_t LTDC_Layer_TypeDef::CFBAR |

LTDC Layerx Color Frame Buffer Address Register Address offset: 0xAC

Definition at line 1417 of file stm32f4xx.h.

| __IO uint32_t LTDC_Layer_TypeDef::CFBLNR |

LTDC Layerx ColorFrame Buffer Line Number Register Address offset: 0xB4

Definition at line 1419 of file stm32f4xx.h.

| __IO uint32_t LTDC_Layer_TypeDef::CFBLR |

LTDC Layerx Color Frame Buffer Length Register Address offset: 0xB0

Definition at line 1418 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::CFGR |

RCC clock configuration register, Address offset: 0x08

Definition at line 1443 of file stm32f4xx.h.

| __IO uint32_t WWDG_TypeDef::CFR |

WWDG Configuration register, Address offset: 0x04

Definition at line 1735 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::CIR |

RCC clock interrupt register, Address offset: 0x0C

Definition at line 1444 of file stm32f4xx.h.

| __IO uint32_t LTDC_Layer_TypeDef::CKCR |

LTDC Layerx Color Keying Configuration Register Address offset: 0x90

Definition at line 1411 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::CKGATENR |

RCC Clocks Gated Enable Register, Address offset: 0x90

Definition at line 1473 of file stm32f4xx.h.

| __IO uint32_t SDIO_TypeDef::CLKCR |

SDI clock control register, Address offset: 0x04

Definition at line 1555 of file stm32f4xx.h.

| __IO uint32_t SAI_Block_TypeDef::CLRFR |

SAI block x clear flag register, Address offset: 0x1C

Definition at line 1544 of file stm32f4xx.h.

| __IO uint32_t LTDC_Layer_TypeDef::CLUTWR |

LTDC Layerx CLUT Write Register Address offset: 0x144

Definition at line 1421 of file stm32f4xx.h.

| __IO uint32_t SDIO_TypeDef::CMD |

SDIO command register, Address offset: 0x0C

Definition at line 1557 of file stm32f4xx.h.

| __IO uint32_t SYSCFG_TypeDef::CMPCR |

SYSCFG Compensation cell control register, Address offset: 0x20

Definition at line 1312 of file stm32f4xx.h.

| __IO uint32_t TIM_TypeDef::CNT |

TIM counter register, Address offset: 0x24

Definition at line 1686 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::CPSR |

LTDC Current Position Status Register, Address offset: 0x44

Definition at line 1398 of file stm32f4xx.h.

| __IO uint32_t CRC_TypeDef::CR |

CRC Control register, Address offset: 0x08

Definition at line 847 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::CR |

DAC control register, Address offset: 0x00

Definition at line 856 of file stm32f4xx.h.

| __IO uint32_t DBGMCU_TypeDef::CR |

Debug MCU configuration register, Address offset: 0x04

Definition at line 879 of file stm32f4xx.h.

| __IO uint32_t DCMI_TypeDef::CR |

DCMI control register 1, Address offset: 0x00

Definition at line 890 of file stm32f4xx.h.

| __IO uint32_t DMA_Stream_TypeDef::CR |

DMA stream x configuration register

Definition at line 909 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::CR |

DMA2D Control Register, Address offset: 0x00

Definition at line 931 of file stm32f4xx.h.

| __IO uint32_t FLASH_TypeDef::CR |

FLASH control register, Address offset: 0x10

Definition at line 1137 of file stm32f4xx.h.

| __IO uint32_t LTDC_Layer_TypeDef::CR |

LTDC Layerx Control Register Address offset: 0x84

Definition at line 1408 of file stm32f4xx.h.

| __IO uint32_t PWR_TypeDef::CR |

PWR power control register, Address offset: 0x00

Definition at line 1431 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::CR |

RCC clock control register, Address offset: 0x00

Definition at line 1441 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::CR |

RTC control register, Address offset: 0x08

Definition at line 1486 of file stm32f4xx.h.

| __IO uint32_t WWDG_TypeDef::CR |

WWDG Control register, Address offset: 0x00

Definition at line 1734 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CR |

CRYP control register, Address offset: 0x00

Definition at line 1745 of file stm32f4xx.h.

| __IO uint32_t HASH_TypeDef::CR |

HASH control register, Address offset: 0x00

Definition at line 1789 of file stm32f4xx.h.

| __IO uint32_t RNG_TypeDef::CR |

RNG control register, Address offset: 0x00

Definition at line 1814 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::CR1 |

ADC control register 1, Address offset: 0x04

Definition at line 728 of file stm32f4xx.h.

| __IO uint16_t I2C_TypeDef::CR1 |

I2C Control register 1, Address offset: 0x00

Definition at line 1322 of file stm32f4xx.h.

| __IO uint32_t SAI_Block_TypeDef::CR1 |

SAI block x configuration register 1, Address offset: 0x04

Definition at line 1538 of file stm32f4xx.h.

| __IO uint16_t SPI_TypeDef::CR1 |

SPI control register 1 (not used in I2S mode), Address offset: 0x00

Definition at line 1582 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::CR1 |

TIM control register 1, Address offset: 0x00

Definition at line 1668 of file stm32f4xx.h.

| __IO uint16_t USART_TypeDef::CR1 |

USART Control register 1, Address offset: 0x0C

Definition at line 1718 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::CR2 |

ADC control register 2, Address offset: 0x08

Definition at line 729 of file stm32f4xx.h.

| __IO uint16_t I2C_TypeDef::CR2 |

I2C Control register 2, Address offset: 0x04

Definition at line 1324 of file stm32f4xx.h.

| __IO uint32_t SAI_Block_TypeDef::CR2 |

SAI block x configuration register 2, Address offset: 0x08

Definition at line 1539 of file stm32f4xx.h.

| __IO uint16_t SPI_TypeDef::CR2 |

SPI control register 2, Address offset: 0x04

Definition at line 1584 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::CR2 |

TIM control register 2, Address offset: 0x04

Definition at line 1670 of file stm32f4xx.h.

| __IO uint16_t USART_TypeDef::CR2 |

USART Control register 2, Address offset: 0x10

Definition at line 1720 of file stm32f4xx.h.

| __IO uint16_t USART_TypeDef::CR3 |

USART Control register 3, Address offset: 0x14

Definition at line 1722 of file stm32f4xx.h.

| __IO uint16_t SPI_TypeDef::CRCPR |

SPI CRC polynomial register (not used in I2S mode), Address offset: 0x10

Definition at line 1590 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCM0R |

CRYP GCM/GMAC context swap register 0, Address offset: 0x70

Definition at line 1773 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCM1R |

CRYP GCM/GMAC context swap register 1, Address offset: 0x74

Definition at line 1774 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCM2R |

CRYP GCM/GMAC context swap register 2, Address offset: 0x78

Definition at line 1775 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCM3R |

CRYP GCM/GMAC context swap register 3, Address offset: 0x7C

Definition at line 1776 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCM4R |

CRYP GCM/GMAC context swap register 4, Address offset: 0x80

Definition at line 1777 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCM5R |

CRYP GCM/GMAC context swap register 5, Address offset: 0x84

Definition at line 1778 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCM6R |

CRYP GCM/GMAC context swap register 6, Address offset: 0x88

Definition at line 1779 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCM7R |

CRYP GCM/GMAC context swap register 7, Address offset: 0x8C

Definition at line 1780 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCMCCM0R |

CRYP GCM/GMAC or CCM/CMAC context swap register 0, Address offset: 0x50

Definition at line 1765 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCMCCM1R |

CRYP GCM/GMAC or CCM/CMAC context swap register 1, Address offset: 0x54

Definition at line 1766 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCMCCM2R |

CRYP GCM/GMAC or CCM/CMAC context swap register 2, Address offset: 0x58

Definition at line 1767 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCMCCM3R |

CRYP GCM/GMAC or CCM/CMAC context swap register 3, Address offset: 0x5C

Definition at line 1768 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCMCCM4R |

CRYP GCM/GMAC or CCM/CMAC context swap register 4, Address offset: 0x60

Definition at line 1769 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCMCCM5R |

CRYP GCM/GMAC or CCM/CMAC context swap register 5, Address offset: 0x64

Definition at line 1770 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCMCCM6R |

CRYP GCM/GMAC or CCM/CMAC context swap register 6, Address offset: 0x68

Definition at line 1771 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::CSGCMCCM7R |

CRYP GCM/GMAC or CCM/CMAC context swap register 7, Address offset: 0x6C

Definition at line 1772 of file stm32f4xx.h.

| __IO uint32_t ADC_Common_TypeDef::CSR |

ADC Common status register, Address offset: ADC1 base address + 0x300

Definition at line 751 of file stm32f4xx.h.

| __IO uint32_t PWR_TypeDef::CSR |

PWR power control/status register, Address offset: 0x04

Definition at line 1432 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::CSR |

RCC clock control & status register, Address offset: 0x74

Definition at line 1467 of file stm32f4xx.h.

| __IO uint32_t HASH_TypeDef::CSR[54] |

HASH context swap registers, Address offset: 0x0F8-0x1CC

Definition at line 1796 of file stm32f4xx.h.

| __IO uint32_t DCMI_TypeDef::CWSIZER |

DCMI crop window size, Address offset: 0x24

Definition at line 899 of file stm32f4xx.h.

| __IO uint32_t DCMI_TypeDef::CWSTRTR |

DCMI crop window start, Address offset: 0x20

Definition at line 898 of file stm32f4xx.h.

| __IO uint32_t LTDC_Layer_TypeDef::DCCR |

LTDC Layerx Default Color Configuration Register Address offset: 0x9C

Definition at line 1414 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::DCKCFGR |

RCC Dedicated Clocks configuration register, Address offset: 0x8C

Definition at line 1472 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::DCKCFGR2 |

RCC Dedicated Clocks configuration register 2, Address offset: 0x94

Definition at line 1474 of file stm32f4xx.h.

| __I uint32_t SDIO_TypeDef::DCOUNT |

SDIO data counter register, Address offset: 0x30

Definition at line 1566 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::DCR |

TIM DMA control register, Address offset: 0x48

Definition at line 1698 of file stm32f4xx.h.

| __IO uint32_t SDIO_TypeDef::DCTRL |

SDIO data control register, Address offset: 0x2C

Definition at line 1565 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR12L1 |

DAC channel1 12-bit left aligned data holding register, Address offset: 0x0C

Definition at line 859 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR12L2 |

DAC channel2 12-bit left aligned data holding register, Address offset: 0x18

Definition at line 862 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR12LD |

DUAL DAC 12-bit left aligned data holding register, Address offset: 0x24

Definition at line 865 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR12R1 |

DAC channel1 12-bit right-aligned data holding register, Address offset: 0x08

Definition at line 858 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR12R2 |

DAC channel2 12-bit right aligned data holding register, Address offset: 0x14

Definition at line 861 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR12RD |

Dual DAC 12-bit right-aligned data holding register, Address offset: 0x20

Definition at line 864 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR8R1 |

DAC channel1 8-bit right aligned data holding register, Address offset: 0x10

Definition at line 860 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR8R2 |

DAC channel2 8-bit right-aligned data holding register, Address offset: 0x1C

Definition at line 863 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR8RD |

DUAL DAC 8-bit right aligned data holding register, Address offset: 0x28

Definition at line 866 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::DIER |

TIM DMA/interrupt enable register, Address offset: 0x0C

Definition at line 1674 of file stm32f4xx.h.

| __IO uint32_t HASH_TypeDef::DIN |

HASH data input register, Address offset: 0x04

Definition at line 1790 of file stm32f4xx.h.

| __IO uint32_t SDIO_TypeDef::DLEN |

SDIO data length register, Address offset: 0x28

Definition at line 1564 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMABMR |

Definition at line 1096 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMACHRBAR |

Definition at line 1110 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMACHRDR |

Definition at line 1108 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMACHTBAR |

Definition at line 1109 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMACHTDR |

Definition at line 1107 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::DMACR |

CRYP DMA control register, Address offset: 0x10

Definition at line 1749 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMAIER |

Definition at line 1103 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMAMFBOCR |

Definition at line 1104 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMAOMR |

Definition at line 1102 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::DMAR |

TIM DMA address for full transfer, Address offset: 0x4C

Definition at line 1700 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMARDLAR |

Definition at line 1099 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMARPDR |

Definition at line 1098 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMARSWTR |

Definition at line 1105 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMASR |

Definition at line 1101 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMATDLAR |

Definition at line 1100 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::DMATPDR |

Definition at line 1097 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DOR1 |

DAC channel1 data output register, Address offset: 0x2C

Definition at line 867 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DOR2 |

DAC channel2 data output register, Address offset: 0x30

Definition at line 868 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::DOUT |

CRYP data output register, Address offset: 0x0C

Definition at line 1748 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::DR |

ADC regular data register, Address offset: 0x4C

Definition at line 746 of file stm32f4xx.h.

| __IO uint32_t CRC_TypeDef::DR |

CRC Data register, Address offset: 0x00

Definition at line 843 of file stm32f4xx.h.

| __IO uint32_t DCMI_TypeDef::DR |

DCMI data register, Address offset: 0x28

Definition at line 900 of file stm32f4xx.h.

| __IO uint16_t I2C_TypeDef::DR |

I2C Data register, Address offset: 0x10

Definition at line 1330 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::DR |

RTC date register, Address offset: 0x04

Definition at line 1485 of file stm32f4xx.h.

| __IO uint32_t SAI_Block_TypeDef::DR |

SAI block x data register, Address offset: 0x20

Definition at line 1545 of file stm32f4xx.h.

| __IO uint16_t SPI_TypeDef::DR |

SPI data register, Address offset: 0x0C

Definition at line 1588 of file stm32f4xx.h.

| __IO uint16_t USART_TypeDef::DR |

USART Data register, Address offset: 0x04

Definition at line 1714 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::DR |

CRYP data input register, Address offset: 0x08

Definition at line 1747 of file stm32f4xx.h.

| __IO uint32_t RNG_TypeDef::DR |

RNG data register, Address offset: 0x08

Definition at line 1816 of file stm32f4xx.h.

| __IO uint32_t SDIO_TypeDef::DTIMER |

SDIO data timer register, Address offset: 0x24

Definition at line 1563 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::EGR |

TIM event generation register, Address offset: 0x14

Definition at line 1678 of file stm32f4xx.h.

| __IO uint32_t EXTI_TypeDef::EMR |

EXTI Event mask register, Address offset: 0x04

Definition at line 1120 of file stm32f4xx.h.

| __IO uint32_t DCMI_TypeDef::ESCR |

DCMI embedded synchronization code register, Address offset: 0x18

Definition at line 896 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::ESR |

CAN error status register, Address offset: 0x18

Definition at line 804 of file stm32f4xx.h.

| __IO uint32_t DCMI_TypeDef::ESUR |

DCMI embedded synchronization unmask register, Address offset: 0x1C

Definition at line 897 of file stm32f4xx.h.

| __IO uint32_t SYSCFG_TypeDef::EXTICR[4] |

SYSCFG external interrupt configuration registers, Address offset: 0x08-0x14

Definition at line 1303 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::FA1R |

CAN filter activation register, Address offset: 0x21C

Definition at line 817 of file stm32f4xx.h.

| __IO uint32_t DMA_Stream_TypeDef::FCR |

DMA stream x FIFO control register

Definition at line 914 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::FFA1R |

CAN filter FIFO assignment register, Address offset: 0x214

Definition at line 815 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::FGCLUT[256] |

DMA2D Foreground CLUT, Address offset:400-7FF

Definition at line 952 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::FGCMAR |

DMA2D Foreground CLUT Memory Address Register, Address offset: 0x2C

Definition at line 942 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::FGCOLR |

DMA2D Foreground Color Register, Address offset: 0x20

Definition at line 939 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::FGMAR |

DMA2D Foreground Memory Address Register, Address offset: 0x0C

Definition at line 934 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::FGOR |

DMA2D Foreground Offset Register, Address offset: 0x10

Definition at line 935 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::FGPFCCR |

DMA2D Foreground PFC Control Register, Address offset: 0x1C

Definition at line 938 of file stm32f4xx.h.

| __IO uint32_t SDIO_TypeDef::FIFO |

SDIO data FIFO register, Address offset: 0x80

Definition at line 1573 of file stm32f4xx.h.

| __I uint32_t SDIO_TypeDef::FIFOCNT |

SDIO FIFO counter register, Address offset: 0x48

Definition at line 1571 of file stm32f4xx.h.

| __IO uint16_t I2C_TypeDef::FLTR |

I2C FLTR register, Address offset: 0x24

Definition at line 1340 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::FM1R |

CAN filter mode register, Address offset: 0x204

Definition at line 811 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::FMR |

CAN filter master register, Address offset: 0x200

Definition at line 810 of file stm32f4xx.h.

| __IO uint32_t CAN_FilterRegister_TypeDef::FR1 |

CAN Filter bank register 1

Definition at line 788 of file stm32f4xx.h.

| __IO uint32_t CAN_FilterRegister_TypeDef::FR2 |

CAN Filter bank register 1

Definition at line 789 of file stm32f4xx.h.

| __IO uint32_t SAI_Block_TypeDef::FRCR |

SAI block x frame configuration register, Address offset: 0x0C

Definition at line 1540 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::FS1R |

CAN filter scale register, Address offset: 0x20C

Definition at line 813 of file stm32f4xx.h.

| __IO uint32_t EXTI_TypeDef::FTSR |

EXTI Falling trigger selection register, Address offset: 0x0C

Definition at line 1122 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::GCR |

LTDC Global Control Register, Address offset: 0x18

Definition at line 1388 of file stm32f4xx.h.

| __IO uint32_t SAI_TypeDef::GCR |

SAI global configuration register, Address offset: 0x00

Definition at line 1533 of file stm32f4xx.h.

| __IO uint16_t USART_TypeDef::GTPR |

USART Guard time and prescaler register, Address offset: 0x18

Definition at line 1724 of file stm32f4xx.h.

| __IO uint32_t DMA_TypeDef::HIFCR |

DMA high interrupt flag clear register, Address offset: 0x0C

Definition at line 922 of file stm32f4xx.h.

| __IO uint32_t DMA_TypeDef::HISR |

DMA high interrupt status register, Address offset: 0x04

Definition at line 920 of file stm32f4xx.h.

| __IO uint32_t HASH_TypeDef::HR[5] |

HASH digest registers, Address offset: 0x0C-0x1C

Definition at line 1792 of file stm32f4xx.h.

| __IO uint32_t HASH_DIGEST_TypeDef::HR[8] |

HASH digest registers, Address offset: 0x310-0x32C

Definition at line 1805 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::HTR |

ADC watchdog higher threshold register, Address offset: 0x24

Definition at line 736 of file stm32f4xx.h.

| __IO uint16_t SPI_TypeDef::I2SCFGR |

SPI_I2S configuration register, Address offset: 0x1C

Definition at line 1596 of file stm32f4xx.h.

| __IO uint16_t SPI_TypeDef::I2SPR |

SPI_I2S prescaler register, Address offset: 0x20

Definition at line 1598 of file stm32f4xx.h.

| __IO uint32_t DCMI_TypeDef::ICR |

DCMI interrupt clear register, Address offset: 0x14

Definition at line 895 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::ICR |

LTDC Interrupt Clear Register, Address offset: 0x3C

Definition at line 1396 of file stm32f4xx.h.

| __IO uint32_t SDIO_TypeDef::ICR |

SDIO interrupt clear register, Address offset: 0x38

Definition at line 1568 of file stm32f4xx.h.

| __IO uint32_t DBGMCU_TypeDef::IDCODE |

MCU device ID code, Address offset: 0x00

Definition at line 878 of file stm32f4xx.h.

| __IO uint8_t CRC_TypeDef::IDR |

CRC Independent data register, Address offset: 0x04

Definition at line 844 of file stm32f4xx.h.

| __IO uint32_t GPIO_TypeDef::IDR |

GPIO port input data register, Address offset: 0x10

Definition at line 1287 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::IER |

CAN interrupt enable register, Address offset: 0x14

Definition at line 803 of file stm32f4xx.h.

| __IO uint32_t DCMI_TypeDef::IER |

DCMI interrupt enable register, Address offset: 0x0C

Definition at line 893 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::IER |

LTDC Interrupt Enable Register, Address offset: 0x34

Definition at line 1394 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::IFCR |

DMA2D Interrupt Flag Clear Register, Address offset: 0x08

Definition at line 933 of file stm32f4xx.h.

| __IO uint32_t EXTI_TypeDef::IMR |

EXTI Interrupt mask register, Address offset: 0x00

Definition at line 1119 of file stm32f4xx.h.

| __IO uint32_t SAI_Block_TypeDef::IMR |

SAI block x interrupt mask register, Address offset: 0x14

Definition at line 1542 of file stm32f4xx.h.

| __IO uint32_t HASH_TypeDef::IMR |

HASH interrupt enable register, Address offset: 0x20

Definition at line 1793 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::IMSCR |

CRYP interrupt mask set/clear register, Address offset: 0x14

Definition at line 1750 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::ISR |

DMA2D Interrupt Status Register, Address offset: 0x04

Definition at line 932 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::ISR |

LTDC Interrupt Status Register, Address offset: 0x38

Definition at line 1395 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::ISR |

RTC initialization and status register, Address offset: 0x0C

Definition at line 1487 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::IV0LR |

CRYP initialization vector left-word register 0, Address offset: 0x40

Definition at line 1761 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::IV0RR |

CRYP initialization vector right-word register 0, Address offset: 0x44

Definition at line 1762 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::IV1LR |

CRYP initialization vector left-word register 1, Address offset: 0x48

Definition at line 1763 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::IV1RR |

CRYP initialization vector right-word register 1, Address offset: 0x4C

Definition at line 1764 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::JDR1 |

ADC injected data register 1, Address offset: 0x3C

Definition at line 742 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::JDR2 |

ADC injected data register 2, Address offset: 0x40

Definition at line 743 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::JDR3 |

ADC injected data register 3, Address offset: 0x44

Definition at line 744 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::JDR4 |

ADC injected data register 4, Address offset: 0x48

Definition at line 745 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::JOFR1 |

ADC injected channel data offset register 1, Address offset: 0x14

Definition at line 732 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::JOFR2 |

ADC injected channel data offset register 2, Address offset: 0x18

Definition at line 733 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::JOFR3 |

ADC injected channel data offset register 3, Address offset: 0x1C

Definition at line 734 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::JOFR4 |

ADC injected channel data offset register 4, Address offset: 0x20

Definition at line 735 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::JSQR |

ADC injected sequence register, Address offset: 0x38

Definition at line 741 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::K0LR |

CRYP key left register 0, Address offset: 0x20

Definition at line 1753 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::K0RR |

CRYP key right register 0, Address offset: 0x24

Definition at line 1754 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::K1LR |

CRYP key left register 1, Address offset: 0x28

Definition at line 1755 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::K1RR |

CRYP key right register 1, Address offset: 0x2C

Definition at line 1756 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::K2LR |

CRYP key left register 2, Address offset: 0x30

Definition at line 1757 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::K2RR |

CRYP key right register 2, Address offset: 0x34

Definition at line 1758 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::K3LR |

CRYP key left register 3, Address offset: 0x38

Definition at line 1759 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::K3RR |

CRYP key right register 3, Address offset: 0x3C

Definition at line 1760 of file stm32f4xx.h.

| __IO uint32_t FLASH_TypeDef::KEYR |

FLASH key register, Address offset: 0x04

Definition at line 1134 of file stm32f4xx.h.

| __IO uint32_t IWDG_TypeDef::KR |

IWDG Key register, Address offset: 0x00

Definition at line 1371 of file stm32f4xx.h.

| __IO uint32_t GPIO_TypeDef::LCKR |

GPIO port configuration lock register, Address offset: 0x1C

Definition at line 1291 of file stm32f4xx.h.

| __IO uint32_t DMA_TypeDef::LIFCR |

DMA low interrupt flag clear register, Address offset: 0x08

Definition at line 921 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::LIPCR |

LTDC Line Interrupt Position Configuration Register, Address offset: 0x40

Definition at line 1397 of file stm32f4xx.h.

| __IO uint32_t DMA_TypeDef::LISR |

DMA low interrupt status register, Address offset: 0x00

Definition at line 919 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::LTR |

ADC watchdog lower threshold register, Address offset: 0x28

Definition at line 737 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::LWR |

DMA2D Line Watermark Register, Address offset: 0x48

Definition at line 949 of file stm32f4xx.h.

| __IO uint32_t DMA_Stream_TypeDef::M0AR |

DMA stream x memory 0 address register

Definition at line 912 of file stm32f4xx.h.

| __IO uint32_t DMA_Stream_TypeDef::M1AR |

DMA stream x memory 1 address register

Definition at line 913 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACA0HR |

Definition at line 1059 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACA0LR |

Definition at line 1060 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACA1HR |

Definition at line 1061 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACA1LR |

Definition at line 1062 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACA2HR |

Definition at line 1063 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACA2LR |

Definition at line 1064 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACA3HR |

Definition at line 1065 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACA3LR |

Definition at line 1066 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACCR |

Definition at line 1045 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACFCR |

Definition at line 1051 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACFFR |

Definition at line 1046 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACHTHR |

Definition at line 1047 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACHTLR |

Definition at line 1048 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACIMR |

Definition at line 1058 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACMIIAR |

Definition at line 1049 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACMIIDR |

Definition at line 1050 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACPMTCSR |

Definition at line 1055 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACRWUFFR |

Definition at line 1054 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACSR |

Definition at line 1057 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MACVLANTR |

Definition at line 1052 of file stm32f4xx.h.

| __IO uint32_t SDIO_TypeDef::MASK |

SDIO mask register, Address offset: 0x3C

Definition at line 1569 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::MCR |

CAN master control register, Address offset: 0x00

Definition at line 798 of file stm32f4xx.h.

| __IO uint32_t SYSCFG_TypeDef::MEMRMP |

SYSCFG memory remap register, Address offset: 0x00

Definition at line 1301 of file stm32f4xx.h.

| __IO uint32_t DCMI_TypeDef::MISR |

DCMI masked interrupt status register, Address offset: 0x10

Definition at line 894 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::MISR |

CRYP masked interrupt status register, Address offset: 0x1C

Definition at line 1752 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MMCCR |

Definition at line 1068 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MMCRFAECR |

Definition at line 1080 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MMCRFCECR |

Definition at line 1079 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MMCRGUFCR |

Definition at line 1082 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MMCRIMR |

Definition at line 1071 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MMCRIR |

Definition at line 1069 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MMCTGFCR |

Definition at line 1077 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MMCTGFMSCCR |

Definition at line 1075 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MMCTGFSCCR |

Definition at line 1074 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MMCTIMR |

Definition at line 1072 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::MMCTIR |

Definition at line 1070 of file stm32f4xx.h.

| __IO uint32_t GPIO_TypeDef::MODER |

GPIO port mode register, Address offset: 0x00

Definition at line 1283 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::MSR |

CAN master status register, Address offset: 0x04

Definition at line 799 of file stm32f4xx.h.

| __IO uint32_t DMA_Stream_TypeDef::NDTR |

DMA stream x number of data register

Definition at line 910 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::NLR |

DMA2D Number of Line Register, Address offset: 0x44

Definition at line 948 of file stm32f4xx.h.

| __IO uint16_t I2C_TypeDef::OAR1 |

I2C Own address register 1, Address offset: 0x08

Definition at line 1326 of file stm32f4xx.h.

| __IO uint16_t I2C_TypeDef::OAR2 |

I2C Own address register 2, Address offset: 0x0C

Definition at line 1328 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::OCOLR |

DMA2D Output Color Register, Address offset: 0x38

Definition at line 945 of file stm32f4xx.h.

| __IO uint32_t GPIO_TypeDef::ODR |

GPIO port output data register, Address offset: 0x14

Definition at line 1288 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::OMAR |

DMA2D Output Memory Address Register, Address offset: 0x3C

Definition at line 946 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::OOR |

DMA2D Output Offset Register, Address offset: 0x40

Definition at line 947 of file stm32f4xx.h.

| __IO uint32_t DMA2D_TypeDef::OPFCCR |

DMA2D Output PFC Control Register, Address offset: 0x34

Definition at line 944 of file stm32f4xx.h.

| __IO uint32_t FLASH_TypeDef::OPTCR |

FLASH option control register , Address offset: 0x14

Definition at line 1138 of file stm32f4xx.h.

| __IO uint32_t FLASH_TypeDef::OPTCR1 |

FLASH option control register 1, Address offset: 0x18

Definition at line 1139 of file stm32f4xx.h.

| __IO uint32_t FLASH_TypeDef::OPTKEYR |

FLASH option key register, Address offset: 0x08

Definition at line 1135 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::OR |

TIM option register, Address offset: 0x50

Definition at line 1702 of file stm32f4xx.h.

| __IO uint32_t GPIO_TypeDef::OSPEEDR |

GPIO port output speed register, Address offset: 0x08

Definition at line 1285 of file stm32f4xx.h.

| __IO uint32_t GPIO_TypeDef::OTYPER |

GPIO port output type register, Address offset: 0x04

Definition at line 1284 of file stm32f4xx.h.

| __IO uint32_t DMA_Stream_TypeDef::PAR |

DMA stream x peripheral address register

Definition at line 911 of file stm32f4xx.h.

| __IO uint32_t LTDC_Layer_TypeDef::PFCR |

LTDC Layerx Pixel Format Configuration Register Address offset: 0x94

Definition at line 1412 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::PLLCFGR |

RCC PLL configuration register, Address offset: 0x04

Definition at line 1442 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::PLLI2SCFGR |

RCC PLLI2S configuration register, Address offset: 0x84

Definition at line 1470 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::PLLSAICFGR |

RCC PLLSAI configuration register, Address offset: 0x88

Definition at line 1471 of file stm32f4xx.h.

| __IO uint32_t SYSCFG_TypeDef::PMC |

SYSCFG peripheral mode configuration register, Address offset: 0x04

Definition at line 1302 of file stm32f4xx.h.

| __IO uint32_t SDIO_TypeDef::POWER |

SDIO power control register, Address offset: 0x00

Definition at line 1554 of file stm32f4xx.h.

| __IO uint32_t EXTI_TypeDef::PR |

EXTI Pending register, Address offset: 0x14

Definition at line 1124 of file stm32f4xx.h.

| __IO uint32_t IWDG_TypeDef::PR |

IWDG Prescaler register, Address offset: 0x04

Definition at line 1372 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::PRER |

RTC prescaler register, Address offset: 0x10

Definition at line 1488 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::PSC |

TIM prescaler, Address offset: 0x28

Definition at line 1687 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::PTPSSIR |

Definition at line 1085 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::PTPTSAR |

Definition at line 1090 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::PTPTSCR |

Definition at line 1084 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::PTPTSHR |

Definition at line 1086 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::PTPTSHUR |

Definition at line 1088 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::PTPTSLR |

Definition at line 1087 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::PTPTSLUR |

Definition at line 1089 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::PTPTSSR |

Definition at line 1094 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::PTPTTHR |

Definition at line 1091 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::PTPTTLR |

Definition at line 1092 of file stm32f4xx.h.

| __IO uint32_t GPIO_TypeDef::PUPDR |

GPIO port pull-up/pull-down register, Address offset: 0x0C

Definition at line 1286 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::RCR |

TIM repetition counter register, Address offset: 0x30

Definition at line 1690 of file stm32f4xx.h.

| __IO uint32_t CAN_FIFOMailBox_TypeDef::RDHR |

CAN receive FIFO mailbox data high register

Definition at line 779 of file stm32f4xx.h.

| __IO uint32_t CAN_FIFOMailBox_TypeDef::RDLR |

CAN receive FIFO mailbox data low register

Definition at line 778 of file stm32f4xx.h.

| __IO uint32_t CAN_FIFOMailBox_TypeDef::RDTR |

CAN receive FIFO mailbox data length control and time stamp register

Definition at line 777 of file stm32f4xx.h.

| uint32_t DMA2D_TypeDef::RESERVED[236] |

Reserved, 0x50-0x3FF

Definition at line 951 of file stm32f4xx.h.

| uint32_t SYSCFG_TypeDef::RESERVED[2] |

Reserved, 0x18-0x1C

Definition at line 1311 of file stm32f4xx.h.

| uint32_t HASH_TypeDef::RESERVED[52] |

Reserved, 0x28-0xF4

Definition at line 1795 of file stm32f4xx.h.

| uint32_t CAN_TypeDef::RESERVED0 |

Reserved, 0x020 - 0x17F

Definition at line 806 of file stm32f4xx.h.

| uint8_t CRC_TypeDef::RESERVED0 |

Reserved, 0x05

Definition at line 845 of file stm32f4xx.h.

| uint32_t ETH_TypeDef::RESERVED0 |

Definition at line 1053 of file stm32f4xx.h.

| uint16_t I2C_TypeDef::RESERVED0 |

Reserved, 0x02

Definition at line 1323 of file stm32f4xx.h.

| uint32_t LTDC_TypeDef::RESERVED0[2] |

Reserved, 0x00-0x04

Definition at line 1383 of file stm32f4xx.h.

| uint32_t LTDC_Layer_TypeDef::RESERVED0[2] |

Reserved

Definition at line 1416 of file stm32f4xx.h.

| uint32_t RCC_TypeDef::RESERVED0 |

Reserved, 0x1C

Definition at line 1448 of file stm32f4xx.h.

| uint32_t SDIO_TypeDef::RESERVED0 |

Reserved, 0x40-0x44

Definition at line 1570 of file stm32f4xx.h.

| uint16_t SPI_TypeDef::RESERVED0 |

Reserved, 0x02

Definition at line 1583 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED0 |

Reserved, 0x02

Definition at line 1669 of file stm32f4xx.h.

| uint16_t USART_TypeDef::RESERVED0 |

Reserved, 0x02

Definition at line 1713 of file stm32f4xx.h.

| uint32_t CAN_TypeDef::RESERVED1 |

Reserved, 0x1D0 - 0x1FF

Definition at line 809 of file stm32f4xx.h.

| uint16_t CRC_TypeDef::RESERVED1 |

Reserved, 0x06

Definition at line 846 of file stm32f4xx.h.

| uint32_t ETH_TypeDef::RESERVED1 |

Definition at line 1056 of file stm32f4xx.h.

| uint16_t I2C_TypeDef::RESERVED1 |

Reserved, 0x06

Definition at line 1325 of file stm32f4xx.h.

| uint32_t LTDC_TypeDef::RESERVED1[2] |

Reserved, 0x1C-0x20

Definition at line 1389 of file stm32f4xx.h.

| uint32_t LTDC_Layer_TypeDef::RESERVED1[3] |

Reserved

Definition at line 1420 of file stm32f4xx.h.

| uint32_t RCC_TypeDef::RESERVED1[2] |

Reserved, 0x28-0x2C

Definition at line 1451 of file stm32f4xx.h.

| uint32_t SDIO_TypeDef::RESERVED1 |

Reserved, 0x4C-0x7C

Definition at line 1572 of file stm32f4xx.h.

| uint16_t SPI_TypeDef::RESERVED1 |

Reserved, 0x06

Definition at line 1585 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED1 |

Reserved, 0x06

Definition at line 1671 of file stm32f4xx.h.

| uint16_t USART_TypeDef::RESERVED1 |

Reserved, 0x06

Definition at line 1715 of file stm32f4xx.h.

| uint32_t ETH_TypeDef::RESERVED10[8] |

Definition at line 1106 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED10 |

Reserved, 0x32

Definition at line 1691 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED11 |

Reserved, 0x46

Definition at line 1697 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED12 |

Reserved, 0x4A

Definition at line 1699 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED13 |

Reserved, 0x4E

Definition at line 1701 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED14 |

Reserved, 0x52

Definition at line 1703 of file stm32f4xx.h.

| uint32_t CAN_TypeDef::RESERVED2 |

Reserved, 0x208

Definition at line 812 of file stm32f4xx.h.

| uint32_t ETH_TypeDef::RESERVED2 |

Definition at line 1067 of file stm32f4xx.h.

| uint16_t I2C_TypeDef::RESERVED2 |

Reserved, 0x0A

Definition at line 1327 of file stm32f4xx.h.

| uint32_t LTDC_TypeDef::RESERVED2[1] |

Reserved, 0x28

Definition at line 1391 of file stm32f4xx.h.

| uint32_t RCC_TypeDef::RESERVED2 |

Reserved, 0x3C

Definition at line 1455 of file stm32f4xx.h.

| uint16_t SPI_TypeDef::RESERVED2 |

Reserved, 0x0A

Definition at line 1587 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED2 |

Reserved, 0x0A

Definition at line 1673 of file stm32f4xx.h.

| uint16_t USART_TypeDef::RESERVED2 |

Reserved, 0x0A

Definition at line 1717 of file stm32f4xx.h.

| uint32_t CAN_TypeDef::RESERVED3 |

Reserved, 0x210

Definition at line 814 of file stm32f4xx.h.

| uint32_t ETH_TypeDef::RESERVED3 |

Definition at line 1073 of file stm32f4xx.h.

| uint16_t I2C_TypeDef::RESERVED3 |

Reserved, 0x0E

Definition at line 1329 of file stm32f4xx.h.

| uint32_t LTDC_TypeDef::RESERVED3[1] |

Reserved, 0x30

Definition at line 1393 of file stm32f4xx.h.

| uint32_t RCC_TypeDef::RESERVED3[2] |

Reserved, 0x48-0x4C

Definition at line 1458 of file stm32f4xx.h.

| uint16_t SPI_TypeDef::RESERVED3 |

Reserved, 0x0E

Definition at line 1589 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED3 |

Reserved, 0x0E

Definition at line 1675 of file stm32f4xx.h.

| uint16_t USART_TypeDef::RESERVED3 |

Reserved, 0x0E

Definition at line 1719 of file stm32f4xx.h.

| uint32_t CAN_TypeDef::RESERVED4 |

Reserved, 0x218

Definition at line 816 of file stm32f4xx.h.

| uint32_t ETH_TypeDef::RESERVED4 |

Definition at line 1076 of file stm32f4xx.h.

| uint16_t I2C_TypeDef::RESERVED4 |

Reserved, 0x12

Definition at line 1331 of file stm32f4xx.h.

| uint32_t RCC_TypeDef::RESERVED4 |

Reserved, 0x5C

Definition at line 1462 of file stm32f4xx.h.

| uint16_t SPI_TypeDef::RESERVED4 |

Reserved, 0x12

Definition at line 1591 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED4 |

Reserved, 0x12

Definition at line 1677 of file stm32f4xx.h.

| uint16_t USART_TypeDef::RESERVED4 |

Reserved, 0x12

Definition at line 1721 of file stm32f4xx.h.

| uint32_t CAN_TypeDef::RESERVED5 |

Reserved, 0x220-0x23F

Definition at line 818 of file stm32f4xx.h.

| uint32_t ETH_TypeDef::RESERVED5 |

Definition at line 1078 of file stm32f4xx.h.

| uint16_t I2C_TypeDef::RESERVED5 |

Reserved, 0x16

Definition at line 1333 of file stm32f4xx.h.

| uint32_t RCC_TypeDef::RESERVED5[2] |

Reserved, 0x68-0x6C

Definition at line 1465 of file stm32f4xx.h.

| uint16_t SPI_TypeDef::RESERVED5 |

Reserved, 0x16

Definition at line 1593 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED5 |

Reserved, 0x16

Definition at line 1679 of file stm32f4xx.h.

| uint16_t USART_TypeDef::RESERVED5 |

Reserved, 0x16

Definition at line 1723 of file stm32f4xx.h.

| uint32_t ETH_TypeDef::RESERVED6 |

Definition at line 1081 of file stm32f4xx.h.

| uint16_t I2C_TypeDef::RESERVED6 |

Reserved, 0x1A

Definition at line 1335 of file stm32f4xx.h.

| uint32_t RCC_TypeDef::RESERVED6[2] |

Reserved, 0x78-0x7C

Definition at line 1468 of file stm32f4xx.h.

| uint16_t SPI_TypeDef::RESERVED6 |

Reserved, 0x1A

Definition at line 1595 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED6 |

Reserved, 0x1A

Definition at line 1681 of file stm32f4xx.h.

| uint16_t USART_TypeDef::RESERVED6 |

Reserved, 0x1A

Definition at line 1725 of file stm32f4xx.h.

| uint32_t ETH_TypeDef::RESERVED7 |

Definition at line 1083 of file stm32f4xx.h.

| uint16_t I2C_TypeDef::RESERVED7 |

Reserved, 0x1E

Definition at line 1337 of file stm32f4xx.h.

| uint32_t RTC_TypeDef::RESERVED7 |

Reserved, 0x4C

Definition at line 1503 of file stm32f4xx.h.

| uint16_t SPI_TypeDef::RESERVED7 |

Reserved, 0x1E

Definition at line 1597 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED7 |

Reserved, 0x1E

Definition at line 1683 of file stm32f4xx.h.

| __IO uint32_t ETH_TypeDef::RESERVED8 |

Definition at line 1093 of file stm32f4xx.h.

| uint16_t I2C_TypeDef::RESERVED8 |

Reserved, 0x22

Definition at line 1339 of file stm32f4xx.h.

| uint16_t SPI_TypeDef::RESERVED8 |

Reserved, 0x22

Definition at line 1599 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED8 |

Reserved, 0x22

Definition at line 1685 of file stm32f4xx.h.

| uint32_t ETH_TypeDef::RESERVED9 |

Definition at line 1095 of file stm32f4xx.h.

| uint16_t I2C_TypeDef::RESERVED9 |

Reserved, 0x26

Definition at line 1341 of file stm32f4xx.h.

| uint16_t TIM_TypeDef::RESERVED9 |

Reserved, 0x2A

Definition at line 1688 of file stm32f4xx.h.

| __I uint32_t SDIO_TypeDef::RESP1 |

SDIO response 1 register, Address offset: 0x14

Definition at line 1559 of file stm32f4xx.h.

| __I uint32_t SDIO_TypeDef::RESP2 |

SDIO response 2 register, Address offset: 0x18

Definition at line 1560 of file stm32f4xx.h.

| __I uint32_t SDIO_TypeDef::RESP3 |

SDIO response 3 register, Address offset: 0x1C

Definition at line 1561 of file stm32f4xx.h.

| __I uint32_t SDIO_TypeDef::RESP4 |

SDIO response 4 register, Address offset: 0x20

Definition at line 1562 of file stm32f4xx.h.

| __I uint32_t SDIO_TypeDef::RESPCMD |

SDIO command response register, Address offset: 0x10

Definition at line 1558 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::RF0R |

CAN receive FIFO 0 register, Address offset: 0x0C

Definition at line 801 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::RF1R |

CAN receive FIFO 1 register, Address offset: 0x10

Definition at line 802 of file stm32f4xx.h.

| __IO uint32_t CAN_FIFOMailBox_TypeDef::RIR |

CAN receive FIFO mailbox identifier register

Definition at line 776 of file stm32f4xx.h.

| __IO uint32_t DCMI_TypeDef::RISR |

DCMI raw interrupt status register, Address offset: 0x08

Definition at line 892 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::RISR |

CRYP raw interrupt status register, Address offset: 0x18

Definition at line 1751 of file stm32f4xx.h.

| __IO uint32_t IWDG_TypeDef::RLR |

IWDG Reload register, Address offset: 0x08

Definition at line 1373 of file stm32f4xx.h.

| __IO uint32_t EXTI_TypeDef::RTSR |

EXTI Rising trigger selection register, Address offset: 0x08

Definition at line 1121 of file stm32f4xx.h.

| __IO uint16_t SPI_TypeDef::RXCRCR |

SPI RX CRC register (not used in I2S mode), Address offset: 0x14

Definition at line 1592 of file stm32f4xx.h.

| CAN_FIFOMailBox_TypeDef CAN_TypeDef::sFIFOMailBox |

CAN FIFO MailBox, Address offset: 0x1B0 - 0x1CC

Definition at line 808 of file stm32f4xx.h.

| CAN_FilterRegister_TypeDef CAN_TypeDef::sFilterRegister |

CAN Filter Register, Address offset: 0x240-0x31C

Definition at line 819 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::SHIFTR |

RTC shift control register, Address offset: 0x2C

Definition at line 1495 of file stm32f4xx.h.

| __IO uint32_t SAI_Block_TypeDef::SLOTR |

SAI block x slot register, Address offset: 0x10

Definition at line 1541 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::SMCR |

TIM slave mode control register, Address offset: 0x08

Definition at line 1672 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::SMPR1 |

ADC sample time register 1, Address offset: 0x0C

Definition at line 730 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::SMPR2 |

ADC sample time register 2, Address offset: 0x10

Definition at line 731 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::SQR1 |

ADC regular sequence register 1, Address offset: 0x2C

Definition at line 738 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::SQR2 |

ADC regular sequence register 2, Address offset: 0x30

Definition at line 739 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::SQR3 |

ADC regular sequence register 3, Address offset: 0x34

Definition at line 740 of file stm32f4xx.h.

| __IO uint32_t ADC_TypeDef::SR |

ADC status register, Address offset: 0x00

Definition at line 727 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::SR |

DAC status register, Address offset: 0x34

Definition at line 869 of file stm32f4xx.h.

| __IO uint32_t DCMI_TypeDef::SR |

DCMI status register, Address offset: 0x04

Definition at line 891 of file stm32f4xx.h.

| __IO uint32_t FLASH_TypeDef::SR |

FLASH status register, Address offset: 0x0C

Definition at line 1136 of file stm32f4xx.h.

| __IO uint32_t IWDG_TypeDef::SR |

IWDG Status register, Address offset: 0x0C

Definition at line 1374 of file stm32f4xx.h.

| __IO uint32_t SAI_Block_TypeDef::SR |

SAI block x status register, Address offset: 0x18

Definition at line 1543 of file stm32f4xx.h.

| __IO uint16_t SPI_TypeDef::SR |

SPI status register, Address offset: 0x08

Definition at line 1586 of file stm32f4xx.h.

| __IO uint16_t TIM_TypeDef::SR |

TIM status register, Address offset: 0x10

Definition at line 1676 of file stm32f4xx.h.

| __IO uint16_t USART_TypeDef::SR |

USART Status register, Address offset: 0x00

Definition at line 1712 of file stm32f4xx.h.

| __IO uint32_t WWDG_TypeDef::SR |

WWDG Status register, Address offset: 0x08

Definition at line 1736 of file stm32f4xx.h.

| __IO uint32_t CRYP_TypeDef::SR |

CRYP status register, Address offset: 0x04

Definition at line 1746 of file stm32f4xx.h.

| __IO uint32_t HASH_TypeDef::SR |

HASH status register, Address offset: 0x24

Definition at line 1794 of file stm32f4xx.h.

| __IO uint32_t RNG_TypeDef::SR |

RNG status register, Address offset: 0x04

Definition at line 1815 of file stm32f4xx.h.

| __IO uint16_t I2C_TypeDef::SR1 |

I2C Status register 1, Address offset: 0x14

Definition at line 1332 of file stm32f4xx.h.

| __IO uint16_t I2C_TypeDef::SR2 |

I2C Status register 2, Address offset: 0x18

Definition at line 1334 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::SRCR |

LTDC Shadow Reload Configuration Register, Address offset: 0x24

Definition at line 1390 of file stm32f4xx.h.

| __IO uint32_t RCC_TypeDef::SSCGR |

RCC spread spectrum clock generation register, Address offset: 0x80

Definition at line 1469 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::SSCR |

LTDC Synchronization Size Configuration Register, Address offset: 0x08

Definition at line 1384 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::SSR |

RTC sub second register, Address offset: 0x28

Definition at line 1494 of file stm32f4xx.h.

| __I uint32_t SDIO_TypeDef::STA |

SDIO status register, Address offset: 0x34

Definition at line 1567 of file stm32f4xx.h.

| __IO uint32_t HASH_TypeDef::STR |

HASH start register, Address offset: 0x08

Definition at line 1791 of file stm32f4xx.h.

| CAN_TxMailBox_TypeDef CAN_TypeDef::sTxMailBox |

CAN Tx MailBox, Address offset: 0x180 - 0x1AC

Definition at line 807 of file stm32f4xx.h.

| __IO uint32_t EXTI_TypeDef::SWIER |

EXTI Software interrupt event register, Address offset: 0x10

Definition at line 1123 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::SWTRIGR |

DAC software trigger register, Address offset: 0x04

Definition at line 857 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::TAFCR |

RTC tamper and alternate function configuration register, Address offset: 0x40

Definition at line 1500 of file stm32f4xx.h.

| __IO uint32_t CAN_TxMailBox_TypeDef::TDHR |

CAN mailbox data high register

Definition at line 767 of file stm32f4xx.h.

| __IO uint32_t CAN_TxMailBox_TypeDef::TDLR |

CAN mailbox data low register

Definition at line 766 of file stm32f4xx.h.

| __IO uint32_t CAN_TxMailBox_TypeDef::TDTR |

CAN mailbox data length control and time stamp register

Definition at line 765 of file stm32f4xx.h.

| __IO uint32_t CAN_TxMailBox_TypeDef::TIR |

CAN TX mailbox identifier register

Definition at line 764 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::TR |

RTC time register, Address offset: 0x00

Definition at line 1484 of file stm32f4xx.h.

| __IO uint16_t I2C_TypeDef::TRISE |

I2C TRISE register, Address offset: 0x20

Definition at line 1338 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::TSDR |

RTC time stamp date register, Address offset: 0x34

Definition at line 1497 of file stm32f4xx.h.

| __IO uint32_t CAN_TypeDef::TSR |

CAN transmit status register, Address offset: 0x08

Definition at line 800 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::TSSSR |

RTC time-stamp sub second register, Address offset: 0x38

Definition at line 1498 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::TSTR |

RTC time stamp time register, Address offset: 0x30

Definition at line 1496 of file stm32f4xx.h.

| __IO uint32_t LTDC_TypeDef::TWCR |

LTDC Total Width Configuration Register, Address offset: 0x14

Definition at line 1387 of file stm32f4xx.h.

| __IO uint16_t SPI_TypeDef::TXCRCR |

SPI TX CRC register (not used in I2S mode), Address offset: 0x18

Definition at line 1594 of file stm32f4xx.h.

| __IO uint32_t LTDC_Layer_TypeDef::WHPCR |

LTDC Layerx Window Horizontal Position Configuration Register Address offset: 0x88

Definition at line 1409 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::WPR |

RTC write protection register, Address offset: 0x24

Definition at line 1493 of file stm32f4xx.h.

| __IO uint32_t RTC_TypeDef::WUTR |

RTC wakeup timer register, Address offset: 0x14

Definition at line 1489 of file stm32f4xx.h.

| __IO uint32_t LTDC_Layer_TypeDef::WVPCR |

LTDC Layerx Window Vertical Position Configuration Register Address offset: 0x8C

Definition at line 1410 of file stm32f4xx.h.