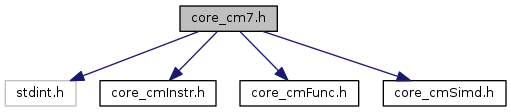

CMSIS Cortex-M7 Core Peripheral Access Layer Header File. More...

Go to the source code of this file.

Classes | |

| union | APSR_Type |

| Union type to access the Application Program Status Register (APSR). More... | |

| union | CONTROL_Type |

| Union type to access the Control Registers (CONTROL). More... | |

| struct | CoreDebug_Type |

| Structure type to access the Core Debug Register (CoreDebug). More... | |

| struct | DWT_Type |

| Structure type to access the Data Watchpoint and Trace Register (DWT). More... | |

| union | IPSR_Type |

| Union type to access the Interrupt Program Status Register (IPSR). More... | |

| struct | ITM_Type |

| Structure type to access the Instrumentation Trace Macrocell Register (ITM). More... | |

| struct | NVIC_Type |

| Structure type to access the Nested Vectored Interrupt Controller (NVIC). More... | |

| struct | SCB_Type |

| Structure type to access the System Control Block (SCB). More... | |

| struct | SCnSCB_Type |

| Structure type to access the System Control and ID Register not in the SCB. More... | |

| struct | SysTick_Type |

| Structure type to access the System Timer (SysTick). More... | |

| struct | TPI_Type |

| Structure type to access the Trace Port Interface Register (TPI). More... | |

| union | xPSR_Type |

| Union type to access the Special-Purpose Program Status Registers (xPSR). More... | |

Macros | |

| #define | __CORE_CM7_H_GENERIC |

| #define | CCSIDR_LSSHIFT(x) (((x) & SCB_CCSIDR_LINESIZE_Msk ) >> SCB_CCSIDR_LINESIZE_Pos ) |

| #define | CCSIDR_SETS(x) (((x) & SCB_CCSIDR_NUMSETS_Msk ) >> SCB_CCSIDR_NUMSETS_Pos ) |

| #define | CCSIDR_WAYS(x) (((x) & SCB_CCSIDR_ASSOCIATIVITY_Msk) >> SCB_CCSIDR_ASSOCIATIVITY_Pos) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | CoreDebug_DCRSR_REGSEL_Msk (0x1FUL << CoreDebug_DCRSR_REGSEL_Pos) |

| #define | CoreDebug_DCRSR_REGSEL_Pos 0 |

| #define | CoreDebug_DCRSR_REGWnR_Msk (1UL << CoreDebug_DCRSR_REGWnR_Pos) |

| #define | CoreDebug_DCRSR_REGWnR_Pos 16 |

| #define | CoreDebug_DEMCR_MON_EN_Msk (1UL << CoreDebug_DEMCR_MON_EN_Pos) |

| #define | CoreDebug_DEMCR_MON_EN_Pos 16 |

| #define | CoreDebug_DEMCR_MON_PEND_Msk (1UL << CoreDebug_DEMCR_MON_PEND_Pos) |

| #define | CoreDebug_DEMCR_MON_PEND_Pos 17 |

| #define | CoreDebug_DEMCR_MON_REQ_Msk (1UL << CoreDebug_DEMCR_MON_REQ_Pos) |

| #define | CoreDebug_DEMCR_MON_REQ_Pos 19 |

| #define | CoreDebug_DEMCR_MON_STEP_Msk (1UL << CoreDebug_DEMCR_MON_STEP_Pos) |

| #define | CoreDebug_DEMCR_MON_STEP_Pos 18 |

| #define | CoreDebug_DEMCR_TRCENA_Msk (1UL << CoreDebug_DEMCR_TRCENA_Pos) |

| #define | CoreDebug_DEMCR_TRCENA_Pos 24 |

| #define | CoreDebug_DEMCR_VC_BUSERR_Msk (1UL << CoreDebug_DEMCR_VC_BUSERR_Pos) |

| #define | CoreDebug_DEMCR_VC_BUSERR_Pos 8 |

| #define | CoreDebug_DEMCR_VC_CHKERR_Msk (1UL << CoreDebug_DEMCR_VC_CHKERR_Pos) |

| #define | CoreDebug_DEMCR_VC_CHKERR_Pos 6 |

| #define | CoreDebug_DEMCR_VC_CORERESET_Msk (1UL << CoreDebug_DEMCR_VC_CORERESET_Pos) |

| #define | CoreDebug_DEMCR_VC_CORERESET_Pos 0 |

| #define | CoreDebug_DEMCR_VC_HARDERR_Msk (1UL << CoreDebug_DEMCR_VC_HARDERR_Pos) |

| #define | CoreDebug_DEMCR_VC_HARDERR_Pos 10 |

| #define | CoreDebug_DEMCR_VC_INTERR_Msk (1UL << CoreDebug_DEMCR_VC_INTERR_Pos) |

| #define | CoreDebug_DEMCR_VC_INTERR_Pos 9 |

| #define | CoreDebug_DEMCR_VC_MMERR_Msk (1UL << CoreDebug_DEMCR_VC_MMERR_Pos) |

| #define | CoreDebug_DEMCR_VC_MMERR_Pos 4 |

| #define | CoreDebug_DEMCR_VC_NOCPERR_Msk (1UL << CoreDebug_DEMCR_VC_NOCPERR_Pos) |

| #define | CoreDebug_DEMCR_VC_NOCPERR_Pos 5 |

| #define | CoreDebug_DEMCR_VC_STATERR_Msk (1UL << CoreDebug_DEMCR_VC_STATERR_Pos) |

| #define | CoreDebug_DEMCR_VC_STATERR_Pos 7 |

| #define | CoreDebug_DHCSR_C_DEBUGEN_Msk (1UL << CoreDebug_DHCSR_C_DEBUGEN_Pos) |

| #define | CoreDebug_DHCSR_C_DEBUGEN_Pos 0 |

| #define | CoreDebug_DHCSR_C_HALT_Msk (1UL << CoreDebug_DHCSR_C_HALT_Pos) |

| #define | CoreDebug_DHCSR_C_HALT_Pos 1 |

| #define | CoreDebug_DHCSR_C_MASKINTS_Msk (1UL << CoreDebug_DHCSR_C_MASKINTS_Pos) |

| #define | CoreDebug_DHCSR_C_MASKINTS_Pos 3 |

| #define | CoreDebug_DHCSR_C_SNAPSTALL_Msk (1UL << CoreDebug_DHCSR_C_SNAPSTALL_Pos) |

| #define | CoreDebug_DHCSR_C_SNAPSTALL_Pos 5 |

| #define | CoreDebug_DHCSR_C_STEP_Msk (1UL << CoreDebug_DHCSR_C_STEP_Pos) |

| #define | CoreDebug_DHCSR_C_STEP_Pos 2 |

| #define | CoreDebug_DHCSR_DBGKEY_Msk (0xFFFFUL << CoreDebug_DHCSR_DBGKEY_Pos) |

| #define | CoreDebug_DHCSR_DBGKEY_Pos 16 |

| #define | CoreDebug_DHCSR_S_HALT_Msk (1UL << CoreDebug_DHCSR_S_HALT_Pos) |

| #define | CoreDebug_DHCSR_S_HALT_Pos 17 |

| #define | CoreDebug_DHCSR_S_LOCKUP_Msk (1UL << CoreDebug_DHCSR_S_LOCKUP_Pos) |

| #define | CoreDebug_DHCSR_S_LOCKUP_Pos 19 |

| #define | CoreDebug_DHCSR_S_REGRDY_Msk (1UL << CoreDebug_DHCSR_S_REGRDY_Pos) |

| #define | CoreDebug_DHCSR_S_REGRDY_Pos 16 |

| #define | CoreDebug_DHCSR_S_RESET_ST_Msk (1UL << CoreDebug_DHCSR_S_RESET_ST_Pos) |

| #define | CoreDebug_DHCSR_S_RESET_ST_Pos 25 |

| #define | CoreDebug_DHCSR_S_RETIRE_ST_Msk (1UL << CoreDebug_DHCSR_S_RETIRE_ST_Pos) |

| #define | CoreDebug_DHCSR_S_RETIRE_ST_Pos 24 |

| #define | CoreDebug_DHCSR_S_SLEEP_Msk (1UL << CoreDebug_DHCSR_S_SLEEP_Pos) |

| #define | CoreDebug_DHCSR_S_SLEEP_Pos 18 |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | DWT_CPICNT_CPICNT_Msk (0xFFUL << DWT_CPICNT_CPICNT_Pos) |

| #define | DWT_CPICNT_CPICNT_Pos 0 |

| #define | DWT_CTRL_CPIEVTENA_Msk (0x1UL << DWT_CTRL_CPIEVTENA_Pos) |

| #define | DWT_CTRL_CPIEVTENA_Pos 17 |

| #define | DWT_CTRL_CYCCNTENA_Msk (0x1UL << DWT_CTRL_CYCCNTENA_Pos) |

| #define | DWT_CTRL_CYCCNTENA_Pos 0 |

| #define | DWT_CTRL_CYCEVTENA_Msk (0x1UL << DWT_CTRL_CYCEVTENA_Pos) |

| #define | DWT_CTRL_CYCEVTENA_Pos 22 |

| #define | DWT_CTRL_CYCTAP_Msk (0x1UL << DWT_CTRL_CYCTAP_Pos) |

| #define | DWT_CTRL_CYCTAP_Pos 9 |

| #define | DWT_CTRL_EXCEVTENA_Msk (0x1UL << DWT_CTRL_EXCEVTENA_Pos) |

| #define | DWT_CTRL_EXCEVTENA_Pos 18 |

| #define | DWT_CTRL_EXCTRCENA_Msk (0x1UL << DWT_CTRL_EXCTRCENA_Pos) |

| #define | DWT_CTRL_EXCTRCENA_Pos 16 |

| #define | DWT_CTRL_FOLDEVTENA_Msk (0x1UL << DWT_CTRL_FOLDEVTENA_Pos) |

| #define | DWT_CTRL_FOLDEVTENA_Pos 21 |

| #define | DWT_CTRL_LSUEVTENA_Msk (0x1UL << DWT_CTRL_LSUEVTENA_Pos) |

| #define | DWT_CTRL_LSUEVTENA_Pos 20 |

| #define | DWT_CTRL_NOCYCCNT_Msk (0x1UL << DWT_CTRL_NOCYCCNT_Pos) |

| #define | DWT_CTRL_NOCYCCNT_Pos 25 |

| #define | DWT_CTRL_NOEXTTRIG_Msk (0x1UL << DWT_CTRL_NOEXTTRIG_Pos) |

| #define | DWT_CTRL_NOEXTTRIG_Pos 26 |

| #define | DWT_CTRL_NOPRFCNT_Msk (0x1UL << DWT_CTRL_NOPRFCNT_Pos) |

| #define | DWT_CTRL_NOPRFCNT_Pos 24 |

| #define | DWT_CTRL_NOTRCPKT_Msk (0x1UL << DWT_CTRL_NOTRCPKT_Pos) |

| #define | DWT_CTRL_NOTRCPKT_Pos 27 |

| #define | DWT_CTRL_NUMCOMP_Msk (0xFUL << DWT_CTRL_NUMCOMP_Pos) |

| #define | DWT_CTRL_NUMCOMP_Pos 28 |

| #define | DWT_CTRL_PCSAMPLENA_Msk (0x1UL << DWT_CTRL_PCSAMPLENA_Pos) |

| #define | DWT_CTRL_PCSAMPLENA_Pos 12 |

| #define | DWT_CTRL_POSTINIT_Msk (0xFUL << DWT_CTRL_POSTINIT_Pos) |

| #define | DWT_CTRL_POSTINIT_Pos 5 |

| #define | DWT_CTRL_POSTPRESET_Msk (0xFUL << DWT_CTRL_POSTPRESET_Pos) |

| #define | DWT_CTRL_POSTPRESET_Pos 1 |

| #define | DWT_CTRL_SLEEPEVTENA_Msk (0x1UL << DWT_CTRL_SLEEPEVTENA_Pos) |

| #define | DWT_CTRL_SLEEPEVTENA_Pos 19 |

| #define | DWT_CTRL_SYNCTAP_Msk (0x3UL << DWT_CTRL_SYNCTAP_Pos) |

| #define | DWT_CTRL_SYNCTAP_Pos 10 |

| #define | DWT_EXCCNT_EXCCNT_Msk (0xFFUL << DWT_EXCCNT_EXCCNT_Pos) |

| #define | DWT_EXCCNT_EXCCNT_Pos 0 |

| #define | DWT_FOLDCNT_FOLDCNT_Msk (0xFFUL << DWT_FOLDCNT_FOLDCNT_Pos) |

| #define | DWT_FOLDCNT_FOLDCNT_Pos 0 |

| #define | DWT_FUNCTION_CYCMATCH_Msk (0x1UL << DWT_FUNCTION_CYCMATCH_Pos) |

| #define | DWT_FUNCTION_CYCMATCH_Pos 7 |

| #define | DWT_FUNCTION_DATAVADDR0_Msk (0xFUL << DWT_FUNCTION_DATAVADDR0_Pos) |

| #define | DWT_FUNCTION_DATAVADDR0_Pos 12 |

| #define | DWT_FUNCTION_DATAVADDR1_Msk (0xFUL << DWT_FUNCTION_DATAVADDR1_Pos) |

| #define | DWT_FUNCTION_DATAVADDR1_Pos 16 |

| #define | DWT_FUNCTION_DATAVMATCH_Msk (0x1UL << DWT_FUNCTION_DATAVMATCH_Pos) |

| #define | DWT_FUNCTION_DATAVMATCH_Pos 8 |

| #define | DWT_FUNCTION_DATAVSIZE_Msk (0x3UL << DWT_FUNCTION_DATAVSIZE_Pos) |

| #define | DWT_FUNCTION_DATAVSIZE_Pos 10 |

| #define | DWT_FUNCTION_EMITRANGE_Msk (0x1UL << DWT_FUNCTION_EMITRANGE_Pos) |

| #define | DWT_FUNCTION_EMITRANGE_Pos 5 |

| #define | DWT_FUNCTION_FUNCTION_Msk (0xFUL << DWT_FUNCTION_FUNCTION_Pos) |

| #define | DWT_FUNCTION_FUNCTION_Pos 0 |

| #define | DWT_FUNCTION_LNK1ENA_Msk (0x1UL << DWT_FUNCTION_LNK1ENA_Pos) |

| #define | DWT_FUNCTION_LNK1ENA_Pos 9 |

| #define | DWT_FUNCTION_MATCHED_Msk (0x1UL << DWT_FUNCTION_MATCHED_Pos) |

| #define | DWT_FUNCTION_MATCHED_Pos 24 |

| #define | DWT_LSUCNT_LSUCNT_Msk (0xFFUL << DWT_LSUCNT_LSUCNT_Pos) |

| #define | DWT_LSUCNT_LSUCNT_Pos 0 |

| #define | DWT_MASK_MASK_Msk (0x1FUL << DWT_MASK_MASK_Pos) |

| #define | DWT_MASK_MASK_Pos 0 |

| #define | DWT_SLEEPCNT_SLEEPCNT_Msk (0xFFUL << DWT_SLEEPCNT_SLEEPCNT_Pos) |

| #define | DWT_SLEEPCNT_SLEEPCNT_Pos 0 |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | ITM_IMCR_INTEGRATION_Msk (1UL << ITM_IMCR_INTEGRATION_Pos) |

| #define | ITM_IMCR_INTEGRATION_Pos 0 |

| #define | ITM_IRR_ATREADYM_Msk (1UL << ITM_IRR_ATREADYM_Pos) |

| #define | ITM_IRR_ATREADYM_Pos 0 |

| #define | ITM_IWR_ATVALIDM_Msk (1UL << ITM_IWR_ATVALIDM_Pos) |

| #define | ITM_IWR_ATVALIDM_Pos 0 |

| #define | ITM_LSR_Access_Msk (1UL << ITM_LSR_Access_Pos) |

| #define | ITM_LSR_Access_Pos 1 |

| #define | ITM_LSR_ByteAcc_Msk (1UL << ITM_LSR_ByteAcc_Pos) |

| #define | ITM_LSR_ByteAcc_Pos 2 |

| #define | ITM_LSR_Present_Msk (1UL << ITM_LSR_Present_Pos) |

| #define | ITM_LSR_Present_Pos 0 |

| #define | ITM_RXBUFFER_EMPTY 0x5AA55AA5 |

| #define | ITM_TCR_BUSY_Msk (1UL << ITM_TCR_BUSY_Pos) |

| #define | ITM_TCR_BUSY_Pos 23 |

| #define | ITM_TCR_DWTENA_Msk (1UL << ITM_TCR_DWTENA_Pos) |

| #define | ITM_TCR_DWTENA_Pos 3 |

| #define | ITM_TCR_GTSFREQ_Msk (3UL << ITM_TCR_GTSFREQ_Pos) |

| #define | ITM_TCR_GTSFREQ_Pos 10 |

| #define | ITM_TCR_ITMENA_Msk (1UL << ITM_TCR_ITMENA_Pos) |

| #define | ITM_TCR_ITMENA_Pos 0 |

| #define | ITM_TCR_SWOENA_Msk (1UL << ITM_TCR_SWOENA_Pos) |

| #define | ITM_TCR_SWOENA_Pos 4 |

| #define | ITM_TCR_SYNCENA_Msk (1UL << ITM_TCR_SYNCENA_Pos) |

| #define | ITM_TCR_SYNCENA_Pos 2 |

| #define | ITM_TCR_TraceBusID_Msk (0x7FUL << ITM_TCR_TraceBusID_Pos) |

| #define | ITM_TCR_TraceBusID_Pos 16 |

| #define | ITM_TCR_TSENA_Msk (1UL << ITM_TCR_TSENA_Pos) |

| #define | ITM_TCR_TSENA_Pos 1 |

| #define | ITM_TCR_TSPrescale_Msk (3UL << ITM_TCR_TSPrescale_Pos) |

| #define | ITM_TCR_TSPrescale_Pos 8 |

| #define | ITM_TPR_PRIVMASK_Msk (0xFUL << ITM_TPR_PRIVMASK_Pos) |

| #define | ITM_TPR_PRIVMASK_Pos 0 |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | NVIC_STIR_INTID_Msk (0x1FFUL << NVIC_STIR_INTID_Pos) |

| #define | NVIC_STIR_INTID_Pos 0 |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SCB_ABFSR_AHBP_Msk (1UL << SCB_ABFSR_AHBP_Pos) |

| #define | SCB_ABFSR_AHBP_Pos 2 |

| #define | SCB_ABFSR_AXIM_Msk (1UL << SCB_ABFSR_AXIM_Pos) |

| #define | SCB_ABFSR_AXIM_Pos 3 |

| #define | SCB_ABFSR_AXIMTYPE_Msk (3UL << SCB_ABFSR_AXIMTYPE_Pos) |

| #define | SCB_ABFSR_AXIMTYPE_Pos 8 |

| #define | SCB_ABFSR_DTCM_Msk (1UL << SCB_ABFSR_DTCM_Pos) |

| #define | SCB_ABFSR_DTCM_Pos 1 |

| #define | SCB_ABFSR_EPPB_Msk (1UL << SCB_ABFSR_EPPB_Pos) |

| #define | SCB_ABFSR_EPPB_Pos 4 |

| #define | SCB_ABFSR_ITCM_Msk (1UL << SCB_ABFSR_ITCM_Pos) |

| #define | SCB_ABFSR_ITCM_Pos 0 |

| #define | SCB_AHBPCR_EN_Msk (1UL << SCB_AHBPCR_EN_Pos) |

| #define | SCB_AHBPCR_EN_Pos 0 |

| #define | SCB_AHBPCR_SZ_Msk (7UL << SCB_AHBPCR_SZ_Pos) |

| #define | SCB_AHBPCR_SZ_Pos 1 |

| #define | SCB_AHBSCR_CTL_Msk (3UL << SCB_AHBPCR_CTL_Pos) |

| #define | SCB_AHBSCR_CTL_Pos 0 |

| #define | SCB_AHBSCR_INITCOUNT_Msk (0x1FUL << SCB_AHBPCR_INITCOUNT_Pos) |

| #define | SCB_AHBSCR_INITCOUNT_Pos 11 |

| #define | SCB_AHBSCR_TPRI_Msk (0x1FFUL << SCB_AHBPCR_TPRI_Pos) |

| #define | SCB_AHBSCR_TPRI_Pos 2 |

| #define | SCB_AIRCR_ENDIANESS_Msk (1UL << SCB_AIRCR_ENDIANESS_Pos) |

| #define | SCB_AIRCR_ENDIANESS_Pos 15 |

| #define | SCB_AIRCR_PRIGROUP_Msk (7UL << SCB_AIRCR_PRIGROUP_Pos) |

| #define | SCB_AIRCR_PRIGROUP_Pos 8 |

| #define | SCB_AIRCR_SYSRESETREQ_Msk (1UL << SCB_AIRCR_SYSRESETREQ_Pos) |

| #define | SCB_AIRCR_SYSRESETREQ_Pos 2 |

| #define | SCB_AIRCR_VECTCLRACTIVE_Msk (1UL << SCB_AIRCR_VECTCLRACTIVE_Pos) |

| #define | SCB_AIRCR_VECTCLRACTIVE_Pos 1 |

| #define | SCB_AIRCR_VECTKEY_Msk (0xFFFFUL << SCB_AIRCR_VECTKEY_Pos) |

| #define | SCB_AIRCR_VECTKEY_Pos 16 |

| #define | SCB_AIRCR_VECTKEYSTAT_Msk (0xFFFFUL << SCB_AIRCR_VECTKEYSTAT_Pos) |

| #define | SCB_AIRCR_VECTKEYSTAT_Pos 16 |

| #define | SCB_AIRCR_VECTRESET_Msk (1UL << SCB_AIRCR_VECTRESET_Pos) |

| #define | SCB_AIRCR_VECTRESET_Pos 0 |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB_CACR_ECCEN_Msk (1UL << SCB_CACR_ECCEN_Pos) |

| #define | SCB_CACR_ECCEN_Pos 1 |

| #define | SCB_CACR_FORCEWT_Msk (1UL << SCB_CACR_FORCEWT_Pos) |

| #define | SCB_CACR_FORCEWT_Pos 2 |

| #define | SCB_CACR_SIWT_Msk (1UL << SCB_CACR_SIWT_Pos) |

| #define | SCB_CACR_SIWT_Pos 0 |

| #define | SCB_CCR_BFHFNMIGN_Msk (1UL << SCB_CCR_BFHFNMIGN_Pos) |

| #define | SCB_CCR_BFHFNMIGN_Pos 8 |

| #define | SCB_CCR_BP_Msk (1UL << SCB_CCR_BP_Pos) |

| #define | SCB_CCR_BP_Pos 18 |

| #define | SCB_CCR_DC_Msk (1UL << SCB_CCR_DC_Pos) |

| #define | SCB_CCR_DC_Pos 16 |

| #define | SCB_CCR_DIV_0_TRP_Msk (1UL << SCB_CCR_DIV_0_TRP_Pos) |

| #define | SCB_CCR_DIV_0_TRP_Pos 4 |

| #define | SCB_CCR_IC_Msk (1UL << SCB_CCR_IC_Pos) |

| #define | SCB_CCR_IC_Pos 17 |

| #define | SCB_CCR_NONBASETHRDENA_Msk (1UL << SCB_CCR_NONBASETHRDENA_Pos) |

| #define | SCB_CCR_NONBASETHRDENA_Pos 0 |

| #define | SCB_CCR_STKALIGN_Msk (1UL << SCB_CCR_STKALIGN_Pos) |

| #define | SCB_CCR_STKALIGN_Pos 9 |

| #define | SCB_CCR_UNALIGN_TRP_Msk (1UL << SCB_CCR_UNALIGN_TRP_Pos) |

| #define | SCB_CCR_UNALIGN_TRP_Pos 3 |

| #define | SCB_CCR_USERSETMPEND_Msk (1UL << SCB_CCR_USERSETMPEND_Pos) |

| #define | SCB_CCR_USERSETMPEND_Pos 1 |

| #define | SCB_CCSIDR_ASSOCIATIVITY_Msk (0x3FFUL << SCB_CCSIDR_ASSOCIATIVITY_Pos) |

| #define | SCB_CCSIDR_ASSOCIATIVITY_Pos 3 |

| #define | SCB_CCSIDR_LINESIZE_Msk (7UL << SCB_CCSIDR_LINESIZE_Pos) |

| #define | SCB_CCSIDR_LINESIZE_Pos 0 |

| #define | SCB_CCSIDR_NUMSETS_Msk (0x7FFFUL << SCB_CCSIDR_NUMSETS_Pos) |

| #define | SCB_CCSIDR_NUMSETS_Pos 13 |

| #define | SCB_CCSIDR_RA_Msk (7UL << SCB_CCSIDR_RA_Pos) |

| #define | SCB_CCSIDR_RA_Pos 29 |

| #define | SCB_CCSIDR_WA_Msk (7UL << SCB_CCSIDR_WA_Pos) |

| #define | SCB_CCSIDR_WA_Pos 28 |

| #define | SCB_CCSIDR_WB_Msk (7UL << SCB_CCSIDR_WB_Pos) |

| #define | SCB_CCSIDR_WB_Pos 30 |

| #define | SCB_CCSIDR_WT_Msk (7UL << SCB_CCSIDR_WT_Pos) |

| #define | SCB_CCSIDR_WT_Pos 31 |

| #define | SCB_CFSR_BUSFAULTSR_Msk (0xFFUL << SCB_CFSR_BUSFAULTSR_Pos) |

| #define | SCB_CFSR_BUSFAULTSR_Pos 8 |

| #define | SCB_CFSR_MEMFAULTSR_Msk (0xFFUL << SCB_CFSR_MEMFAULTSR_Pos) |

| #define | SCB_CFSR_MEMFAULTSR_Pos 0 |

| #define | SCB_CFSR_USGFAULTSR_Msk (0xFFFFUL << SCB_CFSR_USGFAULTSR_Pos) |

| #define | SCB_CFSR_USGFAULTSR_Pos 16 |

| #define | SCB_CLIDR_LOC_Msk (7UL << SCB_CLIDR_FORMAT_Pos) |

| #define | SCB_CLIDR_LOC_Pos 24 |

| #define | SCB_CLIDR_LOUU_Msk (7UL << SCB_CLIDR_LOUU_Pos) |

| #define | SCB_CLIDR_LOUU_Pos 27 |

| #define | SCB_CPUID_ARCHITECTURE_Msk (0xFUL << SCB_CPUID_ARCHITECTURE_Pos) |

| #define | SCB_CPUID_ARCHITECTURE_Pos 16 |

| #define | SCB_CPUID_IMPLEMENTER_Msk (0xFFUL << SCB_CPUID_IMPLEMENTER_Pos) |

| #define | SCB_CPUID_IMPLEMENTER_Pos 24 |

| #define | SCB_CPUID_PARTNO_Msk (0xFFFUL << SCB_CPUID_PARTNO_Pos) |

| #define | SCB_CPUID_PARTNO_Pos 4 |

| #define | SCB_CPUID_REVISION_Msk (0xFUL << SCB_CPUID_REVISION_Pos) |

| #define | SCB_CPUID_REVISION_Pos 0 |

| #define | SCB_CPUID_VARIANT_Msk (0xFUL << SCB_CPUID_VARIANT_Pos) |

| #define | SCB_CPUID_VARIANT_Pos 20 |

| #define | SCB_CSSELR_IND_Msk (1UL << SCB_CSSELR_IND_Pos) |

| #define | SCB_CSSELR_IND_Pos 0 |

| #define | SCB_CSSELR_LEVEL_Msk (1UL << SCB_CSSELR_LEVEL_Pos) |

| #define | SCB_CSSELR_LEVEL_Pos 0 |

| #define | SCB_CTR_CWG_Msk (0xFUL << SCB_CTR_CWG_Pos) |

| #define | SCB_CTR_CWG_Pos 24 |

| #define | SCB_CTR_DMINLINE_Msk (0xFUL << SCB_CTR_DMINLINE_Pos) |

| #define | SCB_CTR_DMINLINE_Pos 16 |

| #define | SCB_CTR_ERG_Msk (0xFUL << SCB_CTR_ERG_Pos) |

| #define | SCB_CTR_ERG_Pos 20 |

| #define | SCB_CTR_FORMAT_Msk (7UL << SCB_CTR_FORMAT_Pos) |

| #define | SCB_CTR_FORMAT_Pos 29 |

| #define | SCB_CTR_IMINLINE_Msk (0xFUL << SCB_CTR_IMINLINE_Pos) |

| #define | SCB_CTR_IMINLINE_Pos 0 |

| #define | SCB_DFSR_BKPT_Msk (1UL << SCB_DFSR_BKPT_Pos) |

| #define | SCB_DFSR_BKPT_Pos 1 |

| #define | SCB_DFSR_DWTTRAP_Msk (1UL << SCB_DFSR_DWTTRAP_Pos) |

| #define | SCB_DFSR_DWTTRAP_Pos 2 |

| #define | SCB_DFSR_EXTERNAL_Msk (1UL << SCB_DFSR_EXTERNAL_Pos) |

| #define | SCB_DFSR_EXTERNAL_Pos 4 |

| #define | SCB_DFSR_HALTED_Msk (1UL << SCB_DFSR_HALTED_Pos) |

| #define | SCB_DFSR_HALTED_Pos 0 |

| #define | SCB_DFSR_VCATCH_Msk (1UL << SCB_DFSR_VCATCH_Pos) |

| #define | SCB_DFSR_VCATCH_Pos 3 |

| #define | SCB_DTCMCR_EN_Msk (1UL << SCB_DTCMCR_EN_Pos) |

| #define | SCB_DTCMCR_EN_Pos 0 |

| #define | SCB_DTCMCR_RETEN_Msk (1UL << SCB_DTCMCR_RETEN_Pos) |

| #define | SCB_DTCMCR_RETEN_Pos 2 |

| #define | SCB_DTCMCR_RMW_Msk (1UL << SCB_DTCMCR_RMW_Pos) |

| #define | SCB_DTCMCR_RMW_Pos 1 |

| #define | SCB_DTCMCR_SZ_Msk (0xFUL << SCB_DTCMCR_SZ_Pos) |

| #define | SCB_DTCMCR_SZ_Pos 3 |

| #define | SCB_HFSR_DEBUGEVT_Msk (1UL << SCB_HFSR_DEBUGEVT_Pos) |

| #define | SCB_HFSR_DEBUGEVT_Pos 31 |

| #define | SCB_HFSR_FORCED_Msk (1UL << SCB_HFSR_FORCED_Pos) |

| #define | SCB_HFSR_FORCED_Pos 30 |

| #define | SCB_HFSR_VECTTBL_Msk (1UL << SCB_HFSR_VECTTBL_Pos) |

| #define | SCB_HFSR_VECTTBL_Pos 1 |

| #define | SCB_ICSR_ISRPENDING_Msk (1UL << SCB_ICSR_ISRPENDING_Pos) |

| #define | SCB_ICSR_ISRPENDING_Pos 22 |

| #define | SCB_ICSR_ISRPREEMPT_Msk (1UL << SCB_ICSR_ISRPREEMPT_Pos) |

| #define | SCB_ICSR_ISRPREEMPT_Pos 23 |

| #define | SCB_ICSR_NMIPENDSET_Msk (1UL << SCB_ICSR_NMIPENDSET_Pos) |

| #define | SCB_ICSR_NMIPENDSET_Pos 31 |

| #define | SCB_ICSR_PENDSTCLR_Msk (1UL << SCB_ICSR_PENDSTCLR_Pos) |

| #define | SCB_ICSR_PENDSTCLR_Pos 25 |

| #define | SCB_ICSR_PENDSTSET_Msk (1UL << SCB_ICSR_PENDSTSET_Pos) |

| #define | SCB_ICSR_PENDSTSET_Pos 26 |

| #define | SCB_ICSR_PENDSVCLR_Msk (1UL << SCB_ICSR_PENDSVCLR_Pos) |

| #define | SCB_ICSR_PENDSVCLR_Pos 27 |

| #define | SCB_ICSR_PENDSVSET_Msk (1UL << SCB_ICSR_PENDSVSET_Pos) |

| #define | SCB_ICSR_PENDSVSET_Pos 28 |

| #define | SCB_ICSR_RETTOBASE_Msk (1UL << SCB_ICSR_RETTOBASE_Pos) |

| #define | SCB_ICSR_RETTOBASE_Pos 11 |

| #define | SCB_ICSR_VECTACTIVE_Msk (0x1FFUL << SCB_ICSR_VECTACTIVE_Pos) |

| #define | SCB_ICSR_VECTACTIVE_Pos 0 |

| #define | SCB_ICSR_VECTPENDING_Msk (0x1FFUL << SCB_ICSR_VECTPENDING_Pos) |

| #define | SCB_ICSR_VECTPENDING_Pos 12 |

| #define | SCB_ITCMCR_EN_Msk (1FFUL << SCB_ITCMCR_EN_Pos) |

| #define | SCB_ITCMCR_EN_Pos 0 |

| #define | SCB_ITCMCR_RETEN_Msk (1FFUL << SCB_ITCMCR_RETEN_Pos) |

| #define | SCB_ITCMCR_RETEN_Pos 2 |

| #define | SCB_ITCMCR_RMW_Msk (1FFUL << SCB_ITCMCR_RMW_Pos) |

| #define | SCB_ITCMCR_RMW_Pos 1 |

| #define | SCB_ITCMCR_SZ_Msk (0xFUL << SCB_ITCMCR_SZ_Pos) |

| #define | SCB_ITCMCR_SZ_Pos 3 |

| #define | SCB_SCR_SEVONPEND_Msk (1UL << SCB_SCR_SEVONPEND_Pos) |

| #define | SCB_SCR_SEVONPEND_Pos 4 |

| #define | SCB_SCR_SLEEPDEEP_Msk (1UL << SCB_SCR_SLEEPDEEP_Pos) |

| #define | SCB_SCR_SLEEPDEEP_Pos 2 |

| #define | SCB_SCR_SLEEPONEXIT_Msk (1UL << SCB_SCR_SLEEPONEXIT_Pos) |

| #define | SCB_SCR_SLEEPONEXIT_Pos 1 |

| #define | SCB_SHCSR_BUSFAULTACT_Msk (1UL << SCB_SHCSR_BUSFAULTACT_Pos) |

| #define | SCB_SHCSR_BUSFAULTACT_Pos 1 |

| #define | SCB_SHCSR_BUSFAULTENA_Msk (1UL << SCB_SHCSR_BUSFAULTENA_Pos) |

| #define | SCB_SHCSR_BUSFAULTENA_Pos 17 |

| #define | SCB_SHCSR_BUSFAULTPENDED_Msk (1UL << SCB_SHCSR_BUSFAULTPENDED_Pos) |

| #define | SCB_SHCSR_BUSFAULTPENDED_Pos 14 |

| #define | SCB_SHCSR_MEMFAULTACT_Msk (1UL << SCB_SHCSR_MEMFAULTACT_Pos) |

| #define | SCB_SHCSR_MEMFAULTACT_Pos 0 |

| #define | SCB_SHCSR_MEMFAULTENA_Msk (1UL << SCB_SHCSR_MEMFAULTENA_Pos) |

| #define | SCB_SHCSR_MEMFAULTENA_Pos 16 |

| #define | SCB_SHCSR_MEMFAULTPENDED_Msk (1UL << SCB_SHCSR_MEMFAULTPENDED_Pos) |

| #define | SCB_SHCSR_MEMFAULTPENDED_Pos 13 |

| #define | SCB_SHCSR_MONITORACT_Msk (1UL << SCB_SHCSR_MONITORACT_Pos) |

| #define | SCB_SHCSR_MONITORACT_Pos 8 |

| #define | SCB_SHCSR_PENDSVACT_Msk (1UL << SCB_SHCSR_PENDSVACT_Pos) |

| #define | SCB_SHCSR_PENDSVACT_Pos 10 |

| #define | SCB_SHCSR_SVCALLACT_Msk (1UL << SCB_SHCSR_SVCALLACT_Pos) |

| #define | SCB_SHCSR_SVCALLACT_Pos 7 |

| #define | SCB_SHCSR_SVCALLPENDED_Msk (1UL << SCB_SHCSR_SVCALLPENDED_Pos) |

| #define | SCB_SHCSR_SVCALLPENDED_Pos 15 |

| #define | SCB_SHCSR_SYSTICKACT_Msk (1UL << SCB_SHCSR_SYSTICKACT_Pos) |

| #define | SCB_SHCSR_SYSTICKACT_Pos 11 |

| #define | SCB_SHCSR_USGFAULTACT_Msk (1UL << SCB_SHCSR_USGFAULTACT_Pos) |

| #define | SCB_SHCSR_USGFAULTACT_Pos 3 |

| #define | SCB_SHCSR_USGFAULTENA_Msk (1UL << SCB_SHCSR_USGFAULTENA_Pos) |

| #define | SCB_SHCSR_USGFAULTENA_Pos 18 |

| #define | SCB_SHCSR_USGFAULTPENDED_Msk (1UL << SCB_SHCSR_USGFAULTPENDED_Pos) |

| #define | SCB_SHCSR_USGFAULTPENDED_Pos 12 |

| #define | SCB_STIR_INTID_Msk (0x1FFUL << SCB_STIR_INTID_Pos) |

| #define | SCB_STIR_INTID_Pos 0 |

| #define | SCB_VTOR_TBLOFF_Msk (0x1FFFFFFUL << SCB_VTOR_TBLOFF_Pos) |

| #define | SCB_VTOR_TBLOFF_Pos 7 |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCnSCB_ACTLR_DISFOLD_Msk (1UL << SCnSCB_ACTLR_DISFOLD_Pos) |

| #define | SCnSCB_ACTLR_DISFOLD_Pos 2 |

| #define | SCnSCB_ACTLR_DISITMATBFLUSH_Msk (1UL << SCnSCB_ACTLR_DISITMATBFLUSH_Pos) |

| #define | SCnSCB_ACTLR_DISITMATBFLUSH_Pos 12 |

| #define | SCnSCB_ACTLR_DISMCYCINT_Msk (1UL << SCnSCB_ACTLR_DISMCYCINT_Pos) |

| #define | SCnSCB_ACTLR_DISMCYCINT_Pos 0 |

| #define | SCnSCB_ACTLR_DISRAMODE_Msk (1UL << SCnSCB_ACTLR_DISRAMODE_Pos) |

| #define | SCnSCB_ACTLR_DISRAMODE_Pos 11 |

| #define | SCnSCB_ACTLR_FPEXCODIS_Msk (1UL << SCnSCB_ACTLR_FPEXCODIS_Pos) |

| #define | SCnSCB_ACTLR_FPEXCODIS_Pos 10 |

| #define | SCnSCB_ICTR_INTLINESNUM_Msk (0xFUL << SCnSCB_ICTR_INTLINESNUM_Pos) |

| #define | SCnSCB_ICTR_INTLINESNUM_Pos 0 |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | SysTick_CALIB_NOREF_Msk (1UL << SysTick_CALIB_NOREF_Pos) |

| #define | SysTick_CALIB_NOREF_Pos 31 |

| #define | SysTick_CALIB_SKEW_Msk (1UL << SysTick_CALIB_SKEW_Pos) |

| #define | SysTick_CALIB_SKEW_Pos 30 |

| #define | SysTick_CALIB_TENMS_Msk (0xFFFFFFUL << SysTick_CALIB_TENMS_Pos) |

| #define | SysTick_CALIB_TENMS_Pos 0 |

| #define | SysTick_CTRL_CLKSOURCE_Msk (1UL << SysTick_CTRL_CLKSOURCE_Pos) |

| #define | SysTick_CTRL_CLKSOURCE_Pos 2 |

| #define | SysTick_CTRL_COUNTFLAG_Msk (1UL << SysTick_CTRL_COUNTFLAG_Pos) |

| #define | SysTick_CTRL_COUNTFLAG_Pos 16 |

| #define | SysTick_CTRL_ENABLE_Msk (1UL << SysTick_CTRL_ENABLE_Pos) |

| #define | SysTick_CTRL_ENABLE_Pos 0 |

| #define | SysTick_CTRL_TICKINT_Msk (1UL << SysTick_CTRL_TICKINT_Pos) |

| #define | SysTick_CTRL_TICKINT_Pos 1 |

| #define | SysTick_LOAD_RELOAD_Msk (0xFFFFFFUL << SysTick_LOAD_RELOAD_Pos) |

| #define | SysTick_LOAD_RELOAD_Pos 0 |

| #define | SysTick_VAL_CURRENT_Msk (0xFFFFFFUL << SysTick_VAL_CURRENT_Pos) |

| #define | SysTick_VAL_CURRENT_Pos 0 |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | TPI_ACPR_PRESCALER_Msk (0x1FFFUL << TPI_ACPR_PRESCALER_Pos) |

| #define | TPI_ACPR_PRESCALER_Pos 0 |

| #define | TPI_BASE (0xE0040000UL) |

| #define | TPI_DEVID_AsynClkIn_Msk (0x1UL << TPI_DEVID_AsynClkIn_Pos) |

| #define | TPI_DEVID_AsynClkIn_Pos 5 |

| #define | TPI_DEVID_MANCVALID_Msk (0x1UL << TPI_DEVID_MANCVALID_Pos) |

| #define | TPI_DEVID_MANCVALID_Pos 10 |

| #define | TPI_DEVID_MinBufSz_Msk (0x7UL << TPI_DEVID_MinBufSz_Pos) |

| #define | TPI_DEVID_MinBufSz_Pos 6 |

| #define | TPI_DEVID_NrTraceInput_Msk (0x1FUL << TPI_DEVID_NrTraceInput_Pos) |

| #define | TPI_DEVID_NrTraceInput_Pos 0 |

| #define | TPI_DEVID_NRZVALID_Msk (0x1UL << TPI_DEVID_NRZVALID_Pos) |

| #define | TPI_DEVID_NRZVALID_Pos 11 |

| #define | TPI_DEVID_PTINVALID_Msk (0x1UL << TPI_DEVID_PTINVALID_Pos) |

| #define | TPI_DEVID_PTINVALID_Pos 9 |

| #define | TPI_DEVTYPE_MajorType_Msk (0xFUL << TPI_DEVTYPE_MajorType_Pos) |

| #define | TPI_DEVTYPE_MajorType_Pos 4 |

| #define | TPI_DEVTYPE_SubType_Msk (0xFUL << TPI_DEVTYPE_SubType_Pos) |

| #define | TPI_DEVTYPE_SubType_Pos 0 |

| #define | TPI_FFCR_EnFCont_Msk (0x1UL << TPI_FFCR_EnFCont_Pos) |

| #define | TPI_FFCR_EnFCont_Pos 1 |

| #define | TPI_FFCR_TrigIn_Msk (0x1UL << TPI_FFCR_TrigIn_Pos) |

| #define | TPI_FFCR_TrigIn_Pos 8 |

| #define | TPI_FFSR_FlInProg_Msk (0x1UL << TPI_FFSR_FlInProg_Pos) |

| #define | TPI_FFSR_FlInProg_Pos 0 |

| #define | TPI_FFSR_FtNonStop_Msk (0x1UL << TPI_FFSR_FtNonStop_Pos) |

| #define | TPI_FFSR_FtNonStop_Pos 3 |

| #define | TPI_FFSR_FtStopped_Msk (0x1UL << TPI_FFSR_FtStopped_Pos) |

| #define | TPI_FFSR_FtStopped_Pos 1 |

| #define | TPI_FFSR_TCPresent_Msk (0x1UL << TPI_FFSR_TCPresent_Pos) |

| #define | TPI_FFSR_TCPresent_Pos 2 |

| #define | TPI_FIFO0_ETM0_Msk (0xFFUL << TPI_FIFO0_ETM0_Pos) |

| #define | TPI_FIFO0_ETM0_Pos 0 |

| #define | TPI_FIFO0_ETM1_Msk (0xFFUL << TPI_FIFO0_ETM1_Pos) |

| #define | TPI_FIFO0_ETM1_Pos 8 |

| #define | TPI_FIFO0_ETM2_Msk (0xFFUL << TPI_FIFO0_ETM2_Pos) |

| #define | TPI_FIFO0_ETM2_Pos 16 |

| #define | TPI_FIFO0_ETM_ATVALID_Msk (0x3UL << TPI_FIFO0_ETM_ATVALID_Pos) |

| #define | TPI_FIFO0_ETM_ATVALID_Pos 26 |

| #define | TPI_FIFO0_ETM_bytecount_Msk (0x3UL << TPI_FIFO0_ETM_bytecount_Pos) |

| #define | TPI_FIFO0_ETM_bytecount_Pos 24 |

| #define | TPI_FIFO0_ITM_ATVALID_Msk (0x3UL << TPI_FIFO0_ITM_ATVALID_Pos) |

| #define | TPI_FIFO0_ITM_ATVALID_Pos 29 |

| #define | TPI_FIFO0_ITM_bytecount_Msk (0x3UL << TPI_FIFO0_ITM_bytecount_Pos) |

| #define | TPI_FIFO0_ITM_bytecount_Pos 27 |

| #define | TPI_FIFO1_ETM_ATVALID_Msk (0x3UL << TPI_FIFO1_ETM_ATVALID_Pos) |

| #define | TPI_FIFO1_ETM_ATVALID_Pos 26 |

| #define | TPI_FIFO1_ETM_bytecount_Msk (0x3UL << TPI_FIFO1_ETM_bytecount_Pos) |

| #define | TPI_FIFO1_ETM_bytecount_Pos 24 |

| #define | TPI_FIFO1_ITM0_Msk (0xFFUL << TPI_FIFO1_ITM0_Pos) |

| #define | TPI_FIFO1_ITM0_Pos 0 |

| #define | TPI_FIFO1_ITM1_Msk (0xFFUL << TPI_FIFO1_ITM1_Pos) |

| #define | TPI_FIFO1_ITM1_Pos 8 |

| #define | TPI_FIFO1_ITM2_Msk (0xFFUL << TPI_FIFO1_ITM2_Pos) |

| #define | TPI_FIFO1_ITM2_Pos 16 |

| #define | TPI_FIFO1_ITM_ATVALID_Msk (0x3UL << TPI_FIFO1_ITM_ATVALID_Pos) |

| #define | TPI_FIFO1_ITM_ATVALID_Pos 29 |

| #define | TPI_FIFO1_ITM_bytecount_Msk (0x3UL << TPI_FIFO1_ITM_bytecount_Pos) |

| #define | TPI_FIFO1_ITM_bytecount_Pos 27 |

| #define | TPI_ITATBCTR0_ATREADY_Msk (0x1UL << TPI_ITATBCTR0_ATREADY_Pos) |

| #define | TPI_ITATBCTR0_ATREADY_Pos 0 |

| #define | TPI_ITATBCTR2_ATREADY_Msk (0x1UL << TPI_ITATBCTR2_ATREADY_Pos) |

| #define | TPI_ITATBCTR2_ATREADY_Pos 0 |

| #define | TPI_ITCTRL_Mode_Msk (0x1UL << TPI_ITCTRL_Mode_Pos) |

| #define | TPI_ITCTRL_Mode_Pos 0 |

| #define | TPI_SPPR_TXMODE_Msk (0x3UL << TPI_SPPR_TXMODE_Pos) |

| #define | TPI_SPPR_TXMODE_Pos 0 |

| #define | TPI_TRIGGER_TRIGGER_Msk (0x1UL << TPI_TRIGGER_TRIGGER_Pos) |

| #define | TPI_TRIGGER_TRIGGER_Pos 0 |

| #define | __CM7_CMSIS_VERSION_MAIN (0x04) |

| #define | __CM7_CMSIS_VERSION_SUB (0x00) |

| #define | __CM7_CMSIS_VERSION |

| #define | __CORTEX_M (0x07) |

| #define | __CORE_CM7_H_DEPENDANT |

| #define | __I volatile const |

| #define | __O volatile |

| #define | __IO volatile |

Functions | |

| __STATIC_INLINE int32_t | ITM_CheckChar (void) |

| ITM Check Character. More... | |

| __STATIC_INLINE int32_t | ITM_ReceiveChar (void) |

| ITM Receive Character. More... | |

| __STATIC_INLINE uint32_t | ITM_SendChar (uint32_t ch) |

| ITM Send Character. More... | |

| __STATIC_INLINE void | NVIC_ClearPendingIRQ (IRQn_Type IRQn) |

| Clear Pending Interrupt. More... | |

| __STATIC_INLINE void | NVIC_DecodePriority (uint32_t Priority, uint32_t PriorityGroup, uint32_t *pPreemptPriority, uint32_t *pSubPriority) |

| Decode Priority. More... | |

| __STATIC_INLINE void | NVIC_DisableIRQ (IRQn_Type IRQn) |

| Disable External Interrupt. More... | |

| __STATIC_INLINE void | NVIC_EnableIRQ (IRQn_Type IRQn) |

| Enable External Interrupt. More... | |

| __STATIC_INLINE uint32_t | NVIC_EncodePriority (uint32_t PriorityGroup, uint32_t PreemptPriority, uint32_t SubPriority) |

| Encode Priority. More... | |

| __STATIC_INLINE uint32_t | NVIC_GetActive (IRQn_Type IRQn) |

| Get Active Interrupt. More... | |

| __STATIC_INLINE uint32_t | NVIC_GetPendingIRQ (IRQn_Type IRQn) |

| Get Pending Interrupt. More... | |

| __STATIC_INLINE uint32_t | NVIC_GetPriority (IRQn_Type IRQn) |

| Get Interrupt Priority. More... | |

| __STATIC_INLINE uint32_t | NVIC_GetPriorityGrouping (void) |

| Get Priority Grouping. More... | |

| __STATIC_INLINE void | NVIC_SetPendingIRQ (IRQn_Type IRQn) |

| Set Pending Interrupt. More... | |

| __STATIC_INLINE void | NVIC_SetPriority (IRQn_Type IRQn, uint32_t priority) |

| Set Interrupt Priority. More... | |

| __STATIC_INLINE void | NVIC_SetPriorityGrouping (uint32_t PriorityGroup) |

| Set Priority Grouping. More... | |

| __STATIC_INLINE void | NVIC_SystemReset (void) |

| System Reset. More... | |

| __STATIC_INLINE void | SCB_CleanDCache (void) |

| Clean D-Cache. More... | |

| __STATIC_INLINE void | SCB_CleanInvalidateDCache (void) |

| Clean & Invalidate D-Cache. More... | |

| __STATIC_INLINE void | SCB_DisableDCache (void) |

| Disable D-Cache. More... | |

| __STATIC_INLINE void | SCB_DisableICache (void) |

| Disable I-Cache. More... | |

| __STATIC_INLINE void | SCB_EnableDCache (void) |

| Enable D-Cache. More... | |

| __STATIC_INLINE void | SCB_EnableICache (void) |

| Enable I-Cache. More... | |

| __STATIC_INLINE void | SCB_InvalidateDCache (void) |

| Invalidate D-Cache. More... | |

| __STATIC_INLINE void | SCB_InvalidateICache (void) |

| Invalidate I-Cache. More... | |

| __STATIC_INLINE uint32_t | SysTick_Config (uint32_t ticks) |

| System Tick Configuration. More... | |

Variables | |

| volatile int32_t | ITM_RxBuffer |

Detailed Description

CMSIS Cortex-M7 Core Peripheral Access Layer Header File.

- Version

- V4.00

- Date

- 01. September 2014

- Note

Definition in file core_cm7.h.

Macro Definition Documentation

| #define __CM7_CMSIS_VERSION |

CMSIS HAL version number

Definition at line 73 of file core_cm7.h.

| #define __CM7_CMSIS_VERSION_MAIN (0x04) |

[31:16] CMSIS HAL main version

Definition at line 71 of file core_cm7.h.

| #define __CM7_CMSIS_VERSION_SUB (0x00) |

[15:0] CMSIS HAL sub version

Definition at line 72 of file core_cm7.h.

| #define __CORE_CM7_H_DEPENDANT |

__FPU_USED indicates whether an FPU is used or not. For this, __FPU_PRESENT has to be checked prior to making use of FPU specific registers and functions.

Definition at line 201 of file core_cm7.h.

| #define __CORE_CM7_H_GENERIC |

Definition at line 43 of file core_cm7.h.

| #define __CORTEX_M (0x07) |

Cortex-M Core

Definition at line 76 of file core_cm7.h.

| #define __I volatile const |

Defines 'read only' permissions

Definition at line 261 of file core_cm7.h.

| #define __IO volatile |

Defines 'read / write' permissions

Definition at line 264 of file core_cm7.h.

| #define __O volatile |

Defines 'write only' permissions

Definition at line 263 of file core_cm7.h.