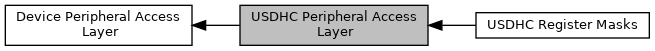

Collaboration diagram for USDHC Peripheral Access Layer:

Modules | |

| USDHC Register Masks | |

Classes | |

| struct | USDHC_Type |

Macros | |

| #define | USDHC1 ((USDHC_Type *)USDHC1_BASE) |

| #define | USDHC1_BASE (0x402C0000u) |

| #define | USDHC2 ((USDHC_Type *)USDHC2_BASE) |

| #define | USDHC2_BASE (0x402C4000u) |

| #define | USDHC_BASE_ADDRS { 0u, USDHC1_BASE, USDHC2_BASE } |

| #define | USDHC_BASE_PTRS { (USDHC_Type *)0u, USDHC1, USDHC2 } |

| #define | USDHC_IRQS { NotAvail_IRQn, USDHC1_IRQn, USDHC2_IRQn } |

Detailed Description

Macro Definition Documentation

◆ USDHC1

| #define USDHC1 ((USDHC_Type *)USDHC1_BASE) |

Peripheral USDHC1 base pointer

Definition at line 43909 of file MIMXRT1052.h.

◆ USDHC1_BASE

| #define USDHC1_BASE (0x402C0000u) |

Peripheral USDHC1 base address

Definition at line 43907 of file MIMXRT1052.h.

◆ USDHC2

| #define USDHC2 ((USDHC_Type *)USDHC2_BASE) |

Peripheral USDHC2 base pointer

Definition at line 43913 of file MIMXRT1052.h.

◆ USDHC2_BASE

| #define USDHC2_BASE (0x402C4000u) |

Peripheral USDHC2 base address

Definition at line 43911 of file MIMXRT1052.h.

◆ USDHC_BASE_ADDRS

| #define USDHC_BASE_ADDRS { 0u, USDHC1_BASE, USDHC2_BASE } |

Array initializer of USDHC peripheral base addresses

Definition at line 43915 of file MIMXRT1052.h.

◆ USDHC_BASE_PTRS

| #define USDHC_BASE_PTRS { (USDHC_Type *)0u, USDHC1, USDHC2 } |

Array initializer of USDHC peripheral base pointers

Definition at line 43917 of file MIMXRT1052.h.

◆ USDHC_IRQS

| #define USDHC_IRQS { NotAvail_IRQn, USDHC1_IRQn, USDHC2_IRQn } |

Interrupt vectors for the USDHC peripheral type

Definition at line 43919 of file MIMXRT1052.h.