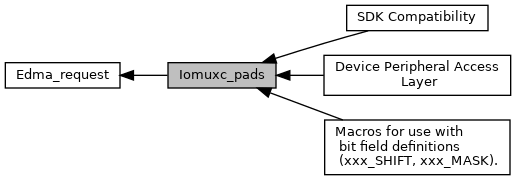

Modules | |

| Device Peripheral Access Layer | |

| Macros for use with bit field definitions (xxx_SHIFT, xxx_MASK). | |

| SDK Compatibility | |

Typedefs | |

| typedef enum _iomuxc_select_input | iomuxc_select_input_t |

| Enumeration for the IOMUXC select input. More... | |

| typedef enum _iomuxc_sw_mux_ctl_pad | iomuxc_sw_mux_ctl_pad_t |

| Enumeration for the IOMUXC SW_MUX_CTL_PAD. More... | |

| typedef enum _iomuxc_sw_pad_ctl_pad | iomuxc_sw_pad_ctl_pad_t |

| Enumeration for the IOMUXC SW_PAD_CTL_PAD. More... | |

| typedef enum _xbar_input_signal | xbar_input_signal_t |

| typedef enum _xbar_output_signal | xbar_output_signal_t |

Detailed Description

Typedef Documentation

◆ iomuxc_select_input_t

| typedef enum _iomuxc_select_input iomuxc_select_input_t |

Enumeration for the IOMUXC select input.

Defines the enumeration for the IOMUXC select input collections.

◆ iomuxc_sw_mux_ctl_pad_t

| typedef enum _iomuxc_sw_mux_ctl_pad iomuxc_sw_mux_ctl_pad_t |

Enumeration for the IOMUXC SW_MUX_CTL_PAD.

Defines the enumeration for the IOMUXC SW_MUX_CTL_PAD collections.

◆ iomuxc_sw_pad_ctl_pad_t

| typedef enum _iomuxc_sw_pad_ctl_pad iomuxc_sw_pad_ctl_pad_t |

Enumeration for the IOMUXC SW_PAD_CTL_PAD.

Defines the enumeration for the IOMUXC SW_PAD_CTL_PAD collections.

◆ xbar_input_signal_t

| typedef enum _xbar_input_signal xbar_input_signal_t |

◆ xbar_output_signal_t

| typedef enum _xbar_output_signal xbar_output_signal_t |

Enumeration Type Documentation

◆ _iomuxc_select_input

| enum _iomuxc_select_input |

Enumeration for the IOMUXC select input.

Defines the enumeration for the IOMUXC select input collections.

Definition at line 715 of file MIMXRT1052.h.

◆ _iomuxc_sw_mux_ctl_pad

Enumeration for the IOMUXC SW_MUX_CTL_PAD.

Defines the enumeration for the IOMUXC SW_MUX_CTL_PAD collections.

Definition at line 437 of file MIMXRT1052.h.

◆ _iomuxc_sw_pad_ctl_pad

Enumeration for the IOMUXC SW_PAD_CTL_PAD.

Defines the enumeration for the IOMUXC SW_PAD_CTL_PAD collections.

Definition at line 580 of file MIMXRT1052.h.

◆ _xbar_input_signal

| enum _xbar_input_signal |

Definition at line 873 of file MIMXRT1052.h.

◆ _xbar_output_signal

| enum _xbar_output_signal |

Definition at line 1081 of file MIMXRT1052.h.

Variable Documentation

◆ @306

| union { ... } |

◆ @308

| union { ... } |

◆ @310

| union { ... } |

◆ @316

| union { ... } |

◆ @319

| union { ... } |

◆ @321

| union { ... } |

◆ @323

| union { ... } |

◆ @325

| union { ... } |

◆ @327

| union { ... } |

◆ @329

| union { ... } |

◆ @331

| union { ... } |

◆ @333

| union { ... } |

◆ @335

| union { ... } |

◆ @337

| union { ... } |

◆ @339

| union { ... } |

◆ @341

| union { ... } |

◆ ADDR_OFFSET0

| __IO uint32_t BEE_Type::ADDR_OFFSET0 |

Offset region 0 Register, offset: 0x4

Definition at line 3012 of file MIMXRT1052.h.

◆ ADDR_OFFSET1

| __IO uint32_t BEE_Type::ADDR_OFFSET1 |

Offset region 1 Register, offset: 0x8

Definition at line 3013 of file MIMXRT1052.h.

◆ ADMA_ERR_STATUS

| __I uint32_t USDHC_Type::ADMA_ERR_STATUS |

ADMA Error Status Register, offset: 0x54

Definition at line 42275 of file MIMXRT1052.h.

◆ ADMA_SYS_ADDR

| __IO uint32_t USDHC_Type::ADMA_SYS_ADDR |

ADMA System Address, offset: 0x58

Definition at line 42276 of file MIMXRT1052.h.

◆ AES_KEY0_W0

| __IO uint32_t BEE_Type::AES_KEY0_W0 |

AES Key 0 Register, offset: 0xC

Definition at line 3014 of file MIMXRT1052.h.

◆ AES_KEY0_W1

| __IO uint32_t BEE_Type::AES_KEY0_W1 |

AES Key 1 Register, offset: 0x10

Definition at line 3015 of file MIMXRT1052.h.

◆ AES_KEY0_W2

| __IO uint32_t BEE_Type::AES_KEY0_W2 |

AES Key 2 Register, offset: 0x14

Definition at line 3016 of file MIMXRT1052.h.

◆ AES_KEY0_W3

| __IO uint32_t BEE_Type::AES_KEY0_W3 |

AES Key 3 Register, offset: 0x18

Definition at line 3017 of file MIMXRT1052.h.

◆ AHBCR

| __IO uint32_t FLEXSPI_Type::AHBCR |

AHB Bus Control Register, offset: 0xC

Definition at line 18093 of file MIMXRT1052.h.

◆ AHBRXBUFCR0

| __IO uint32_t FLEXSPI_Type::AHBRXBUFCR0[4] |

AHB RX Buffer 0 Control Register 0..AHB RX Buffer 3 Control Register 0, array offset: 0x20, array step: 0x4

Definition at line 18098 of file MIMXRT1052.h.

◆ AHBSPNDSTS

| __I uint32_t FLEXSPI_Type::AHBSPNDSTS |

AHB Suspend Status Register, offset: 0xEC

Definition at line 18118 of file MIMXRT1052.h.

◆ ANA0

| __IO uint32_t OCOTP_Type::ANA0 |

Value of OTP Bank1 Word5 (Analog Info.), offset: 0x4D0

Definition at line 27748 of file MIMXRT1052.h.

◆ ANA1

| __IO uint32_t OCOTP_Type::ANA1 |

Value of OTP Bank1 Word6 (Analog Info.), offset: 0x4E0

Definition at line 27750 of file MIMXRT1052.h.

◆ ANA2

| __IO uint32_t OCOTP_Type::ANA2 |

Value of OTP Bank1 Word7 (Analog Info.), offset: 0x4F0

Definition at line 27752 of file MIMXRT1052.h.

◆ AS_BUF

| __IO uint32_t PXP_Type::AS_BUF |

Alpha Surface Buffer Pointer, offset: 0x160

Definition at line 32562 of file MIMXRT1052.h.

◆ AS_CLRKEYHIGH

| __IO uint32_t PXP_Type::AS_CLRKEYHIGH |

Overlay Color Key High, offset: 0x190

Definition at line 32568 of file MIMXRT1052.h.

◆ AS_CLRKEYLOW

| __IO uint32_t PXP_Type::AS_CLRKEYLOW |

Overlay Color Key Low, offset: 0x180

Definition at line 32566 of file MIMXRT1052.h.

◆ AS_CTRL

| __IO uint32_t PXP_Type::AS_CTRL |

Alpha Surface Control, offset: 0x150

Definition at line 32560 of file MIMXRT1052.h.

◆ AS_PITCH

| __IO uint32_t PXP_Type::AS_PITCH |

Alpha Surface Pitch, offset: 0x170

Definition at line 32564 of file MIMXRT1052.h.

◆ ASYNCLISTADDR [1/2]

| __IO uint32_t USB_Type::ASYNCLISTADDR |

Next Asynch. Address, offset: 0x158

Definition at line 39027 of file MIMXRT1052.h.

◆ ASYNCLISTADDR [2/2]

| __IO { ... } ::ASYNCLISTADDR |

Next Asynch. Address, offset: 0x158

Definition at line 39027 of file MIMXRT1052.h.

◆ ATCOR

| __IO uint32_t ENET_Type::ATCOR |

Timer Correction Register, offset: 0x410

Definition at line 15714 of file MIMXRT1052.h.

◆ ATCR

| __IO uint32_t ENET_Type::ATCR |

Adjustable Timer Control Register, offset: 0x400

Definition at line 15710 of file MIMXRT1052.h.

◆ ATINC

| __IO uint32_t ENET_Type::ATINC |

Time-Stamping Clock Period Register, offset: 0x414

Definition at line 15715 of file MIMXRT1052.h.

◆ ATOFF

| __IO uint32_t ENET_Type::ATOFF |

Timer Offset Register, offset: 0x408

Definition at line 15712 of file MIMXRT1052.h.

◆ ATPER

| __IO uint32_t ENET_Type::ATPER |

Timer Period Register, offset: 0x40C

Definition at line 15713 of file MIMXRT1052.h.

◆ ATSTMP

| __I uint32_t ENET_Type::ATSTMP |

Timestamp of Last Transmitted Frame, offset: 0x418

Definition at line 15716 of file MIMXRT1052.h.

◆ ATTR [1/2]

| __IO uint16_t DMA_Type::ATTR |

TCD Transfer Attributes, array offset: 0x1006, array step: 0x20

Definition at line 12007 of file MIMXRT1052.h.

◆ ATTR [2/2]

| __IO { ... } ::ATTR |

TCD Transfer Attributes, array offset: 0x1006, array step: 0x20

Definition at line 12007 of file MIMXRT1052.h.

◆ ATVR

| __IO uint32_t ENET_Type::ATVR |

Timer Value Register, offset: 0x404

Definition at line 15711 of file MIMXRT1052.h.

◆ AUTOCMD12_ERR_STATUS

| __IO uint32_t USDHC_Type::AUTOCMD12_ERR_STATUS |

Auto CMD12 Error Status, offset: 0x3C

Definition at line 42269 of file MIMXRT1052.h.

◆ BASIC_SETTING

| __IO uint32_t TSC_Type::BASIC_SETTING |

Basic Setting, offset: 0x0

Definition at line 38547 of file MIMXRT1052.h.

◆ BAUD

| __IO uint32_t LPUART_Type::BAUD |

LPUART Baud Rate Register, offset: 0x10

Definition at line 26776 of file MIMXRT1052.h.

◆ BFCRT

| struct { ... } AOI_Type::BFCRT[4] |

◆ BFCRT01 [1/2]

| __IO uint16_t AOI_Type::BFCRT01 |

Boolean Function Term 0 and 1 Configuration Register for EVENTn, array offset: 0x0, array step: 0x4

Definition at line 2803 of file MIMXRT1052.h.

◆ BFCRT01 [2/2]

| __IO { ... } ::BFCRT01 |

Boolean Function Term 0 and 1 Configuration Register for EVENTn, array offset: 0x0, array step: 0x4

Definition at line 2803 of file MIMXRT1052.h.

◆ BFCRT23 [1/2]

| __IO uint16_t AOI_Type::BFCRT23 |

Boolean Function Term 2 and 3 Configuration Register for EVENTn, array offset: 0x2, array step: 0x4

Definition at line 2804 of file MIMXRT1052.h.

◆ BFCRT23 [2/2]

| __IO { ... } ::BFCRT23 |

Boolean Function Term 2 and 3 Configuration Register for EVENTn, array offset: 0x2, array step: 0x4

Definition at line 2804 of file MIMXRT1052.h.

◆ BITER_ELINKNO [1/2]

| __IO uint16_t DMA_Type::BITER_ELINKNO |

TCD Beginning Minor Loop Link, Major Loop Count (Channel Linking Disabled), array offset: 0x101E, array step: 0x20

Definition at line 12023 of file MIMXRT1052.h.

◆ BITER_ELINKNO [2/2]

| __IO { ... } ::BITER_ELINKNO |

TCD Beginning Minor Loop Link, Major Loop Count (Channel Linking Disabled), array offset: 0x101E, array step: 0x20

Definition at line 12023 of file MIMXRT1052.h.

◆ BITER_ELINKYES [1/2]

| __IO uint16_t DMA_Type::BITER_ELINKYES |

TCD Beginning Minor Loop Link, Major Loop Count (Channel Linking Enabled), array offset: 0x101E, array step: 0x20

Definition at line 12024 of file MIMXRT1052.h.

◆ BITER_ELINKYES [2/2]

| __IO { ... } ::BITER_ELINKYES |

TCD Beginning Minor Loop Link, Major Loop Count (Channel Linking Enabled), array offset: 0x101E, array step: 0x20

Definition at line 12024 of file MIMXRT1052.h.

◆ BLK_ATT

| __IO uint32_t USDHC_Type::BLK_ATT |

Block Attributes, offset: 0x4

Definition at line 42255 of file MIMXRT1052.h.

◆ BM_ERROR_STAT

| __IO uint32_t LCDIF_Type::BM_ERROR_STAT |

Bus Master Error Status Register, offset: 0x190

Definition at line 23549 of file MIMXRT1052.h.

◆ BMCR0

| __IO uint32_t SEMC_Type::BMCR0 |

Master Bus (AXI) Control Register 0, offset: 0x8

Definition at line 34132 of file MIMXRT1052.h.

◆ BMCR1

| __IO uint32_t SEMC_Type::BMCR1 |

Master Bus (AXI) Control Register 1, offset: 0xC

Definition at line 34133 of file MIMXRT1052.h.

◆ BR

| __IO uint32_t SEMC_Type::BR[9] |

Base Register 0 (For SDRAM CS0 device)..Base Register 8 (For NAND device), array offset: 0x10, array step: 0x4

Definition at line 34134 of file MIMXRT1052.h.

◆ BURSTSIZE

| __IO uint32_t USB_Type::BURSTSIZE |

Programmable Burst Size, offset: 0x160

Definition at line 39031 of file MIMXRT1052.h.

◆ CACRR

| __IO uint32_t CCM_Type::CACRR |

CCM Arm Clock Root Register, offset: 0x10

Definition at line 4159 of file MIMXRT1052.h.

◆ CAL

| __IO uint32_t ADC_Type::CAL |

Calibration value register, offset: 0x58

Definition at line 1305 of file MIMXRT1052.h.

◆ CAPABILITY0

| __IO uint32_t DCP_Type::CAPABILITY0 |

DCP capability 0 register, offset: 0x30

Definition at line 10282 of file MIMXRT1052.h.

◆ CAPABILITY1

| __I uint32_t DCP_Type::CAPABILITY1 |

DCP capability 1 register, offset: 0x40

Definition at line 10284 of file MIMXRT1052.h.

◆ CAPLENGTH

| __I uint8_t USB_Type::CAPLENGTH |

Capability Registers Length, offset: 0x100

Definition at line 39007 of file MIMXRT1052.h.

◆ CAPT [1/2]

| __IO { ... } ::CAPT |

Timer Channel Capture Register, array offset: 0x4, array step: 0x20

Definition at line 37382 of file MIMXRT1052.h.

◆ CAPT [2/2]

| __IO uint16_t TMR_Type::CAPT |

Timer Channel Capture Register, array offset: 0x4, array step: 0x20

Definition at line 37382 of file MIMXRT1052.h.

◆ CAPTCOMPA [1/2]

| __IO uint16_t PWM_Type::CAPTCOMPA |

Capture Compare A Register, array offset: 0x36, array step: 0x60

Definition at line 30871 of file MIMXRT1052.h.

◆ CAPTCOMPA [2/2]

| __IO { ... } ::CAPTCOMPA |

Capture Compare A Register, array offset: 0x36, array step: 0x60

Definition at line 30871 of file MIMXRT1052.h.

◆ CAPTCOMPB [1/2]

| __IO uint16_t PWM_Type::CAPTCOMPB |

Capture Compare B Register, array offset: 0x3A, array step: 0x60

Definition at line 30873 of file MIMXRT1052.h.

◆ CAPTCOMPB [2/2]

| __IO { ... } ::CAPTCOMPB |

Capture Compare B Register, array offset: 0x3A, array step: 0x60

Definition at line 30873 of file MIMXRT1052.h.

◆ CAPTCOMPX [1/2]

| __IO uint16_t PWM_Type::CAPTCOMPX |

Capture Compare X Register, array offset: 0x3E, array step: 0x60

Definition at line 30875 of file MIMXRT1052.h.

◆ CAPTCOMPX [2/2]

| __IO { ... } ::CAPTCOMPX |

Capture Compare X Register, array offset: 0x3E, array step: 0x60

Definition at line 30875 of file MIMXRT1052.h.

◆ CAPTCTRLA [1/2]

| __IO { ... } ::CAPTCTRLA |

Capture Control A Register, array offset: 0x34, array step: 0x60

Definition at line 30870 of file MIMXRT1052.h.

◆ CAPTCTRLA [2/2]

| __IO uint16_t PWM_Type::CAPTCTRLA |

Capture Control A Register, array offset: 0x34, array step: 0x60

Definition at line 30870 of file MIMXRT1052.h.

◆ CAPTCTRLB [1/2]

| __IO uint16_t PWM_Type::CAPTCTRLB |

Capture Control B Register, array offset: 0x38, array step: 0x60

Definition at line 30872 of file MIMXRT1052.h.

◆ CAPTCTRLB [2/2]

| __IO { ... } ::CAPTCTRLB |

Capture Control B Register, array offset: 0x38, array step: 0x60

Definition at line 30872 of file MIMXRT1052.h.

◆ CAPTCTRLX [1/2]

| __IO uint16_t PWM_Type::CAPTCTRLX |

Capture Control X Register, array offset: 0x3C, array step: 0x60

Definition at line 30874 of file MIMXRT1052.h.

◆ CAPTCTRLX [2/2]

| __IO { ... } ::CAPTCTRLX |

Capture Control X Register, array offset: 0x3C, array step: 0x60

Definition at line 30874 of file MIMXRT1052.h.

◆ CBCDR

| __IO uint32_t CCM_Type::CBCDR |

CCM Bus Clock Divider Register, offset: 0x14

Definition at line 4160 of file MIMXRT1052.h.

◆ CBCMR

| __IO uint32_t CCM_Type::CBCMR |

CCM Bus Clock Multiplexer Register, offset: 0x18

Definition at line 4161 of file MIMXRT1052.h.

◆ CCGR0

| __IO uint32_t CCM_Type::CCGR0 |

CCM Clock Gating Register 0, offset: 0x68

Definition at line 4179 of file MIMXRT1052.h.

◆ CCGR1

| __IO uint32_t CCM_Type::CCGR1 |

CCM Clock Gating Register 1, offset: 0x6C

Definition at line 4180 of file MIMXRT1052.h.

◆ CCGR2

| __IO uint32_t CCM_Type::CCGR2 |

CCM Clock Gating Register 2, offset: 0x70

Definition at line 4181 of file MIMXRT1052.h.

◆ CCGR3

| __IO uint32_t CCM_Type::CCGR3 |

CCM Clock Gating Register 3, offset: 0x74

Definition at line 4182 of file MIMXRT1052.h.

◆ CCGR4

| __IO uint32_t CCM_Type::CCGR4 |

CCM Clock Gating Register 4, offset: 0x78

Definition at line 4183 of file MIMXRT1052.h.

◆ CCGR5

| __IO uint32_t CCM_Type::CCGR5 |

CCM Clock Gating Register 5, offset: 0x7C

Definition at line 4184 of file MIMXRT1052.h.

◆ CCGR6

| __IO uint32_t CCM_Type::CCGR6 |

CCM Clock Gating Register 6, offset: 0x80

Definition at line 4185 of file MIMXRT1052.h.

◆ CCOSR

| __IO uint32_t CCM_Type::CCOSR |

CCM Clock Output Source Register, offset: 0x60

Definition at line 4177 of file MIMXRT1052.h.

◆ CCR [1/2]

| __IO uint32_t CCM_Type::CCR |

CCM Control Register, offset: 0x0

Definition at line 4155 of file MIMXRT1052.h.

◆ CCR [2/2]

| __IO uint32_t LPSPI_Type::CCR |

Clock Configuration Register, offset: 0x40

Definition at line 26158 of file MIMXRT1052.h.

◆ CCSR

| __IO uint32_t CCM_Type::CCSR |

CCM Clock Switcher Register, offset: 0xC

Definition at line 4158 of file MIMXRT1052.h.

◆ CDCDR

| __IO uint32_t CCM_Type::CDCDR |

CCM D1 Clock Divider Register, offset: 0x30

Definition at line 4167 of file MIMXRT1052.h.

◆ CDHIPR

| __I uint32_t CCM_Type::CDHIPR |

CCM Divider Handshake In-Process Register, offset: 0x48

Definition at line 4172 of file MIMXRT1052.h.

◆ CDNE

| __O uint8_t DMA_Type::CDNE |

Clear DONE Status Bit Register, offset: 0x1C

Definition at line 11958 of file MIMXRT1052.h.

◆ CEEI

| __O uint8_t DMA_Type::CEEI |

Clear Enable Error Interrupt Register, offset: 0x18

Definition at line 11954 of file MIMXRT1052.h.

◆ CERQ

| __O uint8_t DMA_Type::CERQ |

Clear Enable Request Register, offset: 0x1A

Definition at line 11956 of file MIMXRT1052.h.

◆ CERR

| __O uint8_t DMA_Type::CERR |

Clear Error Register, offset: 0x1E

Definition at line 11960 of file MIMXRT1052.h.

◆ CFG

| __IO uint32_t ADC_Type::CFG |

Configuration register, offset: 0x44

Definition at line 1300 of file MIMXRT1052.h.

◆ CFG0

| __IO uint32_t OCOTP_Type::CFG0 |

Value of OTP Bank0 Word1 (Configuration and Manufacturing Info.), offset: 0x410

Definition at line 27724 of file MIMXRT1052.h.

◆ CFG1

| __IO uint32_t OCOTP_Type::CFG1 |

Value of OTP Bank0 Word2 (Configuration and Manufacturing Info.), offset: 0x420

Definition at line 27726 of file MIMXRT1052.h.

◆ CFG2

| __IO uint32_t OCOTP_Type::CFG2 |

Value of OTP Bank0 Word3 (Configuration and Manufacturing Info.), offset: 0x430

Definition at line 27728 of file MIMXRT1052.h.

◆ CFG3

| __IO uint32_t OCOTP_Type::CFG3 |

Value of OTP Bank0 Word4 (Configuration and Manufacturing Info.), offset: 0x440

Definition at line 27730 of file MIMXRT1052.h.

◆ CFG4

| __IO uint32_t OCOTP_Type::CFG4 |

Value of OTP Bank0 Word5 (Configuration and Manufacturing Info.), offset: 0x450

Definition at line 27732 of file MIMXRT1052.h.

◆ CFG5

| __IO uint32_t OCOTP_Type::CFG5 |

Value of OTP Bank0 Word6 (Configuration and Manufacturing Info.), offset: 0x460

Definition at line 27734 of file MIMXRT1052.h.

◆ CFG6

| __IO uint32_t OCOTP_Type::CFG6 |

Value of OTP Bank0 Word7 (Configuration and Manufacturing Info.), offset: 0x470

Definition at line 27736 of file MIMXRT1052.h.

◆ CFGR0

| __IO uint32_t LPSPI_Type::CFGR0 |

Configuration Register 0, offset: 0x20

Definition at line 26152 of file MIMXRT1052.h.

◆ CFGR1

| __IO uint32_t LPSPI_Type::CFGR1 |

Configuration Register 1, offset: 0x24

Definition at line 26153 of file MIMXRT1052.h.

◆ CGPR

| __IO uint32_t CCM_Type::CGPR |

CCM General Purpose Register, offset: 0x64

Definition at line 4178 of file MIMXRT1052.h.

◆ CH0CMDPTR

| __IO uint32_t DCP_Type::CH0CMDPTR |

DCP channel 0 command pointer address register, offset: 0x100

Definition at line 10306 of file MIMXRT1052.h.

◆ CH0OPTS

| __IO uint32_t DCP_Type::CH0OPTS |

DCP channel 0 options register, offset: 0x130

Definition at line 10314 of file MIMXRT1052.h.

◆ CH0OPTS_CLR

| __IO uint32_t DCP_Type::CH0OPTS_CLR |

DCP channel 0 options register, offset: 0x138

Definition at line 10316 of file MIMXRT1052.h.

◆ CH0OPTS_SET

| __IO uint32_t DCP_Type::CH0OPTS_SET |

DCP channel 0 options register, offset: 0x134

Definition at line 10315 of file MIMXRT1052.h.

◆ CH0OPTS_TOG

| __IO uint32_t DCP_Type::CH0OPTS_TOG |

DCP channel 0 options register, offset: 0x13C

Definition at line 10317 of file MIMXRT1052.h.

◆ CH0SEMA

| __IO uint32_t DCP_Type::CH0SEMA |

DCP channel 0 semaphore register, offset: 0x110

Definition at line 10308 of file MIMXRT1052.h.

◆ CH0STAT

| __IO uint32_t DCP_Type::CH0STAT |

DCP channel 0 status register, offset: 0x120

Definition at line 10310 of file MIMXRT1052.h.

◆ CH0STAT_CLR

| __IO uint32_t DCP_Type::CH0STAT_CLR |

DCP channel 0 status register, offset: 0x128

Definition at line 10312 of file MIMXRT1052.h.

◆ CH0STAT_SET

| __IO uint32_t DCP_Type::CH0STAT_SET |

DCP channel 0 status register, offset: 0x124

Definition at line 10311 of file MIMXRT1052.h.

◆ CH0STAT_TOG

| __IO uint32_t DCP_Type::CH0STAT_TOG |

DCP channel 0 status register, offset: 0x12C

Definition at line 10313 of file MIMXRT1052.h.

◆ CH1CMDPTR

| __IO uint32_t DCP_Type::CH1CMDPTR |

DCP channel 1 command pointer address register, offset: 0x140

Definition at line 10318 of file MIMXRT1052.h.

◆ CH1OPTS

| __IO uint32_t DCP_Type::CH1OPTS |

DCP channel 1 options register, offset: 0x170

Definition at line 10326 of file MIMXRT1052.h.

◆ CH1OPTS_CLR

| __IO uint32_t DCP_Type::CH1OPTS_CLR |

DCP channel 1 options register, offset: 0x178

Definition at line 10328 of file MIMXRT1052.h.

◆ CH1OPTS_SET

| __IO uint32_t DCP_Type::CH1OPTS_SET |

DCP channel 1 options register, offset: 0x174

Definition at line 10327 of file MIMXRT1052.h.

◆ CH1OPTS_TOG

| __IO uint32_t DCP_Type::CH1OPTS_TOG |

DCP channel 1 options register, offset: 0x17C

Definition at line 10329 of file MIMXRT1052.h.

◆ CH1SEMA

| __IO uint32_t DCP_Type::CH1SEMA |

DCP channel 1 semaphore register, offset: 0x150

Definition at line 10320 of file MIMXRT1052.h.

◆ CH1STAT

| __IO uint32_t DCP_Type::CH1STAT |

DCP channel 1 status register, offset: 0x160

Definition at line 10322 of file MIMXRT1052.h.

◆ CH1STAT_CLR

| __IO uint32_t DCP_Type::CH1STAT_CLR |

DCP channel 1 status register, offset: 0x168

Definition at line 10324 of file MIMXRT1052.h.

◆ CH1STAT_SET

| __IO uint32_t DCP_Type::CH1STAT_SET |

DCP channel 1 status register, offset: 0x164

Definition at line 10323 of file MIMXRT1052.h.

◆ CH1STAT_TOG

| __IO uint32_t DCP_Type::CH1STAT_TOG |

DCP channel 1 status register, offset: 0x16C

Definition at line 10325 of file MIMXRT1052.h.

◆ CH2CMDPTR

| __IO uint32_t DCP_Type::CH2CMDPTR |

DCP channel 2 command pointer address register, offset: 0x180

Definition at line 10330 of file MIMXRT1052.h.

◆ CH2OPTS

| __IO uint32_t DCP_Type::CH2OPTS |

DCP channel 2 options register, offset: 0x1B0

Definition at line 10338 of file MIMXRT1052.h.

◆ CH2OPTS_CLR

| __IO uint32_t DCP_Type::CH2OPTS_CLR |

DCP channel 2 options register, offset: 0x1B8

Definition at line 10340 of file MIMXRT1052.h.

◆ CH2OPTS_SET

| __IO uint32_t DCP_Type::CH2OPTS_SET |

DCP channel 2 options register, offset: 0x1B4

Definition at line 10339 of file MIMXRT1052.h.

◆ CH2OPTS_TOG

| __IO uint32_t DCP_Type::CH2OPTS_TOG |

DCP channel 2 options register, offset: 0x1BC

Definition at line 10341 of file MIMXRT1052.h.

◆ CH2SEMA

| __IO uint32_t DCP_Type::CH2SEMA |

DCP channel 2 semaphore register, offset: 0x190

Definition at line 10332 of file MIMXRT1052.h.

◆ CH2STAT

| __IO uint32_t DCP_Type::CH2STAT |

DCP channel 2 status register, offset: 0x1A0

Definition at line 10334 of file MIMXRT1052.h.

◆ CH2STAT_CLR

| __IO uint32_t DCP_Type::CH2STAT_CLR |

DCP channel 2 status register, offset: 0x1A8

Definition at line 10336 of file MIMXRT1052.h.

◆ CH2STAT_SET

| __IO uint32_t DCP_Type::CH2STAT_SET |

DCP channel 2 status register, offset: 0x1A4

Definition at line 10335 of file MIMXRT1052.h.

◆ CH2STAT_TOG

| __IO uint32_t DCP_Type::CH2STAT_TOG |

DCP channel 2 status register, offset: 0x1AC

Definition at line 10337 of file MIMXRT1052.h.

◆ CH3CMDPTR

| __IO uint32_t DCP_Type::CH3CMDPTR |

DCP channel 3 command pointer address register, offset: 0x1C0

Definition at line 10342 of file MIMXRT1052.h.

◆ CH3OPTS

| __IO uint32_t DCP_Type::CH3OPTS |

DCP channel 3 options register, offset: 0x1F0

Definition at line 10350 of file MIMXRT1052.h.

◆ CH3OPTS_CLR

| __IO uint32_t DCP_Type::CH3OPTS_CLR |

DCP channel 3 options register, offset: 0x1F8

Definition at line 10352 of file MIMXRT1052.h.

◆ CH3OPTS_SET

| __IO uint32_t DCP_Type::CH3OPTS_SET |

DCP channel 3 options register, offset: 0x1F4

Definition at line 10351 of file MIMXRT1052.h.

◆ CH3OPTS_TOG

| __IO uint32_t DCP_Type::CH3OPTS_TOG |

DCP channel 3 options register, offset: 0x1FC

Definition at line 10353 of file MIMXRT1052.h.

◆ CH3SEMA

| __IO uint32_t DCP_Type::CH3SEMA |

DCP channel 3 semaphore register, offset: 0x1D0

Definition at line 10344 of file MIMXRT1052.h.

◆ CH3STAT

| __IO uint32_t DCP_Type::CH3STAT |

DCP channel 3 status register, offset: 0x1E0

Definition at line 10346 of file MIMXRT1052.h.

◆ CH3STAT_CLR

| __IO uint32_t DCP_Type::CH3STAT_CLR |

DCP channel 3 status register, offset: 0x1E8

Definition at line 10348 of file MIMXRT1052.h.

◆ CH3STAT_SET

| __IO uint32_t DCP_Type::CH3STAT_SET |

DCP channel 3 status register, offset: 0x1E4

Definition at line 10347 of file MIMXRT1052.h.

◆ CH3STAT_TOG

| __IO uint32_t DCP_Type::CH3STAT_TOG |

DCP channel 3 status register, offset: 0x1EC

Definition at line 10349 of file MIMXRT1052.h.

◆ CHANNEL [1/3]

| struct { ... } ENET_Type::CHANNEL[4] |

◆ CHANNEL [2/3]

| struct { ... } PIT_Type::CHANNEL[4] |

◆ CHANNEL [3/3]

| struct { ... } TMR_Type::CHANNEL[4] |

◆ CHANNELCTRL

| __IO uint32_t DCP_Type::CHANNELCTRL |

DCP channel control register, offset: 0x20

Definition at line 10278 of file MIMXRT1052.h.

◆ CHANNELCTRL_CLR

| __IO uint32_t DCP_Type::CHANNELCTRL_CLR |

DCP channel control register, offset: 0x28

Definition at line 10280 of file MIMXRT1052.h.

◆ CHANNELCTRL_SET

| __IO uint32_t DCP_Type::CHANNELCTRL_SET |

DCP channel control register, offset: 0x24

Definition at line 10279 of file MIMXRT1052.h.

◆ CHANNELCTRL_TOG

| __IO uint32_t DCP_Type::CHANNELCTRL_TOG |

DCP channel control register, offset: 0x2C

Definition at line 10281 of file MIMXRT1052.h.

◆ CHCFG

| __IO uint32_t DMAMUX_Type::CHCFG[32] |

Channel 0 Configuration Register..Channel 31 Configuration Register, array offset: 0x0, array step: 0x4

Definition at line 15061 of file MIMXRT1052.h.

◆ CHRG_DETECT [1/2]

| __IO uint32_t USB_ANALOG_Type::CHRG_DETECT |

USB Charger Detect Register, array offset: 0x1B0, array step: 0x60

Definition at line 41805 of file MIMXRT1052.h.

◆ CHRG_DETECT [2/2]

| __IO { ... } ::CHRG_DETECT |

USB Charger Detect Register, array offset: 0x1B0, array step: 0x60

Definition at line 41805 of file MIMXRT1052.h.

◆ CHRG_DETECT_CLR [1/2]

| __IO uint32_t USB_ANALOG_Type::CHRG_DETECT_CLR |

USB Charger Detect Register, array offset: 0x1B8, array step: 0x60

Definition at line 41807 of file MIMXRT1052.h.

◆ CHRG_DETECT_CLR [2/2]

| __IO { ... } ::CHRG_DETECT_CLR |

USB Charger Detect Register, array offset: 0x1B8, array step: 0x60

Definition at line 41807 of file MIMXRT1052.h.

◆ CHRG_DETECT_SET [1/2]

| __IO uint32_t USB_ANALOG_Type::CHRG_DETECT_SET |

USB Charger Detect Register, array offset: 0x1B4, array step: 0x60

Definition at line 41806 of file MIMXRT1052.h.

◆ CHRG_DETECT_SET [2/2]

| __IO { ... } ::CHRG_DETECT_SET |

USB Charger Detect Register, array offset: 0x1B4, array step: 0x60

Definition at line 41806 of file MIMXRT1052.h.

◆ CHRG_DETECT_STAT [1/2]

| __I uint32_t USB_ANALOG_Type::CHRG_DETECT_STAT |

USB Charger Detect Status Register, array offset: 0x1D0, array step: 0x60

Definition at line 41811 of file MIMXRT1052.h.

◆ CHRG_DETECT_STAT [2/2]

| __I { ... } ::CHRG_DETECT_STAT |

USB Charger Detect Status Register, array offset: 0x1D0, array step: 0x60

Definition at line 41811 of file MIMXRT1052.h.

◆ CHRG_DETECT_TOG [1/2]

| __IO uint32_t USB_ANALOG_Type::CHRG_DETECT_TOG |

USB Charger Detect Register, array offset: 0x1BC, array step: 0x60

Definition at line 41808 of file MIMXRT1052.h.

◆ CHRG_DETECT_TOG [2/2]

| __IO { ... } ::CHRG_DETECT_TOG |

USB Charger Detect Register, array offset: 0x1BC, array step: 0x60

Definition at line 41808 of file MIMXRT1052.h.

◆ CIMR

| __IO uint32_t CCM_Type::CIMR |

CCM Interrupt Mask Register, offset: 0x5C

Definition at line 4176 of file MIMXRT1052.h.

◆ CINT

| __O uint8_t DMA_Type::CINT |

Clear Interrupt Request Register, offset: 0x1F

Definition at line 11961 of file MIMXRT1052.h.

◆ CISR

| __IO uint32_t CCM_Type::CISR |

CCM Interrupt Status Register, offset: 0x58

Definition at line 4175 of file MIMXRT1052.h.

◆ CITER_ELINKNO [1/2]

| __IO uint16_t DMA_Type::CITER_ELINKNO |

TCD Current Minor Loop Link, Major Loop Count (Channel Linking Disabled), array offset: 0x1016, array step: 0x20

Definition at line 12017 of file MIMXRT1052.h.

◆ CITER_ELINKNO [2/2]

| __IO { ... } ::CITER_ELINKNO |

TCD Current Minor Loop Link, Major Loop Count (Channel Linking Disabled), array offset: 0x1016, array step: 0x20

Definition at line 12017 of file MIMXRT1052.h.

◆ CITER_ELINKYES [1/2]

| __IO { ... } ::CITER_ELINKYES |

TCD Current Minor Loop Link, Major Loop Count (Channel Linking Enabled), array offset: 0x1016, array step: 0x20

Definition at line 12018 of file MIMXRT1052.h.

◆ CITER_ELINKYES [2/2]

| __IO uint16_t DMA_Type::CITER_ELINKYES |

TCD Current Minor Loop Link, Major Loop Count (Channel Linking Enabled), array offset: 0x1016, array step: 0x20

Definition at line 12018 of file MIMXRT1052.h.

◆ CLK_TUNE_CTRL_STATUS

| __IO uint32_t USDHC_Type::CLK_TUNE_CTRL_STATUS |

CLK Tuning Control and Status, offset: 0x68

Definition at line 42280 of file MIMXRT1052.h.

◆ CLKCTRL

| __IO uint8_t EWM_Type::CLKCTRL |

Clock Control Register, offset: 0x4

Definition at line 17251 of file MIMXRT1052.h.

◆ CLKPRESCALER

| __IO uint8_t EWM_Type::CLKPRESCALER |

Clock Prescaler Register, offset: 0x5

Definition at line 17252 of file MIMXRT1052.h.

◆ CLPCR

| __IO uint32_t CCM_Type::CLPCR |

CCM Low Power Control Register, offset: 0x54

Definition at line 4174 of file MIMXRT1052.h.

◆ CMD_ARG

| __IO uint32_t USDHC_Type::CMD_ARG |

Command Argument, offset: 0x8

Definition at line 42256 of file MIMXRT1052.h.

◆ CMD_RSP0

| __I uint32_t USDHC_Type::CMD_RSP0 |

Command Response0, offset: 0x10

Definition at line 42258 of file MIMXRT1052.h.

◆ CMD_RSP1

| __I uint32_t USDHC_Type::CMD_RSP1 |

Command Response1, offset: 0x14

Definition at line 42259 of file MIMXRT1052.h.

◆ CMD_RSP2

| __I uint32_t USDHC_Type::CMD_RSP2 |

Command Response2, offset: 0x18

Definition at line 42260 of file MIMXRT1052.h.

◆ CMD_RSP3

| __I uint32_t USDHC_Type::CMD_RSP3 |

Command Response3, offset: 0x1C

Definition at line 42261 of file MIMXRT1052.h.

◆ CMD_XFR_TYP

| __IO uint32_t USDHC_Type::CMD_XFR_TYP |

Command Transfer Type, offset: 0xC

Definition at line 42257 of file MIMXRT1052.h.

◆ CMEOR

| __IO uint32_t CCM_Type::CMEOR |

CCM Module Enable Overide Register, offset: 0x88

Definition at line 4187 of file MIMXRT1052.h.

◆ CMPH

| __IO uint8_t EWM_Type::CMPH |

Compare High Register, offset: 0x3

Definition at line 17250 of file MIMXRT1052.h.

◆ CMPL

| __IO uint8_t EWM_Type::CMPL |

Compare Low Register, offset: 0x2

Definition at line 17249 of file MIMXRT1052.h.

◆ CMPLD1 [1/2]

| __IO { ... } ::CMPLD1 |

Timer Channel Comparator Load Register 1, array offset: 0x10, array step: 0x20

Definition at line 37388 of file MIMXRT1052.h.

◆ CMPLD1 [2/2]

| __IO uint16_t TMR_Type::CMPLD1 |

Timer Channel Comparator Load Register 1, array offset: 0x10, array step: 0x20

Definition at line 37388 of file MIMXRT1052.h.

◆ CMPLD2 [1/2]

| __IO uint16_t TMR_Type::CMPLD2 |

Timer Channel Comparator Load Register 2, array offset: 0x12, array step: 0x20

Definition at line 37389 of file MIMXRT1052.h.

◆ CMPLD2 [2/2]

| __IO { ... } ::CMPLD2 |

Timer Channel Comparator Load Register 2, array offset: 0x12, array step: 0x20

Definition at line 37389 of file MIMXRT1052.h.

◆ CNT [1/4]

| __I uint32_t GPT_Type::CNT |

GPT Counter Register, offset: 0x24

Definition at line 19584 of file MIMXRT1052.h.

◆ CNT [2/4]

| __I uint16_t PWM_Type::CNT |

Counter Register, array offset: 0x0, array step: 0x60

Definition at line 30845 of file MIMXRT1052.h.

◆ CNT [3/4]

| __I { ... } ::CNT |

Counter Register, array offset: 0x0, array step: 0x60

Definition at line 30845 of file MIMXRT1052.h.

◆ CNT [4/4]

| __IO uint32_t RTWDOG_Type::CNT |

Watchdog Counter Register, offset: 0x4

Definition at line 33929 of file MIMXRT1052.h.

◆ CNTR [1/3]

| __IO uint32_t GPC_Type::CNTR |

GPC Interface control register, offset: 0x0

Definition at line 18997 of file MIMXRT1052.h.

◆ CNTR [2/3]

| __IO uint16_t TMR_Type::CNTR |

Timer Channel Counter Register, array offset: 0xA, array step: 0x20

Definition at line 37385 of file MIMXRT1052.h.

◆ CNTR [3/3]

| __IO { ... } ::CNTR |

Timer Channel Counter Register, array offset: 0xA, array step: 0x20

Definition at line 37385 of file MIMXRT1052.h.

◆ COMP1 [1/2]

| __IO uint16_t TMR_Type::COMP1 |

Timer Channel Compare Register 1, array offset: 0x0, array step: 0x20

Definition at line 37380 of file MIMXRT1052.h.

◆ COMP1 [2/2]

| __IO { ... } ::COMP1 |

Timer Channel Compare Register 1, array offset: 0x0, array step: 0x20

Definition at line 37380 of file MIMXRT1052.h.

◆ COMP2 [1/2]

| __IO { ... } ::COMP2 |

Timer Channel Compare Register 2, array offset: 0x2, array step: 0x20

Definition at line 37381 of file MIMXRT1052.h.

◆ COMP2 [2/2]

| __IO uint16_t TMR_Type::COMP2 |

Timer Channel Compare Register 2, array offset: 0x2, array step: 0x20

Definition at line 37381 of file MIMXRT1052.h.

◆ CONFIGFLAG

| __I uint32_t USB_Type::CONFIGFLAG |

Configure Flag Register, offset: 0x180

Definition at line 39036 of file MIMXRT1052.h.

◆ CONTEXT

| __IO uint32_t DCP_Type::CONTEXT |

DCP context buffer pointer, offset: 0x50

Definition at line 10286 of file MIMXRT1052.h.

◆ CPU_CTRL

| __IO uint32_t PGC_Type::CPU_CTRL |

PGC CPU Control Register, offset: 0x2A0

Definition at line 28379 of file MIMXRT1052.h.

◆ CPU_PDNSCR

| __IO uint32_t PGC_Type::CPU_PDNSCR |

PGC CPU Pull Down Sequence Control Register, offset: 0x2A8

Definition at line 28381 of file MIMXRT1052.h.

◆ CPU_PUPSCR

| __IO uint32_t PGC_Type::CPU_PUPSCR |

PGC CPU Power Up Sequence Control Register, offset: 0x2A4

Definition at line 28380 of file MIMXRT1052.h.

◆ CPU_SR

| __IO uint32_t PGC_Type::CPU_SR |

PGC CPU Power Gating Controller Status Register, offset: 0x2AC

Definition at line 28382 of file MIMXRT1052.h.

◆ CR [1/3]

| __IO uint32_t DMA_Type::CR |

Control Register, offset: 0x0

Definition at line 11948 of file MIMXRT1052.h.

◆ CR [2/3]

| __IO uint32_t GPT_Type::CR |

GPT Control Register, offset: 0x0

Definition at line 19578 of file MIMXRT1052.h.

◆ CR [3/3]

| __IO uint32_t LPSPI_Type::CR |

Control Register, offset: 0x10

Definition at line 26148 of file MIMXRT1052.h.

◆ CR0

| __IO uint8_t CMP_Type::CR0 |

CMP Control Register 0, offset: 0x0

Definition at line 8542 of file MIMXRT1052.h.

◆ CR1

| __IO uint8_t CMP_Type::CR1 |

CMP Control Register 1, offset: 0x1

Definition at line 8543 of file MIMXRT1052.h.

◆ CRC_STAT

| __IO uint32_t LCDIF_Type::CRC_STAT |

CRC Status Register, offset: 0x1A0

Definition at line 23551 of file MIMXRT1052.h.

◆ CRCR

| __I uint32_t CAN_Type::CRCR |

CRC Register, offset: 0x44

Definition at line 3329 of file MIMXRT1052.h.

◆ CS [1/3]

| __IO uint32_t CAN_Type::CS |

Message Buffer 0 CS Register..Message Buffer 63 CS Register, array offset: 0x80, array step: 0x10

Definition at line 3337 of file MIMXRT1052.h.

◆ CS [2/3]

| __IO { ... } ::CS |

Message Buffer 0 CS Register..Message Buffer 63 CS Register, array offset: 0x80, array step: 0x10

Definition at line 3337 of file MIMXRT1052.h.

◆ CS [3/3]

| __IO uint32_t RTWDOG_Type::CS |

Watchdog Control and Status Register, offset: 0x0

Definition at line 33928 of file MIMXRT1052.h.

◆ CS1CDR

| __IO uint32_t CCM_Type::CS1CDR |

CCM Clock Divider Register, offset: 0x28

Definition at line 4165 of file MIMXRT1052.h.

◆ CS2CDR

| __IO uint32_t CCM_Type::CS2CDR |

CCM Clock Divider Register, offset: 0x2C

Definition at line 4166 of file MIMXRT1052.h.

◆ CSC1_COEF0

| __IO uint32_t PXP_Type::CSC1_COEF0 |

Color Space Conversion Coefficient Register 0, offset: 0x1A0

Definition at line 32570 of file MIMXRT1052.h.

◆ CSC1_COEF1

| __IO uint32_t PXP_Type::CSC1_COEF1 |

Color Space Conversion Coefficient Register 1, offset: 0x1B0

Definition at line 32572 of file MIMXRT1052.h.

◆ CSC1_COEF2

| __IO uint32_t PXP_Type::CSC1_COEF2 |

Color Space Conversion Coefficient Register 2, offset: 0x1C0

Definition at line 32574 of file MIMXRT1052.h.

◆ CSCDR1

| __IO uint32_t CCM_Type::CSCDR1 |

CCM Serial Clock Divider Register 1, offset: 0x24

Definition at line 4164 of file MIMXRT1052.h.

◆ CSCDR2

| __IO uint32_t CCM_Type::CSCDR2 |

CCM Serial Clock Divider Register 2, offset: 0x38

Definition at line 4169 of file MIMXRT1052.h.

◆ CSCDR3

| __IO uint32_t CCM_Type::CSCDR3 |

CCM Serial Clock Divider Register 3, offset: 0x3C

Definition at line 4170 of file MIMXRT1052.h.

◆ CSCMR1

| __IO uint32_t CCM_Type::CSCMR1 |

CCM Serial Clock Multiplexer Register 1, offset: 0x1C

Definition at line 4162 of file MIMXRT1052.h.

◆ CSCMR2

| __IO uint32_t CCM_Type::CSCMR2 |

CCM Serial Clock Multiplexer Register 2, offset: 0x20

Definition at line 4163 of file MIMXRT1052.h.

◆ CSCTRL [1/2]

| __IO uint16_t TMR_Type::CSCTRL |

Timer Channel Comparator Status and Control Register, array offset: 0x14, array step: 0x20

Definition at line 37390 of file MIMXRT1052.h.

◆ CSCTRL [2/2]

| __IO { ... } ::CSCTRL |

Timer Channel Comparator Status and Control Register, array offset: 0x14, array step: 0x20

Definition at line 37390 of file MIMXRT1052.h.

◆ CSICR1

| __IO uint32_t CSI_Type::CSICR1 |

CSI Control Register 1, offset: 0x0

Definition at line 8792 of file MIMXRT1052.h.

◆ CSICR18

| __IO uint32_t CSI_Type::CSICR18 |

CSI Control Register 18, offset: 0x48

Definition at line 8807 of file MIMXRT1052.h.

◆ CSICR19

| __IO uint32_t CSI_Type::CSICR19 |

CSI Control Register 19, offset: 0x4C

Definition at line 8808 of file MIMXRT1052.h.

◆ CSICR2

| __IO uint32_t CSI_Type::CSICR2 |

CSI Control Register 2, offset: 0x4

Definition at line 8793 of file MIMXRT1052.h.

◆ CSICR3

| __IO uint32_t CSI_Type::CSICR3 |

CSI Control Register 3, offset: 0x8

Definition at line 8794 of file MIMXRT1052.h.

◆ CSIDMASA_FB1

| __IO uint32_t CSI_Type::CSIDMASA_FB1 |

CSI DMA Start Address Register - for Frame Buffer1, offset: 0x28

Definition at line 8802 of file MIMXRT1052.h.

◆ CSIDMASA_FB2

| __IO uint32_t CSI_Type::CSIDMASA_FB2 |

CSI DMA Transfer Size Register - for Frame Buffer2, offset: 0x2C

Definition at line 8803 of file MIMXRT1052.h.

◆ CSIDMASA_STATFIFO

| __IO uint32_t CSI_Type::CSIDMASA_STATFIFO |

CSI DMA Start Address Register - for STATFIFO, offset: 0x20

Definition at line 8800 of file MIMXRT1052.h.

◆ CSIDMATS_STATFIFO

| __IO uint32_t CSI_Type::CSIDMATS_STATFIFO |

CSI DMA Transfer Size Register - for STATFIFO, offset: 0x24

Definition at line 8801 of file MIMXRT1052.h.

◆ CSIFBUF_PARA

| __IO uint32_t CSI_Type::CSIFBUF_PARA |

CSI Frame Buffer Parameter Register, offset: 0x30

Definition at line 8804 of file MIMXRT1052.h.

◆ CSIIMAG_PARA

| __IO uint32_t CSI_Type::CSIIMAG_PARA |

CSI Image Parameter Register, offset: 0x34

Definition at line 8805 of file MIMXRT1052.h.

◆ CSIRFIFO

| __I uint32_t CSI_Type::CSIRFIFO |

CSI RX FIFO Register, offset: 0x10

Definition at line 8796 of file MIMXRT1052.h.

◆ CSIRXCNT

| __IO uint32_t CSI_Type::CSIRXCNT |

CSI RX Count Register, offset: 0x14

Definition at line 8797 of file MIMXRT1052.h.

◆ CSISR

| __IO uint32_t CSI_Type::CSISR |

CSI Status Register, offset: 0x18

Definition at line 8798 of file MIMXRT1052.h.

◆ CSISTATFIFO

| __I uint32_t CSI_Type::CSISTATFIFO |

CSI Statistic FIFO Register, offset: 0xC

Definition at line 8795 of file MIMXRT1052.h.

◆ CSL

| __IO uint32_t CSU_Type::CSL[32] |

Config security level register, array offset: 0x0, array step: 0x4

Definition at line 9470 of file MIMXRT1052.h.

◆ CSR [1/3]

| __I uint32_t CCM_Type::CSR |

CCM Status Register, offset: 0x8

Definition at line 4157 of file MIMXRT1052.h.

◆ CSR [2/3]

| __IO uint16_t DMA_Type::CSR |

TCD Control and Status, array offset: 0x101C, array step: 0x20

Definition at line 12021 of file MIMXRT1052.h.

◆ CSR [3/3]

| __IO { ... } ::CSR |

TCD Control and Status, array offset: 0x101C, array step: 0x20

Definition at line 12021 of file MIMXRT1052.h.

◆ CTR_NONCE0_W0

| __O uint32_t BEE_Type::CTR_NONCE0_W0 |

NONCE00 Register, offset: 0x20

Definition at line 3019 of file MIMXRT1052.h.

◆ CTR_NONCE0_W1

| __O uint32_t BEE_Type::CTR_NONCE0_W1 |

NONCE01 Register, offset: 0x24

Definition at line 3020 of file MIMXRT1052.h.

◆ CTR_NONCE0_W2

| __O uint32_t BEE_Type::CTR_NONCE0_W2 |

NONCE02 Register, offset: 0x28

Definition at line 3021 of file MIMXRT1052.h.

◆ CTR_NONCE0_W3

| __O uint32_t BEE_Type::CTR_NONCE0_W3 |

NONCE03 Register, offset: 0x2C

Definition at line 3022 of file MIMXRT1052.h.

◆ CTR_NONCE1_W0

| __O uint32_t BEE_Type::CTR_NONCE1_W0 |

NONCE10 Register, offset: 0x30

Definition at line 3023 of file MIMXRT1052.h.

◆ CTR_NONCE1_W1

| __O uint32_t BEE_Type::CTR_NONCE1_W1 |

NONCE11 Register, offset: 0x34

Definition at line 3024 of file MIMXRT1052.h.

◆ CTR_NONCE1_W2

| __O uint32_t BEE_Type::CTR_NONCE1_W2 |

NONCE12 Register, offset: 0x38

Definition at line 3025 of file MIMXRT1052.h.

◆ CTR_NONCE1_W3

| __O uint32_t BEE_Type::CTR_NONCE1_W3 |

NONCE13 Register, offset: 0x3C

Definition at line 3026 of file MIMXRT1052.h.

◆ CTRL [1/15]

| __IO uint32_t ADC_ETC_Type::CTRL |

ADC_ETC Global Control Register, offset: 0x0

Definition at line 1618 of file MIMXRT1052.h.

◆ CTRL [2/15]

| __IO uint32_t BEE_Type::CTRL |

Control Register, offset: 0x0

Definition at line 3011 of file MIMXRT1052.h.

◆ CTRL [3/15]

| __IO uint32_t DCP_Type::CTRL |

DCP control register 0, offset: 0x0

Definition at line 10270 of file MIMXRT1052.h.

◆ CTRL [4/15]

| __IO uint16_t ENC_Type::CTRL |

Control Register, offset: 0x0

Definition at line 15139 of file MIMXRT1052.h.

◆ CTRL [5/15]

| __IO uint8_t EWM_Type::CTRL |

Control Register, offset: 0x0

Definition at line 17247 of file MIMXRT1052.h.

◆ CTRL [6/15]

| __IO uint32_t FLEXIO_Type::CTRL |

FlexIO Control Register, offset: 0x8

Definition at line 17369 of file MIMXRT1052.h.

◆ CTRL [7/15]

| __IO uint32_t LCDIF_Type::CTRL |

LCDIF General Control Register, offset: 0x0

Definition at line 23519 of file MIMXRT1052.h.

◆ CTRL [8/15]

| __IO uint32_t LPUART_Type::CTRL |

LPUART Control Register, offset: 0x18

Definition at line 26778 of file MIMXRT1052.h.

◆ CTRL [9/15]

| __IO uint32_t OCOTP_Type::CTRL |

OTP Controller Control Register, offset: 0x0

Definition at line 27699 of file MIMXRT1052.h.

◆ CTRL [10/15]

| __IO uint16_t PWM_Type::CTRL |

Control Register, array offset: 0x6, array step: 0x60

Definition at line 30848 of file MIMXRT1052.h.

◆ CTRL [11/15]

| __IO { ... } ::CTRL |

Control Register, array offset: 0x6, array step: 0x60

Definition at line 30848 of file MIMXRT1052.h.

◆ CTRL [12/15]

| __IO uint32_t PXP_Type::CTRL |

Control Register 0, offset: 0x0

Definition at line 32510 of file MIMXRT1052.h.

◆ CTRL [13/15]

| __IO uint16_t TMR_Type::CTRL |

Timer Channel Control Register, array offset: 0xC, array step: 0x20

Definition at line 37386 of file MIMXRT1052.h.

◆ CTRL [14/15]

| __IO { ... } ::CTRL |

Timer Channel Control Register, array offset: 0xC, array step: 0x20

Definition at line 37386 of file MIMXRT1052.h.

◆ CTRL [15/15]

| __IO uint32_t USBPHY_Type::CTRL |

USB PHY General Control Register, offset: 0x30

Definition at line 40696 of file MIMXRT1052.h.

◆ CTRL0

| __IO uint16_t XBARA_Type::CTRL0 |

Crossbar A Control Register 0, offset: 0x84

Definition at line 44201 of file MIMXRT1052.h.

◆ CTRL1 [1/3]

| __IO uint32_t CAN_Type::CTRL1 |

Control 1 Register, offset: 0x4

Definition at line 3314 of file MIMXRT1052.h.

◆ CTRL1 [2/3]

| __IO uint32_t LCDIF_Type::CTRL1 |

LCDIF General Control1 Register, offset: 0x10

Definition at line 23523 of file MIMXRT1052.h.

◆ CTRL1 [3/3]

| __IO uint16_t XBARA_Type::CTRL1 |

Crossbar A Control Register 1, offset: 0x86

Definition at line 44202 of file MIMXRT1052.h.

◆ CTRL1_CLR

| __IO uint32_t LCDIF_Type::CTRL1_CLR |

LCDIF General Control1 Register, offset: 0x18

Definition at line 23525 of file MIMXRT1052.h.

◆ CTRL1_SET

| __IO uint32_t LCDIF_Type::CTRL1_SET |

LCDIF General Control1 Register, offset: 0x14

Definition at line 23524 of file MIMXRT1052.h.

◆ CTRL1_TOG

| __IO uint32_t LCDIF_Type::CTRL1_TOG |

LCDIF General Control1 Register, offset: 0x1C

Definition at line 23526 of file MIMXRT1052.h.

◆ CTRL2 [1/5]

| __IO uint32_t CAN_Type::CTRL2 |

Control 2 Register, offset: 0x34

Definition at line 3326 of file MIMXRT1052.h.

◆ CTRL2 [2/5]

| __IO uint16_t ENC_Type::CTRL2 |

Control 2 Register, offset: 0x1E

Definition at line 15154 of file MIMXRT1052.h.

◆ CTRL2 [3/5]

| __IO uint32_t LCDIF_Type::CTRL2 |

LCDIF General Control2 Register, offset: 0x20

Definition at line 23527 of file MIMXRT1052.h.

◆ CTRL2 [4/5]

| __IO uint16_t PWM_Type::CTRL2 |

Control 2 Register, array offset: 0x4, array step: 0x60

Definition at line 30847 of file MIMXRT1052.h.

◆ CTRL2 [5/5]

| __IO { ... } ::CTRL2 |

Control 2 Register, array offset: 0x4, array step: 0x60

Definition at line 30847 of file MIMXRT1052.h.

◆ CTRL2_CLR

| __IO uint32_t LCDIF_Type::CTRL2_CLR |

LCDIF General Control2 Register, offset: 0x28

Definition at line 23529 of file MIMXRT1052.h.

◆ CTRL2_SET

| __IO uint32_t LCDIF_Type::CTRL2_SET |

LCDIF General Control2 Register, offset: 0x24

Definition at line 23528 of file MIMXRT1052.h.

◆ CTRL2_TOG

| __IO uint32_t LCDIF_Type::CTRL2_TOG |

LCDIF General Control2 Register, offset: 0x2C

Definition at line 23530 of file MIMXRT1052.h.

◆ CTRL_CLR [1/5]

| __IO uint32_t DCP_Type::CTRL_CLR |

DCP control register 0, offset: 0x8

Definition at line 10272 of file MIMXRT1052.h.

◆ CTRL_CLR [2/5]

| __IO uint32_t LCDIF_Type::CTRL_CLR |

LCDIF General Control Register, offset: 0x8

Definition at line 23521 of file MIMXRT1052.h.

◆ CTRL_CLR [3/5]

| __IO uint32_t OCOTP_Type::CTRL_CLR |

OTP Controller Control Register, offset: 0x8

Definition at line 27701 of file MIMXRT1052.h.

◆ CTRL_CLR [4/5]

| __IO uint32_t PXP_Type::CTRL_CLR |

Control Register 0, offset: 0x8

Definition at line 32512 of file MIMXRT1052.h.

◆ CTRL_CLR [5/5]

| __IO uint32_t USBPHY_Type::CTRL_CLR |

USB PHY General Control Register, offset: 0x38

Definition at line 40698 of file MIMXRT1052.h.

◆ CTRL_SET [1/5]

| __IO uint32_t DCP_Type::CTRL_SET |

DCP control register 0, offset: 0x4

Definition at line 10271 of file MIMXRT1052.h.

◆ CTRL_SET [2/5]

| __IO uint32_t LCDIF_Type::CTRL_SET |

LCDIF General Control Register, offset: 0x4

Definition at line 23520 of file MIMXRT1052.h.

◆ CTRL_SET [3/5]

| __IO uint32_t OCOTP_Type::CTRL_SET |

OTP Controller Control Register, offset: 0x4

Definition at line 27700 of file MIMXRT1052.h.

◆ CTRL_SET [4/5]

| __IO uint32_t PXP_Type::CTRL_SET |

Control Register 0, offset: 0x4

Definition at line 32511 of file MIMXRT1052.h.

◆ CTRL_SET [5/5]

| __IO uint32_t USBPHY_Type::CTRL_SET |

USB PHY General Control Register, offset: 0x34

Definition at line 40697 of file MIMXRT1052.h.

◆ CTRL_TOG [1/5]

| __IO uint32_t DCP_Type::CTRL_TOG |

DCP control register 0, offset: 0xC

Definition at line 10273 of file MIMXRT1052.h.

◆ CTRL_TOG [2/5]

| __IO uint32_t LCDIF_Type::CTRL_TOG |

LCDIF General Control Register, offset: 0xC

Definition at line 23522 of file MIMXRT1052.h.

◆ CTRL_TOG [3/5]

| __IO uint32_t OCOTP_Type::CTRL_TOG |

OTP Controller Control Register, offset: 0xC

Definition at line 27702 of file MIMXRT1052.h.

◆ CTRL_TOG [4/5]

| __IO uint32_t PXP_Type::CTRL_TOG |

Control Register 0, offset: 0xC

Definition at line 32513 of file MIMXRT1052.h.

◆ CTRL_TOG [5/5]

| __IO uint32_t USBPHY_Type::CTRL_TOG |

USB PHY General Control Register, offset: 0x3C

Definition at line 40699 of file MIMXRT1052.h.

◆ CUR_BUF

| __IO uint32_t LCDIF_Type::CUR_BUF |

LCD Interface Current Buffer Address Register, offset: 0x40

Definition at line 23533 of file MIMXRT1052.h.

◆ CV

| __IO uint32_t ADC_Type::CV |

Compare value register, offset: 0x50

Definition at line 1303 of file MIMXRT1052.h.

◆ CVAL [1/2]

| __I uint32_t PIT_Type::CVAL |

Current Timer Value Register, array offset: 0x104, array step: 0x10

Definition at line 28517 of file MIMXRT1052.h.

◆ CVAL [2/2]

| __I { ... } ::CVAL |

Current Timer Value Register, array offset: 0x104, array step: 0x10

Definition at line 28517 of file MIMXRT1052.h.

◆ CVAL0 [1/2]

| __I uint16_t PWM_Type::CVAL0 |

Capture Value 0 Register, array offset: 0x40, array step: 0x60

Definition at line 30876 of file MIMXRT1052.h.

◆ CVAL0 [2/2]

| __I { ... } ::CVAL0 |

Capture Value 0 Register, array offset: 0x40, array step: 0x60

Definition at line 30876 of file MIMXRT1052.h.

◆ CVAL0CYC [1/2]

| __I uint16_t PWM_Type::CVAL0CYC |

Capture Value 0 Cycle Register, array offset: 0x42, array step: 0x60

Definition at line 30877 of file MIMXRT1052.h.

◆ CVAL0CYC [2/2]

| __I { ... } ::CVAL0CYC |

Capture Value 0 Cycle Register, array offset: 0x42, array step: 0x60

Definition at line 30877 of file MIMXRT1052.h.

◆ CVAL1 [1/2]

| __I uint16_t PWM_Type::CVAL1 |

Capture Value 1 Register, array offset: 0x44, array step: 0x60

Definition at line 30878 of file MIMXRT1052.h.

◆ CVAL1 [2/2]

| __I { ... } ::CVAL1 |

Capture Value 1 Register, array offset: 0x44, array step: 0x60

Definition at line 30878 of file MIMXRT1052.h.

◆ CVAL1CYC [1/2]

| __I uint16_t PWM_Type::CVAL1CYC |

Capture Value 1 Cycle Register, array offset: 0x46, array step: 0x60

Definition at line 30879 of file MIMXRT1052.h.

◆ CVAL1CYC [2/2]

| __I { ... } ::CVAL1CYC |

Capture Value 1 Cycle Register, array offset: 0x46, array step: 0x60

Definition at line 30879 of file MIMXRT1052.h.

◆ CVAL2 [1/2]

| __I uint16_t PWM_Type::CVAL2 |

Capture Value 2 Register, array offset: 0x48, array step: 0x60

Definition at line 30880 of file MIMXRT1052.h.

◆ CVAL2 [2/2]

| __I { ... } ::CVAL2 |

Capture Value 2 Register, array offset: 0x48, array step: 0x60

Definition at line 30880 of file MIMXRT1052.h.

◆ CVAL2CYC [1/2]

| __I uint16_t PWM_Type::CVAL2CYC |

Capture Value 2 Cycle Register, array offset: 0x4A, array step: 0x60

Definition at line 30881 of file MIMXRT1052.h.

◆ CVAL2CYC [2/2]

| __I { ... } ::CVAL2CYC |

Capture Value 2 Cycle Register, array offset: 0x4A, array step: 0x60

Definition at line 30881 of file MIMXRT1052.h.

◆ CVAL3 [1/2]

| __I uint16_t PWM_Type::CVAL3 |

Capture Value 3 Register, array offset: 0x4C, array step: 0x60

Definition at line 30882 of file MIMXRT1052.h.

◆ CVAL3 [2/2]

| __I { ... } ::CVAL3 |

Capture Value 3 Register, array offset: 0x4C, array step: 0x60

Definition at line 30882 of file MIMXRT1052.h.

◆ CVAL3CYC [1/2]

| __I uint16_t PWM_Type::CVAL3CYC |

Capture Value 3 Cycle Register, array offset: 0x4E, array step: 0x60

Definition at line 30883 of file MIMXRT1052.h.

◆ CVAL3CYC [2/2]

| __I { ... } ::CVAL3CYC |

Capture Value 3 Cycle Register, array offset: 0x4E, array step: 0x60

Definition at line 30883 of file MIMXRT1052.h.

◆ CVAL4 [1/2]

| __I uint16_t PWM_Type::CVAL4 |

Capture Value 4 Register, array offset: 0x50, array step: 0x60

Definition at line 30884 of file MIMXRT1052.h.

◆ CVAL4 [2/2]

| __I { ... } ::CVAL4 |

Capture Value 4 Register, array offset: 0x50, array step: 0x60

Definition at line 30884 of file MIMXRT1052.h.

◆ CVAL4CYC [1/2]

| __I uint16_t PWM_Type::CVAL4CYC |

Capture Value 4 Cycle Register, array offset: 0x52, array step: 0x60

Definition at line 30885 of file MIMXRT1052.h.

◆ CVAL4CYC [2/2]

| __I { ... } ::CVAL4CYC |

Capture Value 4 Cycle Register, array offset: 0x52, array step: 0x60

Definition at line 30885 of file MIMXRT1052.h.

◆ CVAL5 [1/2]

| __I uint16_t PWM_Type::CVAL5 |

Capture Value 5 Register, array offset: 0x54, array step: 0x60

Definition at line 30886 of file MIMXRT1052.h.

◆ CVAL5 [2/2]

| __I { ... } ::CVAL5 |

Capture Value 5 Register, array offset: 0x54, array step: 0x60

Definition at line 30886 of file MIMXRT1052.h.

◆ CVAL5CYC [1/2]

| __I uint16_t PWM_Type::CVAL5CYC |

Capture Value 5 Cycle Register, array offset: 0x56, array step: 0x60

Definition at line 30887 of file MIMXRT1052.h.

◆ CVAL5CYC [2/2]

| __I { ... } ::CVAL5CYC |

Capture Value 5 Cycle Register, array offset: 0x56, array step: 0x60

Definition at line 30887 of file MIMXRT1052.h.

◆ DACCR

| __IO uint8_t CMP_Type::DACCR |

DAC Control Register, offset: 0x4

Definition at line 8546 of file MIMXRT1052.h.

◆ DADDR [1/2]

| __IO uint32_t DMA_Type::DADDR |

TCD Destination Address, array offset: 0x1010, array step: 0x20

Definition at line 12014 of file MIMXRT1052.h.

◆ DADDR [2/2]

| __IO { ... } ::DADDR |

TCD Destination Address, array offset: 0x1010, array step: 0x20

Definition at line 12014 of file MIMXRT1052.h.

◆ DATA [1/2]

| __IO uint32_t LPUART_Type::DATA |

LPUART Data Register, offset: 0x1C

Definition at line 26779 of file MIMXRT1052.h.

◆ DATA [2/2]

| __IO uint32_t OCOTP_Type::DATA |

OTP Controller Write Data Register, offset: 0x20

Definition at line 27705 of file MIMXRT1052.h.

◆ DATA_BUFF_ACC_PORT

| __IO uint32_t USDHC_Type::DATA_BUFF_ACC_PORT |

Data Buffer Access Port, offset: 0x20

Definition at line 42262 of file MIMXRT1052.h.

◆ DBG1

| __I uint32_t CAN_Type::DBG1 |

Debug 1 register, offset: 0x58

Definition at line 3333 of file MIMXRT1052.h.

◆ DBG2

| __I uint32_t CAN_Type::DBG2 |

Debug 2 register, offset: 0x5C

Definition at line 3334 of file MIMXRT1052.h.

◆ DBGDATA

| __I uint32_t DCP_Type::DBGDATA |

DCP debug data register, offset: 0x410

Definition at line 10357 of file MIMXRT1052.h.

◆ DBGSELECT

| __IO uint32_t DCP_Type::DBGSELECT |

DCP debug select register, offset: 0x400

Definition at line 10355 of file MIMXRT1052.h.

◆ DBICR0

| __IO uint32_t SEMC_Type::DBICR0 |

DBI-B control register 0, offset: 0x80

Definition at line 34154 of file MIMXRT1052.h.

◆ DBICR1

| __IO uint32_t SEMC_Type::DBICR1 |

DBI-B control register 1, offset: 0x84

Definition at line 34155 of file MIMXRT1052.h.

◆ DCCPARAMS

| __I uint32_t USB_Type::DCCPARAMS |

Device Controller Capability Parameters, offset: 0x124

Definition at line 39015 of file MIMXRT1052.h.

◆ DCHPRI0

| __IO uint8_t DMA_Type::DCHPRI0 |

Channel n Priority Register, offset: 0x103

Definition at line 11974 of file MIMXRT1052.h.

◆ DCHPRI1

| __IO uint8_t DMA_Type::DCHPRI1 |

Channel n Priority Register, offset: 0x102

Definition at line 11973 of file MIMXRT1052.h.

◆ DCHPRI10

| __IO uint8_t DMA_Type::DCHPRI10 |

Channel n Priority Register, offset: 0x109

Definition at line 11980 of file MIMXRT1052.h.

◆ DCHPRI11

| __IO uint8_t DMA_Type::DCHPRI11 |

Channel n Priority Register, offset: 0x108

Definition at line 11979 of file MIMXRT1052.h.

◆ DCHPRI12

| __IO uint8_t DMA_Type::DCHPRI12 |

Channel n Priority Register, offset: 0x10F

Definition at line 11986 of file MIMXRT1052.h.

◆ DCHPRI13

| __IO uint8_t DMA_Type::DCHPRI13 |

Channel n Priority Register, offset: 0x10E

Definition at line 11985 of file MIMXRT1052.h.

◆ DCHPRI14

| __IO uint8_t DMA_Type::DCHPRI14 |

Channel n Priority Register, offset: 0x10D

Definition at line 11984 of file MIMXRT1052.h.

◆ DCHPRI15

| __IO uint8_t DMA_Type::DCHPRI15 |

Channel n Priority Register, offset: 0x10C

Definition at line 11983 of file MIMXRT1052.h.

◆ DCHPRI16

| __IO uint8_t DMA_Type::DCHPRI16 |

Channel n Priority Register, offset: 0x113

Definition at line 11990 of file MIMXRT1052.h.

◆ DCHPRI17

| __IO uint8_t DMA_Type::DCHPRI17 |

Channel n Priority Register, offset: 0x112

Definition at line 11989 of file MIMXRT1052.h.

◆ DCHPRI18

| __IO uint8_t DMA_Type::DCHPRI18 |

Channel n Priority Register, offset: 0x111

Definition at line 11988 of file MIMXRT1052.h.

◆ DCHPRI19

| __IO uint8_t DMA_Type::DCHPRI19 |

Channel n Priority Register, offset: 0x110

Definition at line 11987 of file MIMXRT1052.h.

◆ DCHPRI2

| __IO uint8_t DMA_Type::DCHPRI2 |

Channel n Priority Register, offset: 0x101

Definition at line 11972 of file MIMXRT1052.h.

◆ DCHPRI20

| __IO uint8_t DMA_Type::DCHPRI20 |

Channel n Priority Register, offset: 0x117

Definition at line 11994 of file MIMXRT1052.h.

◆ DCHPRI21

| __IO uint8_t DMA_Type::DCHPRI21 |

Channel n Priority Register, offset: 0x116

Definition at line 11993 of file MIMXRT1052.h.

◆ DCHPRI22

| __IO uint8_t DMA_Type::DCHPRI22 |

Channel n Priority Register, offset: 0x115

Definition at line 11992 of file MIMXRT1052.h.

◆ DCHPRI23

| __IO uint8_t DMA_Type::DCHPRI23 |

Channel n Priority Register, offset: 0x114

Definition at line 11991 of file MIMXRT1052.h.

◆ DCHPRI24

| __IO uint8_t DMA_Type::DCHPRI24 |

Channel n Priority Register, offset: 0x11B

Definition at line 11998 of file MIMXRT1052.h.

◆ DCHPRI25

| __IO uint8_t DMA_Type::DCHPRI25 |

Channel n Priority Register, offset: 0x11A

Definition at line 11997 of file MIMXRT1052.h.

◆ DCHPRI26

| __IO uint8_t DMA_Type::DCHPRI26 |

Channel n Priority Register, offset: 0x119

Definition at line 11996 of file MIMXRT1052.h.

◆ DCHPRI27

| __IO uint8_t DMA_Type::DCHPRI27 |

Channel n Priority Register, offset: 0x118

Definition at line 11995 of file MIMXRT1052.h.

◆ DCHPRI28

| __IO uint8_t DMA_Type::DCHPRI28 |

Channel n Priority Register, offset: 0x11F

Definition at line 12002 of file MIMXRT1052.h.

◆ DCHPRI29

| __IO uint8_t DMA_Type::DCHPRI29 |

Channel n Priority Register, offset: 0x11E

Definition at line 12001 of file MIMXRT1052.h.

◆ DCHPRI3

| __IO uint8_t DMA_Type::DCHPRI3 |

Channel n Priority Register, offset: 0x100

Definition at line 11971 of file MIMXRT1052.h.

◆ DCHPRI30

| __IO uint8_t DMA_Type::DCHPRI30 |

Channel n Priority Register, offset: 0x11D

Definition at line 12000 of file MIMXRT1052.h.

◆ DCHPRI31

| __IO uint8_t DMA_Type::DCHPRI31 |

Channel n Priority Register, offset: 0x11C

Definition at line 11999 of file MIMXRT1052.h.

◆ DCHPRI4

| __IO uint8_t DMA_Type::DCHPRI4 |

Channel n Priority Register, offset: 0x107

Definition at line 11978 of file MIMXRT1052.h.

◆ DCHPRI5

| __IO uint8_t DMA_Type::DCHPRI5 |

Channel n Priority Register, offset: 0x106

Definition at line 11977 of file MIMXRT1052.h.

◆ DCHPRI6

| __IO uint8_t DMA_Type::DCHPRI6 |

Channel n Priority Register, offset: 0x105

Definition at line 11976 of file MIMXRT1052.h.

◆ DCHPRI7

| __IO uint8_t DMA_Type::DCHPRI7 |

Channel n Priority Register, offset: 0x104

Definition at line 11975 of file MIMXRT1052.h.

◆ DCHPRI8

| __IO uint8_t DMA_Type::DCHPRI8 |

Channel n Priority Register, offset: 0x10B

Definition at line 11982 of file MIMXRT1052.h.

◆ DCHPRI9

| __IO uint8_t DMA_Type::DCHPRI9 |

Channel n Priority Register, offset: 0x10A

Definition at line 11981 of file MIMXRT1052.h.

◆ DCIVERSION

| __I uint16_t USB_Type::DCIVERSION |

Device Controller Interface Version, offset: 0x120

Definition at line 39013 of file MIMXRT1052.h.

◆ DEBUG0_STATUS

| __I uint32_t USBPHY_Type::DEBUG0_STATUS |

UTMI Debug Status Register 0, offset: 0x60

Definition at line 40706 of file MIMXRT1052.h.

◆ DEBUG1

| __IO uint32_t USBPHY_Type::DEBUG1 |

UTMI Debug Status Register 1, offset: 0x70

Definition at line 40708 of file MIMXRT1052.h.

◆ DEBUG1_CLR

| __IO uint32_t USBPHY_Type::DEBUG1_CLR |

UTMI Debug Status Register 1, offset: 0x78

Definition at line 40710 of file MIMXRT1052.h.

◆ DEBUG1_SET

| __IO uint32_t USBPHY_Type::DEBUG1_SET |

UTMI Debug Status Register 1, offset: 0x74

Definition at line 40709 of file MIMXRT1052.h.

◆ DEBUG1_TOG

| __IO uint32_t USBPHY_Type::DEBUG1_TOG |

UTMI Debug Status Register 1, offset: 0x7C

Definition at line 40711 of file MIMXRT1052.h.

◆ DEBUG_CLR

| __IO uint32_t USBPHY_Type::DEBUG_CLR |

USB PHY Debug Register, offset: 0x58

Definition at line 40704 of file MIMXRT1052.h.

◆ DEBUG_MODE

| __IO uint32_t TSC_Type::DEBUG_MODE |

Debug Mode Register, offset: 0x70

Definition at line 38561 of file MIMXRT1052.h.

◆ DEBUG_MODE2

| __IO uint32_t TSC_Type::DEBUG_MODE2 |

Debug Mode Register 2, offset: 0x80

Definition at line 38563 of file MIMXRT1052.h.

◆ DEBUG_SET

| __IO uint32_t USBPHY_Type::DEBUG_SET |

USB PHY Debug Register, offset: 0x54

Definition at line 40703 of file MIMXRT1052.h.

◆ DEBUG_TOG

| __IO uint32_t USBPHY_Type::DEBUG_TOG |

USB PHY Debug Register, offset: 0x5C

Definition at line 40705 of file MIMXRT1052.h.

◆ DEBUGr

| __IO uint32_t USBPHY_Type::DEBUGr |

USB PHY Debug Register, offset: 0x50

Definition at line 40702 of file MIMXRT1052.h.

◆ DER

| __IO uint32_t LPSPI_Type::DER |

DMA Enable Register, offset: 0x1C

Definition at line 26151 of file MIMXRT1052.h.

◆ DEVICEADDR [1/2]

| __IO uint32_t USB_Type::DEVICEADDR |

Device Address, offset: 0x154

Definition at line 39023 of file MIMXRT1052.h.

◆ DEVICEADDR [2/2]

| __IO { ... } ::DEVICEADDR |

Device Address, offset: 0x154

Definition at line 39023 of file MIMXRT1052.h.

◆ DIGPROG

| __I uint32_t USB_ANALOG_Type::DIGPROG |

Chip Silicon Version, offset: 0x260

Definition at line 41822 of file MIMXRT1052.h.

◆ DISMAP [1/2]

| __IO uint16_t PWM_Type::DISMAP[2] |

Fault Disable Mapping Register 0..Fault Disable Mapping Register 1, array offset: 0x2C, array step: index*0x60, index2*0x2

Definition at line 30867 of file MIMXRT1052.h.

◆ DISMAP [2/2]

| __IO { ... } ::DISMAP[2] |

Fault Disable Mapping Register 0..Fault Disable Mapping Register 1, array offset: 0x2C, array step: index*0x60, index2*0x2

Definition at line 30867 of file MIMXRT1052.h.

◆ DLAST_SGA [1/2]

| __IO uint32_t DMA_Type::DLAST_SGA |

TCD Last Destination Address Adjustment/Scatter Gather Address, array offset: 0x1018, array step: 0x20

Definition at line 12020 of file MIMXRT1052.h.

◆ DLAST_SGA [2/2]

| __IO { ... } ::DLAST_SGA |

TCD Last Destination Address Adjustment/Scatter Gather Address, array offset: 0x1018, array step: 0x20

Definition at line 12020 of file MIMXRT1052.h.

◆ DLL_CTRL

| __IO uint32_t USDHC_Type::DLL_CTRL |

DLL (Delay Line) Control, offset: 0x60

Definition at line 42278 of file MIMXRT1052.h.

◆ DLL_STATUS

| __I uint32_t USDHC_Type::DLL_STATUS |

DLL Status, offset: 0x64

Definition at line 42279 of file MIMXRT1052.h.

◆ DLLCR

| __IO uint32_t FLEXSPI_Type::DLLCR[2] |

DLL Control Register 0, array offset: 0xC0, array step: 0x4

Definition at line 18113 of file MIMXRT1052.h.

◆ DMA [1/2]

| __IO { ... } ::DMA |

Timer Channel DMA Enable Register, array offset: 0x18, array step: 0x20

Definition at line 37392 of file MIMXRT1052.h.

◆ DMA [2/2]

| __IO uint16_t TMR_Type::DMA |

Timer Channel DMA Enable Register, array offset: 0x18, array step: 0x20

Definition at line 37392 of file MIMXRT1052.h.

◆ DMA_CTRL

| __IO uint32_t ADC_ETC_Type::DMA_CTRL |

ETC DMA control Register, offset: 0xC

Definition at line 1621 of file MIMXRT1052.h.

◆ DMAEN [1/2]

| __IO uint16_t PWM_Type::DMAEN |

DMA Enable Register, array offset: 0x28, array step: 0x60

Definition at line 30865 of file MIMXRT1052.h.

◆ DMAEN [2/2]

| __IO { ... } ::DMAEN |

DMA Enable Register, array offset: 0x28, array step: 0x60

Definition at line 30865 of file MIMXRT1052.h.

◆ DMR0

| __IO uint32_t LPSPI_Type::DMR0 |

Data Match Register 0, offset: 0x30

Definition at line 26155 of file MIMXRT1052.h.

◆ DMR1

| __IO uint32_t LPSPI_Type::DMR1 |

Data Match Register 1, offset: 0x34

Definition at line 26156 of file MIMXRT1052.h.

◆ DOFF [1/2]

| __IO uint16_t DMA_Type::DOFF |

TCD Signed Destination Address Offset, array offset: 0x1014, array step: 0x20

Definition at line 12015 of file MIMXRT1052.h.

◆ DOFF [2/2]

| __IO { ... } ::DOFF |

TCD Signed Destination Address Offset, array offset: 0x1014, array step: 0x20

Definition at line 12015 of file MIMXRT1052.h.

◆ DONE0_1_IRQ

| __IO uint32_t ADC_ETC_Type::DONE0_1_IRQ |

ETC DONE0 and DONE1 IRQ State Register, offset: 0x4

Definition at line 1619 of file MIMXRT1052.h.

◆ DONE2_ERR_IRQ

| __IO uint32_t ADC_ETC_Type::DONE2_ERR_IRQ |

ETC DONE_2 and DONE_ERR IRQ State Register, offset: 0x8

Definition at line 1620 of file MIMXRT1052.h.

◆ DR

| __IO uint32_t GPIO_Type::DR |

GPIO data register, offset: 0x0

Definition at line 19126 of file MIMXRT1052.h.

◆ DR_CLEAR

| __O uint32_t GPIO_Type::DR_CLEAR |

GPIO data register CLEAR, offset: 0x88

Definition at line 19136 of file MIMXRT1052.h.

◆ DR_SET

| __O uint32_t GPIO_Type::DR_SET |

GPIO data register SET, offset: 0x84

Definition at line 19135 of file MIMXRT1052.h.

◆ DR_TOGGLE

| __O uint32_t GPIO_Type::DR_TOGGLE |

GPIO data register TOGGLE, offset: 0x8C

Definition at line 19137 of file MIMXRT1052.h.

◆ DS_ADDR

| __IO uint32_t USDHC_Type::DS_ADDR |

DMA System Address, offset: 0x0

Definition at line 42254 of file MIMXRT1052.h.

◆ DTCNT0 [1/2]

| __IO uint16_t PWM_Type::DTCNT0 |

Deadtime Count Register 0, array offset: 0x30, array step: 0x60

Definition at line 30868 of file MIMXRT1052.h.

◆ DTCNT0 [2/2]

| __IO { ... } ::DTCNT0 |

Deadtime Count Register 0, array offset: 0x30, array step: 0x60

Definition at line 30868 of file MIMXRT1052.h.

◆ DTCNT1 [1/2]

| __IO uint16_t PWM_Type::DTCNT1 |

Deadtime Count Register 1, array offset: 0x32, array step: 0x60

Definition at line 30869 of file MIMXRT1052.h.

◆ DTCNT1 [2/2]

| __IO { ... } ::DTCNT1 |

Deadtime Count Register 1, array offset: 0x32, array step: 0x60

Definition at line 30869 of file MIMXRT1052.h.

◆ DTSRCSEL

| __IO uint16_t PWM_Type::DTSRCSEL |

PWM Source Select Register, offset: 0x186

Definition at line 30893 of file MIMXRT1052.h.

◆ EARS

| __IO uint32_t DMA_Type::EARS |

Enable Asynchronous Request in Stop Register, offset: 0x44

Definition at line 11969 of file MIMXRT1052.h.

◆ ECR [1/2]

| __IO uint32_t CAN_Type::ECR |

Error Counter Register, offset: 0x1C

Definition at line 3320 of file MIMXRT1052.h.

◆ ECR [2/2]

| __IO uint32_t ENET_Type::ECR |

Ethernet Control Register, offset: 0x24

Definition at line 15612 of file MIMXRT1052.h.

◆ EDGE_SEL

| __IO uint32_t GPIO_Type::EDGE_SEL |

GPIO edge select register, offset: 0x1C

Definition at line 19133 of file MIMXRT1052.h.

◆ EEI

| __IO uint32_t DMA_Type::EEI |

Enable Error Interrupt Register, offset: 0x14

Definition at line 11953 of file MIMXRT1052.h.

◆ EIMR

| __IO uint32_t ENET_Type::EIMR |

Interrupt Mask Register, offset: 0x8

Definition at line 15607 of file MIMXRT1052.h.

◆ EIR

| __IO uint32_t ENET_Type::EIR |

Interrupt Event Register, offset: 0x4

Definition at line 15606 of file MIMXRT1052.h.

◆ ENBL [1/2]

| __IO uint16_t TMR_Type::ENBL |

Timer Channel Enable Register, array offset: 0x1E, array step: 0x20, this item is not available for all array instances

Definition at line 37394 of file MIMXRT1052.h.

◆ ENBL [2/2]

| __IO { ... } ::ENBL |

Timer Channel Enable Register, array offset: 0x1E, array step: 0x20, this item is not available for all array instances

Definition at line 37394 of file MIMXRT1052.h.

◆ ENDPTCOMPLETE

| __IO uint32_t USB_Type::ENDPTCOMPLETE |

Endpoint Complete, offset: 0x1BC

Definition at line 39045 of file MIMXRT1052.h.

◆ ENDPTCTRL

| __IO uint32_t USB_Type::ENDPTCTRL[7] |

Endpoint Control 1..Endpoint Control 7, array offset: 0x1C4, array step: 0x4

Definition at line 39047 of file MIMXRT1052.h.

◆ ENDPTCTRL0

| __IO uint32_t USB_Type::ENDPTCTRL0 |

Endpoint Control0, offset: 0x1C0

Definition at line 39046 of file MIMXRT1052.h.

◆ ENDPTFLUSH

| __IO uint32_t USB_Type::ENDPTFLUSH |

Endpoint Flush, offset: 0x1B4

Definition at line 39043 of file MIMXRT1052.h.

◆ ENDPTLISTADDR [1/2]

| __IO uint32_t USB_Type::ENDPTLISTADDR |

Endpoint List Address, offset: 0x158

Definition at line 39028 of file MIMXRT1052.h.

◆ ENDPTLISTADDR [2/2]

| __IO { ... } ::ENDPTLISTADDR |

Endpoint List Address, offset: 0x158

Definition at line 39028 of file MIMXRT1052.h.

◆ ENDPTNAK

| __IO uint32_t USB_Type::ENDPTNAK |

Endpoint NAK, offset: 0x178

Definition at line 39034 of file MIMXRT1052.h.

◆ ENDPTNAKEN

| __IO uint32_t USB_Type::ENDPTNAKEN |

Endpoint NAK Enable, offset: 0x17C

Definition at line 39035 of file MIMXRT1052.h.

◆ ENDPTPRIME

| __IO uint32_t USB_Type::ENDPTPRIME |

Endpoint Prime, offset: 0x1B0

Definition at line 39042 of file MIMXRT1052.h.

◆ ENDPTSETUPSTAT

| __IO uint32_t USB_Type::ENDPTSETUPSTAT |

Endpoint Setup Status, offset: 0x1AC

Definition at line 39041 of file MIMXRT1052.h.

◆ ENDPTSTAT

| __I uint32_t USB_Type::ENDPTSTAT |

Endpoint Status, offset: 0x1B8

Definition at line 39044 of file MIMXRT1052.h.

◆ ENT

| __I uint32_t TRNG_Type::ENT[16] |

Entropy Read Register, array offset: 0x40, array step: 0x4

Definition at line 37921 of file MIMXRT1052.h.

◆ ERQ

| __IO uint32_t DMA_Type::ERQ |

Enable Request Register, offset: 0xC

Definition at line 11951 of file MIMXRT1052.h.

◆ ERR

| __IO uint32_t DMA_Type::ERR |

Error Register, offset: 0x2C

Definition at line 11965 of file MIMXRT1052.h.

◆ ES

| __I uint32_t DMA_Type::ES |

Error Status Register, offset: 0x4

Definition at line 11949 of file MIMXRT1052.h.

◆ ESR1

| __IO uint32_t CAN_Type::ESR1 |

Error and Status 1 Register, offset: 0x20

Definition at line 3321 of file MIMXRT1052.h.

◆ ESR2

| __I uint32_t CAN_Type::ESR2 |

Error and Status 2 Register, offset: 0x38

Definition at line 3327 of file MIMXRT1052.h.

◆ FCR

| __IO uint32_t LPSPI_Type::FCR |

FIFO Control Register, offset: 0x58

Definition at line 26160 of file MIMXRT1052.h.

◆ FCTRL

| __IO uint16_t PWM_Type::FCTRL |

Fault Control Register, offset: 0x18C

Definition at line 30896 of file MIMXRT1052.h.

◆ FCTRL2

| __IO uint16_t PWM_Type::FCTRL2 |

Fault Control 2 Register, offset: 0x194

Definition at line 30900 of file MIMXRT1052.h.

◆ FFILT

| __IO uint16_t PWM_Type::FFILT |

Fault Filter Register, offset: 0x190

Definition at line 30898 of file MIMXRT1052.h.

◆ FIFO

| __IO uint32_t LPUART_Type::FIFO |

LPUART FIFO Register, offset: 0x28

Definition at line 26782 of file MIMXRT1052.h.

◆ FILT [1/3]

| __IO uint16_t ENC_Type::FILT |

Input Filter Register, offset: 0x2

Definition at line 15140 of file MIMXRT1052.h.

◆ FILT [2/3]

| __IO uint16_t TMR_Type::FILT |

Timer Channel Input Filter Register, array offset: 0x16, array step: 0x20

Definition at line 37391 of file MIMXRT1052.h.

◆ FILT [3/3]

| __IO { ... } ::FILT |

Timer Channel Input Filter Register, array offset: 0x16, array step: 0x20

Definition at line 37391 of file MIMXRT1052.h.

◆ FLOW_CONTROL

| __IO uint32_t TSC_Type::FLOW_CONTROL |

Flow Control, offset: 0x20

Definition at line 38551 of file MIMXRT1052.h.

◆ FLSHCR0

| __IO uint32_t FLEXSPI_Type::FLSHCR0[4] |

Flash A1 Control Register 0..Flash B2 Control Register 0, array offset: 0x60, array step: 0x4

Definition at line 18100 of file MIMXRT1052.h.

◆ FLSHCR1

| __IO uint32_t FLEXSPI_Type::FLSHCR1[4] |

Flash A1 Control Register 1..Flash B2 Control Register 1, array offset: 0x70, array step: 0x4

Definition at line 18101 of file MIMXRT1052.h.

◆ FLSHCR2

| __IO uint32_t FLEXSPI_Type::FLSHCR2[4] |

Flash A1 Control Register 2..Flash B2 Control Register 2, array offset: 0x80, array step: 0x4

Definition at line 18102 of file MIMXRT1052.h.

◆ FLSHCR4

| __IO uint32_t FLEXSPI_Type::FLSHCR4 |

Flash Control Register 4, offset: 0x94

Definition at line 18104 of file MIMXRT1052.h.

◆ FORCE_EVENT

| __O uint32_t USDHC_Type::FORCE_EVENT |

Force Event, offset: 0x50

Definition at line 42274 of file MIMXRT1052.h.

◆ FPR

| __IO uint8_t CMP_Type::FPR |

CMP Filter Period Register, offset: 0x2

Definition at line 8544 of file MIMXRT1052.h.

◆ FRACVAL1 [1/2]

| __IO uint16_t PWM_Type::FRACVAL1 |