|

Classes | |

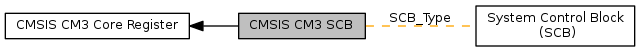

| struct | SCB_Type |

| Structure type to access the System Control Block (SCB). More... | |

Macros | |

| #define | SCB_AIRCR_ENDIANESS_Msk (1ul << SCB_AIRCR_ENDIANESS_Pos) |

| #define | SCB_AIRCR_ENDIANESS_Pos 15 |

| #define | SCB_AIRCR_PRIGROUP_Msk (7ul << SCB_AIRCR_PRIGROUP_Pos) |

| #define | SCB_AIRCR_PRIGROUP_Pos 8 |

| #define | SCB_AIRCR_SYSRESETREQ_Msk (1ul << SCB_AIRCR_SYSRESETREQ_Pos) |

| #define | SCB_AIRCR_SYSRESETREQ_Pos 2 |

| #define | SCB_AIRCR_VECTCLRACTIVE_Msk (1ul << SCB_AIRCR_VECTCLRACTIVE_Pos) |

| #define | SCB_AIRCR_VECTCLRACTIVE_Pos 1 |

| #define | SCB_AIRCR_VECTKEY_Msk (0xFFFFul << SCB_AIRCR_VECTKEY_Pos) |

| #define | SCB_AIRCR_VECTKEY_Pos 16 |

| #define | SCB_AIRCR_VECTKEYSTAT_Msk (0xFFFFul << SCB_AIRCR_VECTKEYSTAT_Pos) |

| #define | SCB_AIRCR_VECTKEYSTAT_Pos 16 |

| #define | SCB_AIRCR_VECTRESET_Msk (1ul << SCB_AIRCR_VECTRESET_Pos) |

| #define | SCB_AIRCR_VECTRESET_Pos 0 |

| #define | SCB_CCR_BFHFNMIGN_Msk (1ul << SCB_CCR_BFHFNMIGN_Pos) |

| #define | SCB_CCR_BFHFNMIGN_Pos 8 |

| #define | SCB_CCR_DIV_0_TRP_Msk (1ul << SCB_CCR_DIV_0_TRP_Pos) |

| #define | SCB_CCR_DIV_0_TRP_Pos 4 |

| #define | SCB_CCR_NONBASETHRDENA_Msk (1ul << SCB_CCR_NONBASETHRDENA_Pos) |

| #define | SCB_CCR_NONBASETHRDENA_Pos 0 |

| #define | SCB_CCR_STKALIGN_Msk (1ul << SCB_CCR_STKALIGN_Pos) |

| #define | SCB_CCR_STKALIGN_Pos 9 |

| #define | SCB_CCR_UNALIGN_TRP_Msk (1ul << SCB_CCR_UNALIGN_TRP_Pos) |

| #define | SCB_CCR_UNALIGN_TRP_Pos 3 |

| #define | SCB_CCR_USERSETMPEND_Msk (1ul << SCB_CCR_USERSETMPEND_Pos) |

| #define | SCB_CCR_USERSETMPEND_Pos 1 |

| #define | SCB_CFSR_BUSFAULTSR_Msk (0xFFul << SCB_CFSR_BUSFAULTSR_Pos) |

| #define | SCB_CFSR_BUSFAULTSR_Pos 8 |

| #define | SCB_CFSR_MEMFAULTSR_Msk (0xFFul << SCB_CFSR_MEMFAULTSR_Pos) |

| #define | SCB_CFSR_MEMFAULTSR_Pos 0 |

| #define | SCB_CFSR_USGFAULTSR_Msk (0xFFFFul << SCB_CFSR_USGFAULTSR_Pos) |

| #define | SCB_CFSR_USGFAULTSR_Pos 16 |

| #define | SCB_CPUID_IMPLEMENTER_Msk (0xFFul << SCB_CPUID_IMPLEMENTER_Pos) |

| #define | SCB_CPUID_IMPLEMENTER_Pos 24 |

| #define | SCB_CPUID_PARTNO_Msk (0xFFFul << SCB_CPUID_PARTNO_Pos) |

| #define | SCB_CPUID_PARTNO_Pos 4 |

| #define | SCB_CPUID_REVISION_Msk (0xFul << SCB_CPUID_REVISION_Pos) |

| #define | SCB_CPUID_REVISION_Pos 0 |

| #define | SCB_CPUID_VARIANT_Msk (0xFul << SCB_CPUID_VARIANT_Pos) |

| #define | SCB_CPUID_VARIANT_Pos 20 |

| #define | SCB_DFSR_BKPT_Msk (1ul << SCB_DFSR_BKPT_Pos) |

| #define | SCB_DFSR_BKPT_Pos 1 |

| #define | SCB_DFSR_DWTTRAP_Msk (1ul << SCB_DFSR_DWTTRAP_Pos) |

| #define | SCB_DFSR_DWTTRAP_Pos 2 |

| #define | SCB_DFSR_EXTERNAL_Msk (1ul << SCB_DFSR_EXTERNAL_Pos) |

| #define | SCB_DFSR_EXTERNAL_Pos 4 |

| #define | SCB_DFSR_HALTED_Msk (1ul << SCB_DFSR_HALTED_Pos) |

| #define | SCB_DFSR_HALTED_Pos 0 |

| #define | SCB_DFSR_VCATCH_Msk (1ul << SCB_DFSR_VCATCH_Pos) |

| #define | SCB_DFSR_VCATCH_Pos 3 |

| #define | SCB_HFSR_DEBUGEVT_Msk (1ul << SCB_HFSR_DEBUGEVT_Pos) |

| #define | SCB_HFSR_DEBUGEVT_Pos 31 |

| #define | SCB_HFSR_FORCED_Msk (1ul << SCB_HFSR_FORCED_Pos) |

| #define | SCB_HFSR_FORCED_Pos 30 |

| #define | SCB_HFSR_VECTTBL_Msk (1ul << SCB_HFSR_VECTTBL_Pos) |

| #define | SCB_HFSR_VECTTBL_Pos 1 |

| #define | SCB_ICSR_ISRPENDING_Msk (1ul << SCB_ICSR_ISRPENDING_Pos) |

| #define | SCB_ICSR_ISRPENDING_Pos 22 |

| #define | SCB_ICSR_ISRPREEMPT_Msk (1ul << SCB_ICSR_ISRPREEMPT_Pos) |

| #define | SCB_ICSR_ISRPREEMPT_Pos 23 |

| #define | SCB_ICSR_NMIPENDSET_Msk (1ul << SCB_ICSR_NMIPENDSET_Pos) |

| #define | SCB_ICSR_NMIPENDSET_Pos 31 |

| #define | SCB_ICSR_PENDSTCLR_Msk (1ul << SCB_ICSR_PENDSTCLR_Pos) |

| #define | SCB_ICSR_PENDSTCLR_Pos 25 |

| #define | SCB_ICSR_PENDSTSET_Msk (1ul << SCB_ICSR_PENDSTSET_Pos) |

| #define | SCB_ICSR_PENDSTSET_Pos 26 |

| #define | SCB_ICSR_PENDSVCLR_Msk (1ul << SCB_ICSR_PENDSVCLR_Pos) |

| #define | SCB_ICSR_PENDSVCLR_Pos 27 |

| #define | SCB_ICSR_PENDSVSET_Msk (1ul << SCB_ICSR_PENDSVSET_Pos) |

| #define | SCB_ICSR_PENDSVSET_Pos 28 |

| #define | SCB_ICSR_RETTOBASE_Msk (1ul << SCB_ICSR_RETTOBASE_Pos) |

| #define | SCB_ICSR_RETTOBASE_Pos 11 |

| #define | SCB_ICSR_VECTACTIVE_Msk (0x1FFul << SCB_ICSR_VECTACTIVE_Pos) |

| #define | SCB_ICSR_VECTACTIVE_Pos 0 |

| #define | SCB_ICSR_VECTPENDING_Msk (0x1FFul << SCB_ICSR_VECTPENDING_Pos) |

| #define | SCB_ICSR_VECTPENDING_Pos 12 |

| #define | SCB_SCR_SEVONPEND_Msk (1ul << SCB_SCR_SEVONPEND_Pos) |

| #define | SCB_SCR_SEVONPEND_Pos 4 |

| #define | SCB_SCR_SLEEPDEEP_Msk (1ul << SCB_SCR_SLEEPDEEP_Pos) |

| #define | SCB_SCR_SLEEPDEEP_Pos 2 |

| #define | SCB_SCR_SLEEPONEXIT_Msk (1ul << SCB_SCR_SLEEPONEXIT_Pos) |

| #define | SCB_SCR_SLEEPONEXIT_Pos 1 |

| #define | SCB_SHCSR_BUSFAULTACT_Msk (1ul << SCB_SHCSR_BUSFAULTACT_Pos) |

| #define | SCB_SHCSR_BUSFAULTACT_Pos 1 |

| #define | SCB_SHCSR_BUSFAULTENA_Msk (1ul << SCB_SHCSR_BUSFAULTENA_Pos) |

| #define | SCB_SHCSR_BUSFAULTENA_Pos 17 |

| #define | SCB_SHCSR_BUSFAULTPENDED_Msk (1ul << SCB_SHCSR_BUSFAULTPENDED_Pos) |

| #define | SCB_SHCSR_BUSFAULTPENDED_Pos 14 |

| #define | SCB_SHCSR_MEMFAULTACT_Msk (1ul << SCB_SHCSR_MEMFAULTACT_Pos) |

| #define | SCB_SHCSR_MEMFAULTACT_Pos 0 |

| #define | SCB_SHCSR_MEMFAULTENA_Msk (1ul << SCB_SHCSR_MEMFAULTENA_Pos) |

| #define | SCB_SHCSR_MEMFAULTENA_Pos 16 |

| #define | SCB_SHCSR_MEMFAULTPENDED_Msk (1ul << SCB_SHCSR_MEMFAULTPENDED_Pos) |

| #define | SCB_SHCSR_MEMFAULTPENDED_Pos 13 |

| #define | SCB_SHCSR_MONITORACT_Msk (1ul << SCB_SHCSR_MONITORACT_Pos) |

| #define | SCB_SHCSR_MONITORACT_Pos 8 |

| #define | SCB_SHCSR_PENDSVACT_Msk (1ul << SCB_SHCSR_PENDSVACT_Pos) |

| #define | SCB_SHCSR_PENDSVACT_Pos 10 |

| #define | SCB_SHCSR_SVCALLACT_Msk (1ul << SCB_SHCSR_SVCALLACT_Pos) |

| #define | SCB_SHCSR_SVCALLACT_Pos 7 |

| #define | SCB_SHCSR_SVCALLPENDED_Msk (1ul << SCB_SHCSR_SVCALLPENDED_Pos) |

| #define | SCB_SHCSR_SVCALLPENDED_Pos 15 |

| #define | SCB_SHCSR_SYSTICKACT_Msk (1ul << SCB_SHCSR_SYSTICKACT_Pos) |

| #define | SCB_SHCSR_SYSTICKACT_Pos 11 |

| #define | SCB_SHCSR_USGFAULTACT_Msk (1ul << SCB_SHCSR_USGFAULTACT_Pos) |

| #define | SCB_SHCSR_USGFAULTACT_Pos 3 |

| #define | SCB_SHCSR_USGFAULTENA_Msk (1ul << SCB_SHCSR_USGFAULTENA_Pos) |

| #define | SCB_SHCSR_USGFAULTENA_Pos 18 |

| #define | SCB_SHCSR_USGFAULTPENDED_Msk (1ul << SCB_SHCSR_USGFAULTPENDED_Pos) |

| #define | SCB_SHCSR_USGFAULTPENDED_Pos 12 |

| #define | SCB_VTOR_TBLBASE_Msk (0x1FFul << SCB_VTOR_TBLBASE_Pos) |

| #define | SCB_VTOR_TBLBASE_Pos 29 |

| #define | SCB_VTOR_TBLOFF_Msk (0x3FFFFFul << SCB_VTOR_TBLOFF_Pos) |

| #define | SCB_VTOR_TBLOFF_Pos 7 |

Detailed Description

memory mapped structure for System Control Block (SCB)

Macro Definition Documentation

| #define SCB_AIRCR_ENDIANESS_Msk (1ul << SCB_AIRCR_ENDIANESS_Pos) |

SCB AIRCR: ENDIANESS Mask

Definition at line 237 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_ENDIANESS_Pos 15 |

SCB AIRCR: ENDIANESS Position

Definition at line 236 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_PRIGROUP_Msk (7ul << SCB_AIRCR_PRIGROUP_Pos) |

SCB AIRCR: PRIGROUP Mask

Definition at line 240 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_PRIGROUP_Pos 8 |

SCB AIRCR: PRIGROUP Position

Definition at line 239 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_SYSRESETREQ_Msk (1ul << SCB_AIRCR_SYSRESETREQ_Pos) |

SCB AIRCR: SYSRESETREQ Mask

Definition at line 243 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_SYSRESETREQ_Pos 2 |

SCB AIRCR: SYSRESETREQ Position

Definition at line 242 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_VECTCLRACTIVE_Msk (1ul << SCB_AIRCR_VECTCLRACTIVE_Pos) |

SCB AIRCR: VECTCLRACTIVE Mask

Definition at line 246 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_VECTCLRACTIVE_Pos 1 |

SCB AIRCR: VECTCLRACTIVE Position

Definition at line 245 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_VECTKEY_Msk (0xFFFFul << SCB_AIRCR_VECTKEY_Pos) |

SCB AIRCR: VECTKEY Mask

Definition at line 231 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_VECTKEY_Pos 16 |

SCB AIRCR: VECTKEY Position

Definition at line 230 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_VECTKEYSTAT_Msk (0xFFFFul << SCB_AIRCR_VECTKEYSTAT_Pos) |

SCB AIRCR: VECTKEYSTAT Mask

Definition at line 234 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_VECTKEYSTAT_Pos 16 |

SCB AIRCR: VECTKEYSTAT Position

Definition at line 233 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_VECTRESET_Msk (1ul << SCB_AIRCR_VECTRESET_Pos) |

SCB AIRCR: VECTRESET Mask

Definition at line 250 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_AIRCR_VECTRESET_Pos 0 |

SCB AIRCR: VECTRESET Position

Definition at line 249 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CCR_BFHFNMIGN_Msk (1ul << SCB_CCR_BFHFNMIGN_Pos) |

SCB CCR: BFHFNMIGN Mask

Definition at line 267 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CCR_BFHFNMIGN_Pos 8 |

SCB CCR: BFHFNMIGN Position

Definition at line 266 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CCR_DIV_0_TRP_Msk (1ul << SCB_CCR_DIV_0_TRP_Pos) |

SCB CCR: DIV_0_TRP Mask

Definition at line 270 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CCR_DIV_0_TRP_Pos 4 |

SCB CCR: DIV_0_TRP Position

Definition at line 269 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CCR_NONBASETHRDENA_Msk (1ul << SCB_CCR_NONBASETHRDENA_Pos) |

SCB CCR: NONBASETHRDENA Mask

Definition at line 279 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CCR_NONBASETHRDENA_Pos 0 |

SCB CCR: NONBASETHRDENA Position

Definition at line 278 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CCR_STKALIGN_Msk (1ul << SCB_CCR_STKALIGN_Pos) |

SCB CCR: STKALIGN Mask

Definition at line 264 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CCR_STKALIGN_Pos 9 |

SCB CCR: STKALIGN Position

Definition at line 263 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CCR_UNALIGN_TRP_Msk (1ul << SCB_CCR_UNALIGN_TRP_Pos) |

SCB CCR: UNALIGN_TRP Mask

Definition at line 273 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CCR_UNALIGN_TRP_Pos 3 |

SCB CCR: UNALIGN_TRP Position

Definition at line 272 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CCR_USERSETMPEND_Msk (1ul << SCB_CCR_USERSETMPEND_Pos) |

SCB CCR: USERSETMPEND Mask

Definition at line 276 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CCR_USERSETMPEND_Pos 1 |

SCB CCR: USERSETMPEND Position

Definition at line 275 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CFSR_BUSFAULTSR_Msk (0xFFul << SCB_CFSR_BUSFAULTSR_Pos) |

SCB CFSR: Bus Fault Status Register Mask

Definition at line 330 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CFSR_BUSFAULTSR_Pos 8 |

SCB CFSR: Bus Fault Status Register Position

Definition at line 329 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CFSR_MEMFAULTSR_Msk (0xFFul << SCB_CFSR_MEMFAULTSR_Pos) |

SCB CFSR: Memory Manage Fault Status Register Mask

Definition at line 333 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CFSR_MEMFAULTSR_Pos 0 |

SCB CFSR: Memory Manage Fault Status Register Position

Definition at line 332 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CFSR_USGFAULTSR_Msk (0xFFFFul << SCB_CFSR_USGFAULTSR_Pos) |

SCB CFSR: Usage Fault Status Register Mask

Definition at line 327 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CFSR_USGFAULTSR_Pos 16 |

SCB CFSR: Usage Fault Status Register Position

Definition at line 326 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CPUID_IMPLEMENTER_Msk (0xFFul << SCB_CPUID_IMPLEMENTER_Pos) |

SCB CPUID: IMPLEMENTER Mask

Definition at line 180 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CPUID_IMPLEMENTER_Pos 24 |

SCB CPUID: IMPLEMENTER Position

Definition at line 179 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CPUID_PARTNO_Msk (0xFFFul << SCB_CPUID_PARTNO_Pos) |

SCB CPUID: PARTNO Mask

Definition at line 186 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CPUID_PARTNO_Pos 4 |

SCB CPUID: PARTNO Position

Definition at line 185 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CPUID_REVISION_Msk (0xFul << SCB_CPUID_REVISION_Pos) |

SCB CPUID: REVISION Mask

Definition at line 189 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CPUID_REVISION_Pos 0 |

SCB CPUID: REVISION Position

Definition at line 188 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CPUID_VARIANT_Msk (0xFul << SCB_CPUID_VARIANT_Pos) |

SCB CPUID: VARIANT Mask

Definition at line 183 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_CPUID_VARIANT_Pos 20 |

SCB CPUID: VARIANT Position

Definition at line 182 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_DFSR_BKPT_Msk (1ul << SCB_DFSR_BKPT_Pos) |

SCB DFSR: BKPT Mask

Definition at line 356 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_DFSR_BKPT_Pos 1 |

SCB DFSR: BKPT Position

Definition at line 355 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_DFSR_DWTTRAP_Msk (1ul << SCB_DFSR_DWTTRAP_Pos) |

SCB DFSR: DWTTRAP Mask

Definition at line 353 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_DFSR_DWTTRAP_Pos 2 |

SCB DFSR: DWTTRAP Position

Definition at line 352 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_DFSR_EXTERNAL_Msk (1ul << SCB_DFSR_EXTERNAL_Pos) |

SCB DFSR: EXTERNAL Mask

Definition at line 347 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_DFSR_EXTERNAL_Pos 4 |

SCB DFSR: EXTERNAL Position

Definition at line 346 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_DFSR_HALTED_Msk (1ul << SCB_DFSR_HALTED_Pos) |

SCB DFSR: HALTED Mask

Definition at line 359 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_DFSR_HALTED_Pos 0 |

SCB DFSR: HALTED Position

Definition at line 358 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_DFSR_VCATCH_Msk (1ul << SCB_DFSR_VCATCH_Pos) |

SCB DFSR: VCATCH Mask

Definition at line 350 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_DFSR_VCATCH_Pos 3 |

SCB DFSR: VCATCH Position

Definition at line 349 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_HFSR_DEBUGEVT_Msk (1ul << SCB_HFSR_DEBUGEVT_Pos) |

SCB HFSR: DEBUGEVT Mask

Definition at line 337 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_HFSR_DEBUGEVT_Pos 31 |

SCB HFSR: DEBUGEVT Position

Definition at line 336 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_HFSR_FORCED_Msk (1ul << SCB_HFSR_FORCED_Pos) |

SCB HFSR: FORCED Mask

Definition at line 340 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_HFSR_FORCED_Pos 30 |

SCB HFSR: FORCED Position

Definition at line 339 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_HFSR_VECTTBL_Msk (1ul << SCB_HFSR_VECTTBL_Pos) |

SCB HFSR: VECTTBL Mask

Definition at line 343 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_HFSR_VECTTBL_Pos 1 |

SCB HFSR: VECTTBL Position

Definition at line 342 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_ISRPENDING_Msk (1ul << SCB_ICSR_ISRPENDING_Pos) |

SCB ICSR: ISRPENDING Mask

Definition at line 211 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_ISRPENDING_Pos 22 |

SCB ICSR: ISRPENDING Position

Definition at line 210 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_ISRPREEMPT_Msk (1ul << SCB_ICSR_ISRPREEMPT_Pos) |

SCB ICSR: ISRPREEMPT Mask

Definition at line 208 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_ISRPREEMPT_Pos 23 |

SCB ICSR: ISRPREEMPT Position

Definition at line 207 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_NMIPENDSET_Msk (1ul << SCB_ICSR_NMIPENDSET_Pos) |

SCB ICSR: NMIPENDSET Mask

Definition at line 193 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_NMIPENDSET_Pos 31 |

SCB ICSR: NMIPENDSET Position

Definition at line 192 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_PENDSTCLR_Msk (1ul << SCB_ICSR_PENDSTCLR_Pos) |

SCB ICSR: PENDSTCLR Mask

Definition at line 205 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_PENDSTCLR_Pos 25 |

SCB ICSR: PENDSTCLR Position

Definition at line 204 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_PENDSTSET_Msk (1ul << SCB_ICSR_PENDSTSET_Pos) |

SCB ICSR: PENDSTSET Mask

Definition at line 202 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_PENDSTSET_Pos 26 |

SCB ICSR: PENDSTSET Position

Definition at line 201 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_PENDSVCLR_Msk (1ul << SCB_ICSR_PENDSVCLR_Pos) |

SCB ICSR: PENDSVCLR Mask

Definition at line 199 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_PENDSVCLR_Pos 27 |

SCB ICSR: PENDSVCLR Position

Definition at line 198 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_PENDSVSET_Msk (1ul << SCB_ICSR_PENDSVSET_Pos) |

SCB ICSR: PENDSVSET Mask

Definition at line 196 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_PENDSVSET_Pos 28 |

SCB ICSR: PENDSVSET Position

Definition at line 195 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_RETTOBASE_Msk (1ul << SCB_ICSR_RETTOBASE_Pos) |

SCB ICSR: RETTOBASE Mask

Definition at line 217 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_RETTOBASE_Pos 11 |

SCB ICSR: RETTOBASE Position

Definition at line 216 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_VECTACTIVE_Msk (0x1FFul << SCB_ICSR_VECTACTIVE_Pos) |

SCB ICSR: VECTACTIVE Mask

Definition at line 220 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_VECTACTIVE_Pos 0 |

SCB ICSR: VECTACTIVE Position

Definition at line 219 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_VECTPENDING_Msk (0x1FFul << SCB_ICSR_VECTPENDING_Pos) |

SCB ICSR: VECTPENDING Mask

Definition at line 214 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_ICSR_VECTPENDING_Pos 12 |

SCB ICSR: VECTPENDING Position

Definition at line 213 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SCR_SEVONPEND_Msk (1ul << SCB_SCR_SEVONPEND_Pos) |

SCB SCR: SEVONPEND Mask

Definition at line 254 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SCR_SEVONPEND_Pos 4 |

SCB SCR: SEVONPEND Position

Definition at line 253 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SCR_SLEEPDEEP_Msk (1ul << SCB_SCR_SLEEPDEEP_Pos) |

SCB SCR: SLEEPDEEP Mask

Definition at line 257 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SCR_SLEEPDEEP_Pos 2 |

SCB SCR: SLEEPDEEP Position

Definition at line 256 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SCR_SLEEPONEXIT_Msk (1ul << SCB_SCR_SLEEPONEXIT_Pos) |

SCB SCR: SLEEPONEXIT Mask

Definition at line 260 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SCR_SLEEPONEXIT_Pos 1 |

SCB SCR: SLEEPONEXIT Position

Definition at line 259 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_BUSFAULTACT_Msk (1ul << SCB_SHCSR_BUSFAULTACT_Pos) |

SCB SHCSR: BUSFAULTACT Mask

Definition at line 320 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_BUSFAULTACT_Pos 1 |

SCB SHCSR: BUSFAULTACT Position

Definition at line 319 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_BUSFAULTENA_Msk (1ul << SCB_SHCSR_BUSFAULTENA_Pos) |

SCB SHCSR: BUSFAULTENA Mask

Definition at line 287 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_BUSFAULTENA_Pos 17 |

SCB SHCSR: BUSFAULTENA Position

Definition at line 286 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_BUSFAULTPENDED_Msk (1ul << SCB_SHCSR_BUSFAULTPENDED_Pos) |

SCB SHCSR: BUSFAULTPENDED Mask

Definition at line 296 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_BUSFAULTPENDED_Pos 14 |

SCB SHCSR: BUSFAULTPENDED Position

Definition at line 295 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_MEMFAULTACT_Msk (1ul << SCB_SHCSR_MEMFAULTACT_Pos) |

SCB SHCSR: MEMFAULTACT Mask

Definition at line 323 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_MEMFAULTACT_Pos 0 |

SCB SHCSR: MEMFAULTACT Position

Definition at line 322 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_MEMFAULTENA_Msk (1ul << SCB_SHCSR_MEMFAULTENA_Pos) |

SCB SHCSR: MEMFAULTENA Mask

Definition at line 290 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_MEMFAULTENA_Pos 16 |

SCB SHCSR: MEMFAULTENA Position

Definition at line 289 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_MEMFAULTPENDED_Msk (1ul << SCB_SHCSR_MEMFAULTPENDED_Pos) |

SCB SHCSR: MEMFAULTPENDED Mask

Definition at line 299 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_MEMFAULTPENDED_Pos 13 |

SCB SHCSR: MEMFAULTPENDED Position

Definition at line 298 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_MONITORACT_Msk (1ul << SCB_SHCSR_MONITORACT_Pos) |

SCB SHCSR: MONITORACT Mask

Definition at line 311 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_MONITORACT_Pos 8 |

SCB SHCSR: MONITORACT Position

Definition at line 310 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_PENDSVACT_Msk (1ul << SCB_SHCSR_PENDSVACT_Pos) |

SCB SHCSR: PENDSVACT Mask

Definition at line 308 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_PENDSVACT_Pos 10 |

SCB SHCSR: PENDSVACT Position

Definition at line 307 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_SVCALLACT_Msk (1ul << SCB_SHCSR_SVCALLACT_Pos) |

SCB SHCSR: SVCALLACT Mask

Definition at line 314 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_SVCALLACT_Pos 7 |

SCB SHCSR: SVCALLACT Position

Definition at line 313 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_SVCALLPENDED_Msk (1ul << SCB_SHCSR_SVCALLPENDED_Pos) |

SCB SHCSR: SVCALLPENDED Mask

Definition at line 293 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_SVCALLPENDED_Pos 15 |

SCB SHCSR: SVCALLPENDED Position

Definition at line 292 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_SYSTICKACT_Msk (1ul << SCB_SHCSR_SYSTICKACT_Pos) |

SCB SHCSR: SYSTICKACT Mask

Definition at line 305 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_SYSTICKACT_Pos 11 |

SCB SHCSR: SYSTICKACT Position

Definition at line 304 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_USGFAULTACT_Msk (1ul << SCB_SHCSR_USGFAULTACT_Pos) |

SCB SHCSR: USGFAULTACT Mask

Definition at line 317 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_USGFAULTACT_Pos 3 |

SCB SHCSR: USGFAULTACT Position

Definition at line 316 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_USGFAULTENA_Msk (1ul << SCB_SHCSR_USGFAULTENA_Pos) |

SCB SHCSR: USGFAULTENA Mask

Definition at line 284 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_USGFAULTENA_Pos 18 |

SCB SHCSR: USGFAULTENA Position

Definition at line 283 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_USGFAULTPENDED_Msk (1ul << SCB_SHCSR_USGFAULTPENDED_Pos) |

SCB SHCSR: USGFAULTPENDED Mask

Definition at line 302 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_SHCSR_USGFAULTPENDED_Pos 12 |

SCB SHCSR: USGFAULTPENDED Position

Definition at line 301 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_VTOR_TBLBASE_Msk (0x1FFul << SCB_VTOR_TBLBASE_Pos) |

SCB VTOR: TBLBASE Mask

Definition at line 224 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_VTOR_TBLBASE_Pos 29 |

SCB VTOR: TBLBASE Position

Definition at line 223 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_VTOR_TBLOFF_Msk (0x3FFFFFul << SCB_VTOR_TBLOFF_Pos) |

SCB VTOR: TBLOFF Mask

Definition at line 227 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.

| #define SCB_VTOR_TBLOFF_Pos 7 |

SCB VTOR: TBLOFF Position

Definition at line 226 of file breezy/breezystm32/lib/CMSIS/CM3/CoreSupport/core_cm3.h.