Go to the source code of this file.

Macros | |

| #define | REG_GMAC_AE (*(__I uint32_t*)0x4005019CU) |

| (GMAC) Alignment Errors Register More... | |

| #define | REG_GMAC_BCFR (*(__I uint32_t*)0x4005015CU) |

| (GMAC) Broadcast Frames Received Register More... | |

| #define | REG_GMAC_BCFT (*(__I uint32_t*)0x4005010CU) |

| (GMAC) Broadcast Frames Transmitted Register More... | |

| #define | REG_GMAC_BFR64 (*(__I uint32_t*)0x40050168U) |

| (GMAC) 64 Byte Frames Received Register More... | |

| #define | REG_GMAC_BFT64 (*(__I uint32_t*)0x40050118U) |

| (GMAC) 64 Byte Frames Transmitted Register More... | |

| #define | REG_GMAC_CBSCR (*(__IO uint32_t*)0x400504BCU) |

| (GMAC) Credit-Based Shaping Control Register More... | |

| #define | REG_GMAC_CBSISQA (*(__IO uint32_t*)0x400504C0U) |

| (GMAC) Credit-Based Shaping IdleSlope Register for Queue A More... | |

| #define | REG_GMAC_CBSISQB (*(__IO uint32_t*)0x400504C4U) |

| (GMAC) Credit-Based Shaping IdleSlope Register for Queue B More... | |

| #define | REG_GMAC_CSE (*(__I uint32_t*)0x4005014CU) |

| (GMAC) Carrier Sense Errors Register More... | |

| #define | REG_GMAC_DCFGR (*(__IO uint32_t*)0x40050010U) |

| (GMAC) DMA Configuration Register More... | |

| #define | REG_GMAC_DTF (*(__I uint32_t*)0x40050148U) |

| (GMAC) Deferred Transmission Frames Register More... | |

| #define | REG_GMAC_EC (*(__I uint32_t*)0x40050140U) |

| (GMAC) Excessive Collisions Register More... | |

| #define | REG_GMAC_EFRN (*(__I uint32_t*)0x400501ECU) |

| (GMAC) PTP Event Frame Received Nanoseconds Register More... | |

| #define | REG_GMAC_EFRSH (*(__I uint32_t*)0x400500ECU) |

| (GMAC) PTP Event Frame Received Seconds High Register More... | |

| #define | REG_GMAC_EFRSL (*(__I uint32_t*)0x400501E8U) |

| (GMAC) PTP Event Frame Received Seconds Low Register More... | |

| #define | REG_GMAC_EFTN (*(__I uint32_t*)0x400501E4U) |

| (GMAC) PTP Event Frame Transmitted Nanoseconds Register More... | |

| #define | REG_GMAC_EFTSH (*(__I uint32_t*)0x400500E8U) |

| (GMAC) PTP Event Frame Transmitted Seconds High Register More... | |

| #define | REG_GMAC_EFTSL (*(__I uint32_t*)0x400501E0U) |

| (GMAC) PTP Event Frame Transmitted Seconds Low Register More... | |

| #define | REG_GMAC_FCSE (*(__I uint32_t*)0x40050190U) |

| (GMAC) Frame Check Sequence Errors Register More... | |

| #define | REG_GMAC_FR (*(__I uint32_t*)0x40050158U) |

| (GMAC) Frames Received Register More... | |

| #define | REG_GMAC_FT (*(__I uint32_t*)0x40050108U) |

| (GMAC) Frames Transmitted Register More... | |

| #define | REG_GMAC_GTBFT1518 (*(__I uint32_t*)0x40050130U) |

| (GMAC) Greater Than 1518 Byte Frames Transmitted Register More... | |

| #define | REG_GMAC_HRB (*(__IO uint32_t*)0x40050080U) |

| (GMAC) Hash Register Bottom More... | |

| #define | REG_GMAC_HRT (*(__IO uint32_t*)0x40050084U) |

| (GMAC) Hash Register Top More... | |

| #define | REG_GMAC_IDR (*(__O uint32_t*)0x4005002CU) |

| (GMAC) Interrupt Disable Register More... | |

| #define | REG_GMAC_IDRPQ (*(__O uint32_t*)0x4005061CU) |

| (GMAC) Interrupt Disable Register Priority Queue (index = 1) More... | |

| #define | REG_GMAC_IER (*(__O uint32_t*)0x40050028U) |

| (GMAC) Interrupt Enable Register More... | |

| #define | REG_GMAC_IERPQ (*(__O uint32_t*)0x400505FCU) |

| (GMAC) Interrupt Enable Register Priority Queue (index = 1) More... | |

| #define | REG_GMAC_IHCE (*(__I uint32_t*)0x400501A8U) |

| (GMAC) IP Header Checksum Errors Register More... | |

| #define | REG_GMAC_IMR (*(__IO uint32_t*)0x40050030U) |

| (GMAC) Interrupt Mask Register More... | |

| #define | REG_GMAC_IMRPQ (*(__IO uint32_t*)0x4005063CU) |

| (GMAC) Interrupt Mask Register Priority Queue (index = 1) More... | |

| #define | REG_GMAC_IPGS (*(__IO uint32_t*)0x400500BCU) |

| (GMAC) IPG Stretch Register More... | |

| #define | REG_GMAC_ISR (*(__I uint32_t*)0x40050024U) |

| (GMAC) Interrupt Status Register More... | |

| #define | REG_GMAC_ISRPQ (*(__I uint32_t*)0x400503FCU) |

| (GMAC) Interrupt Status Register Priority Queue (index = 1) 0 More... | |

| #define | REG_GMAC_JR (*(__I uint32_t*)0x4005018CU) |

| (GMAC) Jabbers Received Register More... | |

| #define | REG_GMAC_LC (*(__I uint32_t*)0x40050144U) |

| (GMAC) Late Collisions Register More... | |

| #define | REG_GMAC_LFFE (*(__I uint32_t*)0x40050194U) |

| (GMAC) Length Field Frame Errors Register More... | |

| #define | REG_GMAC_MAN (*(__IO uint32_t*)0x40050034U) |

| (GMAC) PHY Maintenance Register More... | |

| #define | REG_GMAC_MCF (*(__I uint32_t*)0x4005013CU) |

| (GMAC) Multiple Collision Frames Register More... | |

| #define | REG_GMAC_MFR (*(__I uint32_t*)0x40050160U) |

| (GMAC) Multicast Frames Received Register More... | |

| #define | REG_GMAC_MFT (*(__I uint32_t*)0x40050110U) |

| (GMAC) Multicast Frames Transmitted Register More... | |

| #define | REG_GMAC_MID (*(__I uint32_t*)0x400500FCU) |

| (GMAC) Module ID Register More... | |

| #define | REG_GMAC_NCFGR (*(__IO uint32_t*)0x40050004U) |

| (GMAC) Network Configuration Register More... | |

| #define | REG_GMAC_NCR (*(__IO uint32_t*)0x40050000U) |

| (GMAC) Network Control Register More... | |

| #define | REG_GMAC_NSC (*(__IO uint32_t*)0x400500DCU) |

| (GMAC) 1588 Timer Nanosecond Comparison Register More... | |

| #define | REG_GMAC_NSR (*(__I uint32_t*)0x40050008U) |

| (GMAC) Network Status Register More... | |

| #define | REG_GMAC_OFR (*(__I uint32_t*)0x40050188U) |

| (GMAC) Oversize Frames Received Register More... | |

| #define | REG_GMAC_ORHI (*(__I uint32_t*)0x40050154U) |

| (GMAC) Octets Received High Received Register More... | |

| #define | REG_GMAC_ORLO (*(__I uint32_t*)0x40050150U) |

| (GMAC) Octets Received Low Received Register More... | |

| #define | REG_GMAC_OTHI (*(__I uint32_t*)0x40050104U) |

| (GMAC) Octets Transmitted High Register More... | |

| #define | REG_GMAC_OTLO (*(__I uint32_t*)0x40050100U) |

| (GMAC) Octets Transmitted Low Register More... | |

| #define | REG_GMAC_PEFRN (*(__I uint32_t*)0x400501FCU) |

| (GMAC) PTP Peer Event Frame Received Nanoseconds Register More... | |

| #define | REG_GMAC_PEFRSH (*(__I uint32_t*)0x400500F4U) |

| (GMAC) PTP Peer Event Frame Received Seconds High Register More... | |

| #define | REG_GMAC_PEFRSL (*(__I uint32_t*)0x400501F8U) |

| (GMAC) PTP Peer Event Frame Received Seconds Low Register More... | |

| #define | REG_GMAC_PEFTN (*(__I uint32_t*)0x400501F4U) |

| (GMAC) PTP Peer Event Frame Transmitted Nanoseconds Register More... | |

| #define | REG_GMAC_PEFTSH (*(__I uint32_t*)0x400500F0U) |

| (GMAC) PTP Peer Event Frame Transmitted Seconds High Register More... | |

| #define | REG_GMAC_PEFTSL (*(__I uint32_t*)0x400501F0U) |

| (GMAC) PTP Peer Event Frame Transmitted Seconds Low Register More... | |

| #define | REG_GMAC_PFR (*(__I uint32_t*)0x40050164U) |

| (GMAC) Pause Frames Received Register More... | |

| #define | REG_GMAC_PFT (*(__I uint32_t*)0x40050114U) |

| (GMAC) Pause Frames Transmitted Register More... | |

| #define | REG_GMAC_RBQB (*(__IO uint32_t*)0x40050018U) |

| (GMAC) Receive Buffer Queue Base Address Register More... | |

| #define | REG_GMAC_RBQBAPQ (*(__IO uint32_t*)0x4005047CU) |

| (GMAC) Receive Buffer Queue Base Address Register Priority Queue (index = 1) More... | |

| #define | REG_GMAC_RBSRPQ (*(__IO uint32_t*)0x4005049CU) |

| (GMAC) Receive Buffer Size Register Priority Queue (index = 1) More... | |

| #define | REG_GMAC_RJFML (*(__IO uint32_t*)0x40050048U) |

| (GMAC) RX Jumbo Frame Max Length Register More... | |

| #define | REG_GMAC_ROE (*(__I uint32_t*)0x400501A4U) |

| (GMAC) Receive Overrun Register More... | |

| #define | REG_GMAC_RPQ (*(__I uint32_t*)0x40050038U) |

| (GMAC) Received Pause Quantum Register More... | |

| #define | REG_GMAC_RPSF (*(__IO uint32_t*)0x40050044U) |

| (GMAC) RX Partial Store and Forward Register More... | |

| #define | REG_GMAC_RRE (*(__I uint32_t*)0x400501A0U) |

| (GMAC) Receive Resource Errors Register More... | |

| #define | REG_GMAC_RSE (*(__I uint32_t*)0x40050198U) |

| (GMAC) Receive Symbol Errors Register More... | |

| #define | REG_GMAC_RSR (*(__IO uint32_t*)0x40050020U) |

| (GMAC) Receive Status Register More... | |

| #define | REG_GMAC_RXLPI (*(__I uint32_t*)0x40050270U) |

| (GMAC) Received LPI Transitions More... | |

| #define | REG_GMAC_RXLPITIME (*(__I uint32_t*)0x40050274U) |

| (GMAC) Received LPI Time More... | |

| #define | REG_GMAC_SAB1 (*(__IO uint32_t*)0x40050088U) |

| (GMAC) Specific Address 1 Bottom Register More... | |

| #define | REG_GMAC_SAB2 (*(__IO uint32_t*)0x40050090U) |

| (GMAC) Specific Address 2 Bottom Register More... | |

| #define | REG_GMAC_SAB3 (*(__IO uint32_t*)0x40050098U) |

| (GMAC) Specific Address 3 Bottom Register More... | |

| #define | REG_GMAC_SAB4 (*(__IO uint32_t*)0x400500A0U) |

| (GMAC) Specific Address 4 Bottom Register More... | |

| #define | REG_GMAC_SAMB1 (*(__IO uint32_t*)0x400500C8U) |

| (GMAC) Specific Address 1 Mask Bottom Register More... | |

| #define | REG_GMAC_SAMT1 (*(__IO uint32_t*)0x400500CCU) |

| (GMAC) Specific Address 1 Mask Top Register More... | |

| #define | REG_GMAC_SAT1 (*(__IO uint32_t*)0x4005008CU) |

| (GMAC) Specific Address 1 Top Register More... | |

| #define | REG_GMAC_SAT2 (*(__IO uint32_t*)0x40050094U) |

| (GMAC) Specific Address 2 Top Register More... | |

| #define | REG_GMAC_SAT3 (*(__IO uint32_t*)0x4005009CU) |

| (GMAC) Specific Address 3 Top Register More... | |

| #define | REG_GMAC_SAT4 (*(__IO uint32_t*)0x400500A4U) |

| (GMAC) Specific Address 4 Top Register More... | |

| #define | REG_GMAC_SCF (*(__I uint32_t*)0x40050138U) |

| (GMAC) Single Collision Frames Register More... | |

| #define | REG_GMAC_SCH (*(__IO uint32_t*)0x400500E4U) |

| (GMAC) 1588 Timer Second Comparison High Register More... | |

| #define | REG_GMAC_SCL (*(__IO uint32_t*)0x400500E0U) |

| (GMAC) 1588 Timer Second Comparison Low Register More... | |

| #define | REG_GMAC_ST1RPQ (*(__IO uint32_t*)0x40050500U) |

| (GMAC) Screening Type 1 Register Priority Queue (index = 0) More... | |

| #define | REG_GMAC_ST2CW00 (*(__IO uint32_t*)0x40050700U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 0) More... | |

| #define | REG_GMAC_ST2CW01 (*(__IO uint32_t*)0x40050708U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 1) More... | |

| #define | REG_GMAC_ST2CW010 (*(__IO uint32_t*)0x40050750U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 10) More... | |

| #define | REG_GMAC_ST2CW011 (*(__IO uint32_t*)0x40050758U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 11) More... | |

| #define | REG_GMAC_ST2CW012 (*(__IO uint32_t*)0x40050760U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 12) More... | |

| #define | REG_GMAC_ST2CW013 (*(__IO uint32_t*)0x40050768U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 13) More... | |

| #define | REG_GMAC_ST2CW014 (*(__IO uint32_t*)0x40050770U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 14) More... | |

| #define | REG_GMAC_ST2CW015 (*(__IO uint32_t*)0x40050778U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 15) More... | |

| #define | REG_GMAC_ST2CW016 (*(__IO uint32_t*)0x40050780U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 16) More... | |

| #define | REG_GMAC_ST2CW017 (*(__IO uint32_t*)0x40050788U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 17) More... | |

| #define | REG_GMAC_ST2CW018 (*(__IO uint32_t*)0x40050790U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 18) More... | |

| #define | REG_GMAC_ST2CW019 (*(__IO uint32_t*)0x40050798U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 19) More... | |

| #define | REG_GMAC_ST2CW02 (*(__IO uint32_t*)0x40050710U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 2) More... | |

| #define | REG_GMAC_ST2CW020 (*(__IO uint32_t*)0x400507A0U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 20) More... | |

| #define | REG_GMAC_ST2CW021 (*(__IO uint32_t*)0x400507A8U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 21) More... | |

| #define | REG_GMAC_ST2CW022 (*(__IO uint32_t*)0x400507B0U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 22) More... | |

| #define | REG_GMAC_ST2CW023 (*(__IO uint32_t*)0x400507B8U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 23) More... | |

| #define | REG_GMAC_ST2CW03 (*(__IO uint32_t*)0x40050718U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 3) More... | |

| #define | REG_GMAC_ST2CW04 (*(__IO uint32_t*)0x40050720U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 4) More... | |

| #define | REG_GMAC_ST2CW05 (*(__IO uint32_t*)0x40050728U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 5) More... | |

| #define | REG_GMAC_ST2CW06 (*(__IO uint32_t*)0x40050730U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 6) More... | |

| #define | REG_GMAC_ST2CW07 (*(__IO uint32_t*)0x40050738U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 7) More... | |

| #define | REG_GMAC_ST2CW08 (*(__IO uint32_t*)0x40050740U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 8) More... | |

| #define | REG_GMAC_ST2CW09 (*(__IO uint32_t*)0x40050748U) |

| (GMAC) Screening Type 2 Compare Word 0 Register (index = 9) More... | |

| #define | REG_GMAC_ST2CW10 (*(__IO uint32_t*)0x40050704U) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 0) More... | |

| #define | REG_GMAC_ST2CW11 (*(__IO uint32_t*)0x4005070CU) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 1) More... | |

| #define | REG_GMAC_ST2CW110 (*(__IO uint32_t*)0x40050754U) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 10) More... | |

| #define | REG_GMAC_ST2CW111 (*(__IO uint32_t*)0x4005075CU) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 11) More... | |

| #define | REG_GMAC_ST2CW112 (*(__IO uint32_t*)0x40050764U) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 12) More... | |

| #define | REG_GMAC_ST2CW113 (*(__IO uint32_t*)0x4005076CU) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 13) More... | |

| #define | REG_GMAC_ST2CW114 (*(__IO uint32_t*)0x40050774U) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 14) More... | |

| #define | REG_GMAC_ST2CW115 (*(__IO uint32_t*)0x4005077CU) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 15) More... | |

| #define | REG_GMAC_ST2CW116 (*(__IO uint32_t*)0x40050784U) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 16) More... | |

| #define | REG_GMAC_ST2CW117 (*(__IO uint32_t*)0x4005078CU) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 17) More... | |

| #define | REG_GMAC_ST2CW118 (*(__IO uint32_t*)0x40050794U) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 18) More... | |

| #define | REG_GMAC_ST2CW119 (*(__IO uint32_t*)0x4005079CU) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 19) More... | |

| #define | REG_GMAC_ST2CW12 (*(__IO uint32_t*)0x40050714U) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 2) More... | |

| #define | REG_GMAC_ST2CW120 (*(__IO uint32_t*)0x400507A4U) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 20) More... | |

| #define | REG_GMAC_ST2CW121 (*(__IO uint32_t*)0x400507ACU) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 21) More... | |

| #define | REG_GMAC_ST2CW122 (*(__IO uint32_t*)0x400507B4U) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 22) More... | |

| #define | REG_GMAC_ST2CW123 (*(__IO uint32_t*)0x400507BCU) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 23) More... | |

| #define | REG_GMAC_ST2CW13 (*(__IO uint32_t*)0x4005071CU) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 3) More... | |

| #define | REG_GMAC_ST2CW14 (*(__IO uint32_t*)0x40050724U) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 4) More... | |

| #define | REG_GMAC_ST2CW15 (*(__IO uint32_t*)0x4005072CU) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 5) More... | |

| #define | REG_GMAC_ST2CW16 (*(__IO uint32_t*)0x40050734U) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 6) More... | |

| #define | REG_GMAC_ST2CW17 (*(__IO uint32_t*)0x4005073CU) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 7) More... | |

| #define | REG_GMAC_ST2CW18 (*(__IO uint32_t*)0x40050744U) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 8) More... | |

| #define | REG_GMAC_ST2CW19 (*(__IO uint32_t*)0x4005074CU) |

| (GMAC) Screening Type 2 Compare Word 1 Register (index = 9) More... | |

| #define | REG_GMAC_ST2ER (*(__IO uint32_t*)0x400506E0U) |

| (GMAC) Screening Type 2 Ethertype Register (index = 0) More... | |

| #define | REG_GMAC_ST2RPQ (*(__IO uint32_t*)0x40050540U) |

| (GMAC) Screening Type 2 Register Priority Queue (index = 0) More... | |

| #define | REG_GMAC_SVLAN (*(__IO uint32_t*)0x400500C0U) |

| (GMAC) Stacked VLAN Register More... | |

| #define | REG_GMAC_TA (*(__O uint32_t*)0x400501D8U) |

| (GMAC) 1588 Timer Adjust Register More... | |

| #define | REG_GMAC_TBFR1023 (*(__I uint32_t*)0x40050178U) |

| (GMAC) 512 to 1023 Byte Frames Received Register More... | |

| #define | REG_GMAC_TBFR127 (*(__I uint32_t*)0x4005016CU) |

| (GMAC) 65 to 127 Byte Frames Received Register More... | |

| #define | REG_GMAC_TBFR1518 (*(__I uint32_t*)0x4005017CU) |

| (GMAC) 1024 to 1518 Byte Frames Received Register More... | |

| #define | REG_GMAC_TBFR255 (*(__I uint32_t*)0x40050170U) |

| (GMAC) 128 to 255 Byte Frames Received Register More... | |

| #define | REG_GMAC_TBFR511 (*(__I uint32_t*)0x40050174U) |

| (GMAC) 256 to 511 Byte Frames Received Register More... | |

| #define | REG_GMAC_TBFT1023 (*(__I uint32_t*)0x40050128U) |

| (GMAC) 512 to 1023 Byte Frames Transmitted Register More... | |

| #define | REG_GMAC_TBFT127 (*(__I uint32_t*)0x4005011CU) |

| (GMAC) 65 to 127 Byte Frames Transmitted Register More... | |

| #define | REG_GMAC_TBFT1518 (*(__I uint32_t*)0x4005012CU) |

| (GMAC) 1024 to 1518 Byte Frames Transmitted Register More... | |

| #define | REG_GMAC_TBFT255 (*(__I uint32_t*)0x40050120U) |

| (GMAC) 128 to 255 Byte Frames Transmitted Register More... | |

| #define | REG_GMAC_TBFT511 (*(__I uint32_t*)0x40050124U) |

| (GMAC) 256 to 511 Byte Frames Transmitted Register More... | |

| #define | REG_GMAC_TBQB (*(__IO uint32_t*)0x4005001CU) |

| (GMAC) Transmit Buffer Queue Base Address Register More... | |

| #define | REG_GMAC_TBQBAPQ (*(__IO uint32_t*)0x4005043CU) |

| (GMAC) Transmit Buffer Queue Base Address Register Priority Queue (index = 1) More... | |

| #define | REG_GMAC_TCE (*(__I uint32_t*)0x400501ACU) |

| (GMAC) TCP Checksum Errors Register More... | |

| #define | REG_GMAC_TI (*(__IO uint32_t*)0x400501DCU) |

| (GMAC) 1588 Timer Increment Register More... | |

| #define | REG_GMAC_TIDM1 (*(__IO uint32_t*)0x400500A8U) |

| (GMAC) Type ID Match 1 Register More... | |

| #define | REG_GMAC_TIDM2 (*(__IO uint32_t*)0x400500ACU) |

| (GMAC) Type ID Match 2 Register More... | |

| #define | REG_GMAC_TIDM3 (*(__IO uint32_t*)0x400500B0U) |

| (GMAC) Type ID Match 3 Register More... | |

| #define | REG_GMAC_TIDM4 (*(__IO uint32_t*)0x400500B4U) |

| (GMAC) Type ID Match 4 Register More... | |

| #define | REG_GMAC_TISUBN (*(__IO uint32_t*)0x400501BCU) |

| (GMAC) 1588 Timer Increment Sub-nanoseconds Register More... | |

| #define | REG_GMAC_TMXBFR (*(__I uint32_t*)0x40050180U) |

| (GMAC) 1519 to Maximum Byte Frames Received Register More... | |

| #define | REG_GMAC_TN (*(__IO uint32_t*)0x400501D4U) |

| (GMAC) 1588 Timer Nanoseconds Register More... | |

| #define | REG_GMAC_TPFCP (*(__IO uint32_t*)0x400500C4U) |

| (GMAC) Transmit PFC Pause Register More... | |

| #define | REG_GMAC_TPQ (*(__IO uint32_t*)0x4005003CU) |

| (GMAC) Transmit Pause Quantum Register More... | |

| #define | REG_GMAC_TPSF (*(__IO uint32_t*)0x40050040U) |

| (GMAC) TX Partial Store and Forward Register More... | |

| #define | REG_GMAC_TSH (*(__IO uint32_t*)0x400501C0U) |

| (GMAC) 1588 Timer Seconds High Register More... | |

| #define | REG_GMAC_TSL (*(__IO uint32_t*)0x400501D0U) |

| (GMAC) 1588 Timer Seconds Low Register More... | |

| #define | REG_GMAC_TSR (*(__IO uint32_t*)0x40050014U) |

| (GMAC) Transmit Status Register More... | |

| #define | REG_GMAC_TUR (*(__I uint32_t*)0x40050134U) |

| (GMAC) Transmit Underruns Register More... | |

| #define | REG_GMAC_TXLPI (*(__I uint32_t*)0x40050278U) |

| (GMAC) Transmit LPI Transitions More... | |

| #define | REG_GMAC_TXLPITIME (*(__I uint32_t*)0x4005027CU) |

| (GMAC) Transmit LPI Time More... | |

| #define | REG_GMAC_UCE (*(__I uint32_t*)0x400501B0U) |

| (GMAC) UDP Checksum Errors Register More... | |

| #define | REG_GMAC_UFR (*(__I uint32_t*)0x40050184U) |

| (GMAC) Undersize Frames Received Register More... | |

| #define | REG_GMAC_UR (*(__IO uint32_t*)0x4005000CU) |

| (GMAC) User Register More... | |

| #define | REG_GMAC_WOL (*(__IO uint32_t*)0x400500B8U) |

| (GMAC) Wake on LAN Register More... | |

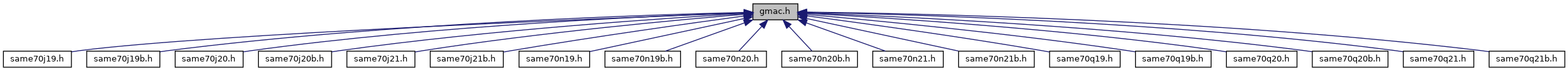

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file instance/gmac.h.

Macro Definition Documentation

◆ REG_GMAC_AE

| #define REG_GMAC_AE (*(__I uint32_t*)0x4005019CU) |

(GMAC) Alignment Errors Register

Definition at line 298 of file instance/gmac.h.

◆ REG_GMAC_BCFR

| #define REG_GMAC_BCFR (*(__I uint32_t*)0x4005015CU) |

(GMAC) Broadcast Frames Received Register

Definition at line 282 of file instance/gmac.h.

◆ REG_GMAC_BCFT

| #define REG_GMAC_BCFT (*(__I uint32_t*)0x4005010CU) |

(GMAC) Broadcast Frames Transmitted Register

Definition at line 262 of file instance/gmac.h.

◆ REG_GMAC_BFR64

| #define REG_GMAC_BFR64 (*(__I uint32_t*)0x40050168U) |

(GMAC) 64 Byte Frames Received Register

Definition at line 285 of file instance/gmac.h.

◆ REG_GMAC_BFT64

| #define REG_GMAC_BFT64 (*(__I uint32_t*)0x40050118U) |

(GMAC) 64 Byte Frames Transmitted Register

Definition at line 265 of file instance/gmac.h.

◆ REG_GMAC_CBSCR

| #define REG_GMAC_CBSCR (*(__IO uint32_t*)0x400504BCU) |

(GMAC) Credit-Based Shaping Control Register

Definition at line 326 of file instance/gmac.h.

◆ REG_GMAC_CBSISQA

| #define REG_GMAC_CBSISQA (*(__IO uint32_t*)0x400504C0U) |

(GMAC) Credit-Based Shaping IdleSlope Register for Queue A

Definition at line 327 of file instance/gmac.h.

◆ REG_GMAC_CBSISQB

| #define REG_GMAC_CBSISQB (*(__IO uint32_t*)0x400504C4U) |

(GMAC) Credit-Based Shaping IdleSlope Register for Queue B

Definition at line 328 of file instance/gmac.h.

◆ REG_GMAC_CSE

| #define REG_GMAC_CSE (*(__I uint32_t*)0x4005014CU) |

(GMAC) Carrier Sense Errors Register

Definition at line 278 of file instance/gmac.h.

◆ REG_GMAC_DCFGR

| #define REG_GMAC_DCFGR (*(__IO uint32_t*)0x40050010U) |

(GMAC) DMA Configuration Register

Definition at line 216 of file instance/gmac.h.

◆ REG_GMAC_DTF

| #define REG_GMAC_DTF (*(__I uint32_t*)0x40050148U) |

(GMAC) Deferred Transmission Frames Register

Definition at line 277 of file instance/gmac.h.

◆ REG_GMAC_EC

| #define REG_GMAC_EC (*(__I uint32_t*)0x40050140U) |

(GMAC) Excessive Collisions Register

Definition at line 275 of file instance/gmac.h.

◆ REG_GMAC_EFRN

| #define REG_GMAC_EFRN (*(__I uint32_t*)0x400501ECU) |

(GMAC) PTP Event Frame Received Nanoseconds Register

Definition at line 313 of file instance/gmac.h.

◆ REG_GMAC_EFRSH

| #define REG_GMAC_EFRSH (*(__I uint32_t*)0x400500ECU) |

(GMAC) PTP Event Frame Received Seconds High Register

Definition at line 255 of file instance/gmac.h.

◆ REG_GMAC_EFRSL

| #define REG_GMAC_EFRSL (*(__I uint32_t*)0x400501E8U) |

(GMAC) PTP Event Frame Received Seconds Low Register

Definition at line 312 of file instance/gmac.h.

◆ REG_GMAC_EFTN

| #define REG_GMAC_EFTN (*(__I uint32_t*)0x400501E4U) |

(GMAC) PTP Event Frame Transmitted Nanoseconds Register

Definition at line 311 of file instance/gmac.h.

◆ REG_GMAC_EFTSH

| #define REG_GMAC_EFTSH (*(__I uint32_t*)0x400500E8U) |

(GMAC) PTP Event Frame Transmitted Seconds High Register

Definition at line 254 of file instance/gmac.h.

◆ REG_GMAC_EFTSL

| #define REG_GMAC_EFTSL (*(__I uint32_t*)0x400501E0U) |

(GMAC) PTP Event Frame Transmitted Seconds Low Register

Definition at line 310 of file instance/gmac.h.

◆ REG_GMAC_FCSE

| #define REG_GMAC_FCSE (*(__I uint32_t*)0x40050190U) |

(GMAC) Frame Check Sequence Errors Register

Definition at line 295 of file instance/gmac.h.

◆ REG_GMAC_FR

| #define REG_GMAC_FR (*(__I uint32_t*)0x40050158U) |

(GMAC) Frames Received Register

Definition at line 281 of file instance/gmac.h.

◆ REG_GMAC_FT

| #define REG_GMAC_FT (*(__I uint32_t*)0x40050108U) |

(GMAC) Frames Transmitted Register

Definition at line 261 of file instance/gmac.h.

◆ REG_GMAC_GTBFT1518

| #define REG_GMAC_GTBFT1518 (*(__I uint32_t*)0x40050130U) |

(GMAC) Greater Than 1518 Byte Frames Transmitted Register

Definition at line 271 of file instance/gmac.h.

◆ REG_GMAC_HRB

| #define REG_GMAC_HRB (*(__IO uint32_t*)0x40050080U) |

(GMAC) Hash Register Bottom

Definition at line 231 of file instance/gmac.h.

◆ REG_GMAC_HRT

| #define REG_GMAC_HRT (*(__IO uint32_t*)0x40050084U) |

(GMAC) Hash Register Top

Definition at line 232 of file instance/gmac.h.

◆ REG_GMAC_IDR

| #define REG_GMAC_IDR (*(__O uint32_t*)0x4005002CU) |

(GMAC) Interrupt Disable Register

Definition at line 223 of file instance/gmac.h.

◆ REG_GMAC_IDRPQ

| #define REG_GMAC_IDRPQ (*(__O uint32_t*)0x4005061CU) |

(GMAC) Interrupt Disable Register Priority Queue (index = 1)

Definition at line 332 of file instance/gmac.h.

◆ REG_GMAC_IER

| #define REG_GMAC_IER (*(__O uint32_t*)0x40050028U) |

(GMAC) Interrupt Enable Register

Definition at line 222 of file instance/gmac.h.

◆ REG_GMAC_IERPQ

| #define REG_GMAC_IERPQ (*(__O uint32_t*)0x400505FCU) |

(GMAC) Interrupt Enable Register Priority Queue (index = 1)

Definition at line 331 of file instance/gmac.h.

◆ REG_GMAC_IHCE

| #define REG_GMAC_IHCE (*(__I uint32_t*)0x400501A8U) |

(GMAC) IP Header Checksum Errors Register

Definition at line 301 of file instance/gmac.h.

◆ REG_GMAC_IMR

| #define REG_GMAC_IMR (*(__IO uint32_t*)0x40050030U) |

(GMAC) Interrupt Mask Register

Definition at line 224 of file instance/gmac.h.

◆ REG_GMAC_IMRPQ

| #define REG_GMAC_IMRPQ (*(__IO uint32_t*)0x4005063CU) |

(GMAC) Interrupt Mask Register Priority Queue (index = 1)

Definition at line 333 of file instance/gmac.h.

◆ REG_GMAC_IPGS

| #define REG_GMAC_IPGS (*(__IO uint32_t*)0x400500BCU) |

(GMAC) IPG Stretch Register

Definition at line 246 of file instance/gmac.h.

◆ REG_GMAC_ISR

| #define REG_GMAC_ISR (*(__I uint32_t*)0x40050024U) |

(GMAC) Interrupt Status Register

Definition at line 221 of file instance/gmac.h.

◆ REG_GMAC_ISRPQ

| #define REG_GMAC_ISRPQ (*(__I uint32_t*)0x400503FCU) |

(GMAC) Interrupt Status Register Priority Queue (index = 1) 0

Definition at line 322 of file instance/gmac.h.

◆ REG_GMAC_JR

| #define REG_GMAC_JR (*(__I uint32_t*)0x4005018CU) |

(GMAC) Jabbers Received Register

Definition at line 294 of file instance/gmac.h.

◆ REG_GMAC_LC

| #define REG_GMAC_LC (*(__I uint32_t*)0x40050144U) |

(GMAC) Late Collisions Register

Definition at line 276 of file instance/gmac.h.

◆ REG_GMAC_LFFE

| #define REG_GMAC_LFFE (*(__I uint32_t*)0x40050194U) |

(GMAC) Length Field Frame Errors Register

Definition at line 296 of file instance/gmac.h.

◆ REG_GMAC_MAN

| #define REG_GMAC_MAN (*(__IO uint32_t*)0x40050034U) |

(GMAC) PHY Maintenance Register

Definition at line 225 of file instance/gmac.h.

◆ REG_GMAC_MCF

| #define REG_GMAC_MCF (*(__I uint32_t*)0x4005013CU) |

(GMAC) Multiple Collision Frames Register

Definition at line 274 of file instance/gmac.h.

◆ REG_GMAC_MFR

| #define REG_GMAC_MFR (*(__I uint32_t*)0x40050160U) |

(GMAC) Multicast Frames Received Register

Definition at line 283 of file instance/gmac.h.

◆ REG_GMAC_MFT

| #define REG_GMAC_MFT (*(__I uint32_t*)0x40050110U) |

(GMAC) Multicast Frames Transmitted Register

Definition at line 263 of file instance/gmac.h.

◆ REG_GMAC_MID

| #define REG_GMAC_MID (*(__I uint32_t*)0x400500FCU) |

(GMAC) Module ID Register

Definition at line 258 of file instance/gmac.h.

◆ REG_GMAC_NCFGR

| #define REG_GMAC_NCFGR (*(__IO uint32_t*)0x40050004U) |

(GMAC) Network Configuration Register

Definition at line 213 of file instance/gmac.h.

◆ REG_GMAC_NCR

| #define REG_GMAC_NCR (*(__IO uint32_t*)0x40050000U) |

(GMAC) Network Control Register

Definition at line 212 of file instance/gmac.h.

◆ REG_GMAC_NSC

| #define REG_GMAC_NSC (*(__IO uint32_t*)0x400500DCU) |

(GMAC) 1588 Timer Nanosecond Comparison Register

Definition at line 251 of file instance/gmac.h.

◆ REG_GMAC_NSR

| #define REG_GMAC_NSR (*(__I uint32_t*)0x40050008U) |

(GMAC) Network Status Register

Definition at line 214 of file instance/gmac.h.

◆ REG_GMAC_OFR

| #define REG_GMAC_OFR (*(__I uint32_t*)0x40050188U) |

(GMAC) Oversize Frames Received Register

Definition at line 293 of file instance/gmac.h.

◆ REG_GMAC_ORHI

| #define REG_GMAC_ORHI (*(__I uint32_t*)0x40050154U) |

(GMAC) Octets Received High Received Register

Definition at line 280 of file instance/gmac.h.

◆ REG_GMAC_ORLO

| #define REG_GMAC_ORLO (*(__I uint32_t*)0x40050150U) |

(GMAC) Octets Received Low Received Register

Definition at line 279 of file instance/gmac.h.

◆ REG_GMAC_OTHI

| #define REG_GMAC_OTHI (*(__I uint32_t*)0x40050104U) |

(GMAC) Octets Transmitted High Register

Definition at line 260 of file instance/gmac.h.

◆ REG_GMAC_OTLO

| #define REG_GMAC_OTLO (*(__I uint32_t*)0x40050100U) |

(GMAC) Octets Transmitted Low Register

Definition at line 259 of file instance/gmac.h.

◆ REG_GMAC_PEFRN

| #define REG_GMAC_PEFRN (*(__I uint32_t*)0x400501FCU) |

(GMAC) PTP Peer Event Frame Received Nanoseconds Register

Definition at line 317 of file instance/gmac.h.

◆ REG_GMAC_PEFRSH

| #define REG_GMAC_PEFRSH (*(__I uint32_t*)0x400500F4U) |

(GMAC) PTP Peer Event Frame Received Seconds High Register

Definition at line 257 of file instance/gmac.h.

◆ REG_GMAC_PEFRSL

| #define REG_GMAC_PEFRSL (*(__I uint32_t*)0x400501F8U) |

(GMAC) PTP Peer Event Frame Received Seconds Low Register

Definition at line 316 of file instance/gmac.h.

◆ REG_GMAC_PEFTN

| #define REG_GMAC_PEFTN (*(__I uint32_t*)0x400501F4U) |

(GMAC) PTP Peer Event Frame Transmitted Nanoseconds Register

Definition at line 315 of file instance/gmac.h.

◆ REG_GMAC_PEFTSH

| #define REG_GMAC_PEFTSH (*(__I uint32_t*)0x400500F0U) |

(GMAC) PTP Peer Event Frame Transmitted Seconds High Register

Definition at line 256 of file instance/gmac.h.

◆ REG_GMAC_PEFTSL

| #define REG_GMAC_PEFTSL (*(__I uint32_t*)0x400501F0U) |

(GMAC) PTP Peer Event Frame Transmitted Seconds Low Register

Definition at line 314 of file instance/gmac.h.

◆ REG_GMAC_PFR

| #define REG_GMAC_PFR (*(__I uint32_t*)0x40050164U) |

(GMAC) Pause Frames Received Register

Definition at line 284 of file instance/gmac.h.

◆ REG_GMAC_PFT

| #define REG_GMAC_PFT (*(__I uint32_t*)0x40050114U) |

(GMAC) Pause Frames Transmitted Register

Definition at line 264 of file instance/gmac.h.

◆ REG_GMAC_RBQB

| #define REG_GMAC_RBQB (*(__IO uint32_t*)0x40050018U) |

(GMAC) Receive Buffer Queue Base Address Register

Definition at line 218 of file instance/gmac.h.

◆ REG_GMAC_RBQBAPQ

| #define REG_GMAC_RBQBAPQ (*(__IO uint32_t*)0x4005047CU) |

(GMAC) Receive Buffer Queue Base Address Register Priority Queue (index = 1)

Definition at line 324 of file instance/gmac.h.

◆ REG_GMAC_RBSRPQ

| #define REG_GMAC_RBSRPQ (*(__IO uint32_t*)0x4005049CU) |

(GMAC) Receive Buffer Size Register Priority Queue (index = 1)

Definition at line 325 of file instance/gmac.h.

◆ REG_GMAC_RJFML

| #define REG_GMAC_RJFML (*(__IO uint32_t*)0x40050048U) |

(GMAC) RX Jumbo Frame Max Length Register

Definition at line 230 of file instance/gmac.h.

◆ REG_GMAC_ROE

| #define REG_GMAC_ROE (*(__I uint32_t*)0x400501A4U) |

(GMAC) Receive Overrun Register

Definition at line 300 of file instance/gmac.h.

◆ REG_GMAC_RPQ

| #define REG_GMAC_RPQ (*(__I uint32_t*)0x40050038U) |

(GMAC) Received Pause Quantum Register

Definition at line 226 of file instance/gmac.h.

◆ REG_GMAC_RPSF

| #define REG_GMAC_RPSF (*(__IO uint32_t*)0x40050044U) |

(GMAC) RX Partial Store and Forward Register

Definition at line 229 of file instance/gmac.h.

◆ REG_GMAC_RRE

| #define REG_GMAC_RRE (*(__I uint32_t*)0x400501A0U) |

(GMAC) Receive Resource Errors Register

Definition at line 299 of file instance/gmac.h.

◆ REG_GMAC_RSE

| #define REG_GMAC_RSE (*(__I uint32_t*)0x40050198U) |

(GMAC) Receive Symbol Errors Register

Definition at line 297 of file instance/gmac.h.

◆ REG_GMAC_RSR

| #define REG_GMAC_RSR (*(__IO uint32_t*)0x40050020U) |

(GMAC) Receive Status Register

Definition at line 220 of file instance/gmac.h.

◆ REG_GMAC_RXLPI

| #define REG_GMAC_RXLPI (*(__I uint32_t*)0x40050270U) |

(GMAC) Received LPI Transitions

Definition at line 318 of file instance/gmac.h.

◆ REG_GMAC_RXLPITIME

| #define REG_GMAC_RXLPITIME (*(__I uint32_t*)0x40050274U) |

(GMAC) Received LPI Time

Definition at line 319 of file instance/gmac.h.

◆ REG_GMAC_SAB1

| #define REG_GMAC_SAB1 (*(__IO uint32_t*)0x40050088U) |

(GMAC) Specific Address 1 Bottom Register

Definition at line 233 of file instance/gmac.h.

◆ REG_GMAC_SAB2

| #define REG_GMAC_SAB2 (*(__IO uint32_t*)0x40050090U) |

(GMAC) Specific Address 2 Bottom Register

Definition at line 235 of file instance/gmac.h.

◆ REG_GMAC_SAB3

| #define REG_GMAC_SAB3 (*(__IO uint32_t*)0x40050098U) |

(GMAC) Specific Address 3 Bottom Register

Definition at line 237 of file instance/gmac.h.

◆ REG_GMAC_SAB4

| #define REG_GMAC_SAB4 (*(__IO uint32_t*)0x400500A0U) |

(GMAC) Specific Address 4 Bottom Register

Definition at line 239 of file instance/gmac.h.

◆ REG_GMAC_SAMB1

| #define REG_GMAC_SAMB1 (*(__IO uint32_t*)0x400500C8U) |

(GMAC) Specific Address 1 Mask Bottom Register

Definition at line 249 of file instance/gmac.h.

◆ REG_GMAC_SAMT1

| #define REG_GMAC_SAMT1 (*(__IO uint32_t*)0x400500CCU) |

(GMAC) Specific Address 1 Mask Top Register

Definition at line 250 of file instance/gmac.h.

◆ REG_GMAC_SAT1

| #define REG_GMAC_SAT1 (*(__IO uint32_t*)0x4005008CU) |

(GMAC) Specific Address 1 Top Register

Definition at line 234 of file instance/gmac.h.

◆ REG_GMAC_SAT2

| #define REG_GMAC_SAT2 (*(__IO uint32_t*)0x40050094U) |

(GMAC) Specific Address 2 Top Register

Definition at line 236 of file instance/gmac.h.

◆ REG_GMAC_SAT3

| #define REG_GMAC_SAT3 (*(__IO uint32_t*)0x4005009CU) |

(GMAC) Specific Address 3 Top Register

Definition at line 238 of file instance/gmac.h.

◆ REG_GMAC_SAT4

| #define REG_GMAC_SAT4 (*(__IO uint32_t*)0x400500A4U) |

(GMAC) Specific Address 4 Top Register

Definition at line 240 of file instance/gmac.h.

◆ REG_GMAC_SCF

| #define REG_GMAC_SCF (*(__I uint32_t*)0x40050138U) |

(GMAC) Single Collision Frames Register

Definition at line 273 of file instance/gmac.h.

◆ REG_GMAC_SCH

| #define REG_GMAC_SCH (*(__IO uint32_t*)0x400500E4U) |

(GMAC) 1588 Timer Second Comparison High Register

Definition at line 253 of file instance/gmac.h.

◆ REG_GMAC_SCL

| #define REG_GMAC_SCL (*(__IO uint32_t*)0x400500E0U) |

(GMAC) 1588 Timer Second Comparison Low Register

Definition at line 252 of file instance/gmac.h.

◆ REG_GMAC_ST1RPQ

| #define REG_GMAC_ST1RPQ (*(__IO uint32_t*)0x40050500U) |

(GMAC) Screening Type 1 Register Priority Queue (index = 0)

Definition at line 329 of file instance/gmac.h.

◆ REG_GMAC_ST2CW00

| #define REG_GMAC_ST2CW00 (*(__IO uint32_t*)0x40050700U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 0)

Definition at line 335 of file instance/gmac.h.

◆ REG_GMAC_ST2CW01

| #define REG_GMAC_ST2CW01 (*(__IO uint32_t*)0x40050708U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 1)

Definition at line 337 of file instance/gmac.h.

◆ REG_GMAC_ST2CW010

| #define REG_GMAC_ST2CW010 (*(__IO uint32_t*)0x40050750U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 10)

Definition at line 355 of file instance/gmac.h.

◆ REG_GMAC_ST2CW011

| #define REG_GMAC_ST2CW011 (*(__IO uint32_t*)0x40050758U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 11)

Definition at line 357 of file instance/gmac.h.

◆ REG_GMAC_ST2CW012

| #define REG_GMAC_ST2CW012 (*(__IO uint32_t*)0x40050760U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 12)

Definition at line 359 of file instance/gmac.h.

◆ REG_GMAC_ST2CW013

| #define REG_GMAC_ST2CW013 (*(__IO uint32_t*)0x40050768U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 13)

Definition at line 361 of file instance/gmac.h.

◆ REG_GMAC_ST2CW014

| #define REG_GMAC_ST2CW014 (*(__IO uint32_t*)0x40050770U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 14)

Definition at line 363 of file instance/gmac.h.

◆ REG_GMAC_ST2CW015

| #define REG_GMAC_ST2CW015 (*(__IO uint32_t*)0x40050778U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 15)

Definition at line 365 of file instance/gmac.h.

◆ REG_GMAC_ST2CW016

| #define REG_GMAC_ST2CW016 (*(__IO uint32_t*)0x40050780U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 16)

Definition at line 367 of file instance/gmac.h.

◆ REG_GMAC_ST2CW017

| #define REG_GMAC_ST2CW017 (*(__IO uint32_t*)0x40050788U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 17)

Definition at line 369 of file instance/gmac.h.

◆ REG_GMAC_ST2CW018

| #define REG_GMAC_ST2CW018 (*(__IO uint32_t*)0x40050790U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 18)

Definition at line 371 of file instance/gmac.h.

◆ REG_GMAC_ST2CW019

| #define REG_GMAC_ST2CW019 (*(__IO uint32_t*)0x40050798U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 19)

Definition at line 373 of file instance/gmac.h.

◆ REG_GMAC_ST2CW02

| #define REG_GMAC_ST2CW02 (*(__IO uint32_t*)0x40050710U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 2)

Definition at line 339 of file instance/gmac.h.

◆ REG_GMAC_ST2CW020

| #define REG_GMAC_ST2CW020 (*(__IO uint32_t*)0x400507A0U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 20)

Definition at line 375 of file instance/gmac.h.

◆ REG_GMAC_ST2CW021

| #define REG_GMAC_ST2CW021 (*(__IO uint32_t*)0x400507A8U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 21)

Definition at line 377 of file instance/gmac.h.

◆ REG_GMAC_ST2CW022

| #define REG_GMAC_ST2CW022 (*(__IO uint32_t*)0x400507B0U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 22)

Definition at line 379 of file instance/gmac.h.

◆ REG_GMAC_ST2CW023

| #define REG_GMAC_ST2CW023 (*(__IO uint32_t*)0x400507B8U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 23)

Definition at line 381 of file instance/gmac.h.

◆ REG_GMAC_ST2CW03

| #define REG_GMAC_ST2CW03 (*(__IO uint32_t*)0x40050718U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 3)

Definition at line 341 of file instance/gmac.h.

◆ REG_GMAC_ST2CW04

| #define REG_GMAC_ST2CW04 (*(__IO uint32_t*)0x40050720U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 4)

Definition at line 343 of file instance/gmac.h.

◆ REG_GMAC_ST2CW05

| #define REG_GMAC_ST2CW05 (*(__IO uint32_t*)0x40050728U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 5)

Definition at line 345 of file instance/gmac.h.

◆ REG_GMAC_ST2CW06

| #define REG_GMAC_ST2CW06 (*(__IO uint32_t*)0x40050730U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 6)

Definition at line 347 of file instance/gmac.h.

◆ REG_GMAC_ST2CW07

| #define REG_GMAC_ST2CW07 (*(__IO uint32_t*)0x40050738U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 7)

Definition at line 349 of file instance/gmac.h.

◆ REG_GMAC_ST2CW08

| #define REG_GMAC_ST2CW08 (*(__IO uint32_t*)0x40050740U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 8)

Definition at line 351 of file instance/gmac.h.

◆ REG_GMAC_ST2CW09

| #define REG_GMAC_ST2CW09 (*(__IO uint32_t*)0x40050748U) |

(GMAC) Screening Type 2 Compare Word 0 Register (index = 9)

Definition at line 353 of file instance/gmac.h.

◆ REG_GMAC_ST2CW10

| #define REG_GMAC_ST2CW10 (*(__IO uint32_t*)0x40050704U) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 0)

Definition at line 336 of file instance/gmac.h.

◆ REG_GMAC_ST2CW11

| #define REG_GMAC_ST2CW11 (*(__IO uint32_t*)0x4005070CU) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 1)

Definition at line 338 of file instance/gmac.h.

◆ REG_GMAC_ST2CW110

| #define REG_GMAC_ST2CW110 (*(__IO uint32_t*)0x40050754U) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 10)

Definition at line 356 of file instance/gmac.h.

◆ REG_GMAC_ST2CW111

| #define REG_GMAC_ST2CW111 (*(__IO uint32_t*)0x4005075CU) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 11)

Definition at line 358 of file instance/gmac.h.

◆ REG_GMAC_ST2CW112

| #define REG_GMAC_ST2CW112 (*(__IO uint32_t*)0x40050764U) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 12)

Definition at line 360 of file instance/gmac.h.

◆ REG_GMAC_ST2CW113

| #define REG_GMAC_ST2CW113 (*(__IO uint32_t*)0x4005076CU) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 13)

Definition at line 362 of file instance/gmac.h.

◆ REG_GMAC_ST2CW114

| #define REG_GMAC_ST2CW114 (*(__IO uint32_t*)0x40050774U) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 14)

Definition at line 364 of file instance/gmac.h.

◆ REG_GMAC_ST2CW115

| #define REG_GMAC_ST2CW115 (*(__IO uint32_t*)0x4005077CU) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 15)

Definition at line 366 of file instance/gmac.h.

◆ REG_GMAC_ST2CW116

| #define REG_GMAC_ST2CW116 (*(__IO uint32_t*)0x40050784U) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 16)

Definition at line 368 of file instance/gmac.h.

◆ REG_GMAC_ST2CW117

| #define REG_GMAC_ST2CW117 (*(__IO uint32_t*)0x4005078CU) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 17)

Definition at line 370 of file instance/gmac.h.

◆ REG_GMAC_ST2CW118

| #define REG_GMAC_ST2CW118 (*(__IO uint32_t*)0x40050794U) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 18)

Definition at line 372 of file instance/gmac.h.

◆ REG_GMAC_ST2CW119

| #define REG_GMAC_ST2CW119 (*(__IO uint32_t*)0x4005079CU) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 19)

Definition at line 374 of file instance/gmac.h.

◆ REG_GMAC_ST2CW12

| #define REG_GMAC_ST2CW12 (*(__IO uint32_t*)0x40050714U) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 2)

Definition at line 340 of file instance/gmac.h.

◆ REG_GMAC_ST2CW120

| #define REG_GMAC_ST2CW120 (*(__IO uint32_t*)0x400507A4U) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 20)

Definition at line 376 of file instance/gmac.h.

◆ REG_GMAC_ST2CW121

| #define REG_GMAC_ST2CW121 (*(__IO uint32_t*)0x400507ACU) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 21)

Definition at line 378 of file instance/gmac.h.

◆ REG_GMAC_ST2CW122

| #define REG_GMAC_ST2CW122 (*(__IO uint32_t*)0x400507B4U) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 22)

Definition at line 380 of file instance/gmac.h.

◆ REG_GMAC_ST2CW123

| #define REG_GMAC_ST2CW123 (*(__IO uint32_t*)0x400507BCU) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 23)

Definition at line 382 of file instance/gmac.h.

◆ REG_GMAC_ST2CW13

| #define REG_GMAC_ST2CW13 (*(__IO uint32_t*)0x4005071CU) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 3)

Definition at line 342 of file instance/gmac.h.

◆ REG_GMAC_ST2CW14

| #define REG_GMAC_ST2CW14 (*(__IO uint32_t*)0x40050724U) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 4)

Definition at line 344 of file instance/gmac.h.

◆ REG_GMAC_ST2CW15

| #define REG_GMAC_ST2CW15 (*(__IO uint32_t*)0x4005072CU) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 5)

Definition at line 346 of file instance/gmac.h.

◆ REG_GMAC_ST2CW16

| #define REG_GMAC_ST2CW16 (*(__IO uint32_t*)0x40050734U) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 6)

Definition at line 348 of file instance/gmac.h.

◆ REG_GMAC_ST2CW17

| #define REG_GMAC_ST2CW17 (*(__IO uint32_t*)0x4005073CU) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 7)

Definition at line 350 of file instance/gmac.h.

◆ REG_GMAC_ST2CW18

| #define REG_GMAC_ST2CW18 (*(__IO uint32_t*)0x40050744U) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 8)

Definition at line 352 of file instance/gmac.h.

◆ REG_GMAC_ST2CW19

| #define REG_GMAC_ST2CW19 (*(__IO uint32_t*)0x4005074CU) |

(GMAC) Screening Type 2 Compare Word 1 Register (index = 9)

Definition at line 354 of file instance/gmac.h.

◆ REG_GMAC_ST2ER

| #define REG_GMAC_ST2ER (*(__IO uint32_t*)0x400506E0U) |

(GMAC) Screening Type 2 Ethertype Register (index = 0)

Definition at line 334 of file instance/gmac.h.

◆ REG_GMAC_ST2RPQ

| #define REG_GMAC_ST2RPQ (*(__IO uint32_t*)0x40050540U) |

(GMAC) Screening Type 2 Register Priority Queue (index = 0)

Definition at line 330 of file instance/gmac.h.

◆ REG_GMAC_SVLAN

| #define REG_GMAC_SVLAN (*(__IO uint32_t*)0x400500C0U) |

(GMAC) Stacked VLAN Register

Definition at line 247 of file instance/gmac.h.

◆ REG_GMAC_TA

| #define REG_GMAC_TA (*(__O uint32_t*)0x400501D8U) |

(GMAC) 1588 Timer Adjust Register

Definition at line 308 of file instance/gmac.h.

◆ REG_GMAC_TBFR1023

| #define REG_GMAC_TBFR1023 (*(__I uint32_t*)0x40050178U) |

(GMAC) 512 to 1023 Byte Frames Received Register

Definition at line 289 of file instance/gmac.h.

◆ REG_GMAC_TBFR127

| #define REG_GMAC_TBFR127 (*(__I uint32_t*)0x4005016CU) |

(GMAC) 65 to 127 Byte Frames Received Register

Definition at line 286 of file instance/gmac.h.

◆ REG_GMAC_TBFR1518

| #define REG_GMAC_TBFR1518 (*(__I uint32_t*)0x4005017CU) |

(GMAC) 1024 to 1518 Byte Frames Received Register

Definition at line 290 of file instance/gmac.h.

◆ REG_GMAC_TBFR255

| #define REG_GMAC_TBFR255 (*(__I uint32_t*)0x40050170U) |

(GMAC) 128 to 255 Byte Frames Received Register

Definition at line 287 of file instance/gmac.h.

◆ REG_GMAC_TBFR511

| #define REG_GMAC_TBFR511 (*(__I uint32_t*)0x40050174U) |

(GMAC) 256 to 511 Byte Frames Received Register

Definition at line 288 of file instance/gmac.h.

◆ REG_GMAC_TBFT1023

| #define REG_GMAC_TBFT1023 (*(__I uint32_t*)0x40050128U) |

(GMAC) 512 to 1023 Byte Frames Transmitted Register

Definition at line 269 of file instance/gmac.h.

◆ REG_GMAC_TBFT127

| #define REG_GMAC_TBFT127 (*(__I uint32_t*)0x4005011CU) |

(GMAC) 65 to 127 Byte Frames Transmitted Register

Definition at line 266 of file instance/gmac.h.

◆ REG_GMAC_TBFT1518

| #define REG_GMAC_TBFT1518 (*(__I uint32_t*)0x4005012CU) |

(GMAC) 1024 to 1518 Byte Frames Transmitted Register

Definition at line 270 of file instance/gmac.h.

◆ REG_GMAC_TBFT255

| #define REG_GMAC_TBFT255 (*(__I uint32_t*)0x40050120U) |

(GMAC) 128 to 255 Byte Frames Transmitted Register

Definition at line 267 of file instance/gmac.h.

◆ REG_GMAC_TBFT511

| #define REG_GMAC_TBFT511 (*(__I uint32_t*)0x40050124U) |

(GMAC) 256 to 511 Byte Frames Transmitted Register

Definition at line 268 of file instance/gmac.h.

◆ REG_GMAC_TBQB

| #define REG_GMAC_TBQB (*(__IO uint32_t*)0x4005001CU) |

(GMAC) Transmit Buffer Queue Base Address Register

Definition at line 219 of file instance/gmac.h.

◆ REG_GMAC_TBQBAPQ

| #define REG_GMAC_TBQBAPQ (*(__IO uint32_t*)0x4005043CU) |

(GMAC) Transmit Buffer Queue Base Address Register Priority Queue (index = 1)

Definition at line 323 of file instance/gmac.h.

◆ REG_GMAC_TCE

| #define REG_GMAC_TCE (*(__I uint32_t*)0x400501ACU) |

(GMAC) TCP Checksum Errors Register

Definition at line 302 of file instance/gmac.h.

◆ REG_GMAC_TI

| #define REG_GMAC_TI (*(__IO uint32_t*)0x400501DCU) |

(GMAC) 1588 Timer Increment Register

Definition at line 309 of file instance/gmac.h.

◆ REG_GMAC_TIDM1

| #define REG_GMAC_TIDM1 (*(__IO uint32_t*)0x400500A8U) |

(GMAC) Type ID Match 1 Register

Definition at line 241 of file instance/gmac.h.

◆ REG_GMAC_TIDM2

| #define REG_GMAC_TIDM2 (*(__IO uint32_t*)0x400500ACU) |

(GMAC) Type ID Match 2 Register

Definition at line 242 of file instance/gmac.h.

◆ REG_GMAC_TIDM3

| #define REG_GMAC_TIDM3 (*(__IO uint32_t*)0x400500B0U) |

(GMAC) Type ID Match 3 Register

Definition at line 243 of file instance/gmac.h.

◆ REG_GMAC_TIDM4

| #define REG_GMAC_TIDM4 (*(__IO uint32_t*)0x400500B4U) |

(GMAC) Type ID Match 4 Register

Definition at line 244 of file instance/gmac.h.

◆ REG_GMAC_TISUBN

| #define REG_GMAC_TISUBN (*(__IO uint32_t*)0x400501BCU) |

(GMAC) 1588 Timer Increment Sub-nanoseconds Register

Definition at line 304 of file instance/gmac.h.

◆ REG_GMAC_TMXBFR

| #define REG_GMAC_TMXBFR (*(__I uint32_t*)0x40050180U) |

(GMAC) 1519 to Maximum Byte Frames Received Register

Definition at line 291 of file instance/gmac.h.

◆ REG_GMAC_TN

| #define REG_GMAC_TN (*(__IO uint32_t*)0x400501D4U) |

(GMAC) 1588 Timer Nanoseconds Register

Definition at line 307 of file instance/gmac.h.

◆ REG_GMAC_TPFCP

| #define REG_GMAC_TPFCP (*(__IO uint32_t*)0x400500C4U) |

(GMAC) Transmit PFC Pause Register

Definition at line 248 of file instance/gmac.h.

◆ REG_GMAC_TPQ

| #define REG_GMAC_TPQ (*(__IO uint32_t*)0x4005003CU) |

(GMAC) Transmit Pause Quantum Register

Definition at line 227 of file instance/gmac.h.

◆ REG_GMAC_TPSF

| #define REG_GMAC_TPSF (*(__IO uint32_t*)0x40050040U) |

(GMAC) TX Partial Store and Forward Register

Definition at line 228 of file instance/gmac.h.

◆ REG_GMAC_TSH

| #define REG_GMAC_TSH (*(__IO uint32_t*)0x400501C0U) |

(GMAC) 1588 Timer Seconds High Register

Definition at line 305 of file instance/gmac.h.

◆ REG_GMAC_TSL

| #define REG_GMAC_TSL (*(__IO uint32_t*)0x400501D0U) |

(GMAC) 1588 Timer Seconds Low Register

Definition at line 306 of file instance/gmac.h.

◆ REG_GMAC_TSR

| #define REG_GMAC_TSR (*(__IO uint32_t*)0x40050014U) |

(GMAC) Transmit Status Register

Definition at line 217 of file instance/gmac.h.

◆ REG_GMAC_TUR

| #define REG_GMAC_TUR (*(__I uint32_t*)0x40050134U) |

(GMAC) Transmit Underruns Register

Definition at line 272 of file instance/gmac.h.

◆ REG_GMAC_TXLPI

| #define REG_GMAC_TXLPI (*(__I uint32_t*)0x40050278U) |

(GMAC) Transmit LPI Transitions

Definition at line 320 of file instance/gmac.h.

◆ REG_GMAC_TXLPITIME

| #define REG_GMAC_TXLPITIME (*(__I uint32_t*)0x4005027CU) |

(GMAC) Transmit LPI Time

Definition at line 321 of file instance/gmac.h.

◆ REG_GMAC_UCE

| #define REG_GMAC_UCE (*(__I uint32_t*)0x400501B0U) |

(GMAC) UDP Checksum Errors Register

Definition at line 303 of file instance/gmac.h.

◆ REG_GMAC_UFR

| #define REG_GMAC_UFR (*(__I uint32_t*)0x40050184U) |

(GMAC) Undersize Frames Received Register

Definition at line 292 of file instance/gmac.h.

◆ REG_GMAC_UR

| #define REG_GMAC_UR (*(__IO uint32_t*)0x4005000CU) |

(GMAC) User Register

Definition at line 215 of file instance/gmac.h.

◆ REG_GMAC_WOL

| #define REG_GMAC_WOL (*(__IO uint32_t*)0x400500B8U) |

(GMAC) Wake on LAN Register

Definition at line 245 of file instance/gmac.h.