Go to the source code of this file.

Macros | |

| #define | REG_CKGR_MCFR (*(__IO uint32_t*)0x400E0624U) |

| (PMC) Main Clock Frequency Register More... | |

| #define | REG_CKGR_MOR (*(__IO uint32_t*)0x400E0620U) |

| (PMC) Main Oscillator Register More... | |

| #define | REG_CKGR_PLLAR (*(__IO uint32_t*)0x400E0628U) |

| (PMC) PLLA Register More... | |

| #define | REG_CKGR_UCKR (*(__IO uint32_t*)0x400E061CU) |

| (PMC) UTMI Clock Register More... | |

| #define | REG_PMC_APLLACR (*(__IO uint32_t*)0x400E0758U) |

| (PMC) Audio PLL Analog Configuration Register More... | |

| #define | REG_PMC_FOCR (*(__O uint32_t*)0x400E0678U) |

| (PMC) Fault Output Clear Register More... | |

| #define | REG_PMC_FSMR (*(__IO uint32_t*)0x400E0670U) |

| (PMC) Fast Startup Mode Register More... | |

| #define | REG_PMC_FSPR (*(__IO uint32_t*)0x400E0674U) |

| (PMC) Fast Startup Polarity Register More... | |

| #define | REG_PMC_IDR (*(__O uint32_t*)0x400E0664U) |

| (PMC) Interrupt Disable Register More... | |

| #define | REG_PMC_IER (*(__O uint32_t*)0x400E0660U) |

| (PMC) Interrupt Enable Register More... | |

| #define | REG_PMC_IMR (*(__I uint32_t*)0x400E066CU) |

| (PMC) Interrupt Mask Register More... | |

| #define | REG_PMC_MCKR (*(__IO uint32_t*)0x400E0630U) |

| (PMC) Master Clock Register More... | |

| #define | REG_PMC_OCR (*(__IO uint32_t*)0x400E0710U) |

| (PMC) Oscillator Calibration Register More... | |

| #define | REG_PMC_PCDR0 (*(__O uint32_t*)0x400E0614U) |

| (PMC) Peripheral Clock Disable Register 0 More... | |

| #define | REG_PMC_PCDR1 (*(__O uint32_t*)0x400E0704U) |

| (PMC) Peripheral Clock Disable Register 1 More... | |

| #define | REG_PMC_PCER0 (*(__O uint32_t*)0x400E0610U) |

| (PMC) Peripheral Clock Enable Register 0 More... | |

| #define | REG_PMC_PCER1 (*(__O uint32_t*)0x400E0700U) |

| (PMC) Peripheral Clock Enable Register 1 More... | |

| #define | REG_PMC_PCK (*(__IO uint32_t*)0x400E0640U) |

| (PMC) Programmable Clock 0 Register More... | |

| #define | REG_PMC_PCR (*(__IO uint32_t*)0x400E070CU) |

| (PMC) Peripheral Control Register More... | |

| #define | REG_PMC_PCSR0 (*(__I uint32_t*)0x400E0618U) |

| (PMC) Peripheral Clock Status Register 0 More... | |

| #define | REG_PMC_PCSR1 (*(__I uint32_t*)0x400E0708U) |

| (PMC) Peripheral Clock Status Register 1 More... | |

| #define | REG_PMC_PMMR (*(__IO uint32_t*)0x400E0730U) |

| (PMC) PLL Maximum Multiplier Value Register More... | |

| #define | REG_PMC_SCDR (*(__O uint32_t*)0x400E0604U) |

| (PMC) System Clock Disable Register More... | |

| #define | REG_PMC_SCER (*(__O uint32_t*)0x400E0600U) |

| (PMC) System Clock Enable Register More... | |

| #define | REG_PMC_SCSR (*(__I uint32_t*)0x400E0608U) |

| (PMC) System Clock Status Register More... | |

| #define | REG_PMC_SLPWK_AIPR (*(__I uint32_t*)0x400E0744U) |

| (PMC) SleepWalking Activity In Progress Register More... | |

| #define | REG_PMC_SLPWK_ASR0 (*(__I uint32_t*)0x400E0720U) |

| (PMC) SleepWalking Activity Status Register 0 More... | |

| #define | REG_PMC_SLPWK_ASR1 (*(__I uint32_t*)0x400E0740U) |

| (PMC) SleepWalking Activity Status Register 1 More... | |

| #define | REG_PMC_SLPWK_DR0 (*(__O uint32_t*)0x400E0718U) |

| (PMC) SleepWalking Disable Register 0 More... | |

| #define | REG_PMC_SLPWK_DR1 (*(__O uint32_t*)0x400E0738U) |

| (PMC) SleepWalking Disable Register 1 More... | |

| #define | REG_PMC_SLPWK_ER0 (*(__O uint32_t*)0x400E0714U) |

| (PMC) SleepWalking Enable Register 0 More... | |

| #define | REG_PMC_SLPWK_ER1 (*(__O uint32_t*)0x400E0734U) |

| (PMC) SleepWalking Enable Register 1 More... | |

| #define | REG_PMC_SLPWK_SR0 (*(__I uint32_t*)0x400E071CU) |

| (PMC) SleepWalking Status Register 0 More... | |

| #define | REG_PMC_SLPWK_SR1 (*(__I uint32_t*)0x400E073CU) |

| (PMC) SleepWalking Status Register 1 More... | |

| #define | REG_PMC_SR (*(__I uint32_t*)0x400E0668U) |

| (PMC) Status Register More... | |

| #define | REG_PMC_USB (*(__IO uint32_t*)0x400E0638U) |

| (PMC) USB Clock Register More... | |

| #define | REG_PMC_VERSION (*(__I uint32_t*)0x400E06FCU) |

| (PMC) Version Register More... | |

| #define | REG_PMC_WMST (*(__IO uint32_t*)0x400E075CU) |

| (PMC) Wait Mode Startup Time Register More... | |

| #define | REG_PMC_WPMR (*(__IO uint32_t*)0x400E06E4U) |

| (PMC) Write Protection Mode Register More... | |

| #define | REG_PMC_WPSR (*(__I uint32_t*)0x400E06E8U) |

| (PMC) Write Protection Status Register More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

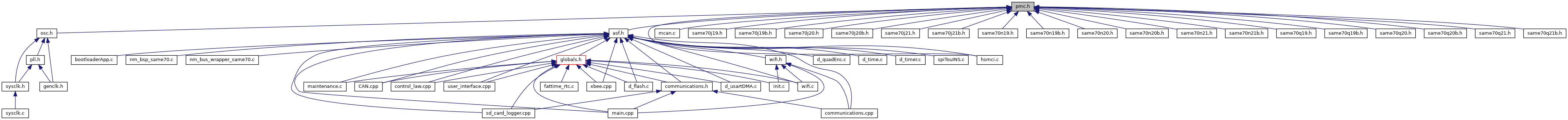

Definition in file utils/cmsis/same70/include/instance/pmc.h.

Macro Definition Documentation

◆ REG_CKGR_MCFR

| #define REG_CKGR_MCFR (*(__IO uint32_t*)0x400E0624U) |

(PMC) Main Clock Frequency Register

Definition at line 89 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_CKGR_MOR

| #define REG_CKGR_MOR (*(__IO uint32_t*)0x400E0620U) |

(PMC) Main Oscillator Register

Definition at line 88 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_CKGR_PLLAR

| #define REG_CKGR_PLLAR (*(__IO uint32_t*)0x400E0628U) |

(PMC) PLLA Register

Definition at line 90 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_CKGR_UCKR

| #define REG_CKGR_UCKR (*(__IO uint32_t*)0x400E061CU) |

(PMC) UTMI Clock Register

Definition at line 87 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_APLLACR

| #define REG_PMC_APLLACR (*(__IO uint32_t*)0x400E0758U) |

(PMC) Audio PLL Analog Configuration Register

Definition at line 119 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_FOCR

| #define REG_PMC_FOCR (*(__O uint32_t*)0x400E0678U) |

(PMC) Fault Output Clear Register

Definition at line 100 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_FSMR

| #define REG_PMC_FSMR (*(__IO uint32_t*)0x400E0670U) |

(PMC) Fast Startup Mode Register

Definition at line 98 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_FSPR

| #define REG_PMC_FSPR (*(__IO uint32_t*)0x400E0674U) |

(PMC) Fast Startup Polarity Register

Definition at line 99 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_IDR

| #define REG_PMC_IDR (*(__O uint32_t*)0x400E0664U) |

(PMC) Interrupt Disable Register

Definition at line 95 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_IER

| #define REG_PMC_IER (*(__O uint32_t*)0x400E0660U) |

(PMC) Interrupt Enable Register

Definition at line 94 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_IMR

| #define REG_PMC_IMR (*(__I uint32_t*)0x400E066CU) |

(PMC) Interrupt Mask Register

Definition at line 97 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_MCKR

| #define REG_PMC_MCKR (*(__IO uint32_t*)0x400E0630U) |

(PMC) Master Clock Register

Definition at line 91 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_OCR

| #define REG_PMC_OCR (*(__IO uint32_t*)0x400E0710U) |

(PMC) Oscillator Calibration Register

Definition at line 108 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_PCDR0

| #define REG_PMC_PCDR0 (*(__O uint32_t*)0x400E0614U) |

(PMC) Peripheral Clock Disable Register 0

Definition at line 85 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_PCDR1

| #define REG_PMC_PCDR1 (*(__O uint32_t*)0x400E0704U) |

(PMC) Peripheral Clock Disable Register 1

Definition at line 105 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_PCER0

| #define REG_PMC_PCER0 (*(__O uint32_t*)0x400E0610U) |

(PMC) Peripheral Clock Enable Register 0

Definition at line 84 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_PCER1

| #define REG_PMC_PCER1 (*(__O uint32_t*)0x400E0700U) |

(PMC) Peripheral Clock Enable Register 1

Definition at line 104 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_PCK

| #define REG_PMC_PCK (*(__IO uint32_t*)0x400E0640U) |

(PMC) Programmable Clock 0 Register

Definition at line 93 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_PCR

| #define REG_PMC_PCR (*(__IO uint32_t*)0x400E070CU) |

(PMC) Peripheral Control Register

Definition at line 107 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_PCSR0

| #define REG_PMC_PCSR0 (*(__I uint32_t*)0x400E0618U) |

(PMC) Peripheral Clock Status Register 0

Definition at line 86 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_PCSR1

| #define REG_PMC_PCSR1 (*(__I uint32_t*)0x400E0708U) |

(PMC) Peripheral Clock Status Register 1

Definition at line 106 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_PMMR

| #define REG_PMC_PMMR (*(__IO uint32_t*)0x400E0730U) |

(PMC) PLL Maximum Multiplier Value Register

Definition at line 113 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SCDR

| #define REG_PMC_SCDR (*(__O uint32_t*)0x400E0604U) |

(PMC) System Clock Disable Register

Definition at line 82 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SCER

| #define REG_PMC_SCER (*(__O uint32_t*)0x400E0600U) |

(PMC) System Clock Enable Register

Definition at line 81 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SCSR

| #define REG_PMC_SCSR (*(__I uint32_t*)0x400E0608U) |

(PMC) System Clock Status Register

Definition at line 83 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SLPWK_AIPR

| #define REG_PMC_SLPWK_AIPR (*(__I uint32_t*)0x400E0744U) |

(PMC) SleepWalking Activity In Progress Register

Definition at line 118 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SLPWK_ASR0

| #define REG_PMC_SLPWK_ASR0 (*(__I uint32_t*)0x400E0720U) |

(PMC) SleepWalking Activity Status Register 0

Definition at line 112 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SLPWK_ASR1

| #define REG_PMC_SLPWK_ASR1 (*(__I uint32_t*)0x400E0740U) |

(PMC) SleepWalking Activity Status Register 1

Definition at line 117 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SLPWK_DR0

| #define REG_PMC_SLPWK_DR0 (*(__O uint32_t*)0x400E0718U) |

(PMC) SleepWalking Disable Register 0

Definition at line 110 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SLPWK_DR1

| #define REG_PMC_SLPWK_DR1 (*(__O uint32_t*)0x400E0738U) |

(PMC) SleepWalking Disable Register 1

Definition at line 115 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SLPWK_ER0

| #define REG_PMC_SLPWK_ER0 (*(__O uint32_t*)0x400E0714U) |

(PMC) SleepWalking Enable Register 0

Definition at line 109 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SLPWK_ER1

| #define REG_PMC_SLPWK_ER1 (*(__O uint32_t*)0x400E0734U) |

(PMC) SleepWalking Enable Register 1

Definition at line 114 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SLPWK_SR0

| #define REG_PMC_SLPWK_SR0 (*(__I uint32_t*)0x400E071CU) |

(PMC) SleepWalking Status Register 0

Definition at line 111 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SLPWK_SR1

| #define REG_PMC_SLPWK_SR1 (*(__I uint32_t*)0x400E073CU) |

(PMC) SleepWalking Status Register 1

Definition at line 116 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_SR

| #define REG_PMC_SR (*(__I uint32_t*)0x400E0668U) |

(PMC) Status Register

Definition at line 96 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_USB

| #define REG_PMC_USB (*(__IO uint32_t*)0x400E0638U) |

(PMC) USB Clock Register

Definition at line 92 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_VERSION

| #define REG_PMC_VERSION (*(__I uint32_t*)0x400E06FCU) |

(PMC) Version Register

Definition at line 103 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_WMST

| #define REG_PMC_WMST (*(__IO uint32_t*)0x400E075CU) |

(PMC) Wait Mode Startup Time Register

Definition at line 120 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_WPMR

| #define REG_PMC_WPMR (*(__IO uint32_t*)0x400E06E4U) |

(PMC) Write Protection Mode Register

Definition at line 101 of file utils/cmsis/same70/include/instance/pmc.h.

◆ REG_PMC_WPSR

| #define REG_PMC_WPSR (*(__I uint32_t*)0x400E06E8U) |

(PMC) Write Protection Status Register

Definition at line 102 of file utils/cmsis/same70/include/instance/pmc.h.