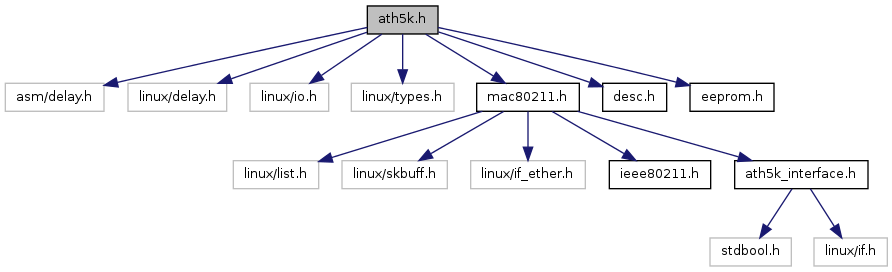

#include <asm/delay.h>#include <linux/delay.h>#include <linux/io.h>#include <linux/types.h>#include "mac80211.h"#include "desc.h"#include "eeprom.h"

Go to the source code of this file.

Define Documentation

| #define ah_ee_version ah_capabilities.cap_eeprom.ee_version |

Definition at line 1028 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ah_modes ah_capabilities.cap_mode |

Definition at line 1027 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_ASSERT_ENTRY | ( | _e, | |

| _s | |||

| ) |

do { \ if (_e >= _s) \ return (false); \ } while (0)

Definition at line 776 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_BEACON_ENA 0x00800000 /*enable beacon xmit*/ |

Definition at line 595 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_BEACON_PERIOD 0x0000ffff |

Definition at line 594 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_BEACON_RESET_TSF 0x01000000 /*force a TSF reset*/ |

Definition at line 596 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_HIGH_ID | ( | _a | ) | ((_a)[4] | (_a)[5] << 8) |

Definition at line 159 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INI_RFGAIN_2GHZ 1 |

Definition at line 143 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INI_RFGAIN_5GHZ 0 |

Definition at line 142 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INI_VAL_11A 0 |

Definition at line 146 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INI_VAL_11A_TURBO 1 |

Definition at line 147 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INI_VAL_11B 2 |

Definition at line 148 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INI_VAL_11G 3 |

Definition at line 149 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INI_VAL_11G_TURBO 4 |

Definition at line 150 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INI_VAL_MAX 5 |

Definition at line 152 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INI_VAL_XR 0 |

Definition at line 151 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_ACK_CTS_TIMEOUT 1024 |

Definition at line 217 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_ACK_CTS_TIMEOUT_TURBO 0x08000800 |

Definition at line 218 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_CARR_SENSE_EN 1 |

Definition at line 198 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_CFG 0x00000000 |

Definition at line 206 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_CYCRSSI_THR1 2 |

Definition at line 210 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_EIFS 3440 |

Definition at line 221 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_EIFS_TURBO 6880 |

Definition at line 222 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_LG_RETRY AR5K_INIT_SH_RETRY |

Definition at line 226 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_PROG_IFS 920 |

Definition at line 219 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_PROG_IFS_TURBO 960 |

Definition at line 220 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_PROTO_TIME_CNTRL |

( \

(AR5K_INIT_CARR_SENSE_EN << 26) | (AR5K_INIT_EIFS << 12) | \

(AR5K_INIT_PROG_IFS) \

)

Definition at line 239 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_PROTO_TIME_CNTRL_TURBO |

( \

(AR5K_INIT_CARR_SENSE_EN << 26) | (AR5K_INIT_EIFS_TURBO << 12) | \

(AR5K_INIT_PROG_IFS_TURBO) \

)

Definition at line 243 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_SH_RETRY 10 |

Definition at line 225 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_SIFS 560 |

Definition at line 223 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_SIFS_TURBO 480 |

Definition at line 224 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

Definition at line 228 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_SLOT_TIME 396 |

Definition at line 215 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_SLOT_TIME_TURBO 480 |

Definition at line 216 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_SSH_RETRY 32 |

Definition at line 227 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_TRANSMIT_LATENCY |

( \

(AR5K_INIT_TX_LATENCY << 14) | (AR5K_INIT_USEC_32 << 7) | \

(AR5K_INIT_USEC) \

)

Definition at line 231 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_TRANSMIT_LATENCY_TURBO |

( \

(AR5K_INIT_TX_LATENCY << 14) | (AR5K_INIT_USEC_32 << 7) | \

(AR5K_INIT_USEC_TURBO) \

)

Definition at line 235 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_TX_LATENCY 502 |

Definition at line 211 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_TX_RETRY 10 |

Definition at line 229 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_USEC 39 |

Definition at line 212 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_USEC_32 31 |

Definition at line 214 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_INIT_USEC_TURBO 79 |

Definition at line 213 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_KEYCACHE_SIZE 8 |

Definition at line 765 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_LED_ASSOC 3 /*IEEE80211_S_ASSOC*/ |

Definition at line 921 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_LED_AUTH 2 /*IEEE80211_S_AUTH*/ |

Definition at line 920 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_LED_INIT 0 /*IEEE80211_S_INIT*/ |

Definition at line 918 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_LED_RUN 4 /*IEEE80211_S_RUN*/ |

Definition at line 922 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_LED_SCAN 1 /*IEEE80211_S_SCAN*/ |

Definition at line 919 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_LOW_ID | ( | _a | ) |

( \ (_a)[0] | (_a)[1] << 8 | (_a)[2] << 16 | (_a)[3] << 24 \ )

Definition at line 155 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_MAX_GPIO 10 |

Definition at line 999 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_MAX_RATES 32 |

Seems the ar5xxx harware supports up to 32 rates, indexed by 1-32.

The rate code is used to get the RX rate or set the TX rate on the hardware descriptors. It is also used for internal modulation control and settings.

This is the hardware rate map we are aware of:

rate_code 0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x08 rate_kbps 3000 1000 ? ? ? 2000 500 48000

rate_code 0x09 0x0A 0x0B 0x0C 0x0D 0x0E 0x0F 0x10 rate_kbps 24000 12000 6000 54000 36000 18000 9000 ?

rate_code 17 18 19 20 21 22 23 24 rate_kbps ? ? ? ? ? ? ? 11000

rate_code 25 26 27 28 29 30 31 32 rate_kbps 5500 2000 1000 11000S 5500S 2000S ? ?

"S" indicates CCK rates with short preamble.

AR5211 has different rate codes for CCK (802.11B) rates. It only uses the lowest 4 bits, so they are the same as below with a 0xF mask. (0xB, 0xA, 0x9 and 0x8 for 1M, 2M, 5.5M and 11M). We handle this in ath5k_setup_bands().

Definition at line 736 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_MAX_RF_BANKS 8 |

Definition at line 1000 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_NUM_TX_QUEUES 10 |

Definition at line 452 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_NUM_TX_QUEUES_NOQCU 2 |

Definition at line 453 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_PHY_READ | ( | ah, | |

| _reg | |||

| ) | ath5k_hw_reg_read(ah, (ah)->ah_phy + ((_reg) << 2)) |

Definition at line 114 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_PHY_WRITE | ( | ah, | |

| _reg, | |||

| _val | |||

| ) | ath5k_hw_reg_write(ah, _val, (ah)->ah_phy + ((_reg) << 2)) |

Definition at line 117 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_Q_DISABLE_BITS | ( | _reg, | |

| _queue | |||

| ) |

do { \ _reg &= ~(1 << _queue); \ } while (0)

Definition at line 131 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_Q_ENABLE_BITS | ( | _reg, | |

| _queue | |||

| ) |

do { \ _reg |= 1 << _queue; \ } while (0)

Definition at line 127 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_REG_DISABLE_BITS | ( | ah, | |

| _reg, | |||

| _flags | |||

| ) | ath5k_hw_reg_write(ah, ath5k_hw_reg_read(ah, _reg) & ~(_flags), _reg) |

Definition at line 110 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_REG_ENABLE_BITS | ( | ah, | |

| _reg, | |||

| _flags | |||

| ) | ath5k_hw_reg_write(ah, ath5k_hw_reg_read(ah, _reg) | (_flags), _reg) |

Definition at line 107 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_REG_MASKED_BITS | ( | ah, | |

| _reg, | |||

| _flags, | |||

| _mask | |||

| ) |

ath5k_hw_reg_write(ah, (ath5k_hw_reg_read(ah, _reg) & \ (_mask)) | (_flags), _reg)

Definition at line 103 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_REG_MS | ( | _val, | |

| _flags | |||

| ) | (((_val) & (_flags)) >> _flags##_S) |

Definition at line 91 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_REG_READ_Q | ( | ah, | |

| _reg, | |||

| _queue | |||

| ) | (ath5k_hw_reg_read(ah, _reg) & (1 << _queue)) \ |

Definition at line 121 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_REG_SM | ( | _val, | |

| _flags | |||

| ) | (((_val) << _flags##_S) & (_flags)) |

Definition at line 87 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_REG_WAIT | ( | _i | ) |

do { \ if (_i % 64) \ udelay(1); \ } while (0)

Definition at line 136 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_REG_WRITE_BITS | ( | ah, | |

| _reg, | |||

| _flags, | |||

| _val | |||

| ) |

ath5k_hw_reg_write(ah, (ath5k_hw_reg_read(ah, _reg) & ~(_flags)) | \ (((_val) << _flags##_S) & (_flags)), _reg)

Definition at line 99 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_REG_WRITE_Q | ( | ah, | |

| _reg, | |||

| _queue | |||

| ) | ath5k_hw_reg_write(ah, (1 << _queue), _reg) |

Definition at line 124 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_RSSI_EP_MULTIPLIER (1<<7) |

Definition at line 774 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_RXERR_CRC 0x01 |

Definition at line 581 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_RXERR_DECRYPT 0x08 |

Definition at line 584 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_RXERR_FIFO 0x04 |

Definition at line 583 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_RXERR_MIC 0x10 |

Definition at line 585 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_RXERR_PHY 0x02 |

Definition at line 582 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_RXKEYIX_INVALID ((u8) - 1) |

Definition at line 586 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SET_SHORT_PREAMBLE 0x04 |

Definition at line 759 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SLOT_TIME_20 880 |

Definition at line 657 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SLOT_TIME_9 396 |

Definition at line 656 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SLOT_TIME_MAX 0xffff |

Definition at line 658 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SOFTLED_OFF 1 |

Definition at line 927 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SOFTLED_ON 0 |

Definition at line 926 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SOFTLED_PIN 0 |

Definition at line 925 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR2413 0x78 /* Griffin lite */ |

Definition at line 298 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR2414 0x70 /* Griffin */ |

Definition at line 299 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR2415 0xb0 /* Talon */ |

Definition at line 303 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR2417 0xf0 /* Nala */ |

Definition at line 307 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR2425 0xe0 /* Swan */ |

Definition at line 306 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5210 0x00 /* Crete */ |

Definition at line 289 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5211 0x40 /* Oahu */ |

Definition at line 293 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5212 0x50 /* Venice */ |

Definition at line 294 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5212_V4 0x54 /* ??? */ |

Definition at line 295 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5213 0x55 /* ??? */ |

Definition at line 296 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5213A 0x59 /* Hainan */ |

Definition at line 297 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5311 0x10 /* Maui 1 */ |

Definition at line 290 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5311A 0x20 /* Maui 2 */ |

Definition at line 291 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5311B 0x30 /* Spirit */ |

Definition at line 292 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5413 0xa4 /* Eagle lite */ |

Definition at line 301 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5414 0xa0 /* Eagle */ |

Definition at line 302 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5416 0xc0 /* PCI-E */ |

Definition at line 304 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5418 0xca /* PCI-E */ |

Definition at line 305 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_AR5424 0x90 /* Condor */ |

Definition at line 300 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_PHY_2413 0x45 |

Definition at line 331 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_PHY_2425 0x70 |

Definition at line 333 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_PHY_5211 0x30 |

Definition at line 327 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_PHY_5212 0x41 |

Definition at line 328 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_PHY_5212A 0x42 |

Definition at line 329 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_PHY_5212B 0x43 |

Definition at line 330 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_PHY_5413 0x61 |

Definition at line 332 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_2111 0x20 |

Definition at line 312 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_2112 0x40 |

Definition at line 316 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_2112A 0x45 |

Definition at line 317 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_2112B 0x46 |

Definition at line 318 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_2316 0x70 /* Cobra SoC */ |

Definition at line 321 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_2317 0x80 |

Definition at line 322 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_2413 0x50 |

Definition at line 319 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_2425 0xa2 |

Definition at line 324 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_5110 0x00 |

Definition at line 309 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_5111 0x10 |

Definition at line 310 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_5111A 0x15 |

Definition at line 311 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_5112 0x30 |

Definition at line 313 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_5112A 0x35 |

Definition at line 314 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_5112B 0x36 |

Definition at line 315 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_5133 0xc0 |

Definition at line 325 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_5413 0x60 |

Definition at line 320 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_RAD_5424 0xa0 /* Mostly same as 5413 */ |

Definition at line 323 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_SREV_UNKNOWN 0xffff |

Definition at line 287 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_ADDITIONAL_SWBA_BACKOFF 0 |

Definition at line 167 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_AIFS 2 |

Definition at line 183 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_AIFS_11B 2 |

Definition at line 184 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_AIFS_XR 0 |

Definition at line 185 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_BEACON_INTERVAL 100 |

Definition at line 182 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_BMISS_THRES 7 |

Definition at line 180 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_CWMAX 1023 |

Definition at line 189 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_CWMAX_11B 1023 |

Definition at line 190 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_CWMAX_XR 7 |

Definition at line 191 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_CWMIN 15 |

Definition at line 186 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_CWMIN_11B 31 |

Definition at line 187 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_CWMIN_XR 3 |

Definition at line 188 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_DEFAULT_TXPOWER 25 |

Definition at line 194 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_DMA_BEACON_RESP 2 |

Definition at line 165 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_HWTXTRIES 0 |

Definition at line 196 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_MAX_TX_FIFO_THRES ((IEEE80211_MAX_LEN / 64) + 1) |

Definition at line 170 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_MAX_TXPOWER 63 |

Definition at line 193 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_MIN_TX_FIFO_THRES 1 |

Definition at line 169 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_NOISE_FLOOR -72 |

Definition at line 192 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_RADAR_ALERT false |

Definition at line 168 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_REGISTER_DWELL_TIME 20000 |

Definition at line 181 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_REGISTER_TIMEOUT 20000 |

Definition at line 171 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_RSSI_THRES 129 |

Definition at line 174 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_SW_BEACON_RESP 10 |

Definition at line 166 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TUNE_TPC_TXPOWER false |

Definition at line 195 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXERR_FIFO 0x04 |

Definition at line 432 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXERR_FILT 0x02 |

Definition at line 431 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXERR_XRETRY 0x01 |

Definition at line 430 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXKEYIX_INVALID ((u32) - 1) |

Definition at line 587 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXPOWER_CCK | ( | _r, | |

| _v | |||

| ) |

( \

(ah->ah_txpower.txp_rates_power_table[(_r)] & 0x3f) << (_v) \

)

Definition at line 543 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXPOWER_OFDM | ( | _r, | |

| _v | |||

| ) |

( \

((0 & 1) << ((_v) + 6)) | \

(((ah->ah_txpower.txp_rates_power_table[(_r)]) & 0x3f) << (_v)) \

)

Definition at line 538 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_BACKOFF_DISABLE 0x0200 /* Disable random post-backoff */ |

Definition at line 499 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_CBRORNINT_ENABLE 0x0020 /* Enable CBRORN interrupt */ |

Definition at line 495 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_CBRURNINT_ENABLE 0x0040 /* Enable CBRURN interrupt */ |

Definition at line 496 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_COMPRESSION_ENABLE 0x2000 /* Enable hw compression -not implemented-*/ |

Definition at line 503 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_FRAG_BURST_BACKOFF_ENABLE 0x0800 /* Enable backoff while bursting */ |

Definition at line 501 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_POST_FR_BKOFF_DIS 0x1000 /* Disable backoff while bursting */ |

Definition at line 502 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_QTRIGINT_ENABLE 0x0080 /* Enable QTRIG interrupt */ |

Definition at line 497 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_RDYTIME_EXP_POLICY_ENABLE 0x0300 /* Enable ready time expiry policy (?)*/ |

Definition at line 500 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_TXDESCINT_ENABLE 0x0008 /* Enable TXDESC interrupt -not used- */ |

Definition at line 493 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_TXEOLINT_ENABLE 0x0004 /* Enable TXEOL interrupt -not used- */ |

Definition at line 492 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_TXERRINT_ENABLE 0x0002 /* Enable TXERR interrupt */ |

Definition at line 491 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_TXNOFRMINT_ENABLE 0x0100 /* Enable TXNOFRM interrupt */ |

Definition at line 498 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_TXOKINT_ENABLE 0x0001 /* Enable TXOK interrupt */ |

Definition at line 490 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_FLAG_TXURNINT_ENABLE 0x0010 /* Enable TXURN interrupt */ |

Definition at line 494 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXQ_USEDEFAULT ((u32) -1) |

Definition at line 249 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define AR5K_TXSTAT_ALTRATE 0x80 |

Definition at line 429 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

Definition at line 77 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_INFO | ( | _sc, | |

| _fmt, | |||

| ... | |||

| ) | printk("ath5k info:" _fmt, ##__VA_ARGS__) |

Definition at line 71 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_PRINTF | ( | fmt, | |

| ... | |||

| ) | printk("%s: " fmt, __func__, ##__VA_ARGS__) |

Definition at line 69 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_11M 0x18 |

Definition at line 742 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_12M 0x0A |

Definition at line 746 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_18M 0x0E |

Definition at line 747 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_1M 0x1B |

Definition at line 739 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_24M 0x09 |

Definition at line 748 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_2M 0x1A |

Definition at line 740 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_36M 0x0D |

Definition at line 749 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_48M 0x08 |

Definition at line 750 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_54M 0x0C |

Definition at line 751 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_5_5M 0x19 |

Definition at line 741 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_6M 0x0B |

Definition at line 744 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_9M 0x0F |

Definition at line 745 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_XR_1M 0x02 |

Definition at line 754 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_XR_2M 0x06 |

Definition at line 755 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_XR_3M 0x01 |

Definition at line 756 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_RATE_CODE_XR_500K 0x07 |

Definition at line 753 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define ATH5K_WARN | ( | _sc, | |

| _fmt, | |||

| ... | |||

| ) | printk("ath5k warn:" _fmt, ##__VA_ARGS__) |

Definition at line 74 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_108A CHANNEL_T |

Definition at line 676 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_108G CHANNEL_TG |

Definition at line 677 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_2GHZ 0x0080 /* 2GHz channel. */ |

Definition at line 665 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_5GHZ 0x0100 /* 5GHz channel */ |

Definition at line 666 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_A (CHANNEL_5GHZ|CHANNEL_OFDM) |

Definition at line 671 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_ALL |

(CHANNEL_OFDM|CHANNEL_CCK|CHANNEL_2GHZ|CHANNEL_5GHZ| \ CHANNEL_TURBO)

Definition at line 680 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_ALL_NOTURBO (CHANNEL_ALL & ~CHANNEL_TURBO) |

Definition at line 683 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_B (CHANNEL_2GHZ|CHANNEL_CCK) |

Definition at line 672 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_CCK 0x0020 /* CCK channel */ |

Definition at line 663 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_CW_INT 0x0008 /* Contention Window interference detected */ |

Definition at line 661 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_DYN 0x0400 /* Dynamic CCK-OFDM channel (for g operation) */ |

Definition at line 668 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_G (CHANNEL_2GHZ|CHANNEL_OFDM) |

Definition at line 673 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_MODES CHANNEL_ALL |

Definition at line 684 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_OFDM 0x0040 /* OFDM channel */ |

Definition at line 664 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_PASSIVE 0x0200 /* Only passive scan allowed */ |

Definition at line 667 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_T (CHANNEL_5GHZ|CHANNEL_OFDM|CHANNEL_TURBO) |

Definition at line 674 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_TG (CHANNEL_2GHZ|CHANNEL_OFDM|CHANNEL_TURBO) |

Definition at line 675 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_TURBO 0x0010 /* Turbo Channel */ |

Definition at line 662 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_X (CHANNEL_5GHZ|CHANNEL_OFDM|CHANNEL_XR) |

Definition at line 678 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define CHANNEL_XR 0x0800 /* XR channel */ |

Definition at line 669 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define IEEE80211_MAX_LEN 2500 |

Definition at line 336 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

Definition at line 691 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define IS_CHAN_XR | ( | _c | ) | ((_c->hw_value & CHANNEL_XR) != 0) |

Definition at line 690 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define MODULATION_TURBO 0x00000080 |

Definition at line 395 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define MODULATION_XR 0x00000200 |

Definition at line 356 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_3COM_2_3CRPAG175 0x0013 /* 3CRPAG175 (Atheros AR5212) */ |

Definition at line 41 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_3COM_3CRDAG675 0x0013 /* 3CRDAG675 (Atheros AR5212) */ |

Definition at line 40 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR2413 0x001a /* AR2413 (Griffin-lite) */ |

Definition at line 59 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5210 0x0007 /* AR5210 */ |

Definition at line 36 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5210_AP 0x0207 /* AR5210 (Early) */ |

Definition at line 42 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5210_DEFAULT 0x1107 /* AR5210 (no eeprom) */ |

Definition at line 44 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5211 0x0012 /* AR5211 */ |

Definition at line 38 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5211_DEFAULT 0x1112 /* AR5211 (no eeprom) */ |

Definition at line 46 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5211_FPGA11B 0xf11b /* AR5211 (emulation board) */ |

Definition at line 49 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5211_LEGACY 0xff12 /* AR5211 (emulation board) */ |

Definition at line 48 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5212 0x0013 /* AR5212 */ |

Definition at line 39 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5212_0014 0x0014 /* AR5212 compatible */ |

Definition at line 53 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5212_0015 0x0015 /* AR5212 compatible */ |

Definition at line 54 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5212_0016 0x0016 /* AR5212 compatible */ |

Definition at line 55 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5212_0017 0x0017 /* AR5212 compatible */ |

Definition at line 56 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5212_0018 0x0018 /* AR5212 compatible */ |

Definition at line 57 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5212_0019 0x0019 /* AR5212 compatible */ |

Definition at line 58 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5212_DEFAULT 0x1113 /* AR5212 (no eeprom) */ |

Definition at line 45 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5212_FPGA 0xf013 /* AR5212 (emulation board) */ |

Definition at line 47 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5212_IBM 0x1014 /* AR5212 (IBM MiniPCI) */ |

Definition at line 43 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5311 0x0011 /* AR5311 */ |

Definition at line 37 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5312_REV2 0x0052 /* AR5312 WMAC (AP31) */ |

Definition at line 50 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5312_REV7 0x0057 /* AR5312 WMAC (AP30-040) */ |

Definition at line 51 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5312_REV8 0x0058 /* AR5312 WMAC (AP43-030) */ |

Definition at line 52 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5413 0x001b /* AR5413 (Eagle) */ |

Definition at line 60 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5416 0x0023 /* AR5416 */ |

Definition at line 62 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5418 0x0024 /* AR5418 */ |

Definition at line 63 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| #define PCI_DEVICE_ID_ATHEROS_AR5424 0x001c /* AR5424 (Condor PCI-E) */ |

Definition at line 61 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

Definition at line 628 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

Enumeration Type Documentation

- Enumerator:

Definition at line 935 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| enum ath5k_dmasize |

- Enumerator:

Definition at line 550 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| enum ath5k_driver_mode |

- Enumerator:

Definition at line 397 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| enum ath5k_int |

enum ath5k_int - Hardware interrupt masks helpers

: mask to identify received frame interrupts, of type AR5K_ISR_RXOK or AR5K_ISR_RXERR : Request RX descriptor/Read RX descriptor (?) : No frame received (?) : received End Of List for VEOL (Virtual End Of List). The Queue Control Unit (QCU) signals an EOL interrupt only if a descriptor's LinkPtr is NULL. For more details, refer to: http://www.freepatentsonline.com/20030225739.html : Indicates we got RX overrun (eg. no more descriptors). Note that Rx overrun is not always fatal, on some chips we can continue operation without reseting the card, that's why int_fatal is not common for all chips. : mask to identify received frame interrupts, of type AR5K_ISR_TXOK or AR5K_ISR_TXERR : Request TX descriptor/Read TX status descriptor (?) : received when we should increase the TX trigger threshold We currently do increments on interrupt by (AR5K_TUNE_MAX_TX_FIFO_THRES - current_trigger_level) / 2 : Indicates the Management Information Base counters should be checked. We should do this with ath5k_hw_update_mib_counters() but it seems we should also then do some noise immunity work. : RX PHY Error : RX Key cache miss : SoftWare Beacon Alert - indicates its time to send a beacon that must be handled in software. The alternative is if you have VEOL support, in that case you let the hardware deal with things. : If in STA mode this indicates we have stopped seeing beacons from the AP have associated with, we should probably try to reassociate. When in IBSS mode this might mean we have not received any beacons from any local stations. Note that every station in an IBSS schedules to send beacons at the Target Beacon Transmission Time (TBTT) with a random backoff. : Beacon Not Ready interrupt - ?? : GPIO interrupt is used for RF Kill, disabled for now until properly handled : Fatal errors were encountered, typically caused by DMA errors. These types of errors we can enable seem to be of type AR5K_SIMR2_MCABT, AR5K_SIMR2_SSERR and AR5K_SIMR2_DPERR. : Used to clear and set the IER : signals the card has been removed : common interrupts shared amogst MACs with the same bit value

These are mapped to take advantage of some common bits between the MACs, to be able to set intr properties easier. Some of them are not used yet inside hw.c. Most map to the respective hw interrupt value as they are common amogst different MACs.

- Enumerator:

Definition at line 837 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| enum ath5k_pkt_type |

- Enumerator:

Definition at line 526 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| enum ath5k_power_mode |

- Enumerator:

Definition at line 905 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| enum ath5k_radio |

- Enumerator:

Definition at line 261 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| enum ath5k_rfgain |

- Enumerator:

Definition at line 635 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

- Enumerator:

AR5K_SWI_FULL_CALIBRATION AR5K_SWI_SHORT_CALIBRATION AR5K_SWI_FULL_CALIBRATION AR5K_SWI_SHORT_CALIBRATION AR5K_SWI_FULL_CALIBRATION AR5K_SWI_SHORT_CALIBRATION

Definition at line 897 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| enum ath5k_srev_type |

- Enumerator:

AR5K_VERSION_MAC AR5K_VERSION_RAD AR5K_VERSION_MAC AR5K_VERSION_RAD AR5K_VERSION_MAC AR5K_VERSION_RAD

Definition at line 276 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| enum ath5k_tx_queue |

enum ath5k_tx_queue - Queue types used to classify tx queues. : q is unused -- see ath5k_hw_release_tx_queue : A normal data queue : An XR-data queue : The beacon queue : The after-beacon queue : Unscheduled Automatic Power Save Delivery queue

- Enumerator:

Definition at line 443 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| enum ath5k_tx_queue_id |

- Enumerator:

Definition at line 475 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

- Enumerator:

AR5K_WME_AC_BK AR5K_WME_AC_BE AR5K_WME_AC_VI AR5K_WME_AC_VO AR5K_WME_AC_BK AR5K_WME_AC_BE AR5K_WME_AC_VI AR5K_WME_AC_VO AR5K_WME_AC_BK AR5K_WME_AC_BE AR5K_WME_AC_VI AR5K_WME_AC_VO

Definition at line 462 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| enum ath5k_version |

- Enumerator:

AR5K_AR5210 AR5K_AR5211 AR5K_AR5212 AR5K_AR5210 AR5K_AR5211 AR5K_AR5212 AR5K_AR5210 AR5K_AR5211 AR5K_AR5212

Definition at line 254 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

Function Documentation

| bool ath5k_channel_ok | ( | struct ath5k_hw * | ah, |

| u16 | freq, | ||

| unsigned int | flags | ||

| ) |

Definition at line 830 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| void ath5k_eeprom_detach | ( | struct ath5k_hw * | ah | ) |

Definition at line 1583 of file linux_ks/hwi/ath5k_raw/module/eeprom.c.

| int ath5k_eeprom_init | ( | struct ath5k_hw * | ah | ) |

Definition at line 1735 of file linux_ks/hwi/ath5k_raw/module/eeprom.c.

| bool ath5k_eeprom_is_hb63 | ( | struct ath5k_hw * | ah | ) |

| int ath5k_eeprom_read_mac | ( | struct ath5k_hw * | ah, |

| u8 * | mac | ||

| ) |

Definition at line 1765 of file linux_ks/hwi/ath5k_raw/module/eeprom.c.

| int ath5k_hw_attach | ( | struct ath5k_softc * | sc | ) |

ath5k_hw_attach - Check if hw is supported and init the needed structs

: The &struct ath5k_softc we got from the driver's attach function

Check if the device is supported, perform a POST and initialize the needed structs. Returns -ENOMEM if we don't have memory for the needed structs, -ENODEV if the device is not supported or prints an error msg if something else went wrong.

Definition at line 104 of file linux_ks/hwi/ath5k_raw/module/attach.c.

| static u32 ath5k_hw_bitswap | ( | u32 | val, |

| unsigned int | bits | ||

| ) | [inline, static] |

Definition at line 1327 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| void ath5k_hw_calibration_poll | ( | struct ath5k_hw * | ah | ) |

Definition at line 1108 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| bool ath5k_hw_chan_has_spur_noise | ( | struct ath5k_hw * | ah, |

| struct ieee80211_channel * | channel | ||

| ) |

Definition at line 1391 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| int ath5k_hw_channel | ( | struct ath5k_hw * | ah, |

| struct ieee80211_channel * | channel | ||

| ) |

Definition at line 1051 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| int ath5k_hw_clear_mcast_filter_idx | ( | struct ath5k_hw * | ah, |

| u32 | index | ||

| ) |

Definition at line 492 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| static unsigned int ath5k_hw_clocktoh | ( | unsigned int | clock, |

| bool | turbo | ||

| ) | [inline, static] |

Definition at line 1289 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| void ath5k_hw_detach | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_detach - Free the ath5k_hw struct

: The &struct ath5k_hw

Definition at line 346 of file linux_ks/hwi/ath5k_raw/module/attach.c.

| int ath5k_hw_disable_pspoll | ( | struct ath5k_hw * | ah | ) |

Definition at line 181 of file linux_ks/hwi/ath5k_raw/module/caps.c.

| int ath5k_hw_enable_pspoll | ( | struct ath5k_hw * | ah, |

| u8 * | bssid, | ||

| u16 | assoc_id | ||

| ) |

Definition at line 167 of file linux_ks/hwi/ath5k_raw/module/caps.c.

| enum ath5k_rfgain ath5k_hw_gainf_calibrate | ( | struct ath5k_hw * | ah | ) |

Definition at line 377 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| unsigned int ath5k_hw_get_ack_timeout | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_het_ack_timeout - Get ACK timeout from PCU in usec

: The &struct ath5k_hw

Definition at line 154 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| int ath5k_hw_get_capability | ( | struct ath5k_hw * | ah, |

| enum ath5k_capability_type | cap_type, | ||

| u32 | capability, | ||

| u32 * | result | ||

| ) |

Definition at line 116 of file linux_ks/hwi/ath5k_raw/module/caps.c.

| unsigned int ath5k_hw_get_cts_timeout | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_get_cts_timeout - Get CTS timeout from PCU in usec

: The &struct ath5k_hw

Definition at line 186 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| unsigned int ath5k_hw_get_def_antenna | ( | struct ath5k_hw * | ah | ) |

Definition at line 1708 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| u32 ath5k_hw_get_gpio | ( | struct ath5k_hw * | ah, |

| u32 | gpio | ||

| ) |

| int ath5k_hw_get_isr | ( | struct ath5k_hw * | ah, |

| enum ath5k_int * | interrupt_mask | ||

| ) |

Definition at line 474 of file linux_ks/hwi/ath5k_raw/module/dma.c.

| void ath5k_hw_get_lladdr | ( | struct ath5k_hw * | ah, |

| u8 * | mac | ||

| ) |

ath5k_hw_get_lladdr - Get station id

: The &struct ath5k_hw : The card's mac address

Initialize ah->ah_sta_id using the mac address provided (just a memcpy).

TODO: Remove it once we merge ath5k_softc and ath5k_hw

Definition at line 228 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| u32 ath5k_hw_get_rx_filter | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_get_rx_filter - Get current rx filter

: The &struct ath5k_hw

Returns the RX filter by reading rx filter and phy error filter registers. RX filter is used to set the allowed frame types that PCU will accept and pass to the driver. For a list of frame types check out reg.h.

Definition at line 518 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| u32 ath5k_hw_get_rxdp | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_get_rxdp - Get RX Descriptor's address

: The &struct ath5k_hw

Definition at line 84 of file linux_ks/hwi/ath5k_raw/module/dma.c.

| unsigned int ath5k_hw_get_slot_time | ( | struct ath5k_hw * | ah | ) |

Definition at line 521 of file linux_ks/hwi/ath5k_raw/module/qcu.c.

| u32 ath5k_hw_get_tsf32 | ( | struct ath5k_hw * | ah | ) |

| u64 ath5k_hw_get_tsf64 | ( | struct ath5k_hw * | ah | ) |

| int ath5k_hw_get_tx_queueprops | ( | struct ath5k_hw * | ah, |

| int | queue, | ||

| struct ath5k_txq_info * | queue_info | ||

| ) |

Definition at line 31 of file linux_ks/hwi/ath5k_raw/module/qcu.c.

| u32 ath5k_hw_get_txdp | ( | struct ath5k_hw * | ah, |

| unsigned int | queue | ||

| ) |

ath5k_hw_get_txdp - Get TX Descriptor's address for a specific queue

: The &struct ath5k_hw : The hw queue number

Get TX descriptor's address for a specific queue. For 5210 we ignore the queue number and use tx queue type since we only have 2 queues. We use TXDP0 for normal data queue and TXDP1 for beacon queue. For newer chips with QCU/DCU we just read the corresponding TXDP register.

XXX: Is TXDP read and clear ?

Definition at line 296 of file linux_ks/hwi/ath5k_raw/module/dma.c.

| static unsigned int ath5k_hw_htoclock | ( | unsigned int | usec, |

| bool | turbo | ||

| ) | [inline, static] |

Definition at line 1280 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| void ath5k_hw_init_beacon | ( | struct ath5k_hw * | ah, |

| u32 | next_beacon, | ||

| u32 | interval | ||

| ) |

| int ath5k_hw_init_desc_functions | ( | struct ath5k_hw * | ah | ) |

Definition at line 663 of file linux_ks/hwi/ath5k_raw/module/desc.c.

| bool ath5k_hw_is_intr_pending | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_is_intr_pending - Check if we have pending interrupts

: The &struct ath5k_hw

Check if we have pending interrupts to process. Returns 1 if we have pending interrupts and 0 if we haven't.

Definition at line 452 of file linux_ks/hwi/ath5k_raw/module/dma.c.

| int ath5k_hw_nic_wakeup | ( | struct ath5k_hw * | ah, |

| int | flags, | ||

| bool | initial | ||

| ) |

Definition at line 366 of file linux_ks/hwi/ath5k_raw/module/reset.c.

| int ath5k_hw_noise_floor_calibration | ( | struct ath5k_hw * | ah, |

| short | freq | ||

| ) |

ath5k_hw_noise_floor_calibration - perform PHY noise floor calibration

: struct ath5k_hw pointer we are operating on : the channel frequency, just used for error logging

This function performs a noise floor calibration of the PHY and waits for it to complete. Then the noise floor value is compared to some maximum noise floor we consider valid.

Note that this is different from what the madwifi HAL does: it reads the noise floor and afterwards initiates the calibration. Since the noise floor calibration can take some time to finish, depending on the current channel use, that avoids the occasional timeout warnings we are seeing now.

See the following link for an Atheros patent on noise floor calibration: http://patft.uspto.gov/netacgi/nph-Parser?Sect1=PTO1&Sect2=HITOFF&d=PALL \ &p=1&u=%2Fnetahtml%2FPTO%2Fsrchnum.htm&r=1&f=G&l=50&s1=7245893.PN.&OS=PN/7

XXX: Since during noise floor calibration antennas are detached according to the patent, we should stop tx queues here.

Definition at line 1153 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| u32 ath5k_hw_num_tx_pending | ( | struct ath5k_hw * | ah, |

| unsigned int | queue | ||

| ) |

Definition at line 149 of file linux_ks/hwi/ath5k_raw/module/qcu.c.

| int ath5k_hw_on_hold | ( | struct ath5k_hw * | ah | ) |

Definition at line 314 of file linux_ks/hwi/ath5k_raw/module/reset.c.

| int ath5k_hw_phy_calibrate | ( | struct ath5k_hw * | ah, |

| struct ieee80211_channel * | channel | ||

| ) |

Definition at line 1374 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| int ath5k_hw_phy_disable | ( | struct ath5k_hw * | ah | ) |

Definition at line 1638 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| u16 ath5k_hw_radio_revision | ( | struct ath5k_hw * | ah, |

| unsigned int | chan | ||

| ) |

Definition at line 1650 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| static u32 ath5k_hw_reg_read | ( | struct ath5k_hw * | ah, |

| u16 | reg | ||

| ) | [inline, static] |

Definition at line 1294 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| static void ath5k_hw_reg_write | ( | struct ath5k_hw * | ah, |

| u32 | val, | ||

| u16 | reg | ||

| ) | [inline, static] |

Definition at line 1299 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| void ath5k_hw_release_tx_queue | ( | struct ath5k_hw * | ah, |

| unsigned int | queue | ||

| ) |

Definition at line 178 of file linux_ks/hwi/ath5k_raw/module/qcu.c.

| int ath5k_hw_reset | ( | struct ath5k_hw * | ah, |

| struct ieee80211_channel * | channel, | ||

| bool | change_channel | ||

| ) |

Definition at line 870 of file linux_ks/hwi/ath5k_raw/module/reset.c.

| void ath5k_hw_reset_tsf | ( | struct ath5k_hw * | ah | ) |

| int ath5k_hw_reset_tx_queue | ( | struct ath5k_hw * | ah, |

| unsigned int | queue | ||

| ) |

Definition at line 193 of file linux_ks/hwi/ath5k_raw/module/qcu.c.

| int ath5k_hw_rfgain_init | ( | struct ath5k_hw * | ah, |

| unsigned int | freq | ||

| ) |

Definition at line 442 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| int ath5k_hw_rfgain_opt_init | ( | struct ath5k_hw * | ah | ) |

Definition at line 143 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| int ath5k_hw_rfregs_init | ( | struct ath5k_hw * | ah, |

| struct ieee80211_channel * | channel, | ||

| unsigned int | mode | ||

| ) |

Definition at line 504 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| void ath5k_hw_set_ack_bitrate_high | ( | struct ath5k_hw * | ah, |

| bool | high | ||

| ) |

ath5k_hw_set_ack_bitrate - set bitrate for ACKs

: The &struct ath5k_hw : Flag to determine if we want to use high transmition rate for ACKs or not

If high flag is set, we tell hw to use a set of control rates based on the current transmition rate (check out control_rates array inside reset.c). If not hw just uses the lowest rate available for the current modulation scheme being used (1Mbit for CCK and 6Mbits for OFDM).

Definition at line 131 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| int ath5k_hw_set_ack_timeout | ( | struct ath5k_hw * | ah, |

| unsigned int | timeout | ||

| ) |

ath5k_hw_set_ack_timeout - Set ACK timeout on PCU

: The &struct ath5k_hw : Timeout in usec

Definition at line 168 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| void ath5k_hw_set_antenna_mode | ( | struct ath5k_hw * | ah, |

| u8 | ant_mode | ||

| ) |

Definition at line 1763 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| void ath5k_hw_set_associd | ( | struct ath5k_hw * | ah, |

| const u8 * | bssid, | ||

| u16 | assoc_id | ||

| ) |

ath5k_hw_set_associd - Set BSSID for association

: The &struct ath5k_hw : BSSID : Assoc id

Sets the BSSID which trigers the "SME Join" operation

Definition at line 271 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| int ath5k_hw_set_bssid_mask | ( | struct ath5k_hw * | ah, |

| const u8 * | mask | ||

| ) |

ath5k_hw_set_bssid_mask - filter out bssids we listen

: the &struct ath5k_hw : the bssid_mask, a u8 array of size ETH_ALEN

BSSID masking is a method used by AR5212 and newer hardware to inform PCU which bits of the interface's MAC address should be looked at when trying to decide which packets to ACK. In station mode and AP mode with a single BSS every bit matters since we lock to only one BSS. In AP mode with multiple BSSes (virtual interfaces) not every bit matters because hw must accept frames for all BSSes and so we tweak some bits of our mac address in order to have multiple BSSes.

NOTE: This is a simple filter and does *not* filter out all relevant frames. Some frames that are not for us might get ACKed from us by PCU because they just match the mask.

When handling multiple BSSes you can get the BSSID mask by computing the set of ~ ( MAC XOR BSSID ) for all bssids we handle.

When you do this you are essentially computing the common bits of all your BSSes. Later it is assumed the harware will "and" (&) the BSSID mask with the MAC address to obtain the relevant bits and compare the result with (frame's BSSID & mask) to see if they match.

Definition at line 402 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| int ath5k_hw_set_capabilities | ( | struct ath5k_hw * | ah | ) |

Definition at line 33 of file linux_ks/hwi/ath5k_raw/module/caps.c.

| int ath5k_hw_set_cts_timeout | ( | struct ath5k_hw * | ah, |

| unsigned int | timeout | ||

| ) |

ath5k_hw_set_cts_timeout - Set CTS timeout on PCU

: The &struct ath5k_hw : Timeout in usec

Definition at line 199 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| void ath5k_hw_set_def_antenna | ( | struct ath5k_hw * | ah, |

| u8 | ant | ||

| ) |

Definition at line 1700 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| int ath5k_hw_set_gpio | ( | struct ath5k_hw * | ah, |

| u32 | gpio, | ||

| u32 | val | ||

| ) |

| int ath5k_hw_set_gpio_input | ( | struct ath5k_hw * | ah, |

| u32 | gpio | ||

| ) |

| void ath5k_hw_set_gpio_intr | ( | struct ath5k_hw * | ah, |

| unsigned int | gpio, | ||

| u32 | interrupt_level | ||

| ) |

| int ath5k_hw_set_gpio_output | ( | struct ath5k_hw * | ah, |

| u32 | gpio | ||

| ) |

| enum ath5k_int ath5k_hw_set_imr | ( | struct ath5k_hw * | ah, |

| enum ath5k_int | new_mask | ||

| ) |

ath5k_hw_set_imr - Set interrupt mask

: The &struct ath5k_hw : The new interrupt mask to be set

Set the interrupt mask in hw to save interrupts. We do that by mapping ath5k_int bits to hw-specific bits to remove abstraction and writing Interrupt Mask Register.

Definition at line 620 of file linux_ks/hwi/ath5k_raw/module/dma.c.

| void ath5k_hw_set_ledstate | ( | struct ath5k_hw * | ah, |

| unsigned int | state | ||

| ) |

| int ath5k_hw_set_lladdr | ( | struct ath5k_hw * | ah, |

| const u8 * | mac | ||

| ) |

ath5k_hw_set_lladdr - Set station id

: The &struct ath5k_hw : The card's mac address

Set station id on hw using the provided mac address

Definition at line 242 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| void ath5k_hw_set_mcast_filter | ( | struct ath5k_hw * | ah, |

| u32 | filter0, | ||

| u32 | filter1 | ||

| ) |

Definition at line 463 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| int ath5k_hw_set_mcast_filter_idx | ( | struct ath5k_hw * | ah, |

| u32 | index | ||

| ) |

Definition at line 474 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| int ath5k_hw_set_opmode | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_set_opmode - Set PCU operating mode

: The &struct ath5k_hw

Initialize PCU for the various operating modes (AP/STA etc)

NOTE: ah->ah_op_mode must be set before calling this.

Definition at line 45 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| int ath5k_hw_set_power | ( | struct ath5k_hw * | ah, |

| enum ath5k_power_mode | mode, | ||

| bool | set_chip, | ||

| u16 | sleep_duration | ||

| ) |

Definition at line 223 of file linux_ks/hwi/ath5k_raw/module/reset.c.

| void ath5k_hw_set_rx_filter | ( | struct ath5k_hw * | ah, |

| u32 | filter | ||

| ) |

ath5k_hw_set_rx_filter - Set rx filter

: The &struct ath5k_hw : RX filter mask (see reg.h)

Sets RX filter register and also handles PHY error filter register on 5212 and newer chips so that we have proper PHY error reporting.

Definition at line 548 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| void ath5k_hw_set_rxdp | ( | struct ath5k_hw * | ah, |

| u32 | phys_addr | ||

| ) |

ath5k_hw_set_rxdp - Set RX Descriptor's address

: The &struct ath5k_hw : RX descriptor address

XXX: Should we check if rx is enabled before setting rxdp ?

Definition at line 97 of file linux_ks/hwi/ath5k_raw/module/dma.c.

| int ath5k_hw_set_slot_time | ( | struct ath5k_hw * | ah, |

| unsigned int | slot_time | ||

| ) |

Definition at line 534 of file linux_ks/hwi/ath5k_raw/module/qcu.c.

| void ath5k_hw_set_spur_mitigation_filter | ( | struct ath5k_hw * | ah, |

| struct ieee80211_channel * | channel | ||

| ) |

Definition at line 1412 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| void ath5k_hw_set_tsf64 | ( | struct ath5k_hw * | ah, |

| u64 | tsf64 | ||

| ) |

| int ath5k_hw_set_tx_queueprops | ( | struct ath5k_hw * | ah, |

| int | queue, | ||

| const struct ath5k_txq_info * | queue_info | ||

| ) |

Definition at line 42 of file linux_ks/hwi/ath5k_raw/module/qcu.c.

| int ath5k_hw_set_txdp | ( | struct ath5k_hw * | ah, |

| unsigned int | queue, | ||

| u32 | phys_addr | ||

| ) |

ath5k_hw_set_txdp - Set TX Descriptor's address for a specific queue

: The &struct ath5k_hw : The hw queue number

Set TX descriptor's address for a specific queue. For 5210 we ignore the queue number and we use tx queue type since we only have 2 queues so as above we use TXDP0 for normal data queue and TXDP1 for beacon queue. For newer chips with QCU/DCU we just set the corresponding TXDP register. Returns -EINVAL if queue type is invalid for 5210 and -EIO if queue is still active.

Definition at line 339 of file linux_ks/hwi/ath5k_raw/module/dma.c.

| int ath5k_hw_set_txpower_limit | ( | struct ath5k_hw * | ah, |

| u8 | txpower | ||

| ) |

Definition at line 3045 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| int ath5k_hw_setup_tx_queue | ( | struct ath5k_hw * | ah, |

| enum ath5k_tx_queue | queue_type, | ||

| struct ath5k_txq_info * | queue_info | ||

| ) |

Definition at line 66 of file linux_ks/hwi/ath5k_raw/module/qcu.c.

| void ath5k_hw_start_rx_dma | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_start_rx_dma - Start DMA receive

: The &struct ath5k_hw

Definition at line 49 of file linux_ks/hwi/ath5k_raw/module/dma.c.

| void ath5k_hw_start_rx_pcu | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_start_rx_pcu - Start RX engine

: The &struct ath5k_hw

Starts RX engine on PCU so that hw can process RXed frames (ACK etc).

NOTE: RX DMA should be already enabled using ath5k_hw_start_rx_dma TODO: Init ANI here

Definition at line 439 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| int ath5k_hw_start_tx_dma | ( | struct ath5k_hw * | ah, |

| unsigned int | queue | ||

| ) |

ath5k_hw_start_tx_dma - Start DMA transmit for a specific queue

: The &struct ath5k_hw : The hw queue number

Start DMA transmit for a specific queue and since 5210 doesn't have QCU/DCU, set up queue parameters for 5210 here based on queue type (one queue for normal data and one queue for beacons). For queue setup on newer chips check out qcu.c. Returns -EINVAL if queue number is out of range or if queue is already disabled.

NOTE: Must be called after setting up tx control descriptor for that queue (see below).

Definition at line 124 of file linux_ks/hwi/ath5k_raw/module/dma.c.

| int ath5k_hw_stop_rx_dma | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_stop_rx_dma - Stop DMA receive

: The &struct ath5k_hw

Definition at line 61 of file linux_ks/hwi/ath5k_raw/module/dma.c.

| void ath5k_hw_stop_rx_pcu | ( | struct ath5k_hw * | ah | ) |

at5k_hw_stop_rx_pcu - Stop RX engine

: The &struct ath5k_hw

Stops RX engine on PCU

TODO: Detach ANI here

Definition at line 454 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| int ath5k_hw_stop_tx_dma | ( | struct ath5k_hw * | ah, |

| unsigned int | queue | ||

| ) |

ath5k_hw_stop_tx_dma - Stop DMA transmit on a specific queue

: The &struct ath5k_hw : The hw queue number

Stop DMA transmit on a specific hw queue and drain queue so we don't have any pending frames. Returns -EBUSY if we still have pending frames, -EINVAL if queue number is out of range.

Definition at line 184 of file linux_ks/hwi/ath5k_raw/module/dma.c.

| int ath5k_hw_txpower | ( | struct ath5k_hw * | ah, |

| struct ieee80211_channel * | channel, | ||

| u8 | ee_mode, | ||

| u8 | txpower | ||

| ) |

Definition at line 2946 of file linux_ks/hwi/ath5k_raw/module/phy.c.

| void ath5k_hw_update_mib_counters | ( | struct ath5k_hw * | ah, |

| struct ieee80211_low_level_stats * | stats | ||

| ) |

ath5k_hw_update - Update mib counters (mac layer statistics)

: The &struct ath5k_hw : The &struct ieee80211_low_level_stats we use to track statistics on the driver

Reads MIB counters from PCU and updates sw statistics. Must be called after a MIB interrupt.

Definition at line 93 of file linux_ks/hwi/ath5k_raw/module/pcu.c.

| int ath5k_hw_update_tx_triglevel | ( | struct ath5k_hw * | ah, |

| bool | increase | ||

| ) |

ath5k_hw_update_tx_triglevel - Update tx trigger level

: The &struct ath5k_hw : Flag to force increase of trigger level

This function increases/decreases the tx trigger level for the tx fifo buffer (aka FIFO threshold) that is used to indicate when PCU flushes the buffer and transmits it's data. Lowering this results sending small frames more quickly but can lead to tx underruns, raising it a lot can result other problems (i think bmiss is related). Right now we start with the lowest possible (64Bytes) and if we get tx underrun we increase it using the increase flag. Returns -EIO if we have have reached maximum/minimum.

XXX: Link this with tx DMA size ? XXX: Use it to save interrupts ? TODO: Needs testing, i think it's related to bmiss...

Definition at line 398 of file linux_ks/hwi/ath5k_raw/module/dma.c.

| int ath5k_hw_write_initvals | ( | struct ath5k_hw * | ah, |

| u8 | mode, | ||

| bool | change_channel | ||

| ) |

Definition at line 1412 of file linux_ks/hwi/ath5k_raw/module/initvals.c.

| int ath5k_init_leds | ( | struct ath5k_softc * | sc | ) |

| void ath5k_led_enable | ( | struct ath5k_softc * | sc | ) |

| void ath5k_led_off | ( | struct ath5k_softc * | sc | ) |

| static int ath5k_pad_size | ( | int | hdrlen | ) | [inline, static] |

Definition at line 1339 of file linux_ks/hwi/ath5k_raw/module/ath5k.h.

| void ath5k_rfkill_hw_start | ( | struct ath5k_hw * | ah | ) |

| void ath5k_rfkill_hw_stop | ( | struct ath5k_hw * | ah | ) |

| void ath5k_unregister_leds | ( | struct ath5k_softc * | sc | ) |