Header file of SPI HAL module. More...

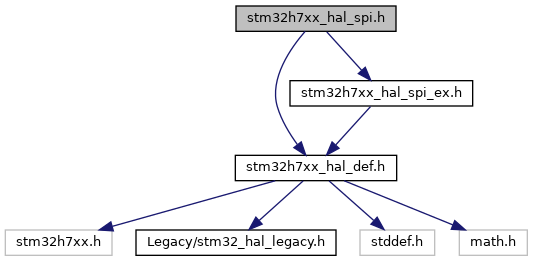

Include dependency graph for stm32h7xx_hal_spi.h:

Go to the source code of this file.

Classes | |

| struct | __SPI_HandleTypeDef |

| SPI handle Structure definition. More... | |

| struct | SPI_InitTypeDef |

| SPI Configuration Structure definition. More... | |

Macros | |

| #define | __HAL_SPI_CLEAR_CRCERRFLAG(__HANDLE__) SET_BIT((__HANDLE__)->Instance->IFCR , SPI_IFCR_CRCEC) |

| Clear the SPI CRCERR pending flag. More... | |

| #define | __HAL_SPI_CLEAR_EOTFLAG(__HANDLE__) SET_BIT((__HANDLE__)->Instance->IFCR , SPI_IFCR_EOTC) |

| Clear the SPI EOT pending flag. More... | |

| #define | __HAL_SPI_CLEAR_FREFLAG(__HANDLE__) SET_BIT((__HANDLE__)->Instance->IFCR , SPI_IFCR_TIFREC) |

| Clear the SPI FRE pending flag. More... | |

| #define | __HAL_SPI_CLEAR_MODFFLAG(__HANDLE__) SET_BIT((__HANDLE__)->Instance->IFCR , (uint32_t)(SPI_IFCR_MODFC)); |

| Clear the SPI MODF pending flag. More... | |

| #define | __HAL_SPI_CLEAR_OVRFLAG(__HANDLE__) SET_BIT((__HANDLE__)->Instance->IFCR , SPI_IFCR_OVRC) |

| Clear the SPI OVR pending flag. More... | |

| #define | __HAL_SPI_CLEAR_SUSPFLAG(__HANDLE__) SET_BIT((__HANDLE__)->Instance->IFCR , SPI_IFCR_SUSPC) |

| Clear the SPI SUSP pending flag. More... | |

| #define | __HAL_SPI_CLEAR_TSERFFLAG(__HANDLE__) SET_BIT((__HANDLE__)->Instance->IFCR , SPI_IFCR_TSERFC) |

| Clear the SPI TSERF pending flag. More... | |

| #define | __HAL_SPI_CLEAR_TXTFFLAG(__HANDLE__) SET_BIT((__HANDLE__)->Instance->IFCR , SPI_IFCR_TXTFC) |

| Clear the SPI UDR pending flag. More... | |

| #define | __HAL_SPI_CLEAR_UDRFLAG(__HANDLE__) SET_BIT((__HANDLE__)->Instance->IFCR , SPI_IFCR_UDRC) |

| Clear the SPI UDR pending flag. More... | |

| #define | __HAL_SPI_DISABLE(__HANDLE__) CLEAR_BIT((__HANDLE__)->Instance->CR1 , SPI_CR1_SPE) |

| Disable the SPI peripheral. More... | |

| #define | __HAL_SPI_DISABLE_IT(__HANDLE__, __INTERRUPT__) ((__HANDLE__)->Instance->IER &= (~(__INTERRUPT__))) |

| Disable the specified SPI interrupts. More... | |

| #define | __HAL_SPI_ENABLE(__HANDLE__) SET_BIT((__HANDLE__)->Instance->CR1 , SPI_CR1_SPE) |

| Enable the SPI peripheral. More... | |

| #define | __HAL_SPI_ENABLE_IT(__HANDLE__, __INTERRUPT__) ((__HANDLE__)->Instance->IER |= (__INTERRUPT__)) |

| Enable the specified SPI interrupts. More... | |

| #define | __HAL_SPI_GET_FLAG(__HANDLE__, __FLAG__) ((((__HANDLE__)->Instance->SR) & (__FLAG__)) == (__FLAG__)) |

| Check whether the specified SPI flag is set or not. More... | |

| #define | __HAL_SPI_GET_IT_SOURCE(__HANDLE__, __INTERRUPT__) ((((__HANDLE__)->Instance->IER & (__INTERRUPT__)) == (__INTERRUPT__)) ? SET : RESET) |

| Check whether the specified SPI interrupt source is enabled or not. More... | |

| #define | __HAL_SPI_RESET_HANDLE_STATE(__HANDLE__) ((__HANDLE__)->State = HAL_SPI_STATE_RESET) |

| Reset SPI handle state. More... | |

| #define | HAL_SPI_ERROR_ABORT (0x00000040UL) |

| #define | HAL_SPI_ERROR_CRC (0x00000002UL) |

| #define | HAL_SPI_ERROR_DMA (0x00000010UL) |

| #define | HAL_SPI_ERROR_FLAG (0x00000020UL) |

| #define | HAL_SPI_ERROR_FRE (0x00000008UL) |

| #define | HAL_SPI_ERROR_MODF (0x00000001UL) |

| #define | HAL_SPI_ERROR_NONE (0x00000000UL) |

| #define | HAL_SPI_ERROR_NOT_SUPPORTED (0x00000400UL) |

| #define | HAL_SPI_ERROR_OVR (0x00000004UL) |

| #define | HAL_SPI_ERROR_TIMEOUT (0x00000100UL) |

| #define | HAL_SPI_ERROR_UDR (0x00000080UL) |

| #define | HAL_SPI_ERROR_UNKNOW (0x00000200UL) |

| #define | IS_SPI_BAUDRATE_PRESCALER(PRESCALER) |

| #define | IS_SPI_CPHA(CPHA) |

| #define | IS_SPI_CPOL(CPOL) |

| #define | IS_SPI_CRC_CALCULATION(CALCULATION) |

| #define | IS_SPI_CRC_INITIALIZATION_PATTERN(PATTERN) |

| #define | IS_SPI_CRC_LENGTH(LENGTH) |

| #define | IS_SPI_CRC_POLYNOMIAL(POLYNOMIAL) ((POLYNOMIAL) >= 0x1UL) |

| #define | IS_SPI_DATASIZE(DATASIZE) |

| #define | IS_SPI_DIRECTION(MODE) |

| #define | IS_SPI_DIRECTION_2LINES(MODE) ((MODE) == SPI_DIRECTION_2LINES) |

| #define | IS_SPI_DIRECTION_2LINES_OR_1LINE_2LINES_RXONLY(MODE) |

| #define | IS_SPI_DIRECTION_2LINES_OR_1LINE_2LINES_TXONLY(MODE) |

| #define | IS_SPI_FIFOTHRESHOLD(THRESHOLD) |

| #define | IS_SPI_FIRST_BIT(BIT) |

| #define | IS_SPI_MODE(MODE) |

| #define | IS_SPI_NSS(NSS) |

| #define | IS_SPI_NSSP(NSSP) |

| #define | IS_SPI_TIMODE(MODE) |

| #define | IS_SPI_UNDERRUN_BEHAVIOUR(MODE) |

| #define | IS_SPI_UNDERRUN_DETECTION(MODE) |

| #define | SPI_1LINE_RX(__HANDLE__) CLEAR_BIT((__HANDLE__)->Instance->CR1 ,SPI_CR1_HDDIR) |

| Set the SPI receive-only mode. More... | |

| #define | SPI_1LINE_TX(__HANDLE__) SET_BIT((__HANDLE__)->Instance->CR1 , SPI_CR1_HDDIR) |

| Set the SPI transmit-only mode. More... | |

| #define | SPI_BAUDRATEPRESCALER_128 (0x60000000UL) |

| #define | SPI_BAUDRATEPRESCALER_16 (0x30000000UL) |

| #define | SPI_BAUDRATEPRESCALER_2 (0x00000000UL) |

| #define | SPI_BAUDRATEPRESCALER_256 (0x70000000UL) |

| #define | SPI_BAUDRATEPRESCALER_32 (0x40000000UL) |

| #define | SPI_BAUDRATEPRESCALER_4 (0x10000000UL) |

| #define | SPI_BAUDRATEPRESCALER_64 (0x50000000UL) |

| #define | SPI_BAUDRATEPRESCALER_8 (0x20000000UL) |

| #define | SPI_CRC_INITIALIZATION_ALL_ONE_PATTERN (0x00000001UL) |

| #define | SPI_CRC_INITIALIZATION_ALL_ZERO_PATTERN (0x00000000UL) |

| #define | SPI_CRC_LENGTH_10BIT (0x00090000UL) |

| #define | SPI_CRC_LENGTH_11BIT (0x000A0000UL) |

| #define | SPI_CRC_LENGTH_12BIT (0x000B0000UL) |

| #define | SPI_CRC_LENGTH_13BIT (0x000C0000UL) |

| #define | SPI_CRC_LENGTH_14BIT (0x000D0000UL) |

| #define | SPI_CRC_LENGTH_15BIT (0x000E0000UL) |

| #define | SPI_CRC_LENGTH_16BIT (0x000F0000UL) |

| #define | SPI_CRC_LENGTH_17BIT (0x00100000UL) |

| #define | SPI_CRC_LENGTH_18BIT (0x00110000UL) |

| #define | SPI_CRC_LENGTH_19BIT (0x00120000UL) |

| #define | SPI_CRC_LENGTH_20BIT (0x00130000UL) |

| #define | SPI_CRC_LENGTH_21BIT (0x00140000UL) |

| #define | SPI_CRC_LENGTH_22BIT (0x00150000UL) |

| #define | SPI_CRC_LENGTH_23BIT (0x00160000UL) |

| #define | SPI_CRC_LENGTH_24BIT (0x00170000UL) |

| #define | SPI_CRC_LENGTH_25BIT (0x00180000UL) |

| #define | SPI_CRC_LENGTH_26BIT (0x00190000UL) |

| #define | SPI_CRC_LENGTH_27BIT (0x001A0000UL) |

| #define | SPI_CRC_LENGTH_28BIT (0x001B0000UL) |

| #define | SPI_CRC_LENGTH_29BIT (0x001C0000UL) |

| #define | SPI_CRC_LENGTH_30BIT (0x001D0000UL) |

| #define | SPI_CRC_LENGTH_31BIT (0x001E0000UL) |

| #define | SPI_CRC_LENGTH_32BIT (0x001F0000UL) |

| #define | SPI_CRC_LENGTH_4BIT (0x00030000UL) |

| #define | SPI_CRC_LENGTH_5BIT (0x00040000UL) |

| #define | SPI_CRC_LENGTH_6BIT (0x00050000UL) |

| #define | SPI_CRC_LENGTH_7BIT (0x00060000UL) |

| #define | SPI_CRC_LENGTH_8BIT (0x00070000UL) |

| #define | SPI_CRC_LENGTH_9BIT (0x00080000UL) |

| #define | SPI_CRC_LENGTH_DATASIZE (0x00000000UL) |

| #define | SPI_CRCCALCULATION_DISABLE (0x00000000UL) |

| #define | SPI_CRCCALCULATION_ENABLE SPI_CFG1_CRCEN |

| #define | SPI_DATASIZE_10BIT (0x00000009UL) |

| #define | SPI_DATASIZE_11BIT (0x0000000AUL) |

| #define | SPI_DATASIZE_12BIT (0x0000000BUL) |

| #define | SPI_DATASIZE_13BIT (0x0000000CUL) |

| #define | SPI_DATASIZE_14BIT (0x0000000DUL) |

| #define | SPI_DATASIZE_15BIT (0x0000000EUL) |

| #define | SPI_DATASIZE_16BIT (0x0000000FUL) |

| #define | SPI_DATASIZE_17BIT (0x00000010UL) |

| #define | SPI_DATASIZE_18BIT (0x00000011UL) |

| #define | SPI_DATASIZE_19BIT (0x00000012UL) |

| #define | SPI_DATASIZE_20BIT (0x00000013UL) |

| #define | SPI_DATASIZE_21BIT (0x00000014UL) |

| #define | SPI_DATASIZE_22BIT (0x00000015UL) |

| #define | SPI_DATASIZE_23BIT (0x00000016UL) |

| #define | SPI_DATASIZE_24BIT (0x00000017UL) |

| #define | SPI_DATASIZE_25BIT (0x00000018UL) |

| #define | SPI_DATASIZE_26BIT (0x00000019UL) |

| #define | SPI_DATASIZE_27BIT (0x0000001AUL) |

| #define | SPI_DATASIZE_28BIT (0x0000001BUL) |

| #define | SPI_DATASIZE_29BIT (0x0000001CUL) |

| #define | SPI_DATASIZE_30BIT (0x0000001DUL) |

| #define | SPI_DATASIZE_31BIT (0x0000001EUL) |

| #define | SPI_DATASIZE_32BIT (0x0000001FUL) |

| #define | SPI_DATASIZE_4BIT (0x00000003UL) |

| #define | SPI_DATASIZE_5BIT (0x00000004UL) |

| #define | SPI_DATASIZE_6BIT (0x00000005UL) |

| #define | SPI_DATASIZE_7BIT (0x00000006UL) |

| #define | SPI_DATASIZE_8BIT (0x00000007UL) |

| #define | SPI_DATASIZE_9BIT (0x00000008UL) |

| #define | SPI_DIRECTION_1LINE SPI_CFG2_COMM |

| #define | SPI_DIRECTION_2LINES (0x00000000UL) |

| #define | SPI_DIRECTION_2LINES_RXONLY SPI_CFG2_COMM_1 |

| #define | SPI_DIRECTION_2LINES_TXONLY SPI_CFG2_COMM_0 |

| #define | SPI_FIFO_THRESHOLD_01DATA (0x00000000UL) |

| #define | SPI_FIFO_THRESHOLD_02DATA (0x00000020UL) |

| #define | SPI_FIFO_THRESHOLD_03DATA (0x00000040UL) |

| #define | SPI_FIFO_THRESHOLD_04DATA (0x00000060UL) |

| #define | SPI_FIFO_THRESHOLD_05DATA (0x00000080UL) |

| #define | SPI_FIFO_THRESHOLD_06DATA (0x000000A0UL) |

| #define | SPI_FIFO_THRESHOLD_07DATA (0x000000C0UL) |

| #define | SPI_FIFO_THRESHOLD_08DATA (0x000000E0UL) |

| #define | SPI_FIFO_THRESHOLD_09DATA (0x00000100UL) |

| #define | SPI_FIFO_THRESHOLD_10DATA (0x00000120UL) |

| #define | SPI_FIFO_THRESHOLD_11DATA (0x00000140UL) |

| #define | SPI_FIFO_THRESHOLD_12DATA (0x00000160UL) |

| #define | SPI_FIFO_THRESHOLD_13DATA (0x00000180UL) |

| #define | SPI_FIFO_THRESHOLD_14DATA (0x000001A0UL) |

| #define | SPI_FIFO_THRESHOLD_15DATA (0x000001C0UL) |

| #define | SPI_FIFO_THRESHOLD_16DATA (0x000001E0UL) |

| #define | SPI_FIRSTBIT_LSB SPI_CFG2_LSBFRST |

| #define | SPI_FIRSTBIT_MSB (0x00000000UL) |

| #define | SPI_FLAG_CRCERR SPI_SR_CRCE /* SPI Error flag : CRC error flag */ |

| #define | SPI_FLAG_DXP SPI_SR_DXP /* SPI status flag : Duplex Packet flag */ |

| #define | SPI_FLAG_EOT SPI_SR_EOT /* SPI status flag : End of transfer flag */ |

| #define | SPI_FLAG_FRE SPI_SR_TIFRE /* SPI Error flag : TI mode frame format error flag */ |

| #define | SPI_FLAG_FRLVL SPI_SR_RXPLVL /* SPI status flag : Fifo reception level flag */ |

| #define | SPI_FLAG_MODF SPI_SR_MODF /* SPI Error flag : Mode fault flag */ |

| #define | SPI_FLAG_OVR SPI_SR_OVR /* SPI Error flag : Overrun flag */ |

| #define | SPI_FLAG_RXP SPI_SR_RXP /* SPI status flag : Rx-Packet available flag */ |

| #define | SPI_FLAG_RXWNE SPI_SR_RXWNE /* SPI status flag : RxFIFO word not empty flag */ |

| #define | SPI_FLAG_SUSP SPI_SR_SUSP /* SPI status flag : Transfer suspend complete flag */ |

| #define | SPI_FLAG_TSERF SPI_SR_TSERF /* SPI status flag : Additional number of data reloaded flag */ |

| #define | SPI_FLAG_TXC SPI_SR_TXC /* SPI status flag : TxFIFO transmission complete flag */ |

| #define | SPI_FLAG_TXP SPI_SR_TXP /* SPI status flag : Tx-Packet space available flag */ |

| #define | SPI_FLAG_TXTF SPI_SR_TXTF /* SPI status flag : Transmission Transfer Filled flag */ |

| #define | SPI_FLAG_UDR SPI_SR_UDR /* SPI Error flag : Underrun flag */ |

| #define | SPI_HIGHEND_FIFO_SIZE 16UL |

| #define | SPI_IO_SWAP_DISABLE (0x00000000UL) |

| #define | SPI_IO_SWAP_ENABLE SPI_CFG2_IOSWP |

| #define | SPI_IT_CRCERR SPI_IER_CRCEIE |

| #define | SPI_IT_DXP SPI_IER_DXPIE |

| #define | SPI_IT_EOT SPI_IER_EOTIE |

| #define | SPI_IT_ERR (SPI_IT_UDR | SPI_IT_OVR | SPI_IT_FRE | SPI_IT_MODF | SPI_IT_CRCERR) |

| #define | SPI_IT_FRE SPI_IER_TIFREIE |

| #define | SPI_IT_MODF SPI_IER_MODFIE |

| #define | SPI_IT_OVR SPI_IER_OVRIE |

| #define | SPI_IT_RXP SPI_IER_RXPIE |

| #define | SPI_IT_TSERF SPI_IER_TSERFIE |

| #define | SPI_IT_TXP SPI_IER_TXPIE |

| #define | SPI_IT_TXTF SPI_IER_TXTFIE |

| #define | SPI_IT_UDR SPI_IER_UDRIE |

| #define | SPI_LOWEND_FIFO_SIZE 8UL |

| #define | SPI_MASTER_INTERDATA_IDLENESS_00CYCLE (0x00000000UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_01CYCLE (0x00000010UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_02CYCLE (0x00000020UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_03CYCLE (0x00000030UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_04CYCLE (0x00000040UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_05CYCLE (0x00000050UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_06CYCLE (0x00000060UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_07CYCLE (0x00000070UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_08CYCLE (0x00000080UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_09CYCLE (0x00000090UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_10CYCLE (0x000000A0UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_11CYCLE (0x000000B0UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_12CYCLE (0x000000C0UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_13CYCLE (0x000000D0UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_14CYCLE (0x000000E0UL) |

| #define | SPI_MASTER_INTERDATA_IDLENESS_15CYCLE (0x000000F0UL) |

| #define | SPI_MASTER_KEEP_IO_STATE_DISABLE (0x00000000UL) |

| #define | SPI_MASTER_KEEP_IO_STATE_ENABLE SPI_CFG2_AFCNTR |

| #define | SPI_MASTER_RX_AUTOSUSP_DISABLE (0x00000000UL) |

| #define | SPI_MASTER_RX_AUTOSUSP_ENABLE SPI_CR1_MASRX |

| #define | SPI_MASTER_SS_IDLENESS_00CYCLE (0x00000000UL) |

| #define | SPI_MASTER_SS_IDLENESS_01CYCLE (0x00000001UL) |

| #define | SPI_MASTER_SS_IDLENESS_02CYCLE (0x00000002UL) |

| #define | SPI_MASTER_SS_IDLENESS_03CYCLE (0x00000003UL) |

| #define | SPI_MASTER_SS_IDLENESS_04CYCLE (0x00000004UL) |

| #define | SPI_MASTER_SS_IDLENESS_05CYCLE (0x00000005UL) |

| #define | SPI_MASTER_SS_IDLENESS_06CYCLE (0x00000006UL) |

| #define | SPI_MASTER_SS_IDLENESS_07CYCLE (0x00000007UL) |

| #define | SPI_MASTER_SS_IDLENESS_08CYCLE (0x00000008UL) |

| #define | SPI_MASTER_SS_IDLENESS_09CYCLE (0x00000009UL) |

| #define | SPI_MASTER_SS_IDLENESS_10CYCLE (0x0000000AUL) |

| #define | SPI_MASTER_SS_IDLENESS_11CYCLE (0x0000000BUL) |

| #define | SPI_MASTER_SS_IDLENESS_12CYCLE (0x0000000CUL) |

| #define | SPI_MASTER_SS_IDLENESS_13CYCLE (0x0000000DUL) |

| #define | SPI_MASTER_SS_IDLENESS_14CYCLE (0x0000000EUL) |

| #define | SPI_MASTER_SS_IDLENESS_15CYCLE (0x0000000FUL) |

| #define | SPI_MODE_MASTER SPI_CFG2_MASTER |

| #define | SPI_MODE_SLAVE (0x00000000UL) |

| #define | SPI_NSS_HARD_INPUT (0x00000000UL) |

| #define | SPI_NSS_HARD_OUTPUT SPI_CFG2_SSOE |

| #define | SPI_NSS_POLARITY_HIGH SPI_CFG2_SSIOP |

| #define | SPI_NSS_POLARITY_LOW (0x00000000UL) |

| #define | SPI_NSS_PULSE_DISABLE (0x00000000UL) |

| #define | SPI_NSS_PULSE_ENABLE SPI_CFG2_SSOM |

| #define | SPI_NSS_SOFT SPI_CFG2_SSM |

| #define | SPI_PHASE_1EDGE (0x00000000UL) |

| #define | SPI_PHASE_2EDGE SPI_CFG2_CPHA |

| #define | SPI_POLARITY_HIGH SPI_CFG2_CPOL |

| #define | SPI_POLARITY_LOW (0x00000000UL) |

| #define | SPI_RX_FIFO_0PACKET (0x00000000UL) /* 0 or multiple of 4 packets available in the RxFIFO */ |

| #define | SPI_RX_FIFO_1PACKET (SPI_SR_RXPLVL_0) |

| #define | SPI_RX_FIFO_2PACKET (SPI_SR_RXPLVL_1) |

| #define | SPI_RX_FIFO_3PACKET (SPI_SR_RXPLVL_1 | SPI_SR_RXPLVL_0) |

| #define | SPI_TIMODE_DISABLE (0x00000000UL) |

| #define | SPI_TIMODE_ENABLE SPI_CFG2_SP_0 |

| #define | SPI_UNDERRUN_BEHAV_LAST_RECEIVED SPI_CFG1_UDRCFG_0 |

| #define | SPI_UNDERRUN_BEHAV_LAST_TRANSMITTED SPI_CFG1_UDRCFG_1 |

| #define | SPI_UNDERRUN_BEHAV_REGISTER_PATTERN (0x00000000UL) |

| #define | SPI_UNDERRUN_DETECT_BEGIN_ACTIVE_NSS SPI_CFG1_UDRDET_1 |

| #define | SPI_UNDERRUN_DETECT_BEGIN_DATA_FRAME (0x00000000UL) |

| #define | SPI_UNDERRUN_DETECT_END_DATA_FRAME SPI_CFG1_UDRDET_0 |

Typedefs | |

| typedef struct __SPI_HandleTypeDef | SPI_HandleTypeDef |

| SPI handle Structure definition. More... | |

Detailed Description

Header file of SPI HAL module.

- Attention

© Copyright (c) 2017 STMicroelectronics. All rights reserved.

This software component is licensed by ST under BSD 3-Clause license, the "License"; You may not use this file except in compliance with the License. You may obtain a copy of the License at: opensource.org/licenses/BSD-3-Clause

Definition in file stm32h7xx_hal_spi.h.