Header file of FMC HAL module. More...

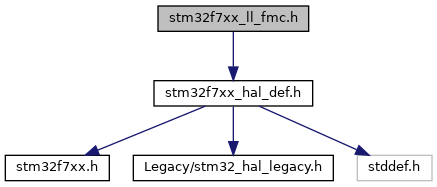

#include "stm32f7xx_hal_def.h"

Include dependency graph for stm32f7xx_ll_fmc.h:

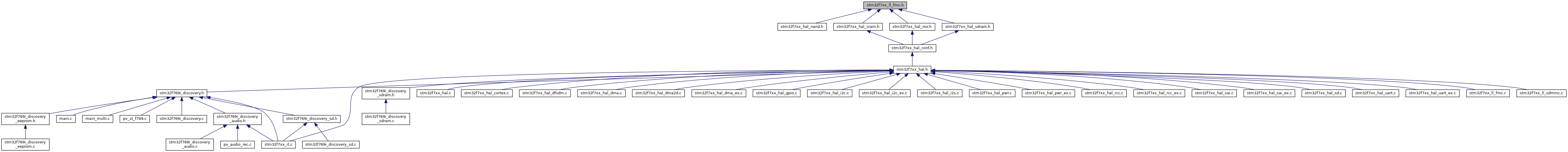

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | FMC_NAND_InitTypeDef |

| FMC NAND Configuration Structure definition More... | |

| struct | FMC_NAND_PCC_TimingTypeDef |

| FMC NAND Timing parameters structure definition. More... | |

| struct | FMC_NORSRAM_InitTypeDef |

| FMC NORSRAM Configuration Structure definition. More... | |

| struct | FMC_NORSRAM_TimingTypeDef |

| FMC NORSRAM Timing parameters structure definition More... | |

| struct | FMC_SDRAM_CommandTypeDef |

| SDRAM command parameters structure definition. More... | |

| struct | FMC_SDRAM_InitTypeDef |

| FMC SDRAM Configuration Structure definition More... | |

| struct | FMC_SDRAM_TimingTypeDef |

| FMC SDRAM Timing parameters structure definition. More... | |

Macros | |

| #define | __FMC_NAND_CLEAR_FLAG(__INSTANCE__, __FLAG__) ((__INSTANCE__)->SR &= ~(__FLAG__)) |

| Clear flag status of the NAND device. More... | |

| #define | __FMC_NAND_DISABLE(__INSTANCE__) ((__INSTANCE__)->PCR &= ~FMC_PCR_PBKEN) |

| Disable the NAND device access. More... | |

| #define | __FMC_NAND_DISABLE_IT(__INSTANCE__, __INTERRUPT__) ((__INSTANCE__)->SR &= ~(__INTERRUPT__)) |

| Disable the NAND device interrupt. More... | |

| #define | __FMC_NAND_ENABLE(__INSTANCE__) ((__INSTANCE__)->PCR |= FMC_PCR_PBKEN) |

| Enable the NAND device access. More... | |

| #define | __FMC_NAND_ENABLE_IT(__INSTANCE__, __INTERRUPT__) ((__INSTANCE__)->SR |= (__INTERRUPT__)) |

| Enable the NAND device interrupt. More... | |

| #define | __FMC_NAND_GET_FLAG(__INSTANCE__, __BANK__, __FLAG__) (((__INSTANCE__)->SR &(__FLAG__)) == (__FLAG__)) |

| Get flag status of the NAND device. More... | |

| #define | __FMC_NORSRAM_DISABLE(__INSTANCE__, __BANK__) ((__INSTANCE__)->BTCR[(__BANK__)] &= ~FMC_BCR1_MBKEN) |

| Disable the NORSRAM device access. More... | |

| #define | __FMC_NORSRAM_ENABLE(__INSTANCE__, __BANK__) ((__INSTANCE__)->BTCR[(__BANK__)] |= FMC_BCR1_MBKEN) |

| Enable the NORSRAM device access. More... | |

| #define | __FMC_SDRAM_CLEAR_FLAG(__INSTANCE__, __FLAG__) ((__INSTANCE__)->SDRTR |= (__FLAG__)) |

| Clear flag status of the SDRAM device. More... | |

| #define | __FMC_SDRAM_DISABLE_IT(__INSTANCE__, __INTERRUPT__) ((__INSTANCE__)->SDRTR &= ~(__INTERRUPT__)) |

| Disable the SDRAM device interrupt. More... | |

| #define | __FMC_SDRAM_ENABLE_IT(__INSTANCE__, __INTERRUPT__) ((__INSTANCE__)->SDRTR |= (__INTERRUPT__)) |

| Enable the SDRAM device interrupt. More... | |

| #define | __FMC_SDRAM_GET_FLAG(__INSTANCE__, __FLAG__) (((__INSTANCE__)->SDSR &(__FLAG__)) == (__FLAG__)) |

| Get flag status of the SDRAM device. More... | |

| #define | FMC_ACCESS_MODE_A ((uint32_t)0x00000000U) |

| #define | FMC_ACCESS_MODE_B ((uint32_t)0x10000000U) |

| #define | FMC_ACCESS_MODE_C ((uint32_t)0x20000000U) |

| #define | FMC_ACCESS_MODE_D ((uint32_t)0x30000000) |

| #define | FMC_ASYNCHRONOUS_WAIT_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_ASYNCHRONOUS_WAIT_ENABLE ((uint32_t)0x00008000U) |

| #define | FMC_BURST_ACCESS_MODE_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_BURST_ACCESS_MODE_ENABLE ((uint32_t)0x00000100U) |

| #define | FMC_CONTINUOUS_CLOCK_SYNC_ASYNC ((uint32_t)0x00100000U) |

| #define | FMC_CONTINUOUS_CLOCK_SYNC_ONLY ((uint32_t)0x00000000U) |

| #define | FMC_DATA_ADDRESS_MUX_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_DATA_ADDRESS_MUX_ENABLE ((uint32_t)0x00000002U) |

| #define | FMC_EXTENDED_MODE_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_EXTENDED_MODE_ENABLE ((uint32_t)0x00004000U) |

| #define | FMC_FLAG_FALLING_EDGE ((uint32_t)0x00000004U) |

| #define | FMC_FLAG_FEMPT ((uint32_t)0x00000040U) |

| #define | FMC_FLAG_LEVEL ((uint32_t)0x00000002U) |

| #define | FMC_FLAG_RISING_EDGE ((uint32_t)0x00000001U) |

| #define | FMC_IT_FALLING_EDGE ((uint32_t)0x00000020U) |

| #define | FMC_IT_LEVEL ((uint32_t)0x00000010U) |

| #define | FMC_IT_REFRESH_ERROR ((uint32_t)0x00004000U) |

| #define | FMC_IT_RISING_EDGE ((uint32_t)0x00000008U) |

| #define | FMC_MEMORY_TYPE_NOR ((uint32_t)0x00000008U) |

| #define | FMC_MEMORY_TYPE_PSRAM ((uint32_t)0x00000004U) |

| #define | FMC_MEMORY_TYPE_SRAM ((uint32_t)0x00000000U) |

| #define | FMC_NAND_BANK3 ((uint32_t)0x00000100U) |

| #define | FMC_NAND_DEVICE FMC_Bank3 |

| #define | FMC_NAND_ECC_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_NAND_ECC_ENABLE ((uint32_t)0x00000040U) |

| #define | FMC_NAND_ECC_PAGE_SIZE_1024BYTE ((uint32_t)0x00040000U) |

| #define | FMC_NAND_ECC_PAGE_SIZE_2048BYTE ((uint32_t)0x00060000U) |

| #define | FMC_NAND_ECC_PAGE_SIZE_256BYTE ((uint32_t)0x00000000U) |

| #define | FMC_NAND_ECC_PAGE_SIZE_4096BYTE ((uint32_t)0x00080000U) |

| #define | FMC_NAND_ECC_PAGE_SIZE_512BYTE ((uint32_t)0x00020000U) |

| #define | FMC_NAND_ECC_PAGE_SIZE_8192BYTE ((uint32_t)0x000A0000U) |

| #define | FMC_NAND_MEM_BUS_WIDTH_16 ((uint32_t)0x00000010U) |

| #define | FMC_NAND_MEM_BUS_WIDTH_8 ((uint32_t)0x00000000U) |

| #define | FMC_NAND_TypeDef FMC_Bank3_TypeDef |

| #define | FMC_NAND_WAIT_FEATURE_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_NAND_WAIT_FEATURE_ENABLE ((uint32_t)0x00000002U) |

| #define | FMC_NORSRAM_BANK1 ((uint32_t)0x00000000U) |

| #define | FMC_NORSRAM_BANK2 ((uint32_t)0x00000002U) |

| #define | FMC_NORSRAM_BANK3 ((uint32_t)0x00000004U) |

| #define | FMC_NORSRAM_BANK4 ((uint32_t)0x00000006U) |

| #define | FMC_NORSRAM_DEVICE FMC_Bank1 |

| #define | FMC_NORSRAM_EXTENDED_DEVICE FMC_Bank1E |

| #define | FMC_NORSRAM_EXTENDED_TypeDef FMC_Bank1E_TypeDef |

| #define | FMC_NORSRAM_FLASH_ACCESS_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_NORSRAM_FLASH_ACCESS_ENABLE ((uint32_t)0x00000040U) |

| #define | FMC_NORSRAM_MEM_BUS_WIDTH_16 ((uint32_t)0x00000010U) |

| #define | FMC_NORSRAM_MEM_BUS_WIDTH_32 ((uint32_t)0x00000020U) |

| #define | FMC_NORSRAM_MEM_BUS_WIDTH_8 ((uint32_t)0x00000000U) |

| #define | FMC_NORSRAM_TypeDef FMC_Bank1_TypeDef |

| #define | FMC_PAGE_SIZE_1024 ((uint32_t)FMC_BCR1_CPSIZE_2) |

| #define | FMC_PAGE_SIZE_128 ((uint32_t)FMC_BCR1_CPSIZE_0) |

| #define | FMC_PAGE_SIZE_256 ((uint32_t)FMC_BCR1_CPSIZE_1) |

| #define | FMC_PAGE_SIZE_512 ((uint32_t)(FMC_BCR1_CPSIZE_0 | FMC_BCR1_CPSIZE_1)) |

| #define | FMC_PAGE_SIZE_NONE ((uint32_t)0x00000000U) |

| #define | FMC_PCR_MEMORY_TYPE_NAND ((uint32_t)0x00000008U) |

| #define | FMC_SDRAM_BANK1 ((uint32_t)0x00000000U) |

| #define | FMC_SDRAM_BANK2 ((uint32_t)0x00000001U) |

| #define | FMC_SDRAM_CAS_LATENCY_1 ((uint32_t)0x00000080U) |

| #define | FMC_SDRAM_CAS_LATENCY_2 ((uint32_t)0x00000100U) |

| #define | FMC_SDRAM_CAS_LATENCY_3 ((uint32_t)0x00000180) |

| #define | FMC_SDRAM_CLOCK_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_SDRAM_CLOCK_PERIOD_2 ((uint32_t)0x00000800U) |

| #define | FMC_SDRAM_CLOCK_PERIOD_3 ((uint32_t)0x00000C00) |

| #define | FMC_SDRAM_CMD_AUTOREFRESH_MODE ((uint32_t)0x00000003U) |

| #define | FMC_SDRAM_CMD_CLK_ENABLE ((uint32_t)0x00000001U) |

| #define | FMC_SDRAM_CMD_LOAD_MODE ((uint32_t)0x00000004U) |

| #define | FMC_SDRAM_CMD_NORMAL_MODE ((uint32_t)0x00000000U) |

| #define | FMC_SDRAM_CMD_PALL ((uint32_t)0x00000002U) |

| #define | FMC_SDRAM_CMD_POWERDOWN_MODE ((uint32_t)0x00000006U) |

| #define | FMC_SDRAM_CMD_SELFREFRESH_MODE ((uint32_t)0x00000005U) |

| #define | FMC_SDRAM_CMD_TARGET_BANK1 FMC_SDCMR_CTB1 |

| #define | FMC_SDRAM_CMD_TARGET_BANK1_2 ((uint32_t)0x00000018U) |

| #define | FMC_SDRAM_CMD_TARGET_BANK2 FMC_SDCMR_CTB2 |

| #define | FMC_SDRAM_COLUMN_BITS_NUM_10 ((uint32_t)0x00000002U) |

| #define | FMC_SDRAM_COLUMN_BITS_NUM_11 ((uint32_t)0x00000003U) |

| #define | FMC_SDRAM_COLUMN_BITS_NUM_8 ((uint32_t)0x00000000U) |

| #define | FMC_SDRAM_COLUMN_BITS_NUM_9 ((uint32_t)0x00000001U) |

| #define | FMC_SDRAM_DEVICE FMC_Bank5_6 |

| #define | FMC_SDRAM_FLAG_BUSY FMC_SDSR_BUSY |

| #define | FMC_SDRAM_FLAG_REFRESH_ERROR FMC_SDRTR_CRE |

| #define | FMC_SDRAM_FLAG_REFRESH_IT FMC_SDSR_RE |

| #define | FMC_SDRAM_INTERN_BANKS_NUM_2 ((uint32_t)0x00000000U) |

| #define | FMC_SDRAM_INTERN_BANKS_NUM_4 ((uint32_t)0x00000040U) |

| #define | FMC_SDRAM_MEM_BUS_WIDTH_16 ((uint32_t)0x00000010U) |

| #define | FMC_SDRAM_MEM_BUS_WIDTH_32 ((uint32_t)0x00000020U) |

| #define | FMC_SDRAM_MEM_BUS_WIDTH_8 ((uint32_t)0x00000000U) |

| #define | FMC_SDRAM_NORMAL_MODE ((uint32_t)0x00000000U) |

| #define | FMC_SDRAM_POWER_DOWN_MODE FMC_SDSR_MODES1_1 |

| #define | FMC_SDRAM_RBURST_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_SDRAM_RBURST_ENABLE ((uint32_t)0x00001000U) |

| #define | FMC_SDRAM_ROW_BITS_NUM_11 ((uint32_t)0x00000000U) |

| #define | FMC_SDRAM_ROW_BITS_NUM_12 ((uint32_t)0x00000004U) |

| #define | FMC_SDRAM_ROW_BITS_NUM_13 ((uint32_t)0x00000008U) |

| #define | FMC_SDRAM_RPIPE_DELAY_0 ((uint32_t)0x00000000U) |

| #define | FMC_SDRAM_RPIPE_DELAY_1 ((uint32_t)0x00002000U) |

| #define | FMC_SDRAM_RPIPE_DELAY_2 ((uint32_t)0x00004000U) |

| #define | FMC_SDRAM_SELF_REFRESH_MODE FMC_SDSR_MODES1_0 |

| #define | FMC_SDRAM_TypeDef FMC_Bank5_6_TypeDef |

| #define | FMC_SDRAM_WRITE_PROTECTION_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_SDRAM_WRITE_PROTECTION_ENABLE ((uint32_t)0x00000200U) |

| #define | FMC_WAIT_SIGNAL_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_WAIT_SIGNAL_ENABLE ((uint32_t)0x00002000U) |

| #define | FMC_WAIT_SIGNAL_POLARITY_HIGH ((uint32_t)0x00000200U) |

| #define | FMC_WAIT_SIGNAL_POLARITY_LOW ((uint32_t)0x00000000U) |

| #define | FMC_WAIT_TIMING_BEFORE_WS ((uint32_t)0x00000000U) |

| #define | FMC_WAIT_TIMING_DURING_WS ((uint32_t)0x00000800U) |

| #define | FMC_WRITE_BURST_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_WRITE_BURST_ENABLE ((uint32_t)0x00080000U) |

| #define | FMC_WRITE_FIFO_DISABLE ((uint32_t)FMC_BCR1_WFDIS) |

| #define | FMC_WRITE_FIFO_ENABLE ((uint32_t)0x00000000U) |

| #define | FMC_WRITE_OPERATION_DISABLE ((uint32_t)0x00000000U) |

| #define | FMC_WRITE_OPERATION_ENABLE ((uint32_t)0x00001000U) |

| #define | IS_FMC_ACCESS_MODE(__MODE__) |

| #define | IS_FMC_ADDRESS_HOLD_TIME(__TIME__) (((__TIME__) > 0) && ((__TIME__) <= 15)) |

| #define | IS_FMC_ADDRESS_SETUP_TIME(__TIME__) ((__TIME__) <= 15) |

| #define | IS_FMC_ASYNWAIT(__STATE__) |

| #define | IS_FMC_AUTOREFRESH_NUMBER(__NUMBER__) (((__NUMBER__) > 0) && ((__NUMBER__) <= 16)) |

| #define | IS_FMC_BURSTMODE(__STATE__) |

| #define | IS_FMC_CAS_LATENCY(LATENCY) |

| #define | IS_FMC_CLK_DIV(DIV) (((DIV) > 1) && ((DIV) <= 16)) |

| #define | IS_FMC_COLUMNBITS_NUMBER(COLUMN) |

| #define | IS_FMC_COMMAND_MODE(__COMMAND__) |

| #define | IS_FMC_COMMAND_TARGET(__TARGET__) |

| #define | IS_FMC_CONTINOUS_CLOCK(CCLOCK) |

| #define | IS_FMC_DATA_LATENCY(__LATENCY__) (((__LATENCY__) > 1) && ((__LATENCY__) <= 17)) |

| #define | IS_FMC_DATASETUP_TIME(__TIME__) (((__TIME__) > 0) && ((__TIME__) <= 255)) |

| #define | IS_FMC_ECC_STATE(STATE) |

| #define | IS_FMC_ECCPAGE_SIZE(SIZE) |

| #define | IS_FMC_EXITSELFREFRESH_DELAY(__DELAY__) (((__DELAY__) > 0) && ((__DELAY__) <= 16)) |

| #define | IS_FMC_EXTENDED_MODE(__MODE__) |

| #define | IS_FMC_HIZ_TIME(TIME) ((TIME) <= 254) |

| #define | IS_FMC_HOLD_TIME(TIME) ((TIME) <= 254) |

| #define | IS_FMC_INTERNALBANK_NUMBER(NUMBER) |

| #define | IS_FMC_LOADTOACTIVE_DELAY(__DELAY__) (((__DELAY__) > 0) && ((__DELAY__) <= 16)) |

| #define | IS_FMC_MEMORY(__MEMORY__) |

| #define | IS_FMC_MODE_REGISTER(__CONTENT__) ((__CONTENT__) <= 8191) |

| #define | IS_FMC_MUX(__MUX__) |

| #define | IS_FMC_NAND_BANK(BANK) ((BANK) == FMC_NAND_BANK3) |

| #define | IS_FMC_NAND_DEVICE(__INSTANCE__) ((__INSTANCE__) == FMC_NAND_DEVICE) |

| #define | IS_FMC_NAND_MEMORY_WIDTH(WIDTH) |

| #define | IS_FMC_NORSRAM_BANK(BANK) |

| #define | IS_FMC_NORSRAM_DEVICE(__INSTANCE__) ((__INSTANCE__) == FMC_NORSRAM_DEVICE) |

| #define | IS_FMC_NORSRAM_EXTENDED_DEVICE(__INSTANCE__) ((__INSTANCE__) == FMC_NORSRAM_EXTENDED_DEVICE) |

| #define | IS_FMC_NORSRAM_MEMORY_WIDTH(__WIDTH__) |

| #define | IS_FMC_PAGESIZE(__SIZE__) |

| #define | IS_FMC_RCD_DELAY(__DELAY__) (((__DELAY__) > 0) && ((__DELAY__) <= 16)) |

| #define | IS_FMC_READ_BURST(__RBURST__) |

| #define | IS_FMC_READPIPE_DELAY(__DELAY__) |

| #define | IS_FMC_REFRESH_RATE(__RATE__) ((__RATE__) <= 8191) |

| #define | IS_FMC_ROWBITS_NUMBER(ROW) |

| #define | IS_FMC_ROWCYCLE_DELAY(__DELAY__) (((__DELAY__) > 0) && ((__DELAY__) <= 16)) |

| #define | IS_FMC_RP_DELAY(__DELAY__) (((__DELAY__) > 0) && ((__DELAY__) <= 16)) |

| #define | IS_FMC_SDCLOCK_PERIOD(__PERIOD__) |

| #define | IS_FMC_SDMEMORY_WIDTH(WIDTH) |

| #define | IS_FMC_SDRAM_BANK(BANK) |

| #define | IS_FMC_SDRAM_DEVICE(__INSTANCE__) ((__INSTANCE__) == FMC_SDRAM_DEVICE) |

| #define | IS_FMC_SELFREFRESH_TIME(__TIME__) (((__TIME__) > 0) && ((__TIME__) <= 16)) |

| #define | IS_FMC_SETUP_TIME(TIME) ((TIME) <= 254) |

| #define | IS_FMC_TAR_TIME(TIME) ((TIME) <= 255) |

| #define | IS_FMC_TCLR_TIME(__TIME__) ((__TIME__) <= 255) |

| #define | IS_FMC_TURNAROUND_TIME(__TIME__) ((__TIME__) <= 15) |

| #define | IS_FMC_WAIT_FEATURE(FEATURE) |

| #define | IS_FMC_WAIT_POLARITY(__POLARITY__) |

| #define | IS_FMC_WAIT_SIGNAL_ACTIVE(__ACTIVE__) |

| #define | IS_FMC_WAIT_TIME(TIME) ((TIME) <= 254) |

| #define | IS_FMC_WAITE_SIGNAL(__SIGNAL__) |

| #define | IS_FMC_WRITE_BURST(__BURST__) |

| #define | IS_FMC_WRITE_FIFO(__FIFO__) |

| #define | IS_FMC_WRITE_OPERATION(__OPERATION__) |

| #define | IS_FMC_WRITE_PROTECTION(__WRITE__) |

| #define | IS_FMC_WRITE_RECOVERY_TIME(__TIME__) (((__TIME__) > 0) && ((__TIME__) <= 16)) |

Detailed Description

Header file of FMC HAL module.

- Attention

© Copyright (c) 2017 STMicroelectronics. All rights reserved.

This software component is licensed by ST under BSD 3-Clause license, the "License"; You may not use this file except in compliance with the License. You may obtain a copy of the License at: opensource.org/licenses/BSD-3-Clause

Definition in file stm32f7xx_ll_fmc.h.