CMSIS STM32F469xx Device Peripheral Access Layer Header File. More...

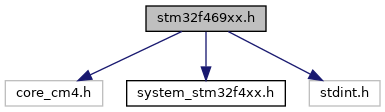

Include dependency graph for stm32f469xx.h:

Go to the source code of this file.

Classes | |

| struct | ADC_Common_TypeDef |

| struct | ADC_TypeDef |

| Analog to Digital Converter More... | |

| struct | CAN_FIFOMailBox_TypeDef |

| Controller Area Network FIFOMailBox. More... | |

| struct | CAN_FilterRegister_TypeDef |

| Controller Area Network FilterRegister. More... | |

| struct | CAN_TxMailBox_TypeDef |

| Controller Area Network TxMailBox. More... | |

| struct | CAN_TypeDef |

| Controller Area Network. More... | |

| struct | CRC_TypeDef |

| CRC calculation unit. More... | |

| struct | DAC_TypeDef |

| Digital to Analog Converter. More... | |

| struct | DBGMCU_TypeDef |

| Debug MCU. More... | |

| struct | DCMI_TypeDef |

| DCMI. More... | |

| struct | DMA2D_TypeDef |

| DMA2D Controller. More... | |

| struct | DMA_Stream_TypeDef |

| DMA Controller. More... | |

| struct | DMA_TypeDef |

| struct | DSI_TypeDef |

| DSI Controller. More... | |

| struct | ETH_TypeDef |

| Ethernet MAC. More... | |

| struct | EXTI_TypeDef |

| External Interrupt/Event Controller. More... | |

| struct | FLASH_TypeDef |

| FLASH Registers. More... | |

| struct | FMC_Bank1_TypeDef |

| Flexible Memory Controller. More... | |

| struct | FMC_Bank1E_TypeDef |

| Flexible Memory Controller Bank1E. More... | |

| struct | FMC_Bank3_TypeDef |

| Flexible Memory Controller Bank3. More... | |

| struct | FMC_Bank5_6_TypeDef |

| Flexible Memory Controller Bank5_6. More... | |

| struct | GPIO_TypeDef |

| General Purpose I/O. More... | |

| struct | I2C_TypeDef |

| Inter-integrated Circuit Interface. More... | |

| struct | IWDG_TypeDef |

| Independent WATCHDOG. More... | |

| struct | LTDC_Layer_TypeDef |

| LCD-TFT Display layer x Controller. More... | |

| struct | LTDC_TypeDef |

| LCD-TFT Display Controller. More... | |

| struct | PWR_TypeDef |

| Power Control. More... | |

| struct | QUADSPI_TypeDef |

| QUAD Serial Peripheral Interface. More... | |

| struct | RCC_TypeDef |

| Reset and Clock Control. More... | |

| struct | RNG_TypeDef |

| RNG. More... | |

| struct | RTC_TypeDef |

| Real-Time Clock. More... | |

| struct | SAI_Block_TypeDef |

| struct | SAI_TypeDef |

| Serial Audio Interface. More... | |

| struct | SDIO_TypeDef |

| SD host Interface. More... | |

| struct | SPI_TypeDef |

| Serial Peripheral Interface. More... | |

| struct | SYSCFG_TypeDef |

| System configuration controller. More... | |

| struct | TIM_TypeDef |

| TIM. More... | |

| struct | USART_TypeDef |

| Universal Synchronous Asynchronous Receiver Transmitter. More... | |

| struct | USB_OTG_DeviceTypeDef |

| USB_OTG_device_Registers. More... | |

| struct | USB_OTG_GlobalTypeDef |

| USB_OTG_Core_Registers. More... | |

| struct | USB_OTG_HostChannelTypeDef |

| USB_OTG_Host_Channel_Specific_Registers. More... | |

| struct | USB_OTG_HostTypeDef |

| USB_OTG_Host_Mode_Register_Structures. More... | |

| struct | USB_OTG_INEndpointTypeDef |

| USB_OTG_IN_Endpoint-Specific_Register. More... | |

| struct | USB_OTG_OUTEndpointTypeDef |

| USB_OTG_OUT_Endpoint-Specific_Registers. More... | |

| struct | WWDG_TypeDef |

| Window WATCHDOG. More... | |

Detailed Description

CMSIS STM32F469xx Device Peripheral Access Layer Header File.

- Attention

© Copyright (c) 2017 STMicroelectronics. All rights reserved.

This software component is licensed by ST under BSD 3-Clause license, the "License"; You may not use this file except in compliance with the License. You may obtain a copy of the License at: opensource.org/licenses/BSD-3-Clause

Definition in file stm32f469xx.h.