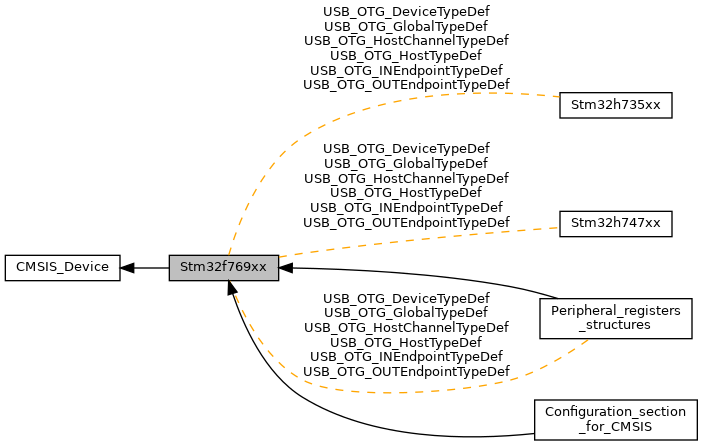

Collaboration diagram for Stm32f769xx:

Modules | |

| Configuration_section_for_CMSIS | |

| Peripheral_registers_structures | |

Classes | |

| struct | USB_OTG_DeviceTypeDef |

| USB_OTG_device_Registers. More... | |

| struct | USB_OTG_GlobalTypeDef |

| USB_OTG_Core_Registers. More... | |

| struct | USB_OTG_HostChannelTypeDef |

| USB_OTG_Host_Channel_Specific_Registers. More... | |

| struct | USB_OTG_HostTypeDef |

| USB_OTG_Host_Mode_Register_Structures. More... | |

| struct | USB_OTG_INEndpointTypeDef |

| USB_OTG_IN_Endpoint-Specific_Register. More... | |

| struct | USB_OTG_OUTEndpointTypeDef |

| USB_OTG_OUT_Endpoint-Specific_Registers. More... | |

Macros | |

| #define | __CM7_REV 0x0100U |

| Configuration of the Cortex-M7 Processor and Core Peripherals. More... | |

| #define | __DCACHE_PRESENT 1 |

| #define | __FPU_PRESENT 1 |

| #define | __ICACHE_PRESENT 1 |

| #define | __MPU_PRESENT 1 |

| #define | __NVIC_PRIO_BITS 4 |

| #define | __Vendor_SysTickConfig 0 |

Detailed Description

Macro Definition Documentation

◆ __CM7_REV

| #define __CM7_REV 0x0100U |

Configuration of the Cortex-M7 Processor and Core Peripherals.

Cortex-M7 revision r1p0

Definition at line 179 of file stm32f769xx.h.

◆ __DCACHE_PRESENT

| #define __DCACHE_PRESENT 1 |

CM7 data cache present

Cortex-M7 processor and core peripherals

Definition at line 185 of file stm32f769xx.h.

◆ __FPU_PRESENT

| #define __FPU_PRESENT 1 |

FPU present

Definition at line 183 of file stm32f769xx.h.

◆ __ICACHE_PRESENT

| #define __ICACHE_PRESENT 1 |

CM7 instruction cache present

Definition at line 184 of file stm32f769xx.h.

◆ __MPU_PRESENT

| #define __MPU_PRESENT 1 |

CM7 provides an MPU

Definition at line 180 of file stm32f769xx.h.

◆ __NVIC_PRIO_BITS

| #define __NVIC_PRIO_BITS 4 |

CM7 uses 4 Bits for the Priority Levels

Definition at line 181 of file stm32f769xx.h.

◆ __Vendor_SysTickConfig

| #define __Vendor_SysTickConfig 0 |

Set to 1 if different SysTick Config is used

Definition at line 182 of file stm32f769xx.h.