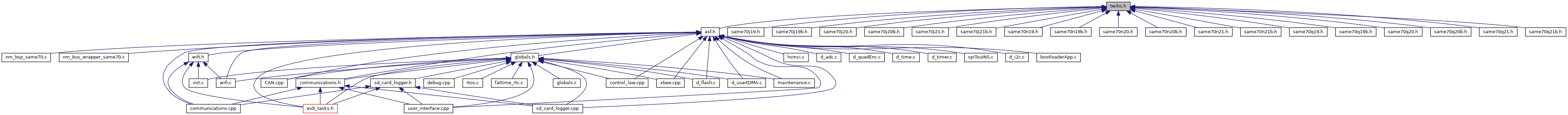

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Twihs |

| Twihs hardware registers. More... | |

Macros | |

| #define | TWIHS_CR_ACMDIS (0x1u << 17) |

| (TWIHS_CR) Alternative Command Mode Disable More... | |

| #define | TWIHS_CR_ACMEN (0x1u << 16) |

| (TWIHS_CR) Alternative Command Mode Enable More... | |

| #define | TWIHS_CR_CLEAR (0x1u << 15) |

| (TWIHS_CR) Bus CLEAR Command More... | |

| #define | TWIHS_CR_FIFODIS (0x1u << 29) |

| (TWIHS_CR) FIFO Disable More... | |

| #define | TWIHS_CR_FIFOEN (0x1u << 28) |

| (TWIHS_CR) FIFO Enable More... | |

| #define | TWIHS_CR_HSDIS (0x1u << 9) |

| (TWIHS_CR) TWIHS High-Speed Mode Disabled More... | |

| #define | TWIHS_CR_HSEN (0x1u << 8) |

| (TWIHS_CR) TWIHS High-Speed Mode Enabled More... | |

| #define | TWIHS_CR_LOCKCLR (0x1u << 26) |

| (TWIHS_CR) Lock Clear More... | |

| #define | TWIHS_CR_MSDIS (0x1u << 3) |

| (TWIHS_CR) TWIHS Master Mode Disabled More... | |

| #define | TWIHS_CR_MSEN (0x1u << 2) |

| (TWIHS_CR) TWIHS Master Mode Enabled More... | |

| #define | TWIHS_CR_PECDIS (0x1u << 13) |

| (TWIHS_CR) Packet Error Checking Disable More... | |

| #define | TWIHS_CR_PECEN (0x1u << 12) |

| (TWIHS_CR) Packet Error Checking Enable More... | |

| #define | TWIHS_CR_PECRQ (0x1u << 14) |

| (TWIHS_CR) PEC Request More... | |

| #define | TWIHS_CR_QUICK (0x1u << 6) |

| (TWIHS_CR) SMBus Quick Command More... | |

| #define | TWIHS_CR_SMBDIS (0x1u << 11) |

| (TWIHS_CR) SMBus Mode Disabled More... | |

| #define | TWIHS_CR_SMBEN (0x1u << 10) |

| (TWIHS_CR) SMBus Mode Enabled More... | |

| #define | TWIHS_CR_START (0x1u << 0) |

| (TWIHS_CR) Send a START Condition More... | |

| #define | TWIHS_CR_STOP (0x1u << 1) |

| (TWIHS_CR) Send a STOP Condition More... | |

| #define | TWIHS_CR_SVDIS (0x1u << 5) |

| (TWIHS_CR) TWIHS Slave Mode Disabled More... | |

| #define | TWIHS_CR_SVEN (0x1u << 4) |

| (TWIHS_CR) TWIHS Slave Mode Enabled More... | |

| #define | TWIHS_CR_SWRST (0x1u << 7) |

| (TWIHS_CR) Software Reset More... | |

| #define | TWIHS_CR_THRCLR (0x1u << 24) |

| (TWIHS_CR) Transmit Holding Register Clear More... | |

| #define | TWIHS_CWGR_CHDIV(value) ((TWIHS_CWGR_CHDIV_Msk & ((value) << TWIHS_CWGR_CHDIV_Pos))) |

| #define | TWIHS_CWGR_CHDIV_Msk (0xffu << TWIHS_CWGR_CHDIV_Pos) |

| (TWIHS_CWGR) Clock High Divider More... | |

| #define | TWIHS_CWGR_CHDIV_Pos 8 |

| #define | TWIHS_CWGR_CKDIV(value) ((TWIHS_CWGR_CKDIV_Msk & ((value) << TWIHS_CWGR_CKDIV_Pos))) |

| #define | TWIHS_CWGR_CKDIV_Msk (0x7u << TWIHS_CWGR_CKDIV_Pos) |

| (TWIHS_CWGR) Clock Divider More... | |

| #define | TWIHS_CWGR_CKDIV_Pos 16 |

| #define | TWIHS_CWGR_CLDIV(value) ((TWIHS_CWGR_CLDIV_Msk & ((value) << TWIHS_CWGR_CLDIV_Pos))) |

| #define | TWIHS_CWGR_CLDIV_Msk (0xffu << TWIHS_CWGR_CLDIV_Pos) |

| (TWIHS_CWGR) Clock Low Divider More... | |

| #define | TWIHS_CWGR_CLDIV_Pos 0 |

| #define | TWIHS_CWGR_HOLD(value) ((TWIHS_CWGR_HOLD_Msk & ((value) << TWIHS_CWGR_HOLD_Pos))) |

| #define | TWIHS_CWGR_HOLD_Msk (0x3fu << TWIHS_CWGR_HOLD_Pos) |

| (TWIHS_CWGR) TWD Hold Time Versus TWCK Falling More... | |

| #define | TWIHS_CWGR_HOLD_Pos 24 |

| #define | TWIHS_DR_CLKRQ (0x1u << 1) |

| (TWIHS_DR) Clock Request More... | |

| #define | TWIHS_DR_SWEN (0x1u << 0) |

| (TWIHS_DR) SleepWalking Enable More... | |

| #define | TWIHS_DR_SWMATCH (0x1u << 2) |

| (TWIHS_DR) SleepWalking Match More... | |

| #define | TWIHS_DR_TRP (0x1u << 3) |

| (TWIHS_DR) Transfer Pending More... | |

| #define | TWIHS_FILTR_FILT (0x1u << 0) |

| (TWIHS_FILTR) RX Digital Filter More... | |

| #define | TWIHS_FILTR_PADFCFG (0x1u << 2) |

| (TWIHS_FILTR) PAD Filter Config More... | |

| #define | TWIHS_FILTR_PADFEN (0x1u << 1) |

| (TWIHS_FILTR) PAD Filter Enable More... | |

| #define | TWIHS_FILTR_THRES(value) ((TWIHS_FILTR_THRES_Msk & ((value) << TWIHS_FILTR_THRES_Pos))) |

| #define | TWIHS_FILTR_THRES_Msk (0x7u << TWIHS_FILTR_THRES_Pos) |

| (TWIHS_FILTR) Digital Filter Threshold More... | |

| #define | TWIHS_FILTR_THRES_Pos 8 |

| #define | TWIHS_IADR_IADR(value) ((TWIHS_IADR_IADR_Msk & ((value) << TWIHS_IADR_IADR_Pos))) |

| #define | TWIHS_IADR_IADR_Msk (0xffffffu << TWIHS_IADR_IADR_Pos) |

| (TWIHS_IADR) Internal Address More... | |

| #define | TWIHS_IADR_IADR_Pos 0 |

| #define | TWIHS_IDR_ARBLST (0x1u << 9) |

| (TWIHS_IDR) Arbitration Lost Interrupt Disable More... | |

| #define | TWIHS_IDR_EOSACC (0x1u << 11) |

| (TWIHS_IDR) End Of Slave Access Interrupt Disable More... | |

| #define | TWIHS_IDR_GACC (0x1u << 5) |

| (TWIHS_IDR) General Call Access Interrupt Disable More... | |

| #define | TWIHS_IDR_MCACK (0x1u << 16) |

| (TWIHS_IDR) Master Code Acknowledge Interrupt Disable More... | |

| #define | TWIHS_IDR_NACK (0x1u << 8) |

| (TWIHS_IDR) Not Acknowledge Interrupt Disable More... | |

| #define | TWIHS_IDR_OVRE (0x1u << 6) |

| (TWIHS_IDR) Overrun Error Interrupt Disable More... | |

| #define | TWIHS_IDR_PECERR (0x1u << 19) |

| (TWIHS_IDR) PEC Error Interrupt Disable More... | |

| #define | TWIHS_IDR_RXRDY (0x1u << 1) |

| (TWIHS_IDR) Receive Holding Register Ready Interrupt Disable More... | |

| #define | TWIHS_IDR_SCL_WS (0x1u << 10) |

| (TWIHS_IDR) Clock Wait State Interrupt Disable More... | |

| #define | TWIHS_IDR_SMBDAM (0x1u << 20) |

| (TWIHS_IDR) SMBus Default Address Match Interrupt Disable More... | |

| #define | TWIHS_IDR_SMBHHM (0x1u << 21) |

| (TWIHS_IDR) SMBus Host Header Address Match Interrupt Disable More... | |

| #define | TWIHS_IDR_SVACC (0x1u << 4) |

| (TWIHS_IDR) Slave Access Interrupt Disable More... | |

| #define | TWIHS_IDR_TOUT (0x1u << 18) |

| (TWIHS_IDR) Timeout Error Interrupt Disable More... | |

| #define | TWIHS_IDR_TXCOMP (0x1u << 0) |

| (TWIHS_IDR) Transmission Completed Interrupt Disable More... | |

| #define | TWIHS_IDR_TXRDY (0x1u << 2) |

| (TWIHS_IDR) Transmit Holding Register Ready Interrupt Disable More... | |

| #define | TWIHS_IDR_UNRE (0x1u << 7) |

| (TWIHS_IDR) Underrun Error Interrupt Disable More... | |

| #define | TWIHS_IER_ARBLST (0x1u << 9) |

| (TWIHS_IER) Arbitration Lost Interrupt Enable More... | |

| #define | TWIHS_IER_EOSACC (0x1u << 11) |

| (TWIHS_IER) End Of Slave Access Interrupt Enable More... | |

| #define | TWIHS_IER_GACC (0x1u << 5) |

| (TWIHS_IER) General Call Access Interrupt Enable More... | |

| #define | TWIHS_IER_MCACK (0x1u << 16) |

| (TWIHS_IER) Master Code Acknowledge Interrupt Enable More... | |

| #define | TWIHS_IER_NACK (0x1u << 8) |

| (TWIHS_IER) Not Acknowledge Interrupt Enable More... | |

| #define | TWIHS_IER_OVRE (0x1u << 6) |

| (TWIHS_IER) Overrun Error Interrupt Enable More... | |

| #define | TWIHS_IER_PECERR (0x1u << 19) |

| (TWIHS_IER) PEC Error Interrupt Enable More... | |

| #define | TWIHS_IER_RXRDY (0x1u << 1) |

| (TWIHS_IER) Receive Holding Register Ready Interrupt Enable More... | |

| #define | TWIHS_IER_SCL_WS (0x1u << 10) |

| (TWIHS_IER) Clock Wait State Interrupt Enable More... | |

| #define | TWIHS_IER_SMBDAM (0x1u << 20) |

| (TWIHS_IER) SMBus Default Address Match Interrupt Enable More... | |

| #define | TWIHS_IER_SMBHHM (0x1u << 21) |

| (TWIHS_IER) SMBus Host Header Address Match Interrupt Enable More... | |

| #define | TWIHS_IER_SVACC (0x1u << 4) |

| (TWIHS_IER) Slave Access Interrupt Enable More... | |

| #define | TWIHS_IER_TOUT (0x1u << 18) |

| (TWIHS_IER) Timeout Error Interrupt Enable More... | |

| #define | TWIHS_IER_TXCOMP (0x1u << 0) |

| (TWIHS_IER) Transmission Completed Interrupt Enable More... | |

| #define | TWIHS_IER_TXRDY (0x1u << 2) |

| (TWIHS_IER) Transmit Holding Register Ready Interrupt Enable More... | |

| #define | TWIHS_IER_UNRE (0x1u << 7) |

| (TWIHS_IER) Underrun Error Interrupt Enable More... | |

| #define | TWIHS_IMR_ARBLST (0x1u << 9) |

| (TWIHS_IMR) Arbitration Lost Interrupt Mask More... | |

| #define | TWIHS_IMR_EOSACC (0x1u << 11) |

| (TWIHS_IMR) End Of Slave Access Interrupt Mask More... | |

| #define | TWIHS_IMR_GACC (0x1u << 5) |

| (TWIHS_IMR) General Call Access Interrupt Mask More... | |

| #define | TWIHS_IMR_MCACK (0x1u << 16) |

| (TWIHS_IMR) Master Code Acknowledge Interrupt Mask More... | |

| #define | TWIHS_IMR_NACK (0x1u << 8) |

| (TWIHS_IMR) Not Acknowledge Interrupt Mask More... | |

| #define | TWIHS_IMR_OVRE (0x1u << 6) |

| (TWIHS_IMR) Overrun Error Interrupt Mask More... | |

| #define | TWIHS_IMR_PECERR (0x1u << 19) |

| (TWIHS_IMR) PEC Error Interrupt Mask More... | |

| #define | TWIHS_IMR_RXRDY (0x1u << 1) |

| (TWIHS_IMR) Receive Holding Register Ready Interrupt Mask More... | |

| #define | TWIHS_IMR_SCL_WS (0x1u << 10) |

| (TWIHS_IMR) Clock Wait State Interrupt Mask More... | |

| #define | TWIHS_IMR_SMBDAM (0x1u << 20) |

| (TWIHS_IMR) SMBus Default Address Match Interrupt Mask More... | |

| #define | TWIHS_IMR_SMBHHM (0x1u << 21) |

| (TWIHS_IMR) SMBus Host Header Address Match Interrupt Mask More... | |

| #define | TWIHS_IMR_SVACC (0x1u << 4) |

| (TWIHS_IMR) Slave Access Interrupt Mask More... | |

| #define | TWIHS_IMR_TOUT (0x1u << 18) |

| (TWIHS_IMR) Timeout Error Interrupt Mask More... | |

| #define | TWIHS_IMR_TXCOMP (0x1u << 0) |

| (TWIHS_IMR) Transmission Completed Interrupt Mask More... | |

| #define | TWIHS_IMR_TXRDY (0x1u << 2) |

| (TWIHS_IMR) Transmit Holding Register Ready Interrupt Mask More... | |

| #define | TWIHS_IMR_UNRE (0x1u << 7) |

| (TWIHS_IMR) Underrun Error Interrupt Mask More... | |

| #define | TWIHS_MMR_DADR(value) ((TWIHS_MMR_DADR_Msk & ((value) << TWIHS_MMR_DADR_Pos))) |

| #define | TWIHS_MMR_DADR_Msk (0x7fu << TWIHS_MMR_DADR_Pos) |

| (TWIHS_MMR) Device Address More... | |

| #define | TWIHS_MMR_DADR_Pos 16 |

| #define | TWIHS_MMR_IADRSZ(value) ((TWIHS_MMR_IADRSZ_Msk & ((value) << TWIHS_MMR_IADRSZ_Pos))) |

| #define | TWIHS_MMR_IADRSZ_1_BYTE (0x1u << 8) |

| (TWIHS_MMR) One-byte internal device address More... | |

| #define | TWIHS_MMR_IADRSZ_2_BYTE (0x2u << 8) |

| (TWIHS_MMR) Two-byte internal device address More... | |

| #define | TWIHS_MMR_IADRSZ_3_BYTE (0x3u << 8) |

| (TWIHS_MMR) Three-byte internal device address More... | |

| #define | TWIHS_MMR_IADRSZ_Msk (0x3u << TWIHS_MMR_IADRSZ_Pos) |

| (TWIHS_MMR) Internal Device Address Size More... | |

| #define | TWIHS_MMR_IADRSZ_NONE (0x0u << 8) |

| (TWIHS_MMR) No internal device address More... | |

| #define | TWIHS_MMR_IADRSZ_Pos 8 |

| #define | TWIHS_MMR_MREAD (0x1u << 12) |

| (TWIHS_MMR) Master Read Direction More... | |

| #define | TWIHS_RHR_RXDATA_Msk (0xffu << TWIHS_RHR_RXDATA_Pos) |

| (TWIHS_RHR) Master or Slave Receive Holding Data More... | |

| #define | TWIHS_RHR_RXDATA_Pos 0 |

| #define | TWIHS_SMBTR_PRESC(value) ((TWIHS_SMBTR_PRESC_Msk & ((value) << TWIHS_SMBTR_PRESC_Pos))) |

| #define | TWIHS_SMBTR_PRESC_Msk (0xfu << TWIHS_SMBTR_PRESC_Pos) |

| (TWIHS_SMBTR) SMBus Clock Prescaler More... | |

| #define | TWIHS_SMBTR_PRESC_Pos 0 |

| #define | TWIHS_SMBTR_THMAX(value) ((TWIHS_SMBTR_THMAX_Msk & ((value) << TWIHS_SMBTR_THMAX_Pos))) |

| #define | TWIHS_SMBTR_THMAX_Msk (0xffu << TWIHS_SMBTR_THMAX_Pos) |

| (TWIHS_SMBTR) Clock High Maximum Cycles More... | |

| #define | TWIHS_SMBTR_THMAX_Pos 24 |

| #define | TWIHS_SMBTR_TLOWM(value) ((TWIHS_SMBTR_TLOWM_Msk & ((value) << TWIHS_SMBTR_TLOWM_Pos))) |

| #define | TWIHS_SMBTR_TLOWM_Msk (0xffu << TWIHS_SMBTR_TLOWM_Pos) |

| (TWIHS_SMBTR) Master Clock Stretch Maximum Cycles More... | |

| #define | TWIHS_SMBTR_TLOWM_Pos 16 |

| #define | TWIHS_SMBTR_TLOWS(value) ((TWIHS_SMBTR_TLOWS_Msk & ((value) << TWIHS_SMBTR_TLOWS_Pos))) |

| #define | TWIHS_SMBTR_TLOWS_Msk (0xffu << TWIHS_SMBTR_TLOWS_Pos) |

| (TWIHS_SMBTR) Slave Clock Stretch Maximum Cycles More... | |

| #define | TWIHS_SMBTR_TLOWS_Pos 8 |

| #define | TWIHS_SMR_DATAMEN (0x1u << 31) |

| (TWIHS_SMR) Data Matching Enable More... | |

| #define | TWIHS_SMR_MASK(value) ((TWIHS_SMR_MASK_Msk & ((value) << TWIHS_SMR_MASK_Pos))) |

| #define | TWIHS_SMR_MASK_Msk (0x7fu << TWIHS_SMR_MASK_Pos) |

| (TWIHS_SMR) Slave Address Mask More... | |

| #define | TWIHS_SMR_MASK_Pos 8 |

| #define | TWIHS_SMR_NACKEN (0x1u << 0) |

| (TWIHS_SMR) Slave Receiver Data Phase NACK enable More... | |

| #define | TWIHS_SMR_SADR(value) ((TWIHS_SMR_SADR_Msk & ((value) << TWIHS_SMR_SADR_Pos))) |

| #define | TWIHS_SMR_SADR1EN (0x1u << 28) |

| (TWIHS_SMR) Slave Address 1 Enable More... | |

| #define | TWIHS_SMR_SADR2EN (0x1u << 29) |

| (TWIHS_SMR) Slave Address 2 Enable More... | |

| #define | TWIHS_SMR_SADR3EN (0x1u << 30) |

| (TWIHS_SMR) Slave Address 3 Enable More... | |

| #define | TWIHS_SMR_SADR_Msk (0x7fu << TWIHS_SMR_SADR_Pos) |

| (TWIHS_SMR) Slave Address More... | |

| #define | TWIHS_SMR_SADR_Pos 16 |

| #define | TWIHS_SMR_SCLWSDIS (0x1u << 6) |

| (TWIHS_SMR) Clock Wait State Disable More... | |

| #define | TWIHS_SMR_SMDA (0x1u << 2) |

| (TWIHS_SMR) SMBus Default Address More... | |

| #define | TWIHS_SMR_SMHH (0x1u << 3) |

| (TWIHS_SMR) SMBus Host Header More... | |

| #define | TWIHS_SR_ARBLST (0x1u << 9) |

| (TWIHS_SR) Arbitration Lost (cleared on read) More... | |

| #define | TWIHS_SR_EOSACC (0x1u << 11) |

| (TWIHS_SR) End Of Slave Access (cleared on read) More... | |

| #define | TWIHS_SR_GACC (0x1u << 5) |

| (TWIHS_SR) General Call Access (cleared on read) More... | |

| #define | TWIHS_SR_MCACK (0x1u << 16) |

| (TWIHS_SR) Master Code Acknowledge (cleared on read) More... | |

| #define | TWIHS_SR_NACK (0x1u << 8) |

| (TWIHS_SR) Not Acknowledged (cleared on read) More... | |

| #define | TWIHS_SR_OVRE (0x1u << 6) |

| (TWIHS_SR) Overrun Error (cleared on read) More... | |

| #define | TWIHS_SR_PECERR (0x1u << 19) |

| (TWIHS_SR) PEC Error (cleared on read) More... | |

| #define | TWIHS_SR_RXRDY (0x1u << 1) |

| (TWIHS_SR) Receive Holding Register Ready (cleared by reading TWIHS_RHR) More... | |

| #define | TWIHS_SR_SCL (0x1u << 24) |

| (TWIHS_SR) SCL line value More... | |

| #define | TWIHS_SR_SCLWS (0x1u << 10) |

| (TWIHS_SR) Clock Wait State More... | |

| #define | TWIHS_SR_SDA (0x1u << 25) |

| (TWIHS_SR) SDA line value More... | |

| #define | TWIHS_SR_SMBDAM (0x1u << 20) |

| (TWIHS_SR) SMBus Default Address Match (cleared on read) More... | |

| #define | TWIHS_SR_SMBHHM (0x1u << 21) |

| (TWIHS_SR) SMBus Host Header Address Match (cleared on read) More... | |

| #define | TWIHS_SR_SVACC (0x1u << 4) |

| (TWIHS_SR) Slave Access More... | |

| #define | TWIHS_SR_SVREAD (0x1u << 3) |

| (TWIHS_SR) Slave Read More... | |

| #define | TWIHS_SR_TOUT (0x1u << 18) |

| (TWIHS_SR) Timeout Error (cleared on read) More... | |

| #define | TWIHS_SR_TXCOMP (0x1u << 0) |

| (TWIHS_SR) Transmission Completed (cleared by writing TWIHS_THR) More... | |

| #define | TWIHS_SR_TXRDY (0x1u << 2) |

| (TWIHS_SR) Transmit Holding Register Ready (cleared by writing TWIHS_THR) More... | |

| #define | TWIHS_SR_UNRE (0x1u << 7) |

| (TWIHS_SR) Underrun Error (cleared on read) More... | |

| #define | TWIHS_SWMR_DATAM(value) ((TWIHS_SWMR_DATAM_Msk & ((value) << TWIHS_SWMR_DATAM_Pos))) |

| #define | TWIHS_SWMR_DATAM_Msk (0xffu << TWIHS_SWMR_DATAM_Pos) |

| (TWIHS_SWMR) Data Match More... | |

| #define | TWIHS_SWMR_DATAM_Pos 24 |

| #define | TWIHS_SWMR_SADR1(value) ((TWIHS_SWMR_SADR1_Msk & ((value) << TWIHS_SWMR_SADR1_Pos))) |

| #define | TWIHS_SWMR_SADR1_Msk (0x7fu << TWIHS_SWMR_SADR1_Pos) |

| (TWIHS_SWMR) Slave Address 1 More... | |

| #define | TWIHS_SWMR_SADR1_Pos 0 |

| #define | TWIHS_SWMR_SADR2(value) ((TWIHS_SWMR_SADR2_Msk & ((value) << TWIHS_SWMR_SADR2_Pos))) |

| #define | TWIHS_SWMR_SADR2_Msk (0x7fu << TWIHS_SWMR_SADR2_Pos) |

| (TWIHS_SWMR) Slave Address 2 More... | |

| #define | TWIHS_SWMR_SADR2_Pos 8 |

| #define | TWIHS_SWMR_SADR3(value) ((TWIHS_SWMR_SADR3_Msk & ((value) << TWIHS_SWMR_SADR3_Pos))) |

| #define | TWIHS_SWMR_SADR3_Msk (0x7fu << TWIHS_SWMR_SADR3_Pos) |

| (TWIHS_SWMR) Slave Address 3 More... | |

| #define | TWIHS_SWMR_SADR3_Pos 16 |

| #define | TWIHS_THR_TXDATA(value) ((TWIHS_THR_TXDATA_Msk & ((value) << TWIHS_THR_TXDATA_Pos))) |

| #define | TWIHS_THR_TXDATA_Msk (0xffu << TWIHS_THR_TXDATA_Pos) |

| (TWIHS_THR) Master or Slave Transmit Holding Data More... | |

| #define | TWIHS_THR_TXDATA_Pos 0 |

| #define | TWIHS_VER_MFN_Msk (0x7u << TWIHS_VER_MFN_Pos) |

| (TWIHS_VER) Metal Fix Number More... | |

| #define | TWIHS_VER_MFN_Pos 16 |

| #define | TWIHS_VER_VERSION_Msk (0xfffu << TWIHS_VER_VERSION_Pos) |

| (TWIHS_VER) Version of the Hardware Module More... | |

| #define | TWIHS_VER_VERSION_Pos 0 |

| #define | TWIHS_WPMR_WPEN (0x1u << 0) |

| (TWIHS_WPMR) Write Protection Enable More... | |

| #define | TWIHS_WPMR_WPKEY(value) ((TWIHS_WPMR_WPKEY_Msk & ((value) << TWIHS_WPMR_WPKEY_Pos))) |

| #define | TWIHS_WPMR_WPKEY_Msk (0xffffffu << TWIHS_WPMR_WPKEY_Pos) |

| (TWIHS_WPMR) Write Protection Key More... | |

| #define | TWIHS_WPMR_WPKEY_PASSWD (0x545749u << 8) |

| (TWIHS_WPMR) Writing any other value in this field aborts the write operation of the WPEN bit.Always reads as 0 More... | |

| #define | TWIHS_WPMR_WPKEY_Pos 8 |

| #define | TWIHS_WPSR_WPVS (0x1u << 0) |

| (TWIHS_WPSR) Write Protection Violation Status More... | |

| #define | TWIHS_WPSR_WPVSRC_Msk (0xffffffu << TWIHS_WPSR_WPVSRC_Pos) |

| (TWIHS_WPSR) Write Protection Violation Source More... | |

| #define | TWIHS_WPSR_WPVSRC_Pos 8 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file utils/cmsis/same70/include/component/twihs.h.