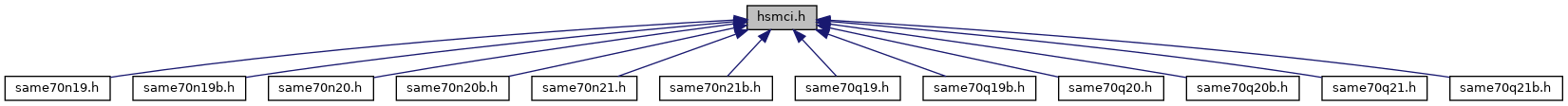

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Hsmci |

| Hsmci hardware registers. More... | |

Macros | |

| #define | HSMCI_ARGR_ARG(value) ((HSMCI_ARGR_ARG_Msk & ((value) << HSMCI_ARGR_ARG_Pos))) |

| #define | HSMCI_ARGR_ARG_Msk (0xffffffffu << HSMCI_ARGR_ARG_Pos) |

| (HSMCI_ARGR) Command Argument More... | |

| #define | HSMCI_ARGR_ARG_Pos 0 |

| #define | HSMCI_BLKR_BCNT(value) ((HSMCI_BLKR_BCNT_Msk & ((value) << HSMCI_BLKR_BCNT_Pos))) |

| #define | HSMCI_BLKR_BCNT_Msk (0xffffu << HSMCI_BLKR_BCNT_Pos) |

| (HSMCI_BLKR) MMC/SDIO Block Count - SDIO Byte Count More... | |

| #define | HSMCI_BLKR_BCNT_Pos 0 |

| #define | HSMCI_BLKR_BLKLEN(value) ((HSMCI_BLKR_BLKLEN_Msk & ((value) << HSMCI_BLKR_BLKLEN_Pos))) |

| #define | HSMCI_BLKR_BLKLEN_Msk (0xffffu << HSMCI_BLKR_BLKLEN_Pos) |

| (HSMCI_BLKR) Data Block Length More... | |

| #define | HSMCI_BLKR_BLKLEN_Pos 16 |

| #define | HSMCI_CFG_FERRCTRL (0x1u << 4) |

| (HSMCI_CFG) Flow Error flag reset control mode More... | |

| #define | HSMCI_CFG_FIFOMODE (0x1u << 0) |

| (HSMCI_CFG) HSMCI Internal FIFO control mode More... | |

| #define | HSMCI_CFG_HSMODE (0x1u << 8) |

| (HSMCI_CFG) High Speed Mode More... | |

| #define | HSMCI_CFG_LSYNC (0x1u << 12) |

| (HSMCI_CFG) Synchronize on the last block More... | |

| #define | HSMCI_CMDR_ATACS (0x1u << 26) |

| (HSMCI_CMDR) ATA with Command Completion Signal More... | |

| #define | HSMCI_CMDR_ATACS_COMPLETION (0x1u << 26) |

| (HSMCI_CMDR) This bit indicates that a completion signal is expected within a programmed amount of time (HSMCI_CSTOR). More... | |

| #define | HSMCI_CMDR_ATACS_NORMAL (0x0u << 26) |

| (HSMCI_CMDR) Normal operation mode. More... | |

| #define | HSMCI_CMDR_BOOT_ACK (0x1u << 27) |

| (HSMCI_CMDR) Boot Operation Acknowledge More... | |

| #define | HSMCI_CMDR_CMDNB(value) ((HSMCI_CMDR_CMDNB_Msk & ((value) << HSMCI_CMDR_CMDNB_Pos))) |

| #define | HSMCI_CMDR_CMDNB_Msk (0x3fu << HSMCI_CMDR_CMDNB_Pos) |

| (HSMCI_CMDR) Command Number More... | |

| #define | HSMCI_CMDR_CMDNB_Pos 0 |

| #define | HSMCI_CMDR_IOSPCMD(value) ((HSMCI_CMDR_IOSPCMD_Msk & ((value) << HSMCI_CMDR_IOSPCMD_Pos))) |

| #define | HSMCI_CMDR_IOSPCMD_Msk (0x3u << HSMCI_CMDR_IOSPCMD_Pos) |

| (HSMCI_CMDR) SDIO Special Command More... | |

| #define | HSMCI_CMDR_IOSPCMD_Pos 24 |

| #define | HSMCI_CMDR_IOSPCMD_RESUME (0x2u << 24) |

| (HSMCI_CMDR) SDIO Resume Command More... | |

| #define | HSMCI_CMDR_IOSPCMD_STD (0x0u << 24) |

| (HSMCI_CMDR) Not an SDIO Special Command More... | |

| #define | HSMCI_CMDR_IOSPCMD_SUSPEND (0x1u << 24) |

| (HSMCI_CMDR) SDIO Suspend Command More... | |

| #define | HSMCI_CMDR_MAXLAT (0x1u << 12) |

| (HSMCI_CMDR) Max Latency for Command to Response More... | |

| #define | HSMCI_CMDR_MAXLAT_5 (0x0u << 12) |

| (HSMCI_CMDR) 5-cycle max latency. More... | |

| #define | HSMCI_CMDR_MAXLAT_64 (0x1u << 12) |

| (HSMCI_CMDR) 64-cycle max latency. More... | |

| #define | HSMCI_CMDR_OPDCMD (0x1u << 11) |

| (HSMCI_CMDR) Open Drain Command More... | |

| #define | HSMCI_CMDR_OPDCMD_OPENDRAIN (0x1u << 11) |

| (HSMCI_CMDR) Open drain command. More... | |

| #define | HSMCI_CMDR_OPDCMD_PUSHPULL (0x0u << 11) |

| (HSMCI_CMDR) Push pull command. More... | |

| #define | HSMCI_CMDR_RSPTYP(value) ((HSMCI_CMDR_RSPTYP_Msk & ((value) << HSMCI_CMDR_RSPTYP_Pos))) |

| #define | HSMCI_CMDR_RSPTYP_136_BIT (0x2u << 6) |

| (HSMCI_CMDR) 136-bit response More... | |

| #define | HSMCI_CMDR_RSPTYP_48_BIT (0x1u << 6) |

| (HSMCI_CMDR) 48-bit response More... | |

| #define | HSMCI_CMDR_RSPTYP_Msk (0x3u << HSMCI_CMDR_RSPTYP_Pos) |

| (HSMCI_CMDR) Response Type More... | |

| #define | HSMCI_CMDR_RSPTYP_NORESP (0x0u << 6) |

| (HSMCI_CMDR) No response More... | |

| #define | HSMCI_CMDR_RSPTYP_Pos 6 |

| #define | HSMCI_CMDR_RSPTYP_R1B (0x3u << 6) |

| (HSMCI_CMDR) R1b response type More... | |

| #define | HSMCI_CMDR_SPCMD(value) ((HSMCI_CMDR_SPCMD_Msk & ((value) << HSMCI_CMDR_SPCMD_Pos))) |

| #define | HSMCI_CMDR_SPCMD_BOR (0x6u << 8) |

| (HSMCI_CMDR) Boot Operation Request. Start a boot operation mode, the host processor can read boot data from the MMC device directly. More... | |

| #define | HSMCI_CMDR_SPCMD_CE_ATA (0x3u << 8) |

| (HSMCI_CMDR) CE-ATA Completion Signal disable Command. The host cancels the ability for the device to return a command completion signal on the command line. More... | |

| #define | HSMCI_CMDR_SPCMD_EBO (0x7u << 8) |

| (HSMCI_CMDR) End Boot Operation. This command allows the host processor to terminate the boot operation mode. More... | |

| #define | HSMCI_CMDR_SPCMD_INIT (0x1u << 8) |

| (HSMCI_CMDR) Initialization CMD: 74 clock cycles for initialization sequence. More... | |

| #define | HSMCI_CMDR_SPCMD_IT_CMD (0x4u << 8) |

| (HSMCI_CMDR) Interrupt command: Corresponds to the Interrupt Mode (CMD40). More... | |

| #define | HSMCI_CMDR_SPCMD_IT_RESP (0x5u << 8) |

| (HSMCI_CMDR) Interrupt response: Corresponds to the Interrupt Mode (CMD40). More... | |

| #define | HSMCI_CMDR_SPCMD_Msk (0x7u << HSMCI_CMDR_SPCMD_Pos) |

| (HSMCI_CMDR) Special Command More... | |

| #define | HSMCI_CMDR_SPCMD_Pos 8 |

| #define | HSMCI_CMDR_SPCMD_STD (0x0u << 8) |

| (HSMCI_CMDR) Not a special CMD. More... | |

| #define | HSMCI_CMDR_SPCMD_SYNC (0x2u << 8) |

| (HSMCI_CMDR) Synchronized CMD: Wait for the end of the current data block transfer before sending the pending command. More... | |

| #define | HSMCI_CMDR_TRCMD(value) ((HSMCI_CMDR_TRCMD_Msk & ((value) << HSMCI_CMDR_TRCMD_Pos))) |

| #define | HSMCI_CMDR_TRCMD_Msk (0x3u << HSMCI_CMDR_TRCMD_Pos) |

| (HSMCI_CMDR) Transfer Command More... | |

| #define | HSMCI_CMDR_TRCMD_NO_DATA (0x0u << 16) |

| (HSMCI_CMDR) No data transfer More... | |

| #define | HSMCI_CMDR_TRCMD_Pos 16 |

| #define | HSMCI_CMDR_TRCMD_START_DATA (0x1u << 16) |

| (HSMCI_CMDR) Start data transfer More... | |

| #define | HSMCI_CMDR_TRCMD_STOP_DATA (0x2u << 16) |

| (HSMCI_CMDR) Stop data transfer More... | |

| #define | HSMCI_CMDR_TRDIR (0x1u << 18) |

| (HSMCI_CMDR) Transfer Direction More... | |

| #define | HSMCI_CMDR_TRDIR_READ (0x1u << 18) |

| (HSMCI_CMDR) Read. More... | |

| #define | HSMCI_CMDR_TRDIR_WRITE (0x0u << 18) |

| (HSMCI_CMDR) Write. More... | |

| #define | HSMCI_CMDR_TRTYP(value) ((HSMCI_CMDR_TRTYP_Msk & ((value) << HSMCI_CMDR_TRTYP_Pos))) |

| #define | HSMCI_CMDR_TRTYP_BLOCK (0x5u << 19) |

| (HSMCI_CMDR) SDIO Block More... | |

| #define | HSMCI_CMDR_TRTYP_BYTE (0x4u << 19) |

| (HSMCI_CMDR) SDIO Byte More... | |

| #define | HSMCI_CMDR_TRTYP_Msk (0x7u << HSMCI_CMDR_TRTYP_Pos) |

| (HSMCI_CMDR) Transfer Type More... | |

| #define | HSMCI_CMDR_TRTYP_MULTIPLE (0x1u << 19) |

| (HSMCI_CMDR) MMC/SD Card Multiple Block More... | |

| #define | HSMCI_CMDR_TRTYP_Pos 19 |

| #define | HSMCI_CMDR_TRTYP_SINGLE (0x0u << 19) |

| (HSMCI_CMDR) MMC/SD Card Single Block More... | |

| #define | HSMCI_CMDR_TRTYP_STREAM (0x2u << 19) |

| (HSMCI_CMDR) MMC Stream More... | |

| #define | HSMCI_CR_MCIDIS (0x1u << 1) |

| (HSMCI_CR) Multi-Media Interface Disable More... | |

| #define | HSMCI_CR_MCIEN (0x1u << 0) |

| (HSMCI_CR) Multi-Media Interface Enable More... | |

| #define | HSMCI_CR_PWSDIS (0x1u << 3) |

| (HSMCI_CR) Power Save Mode Disable More... | |

| #define | HSMCI_CR_PWSEN (0x1u << 2) |

| (HSMCI_CR) Power Save Mode Enable More... | |

| #define | HSMCI_CR_SWRST (0x1u << 7) |

| (HSMCI_CR) Software Reset More... | |

| #define | HSMCI_CSTOR_CSTOCYC(value) ((HSMCI_CSTOR_CSTOCYC_Msk & ((value) << HSMCI_CSTOR_CSTOCYC_Pos))) |

| #define | HSMCI_CSTOR_CSTOCYC_Msk (0xfu << HSMCI_CSTOR_CSTOCYC_Pos) |

| (HSMCI_CSTOR) Completion Signal Timeout Cycle Number More... | |

| #define | HSMCI_CSTOR_CSTOCYC_Pos 0 |

| #define | HSMCI_CSTOR_CSTOMUL(value) ((HSMCI_CSTOR_CSTOMUL_Msk & ((value) << HSMCI_CSTOR_CSTOMUL_Pos))) |

| #define | HSMCI_CSTOR_CSTOMUL_1 (0x0u << 4) |

| (HSMCI_CSTOR) CSTOCYC x 1 More... | |

| #define | HSMCI_CSTOR_CSTOMUL_1024 (0x4u << 4) |

| (HSMCI_CSTOR) CSTOCYC x 1024 More... | |

| #define | HSMCI_CSTOR_CSTOMUL_1048576 (0x7u << 4) |

| (HSMCI_CSTOR) CSTOCYC x 1048576 More... | |

| #define | HSMCI_CSTOR_CSTOMUL_128 (0x2u << 4) |

| (HSMCI_CSTOR) CSTOCYC x 128 More... | |

| #define | HSMCI_CSTOR_CSTOMUL_16 (0x1u << 4) |

| (HSMCI_CSTOR) CSTOCYC x 16 More... | |

| #define | HSMCI_CSTOR_CSTOMUL_256 (0x3u << 4) |

| (HSMCI_CSTOR) CSTOCYC x 256 More... | |

| #define | HSMCI_CSTOR_CSTOMUL_4096 (0x5u << 4) |

| (HSMCI_CSTOR) CSTOCYC x 4096 More... | |

| #define | HSMCI_CSTOR_CSTOMUL_65536 (0x6u << 4) |

| (HSMCI_CSTOR) CSTOCYC x 65536 More... | |

| #define | HSMCI_CSTOR_CSTOMUL_Msk (0x7u << HSMCI_CSTOR_CSTOMUL_Pos) |

| (HSMCI_CSTOR) Completion Signal Timeout Multiplier More... | |

| #define | HSMCI_CSTOR_CSTOMUL_Pos 4 |

| #define | HSMCI_DMA_CHKSIZE(value) ((HSMCI_DMA_CHKSIZE_Msk & ((value) << HSMCI_DMA_CHKSIZE_Pos))) |

| #define | HSMCI_DMA_CHKSIZE_1 (0x0u << 4) |

| (HSMCI_DMA) 1 data available More... | |

| #define | HSMCI_DMA_CHKSIZE_16 (0x4u << 4) |

| (HSMCI_DMA) 16 data available More... | |

| #define | HSMCI_DMA_CHKSIZE_2 (0x1u << 4) |

| (HSMCI_DMA) 2 data available More... | |

| #define | HSMCI_DMA_CHKSIZE_4 (0x2u << 4) |

| (HSMCI_DMA) 4 data available More... | |

| #define | HSMCI_DMA_CHKSIZE_8 (0x3u << 4) |

| (HSMCI_DMA) 8 data available More... | |

| #define | HSMCI_DMA_CHKSIZE_Msk (0x7u << HSMCI_DMA_CHKSIZE_Pos) |

| (HSMCI_DMA) DMA Channel Read and Write Chunk Size More... | |

| #define | HSMCI_DMA_CHKSIZE_Pos 4 |

| #define | HSMCI_DMA_DMAEN (0x1u << 8) |

| (HSMCI_DMA) DMA Hardware Handshaking Enable More... | |

| #define | HSMCI_DTOR_DTOCYC(value) ((HSMCI_DTOR_DTOCYC_Msk & ((value) << HSMCI_DTOR_DTOCYC_Pos))) |

| #define | HSMCI_DTOR_DTOCYC_Msk (0xfu << HSMCI_DTOR_DTOCYC_Pos) |

| (HSMCI_DTOR) Data Timeout Cycle Number More... | |

| #define | HSMCI_DTOR_DTOCYC_Pos 0 |

| #define | HSMCI_DTOR_DTOMUL(value) ((HSMCI_DTOR_DTOMUL_Msk & ((value) << HSMCI_DTOR_DTOMUL_Pos))) |

| #define | HSMCI_DTOR_DTOMUL_1 (0x0u << 4) |

| (HSMCI_DTOR) DTOCYC More... | |

| #define | HSMCI_DTOR_DTOMUL_1024 (0x4u << 4) |

| (HSMCI_DTOR) DTOCYC x 1024 More... | |

| #define | HSMCI_DTOR_DTOMUL_1048576 (0x7u << 4) |

| (HSMCI_DTOR) DTOCYC x 1048576 More... | |

| #define | HSMCI_DTOR_DTOMUL_128 (0x2u << 4) |

| (HSMCI_DTOR) DTOCYC x 128 More... | |

| #define | HSMCI_DTOR_DTOMUL_16 (0x1u << 4) |

| (HSMCI_DTOR) DTOCYC x 16 More... | |

| #define | HSMCI_DTOR_DTOMUL_256 (0x3u << 4) |

| (HSMCI_DTOR) DTOCYC x 256 More... | |

| #define | HSMCI_DTOR_DTOMUL_4096 (0x5u << 4) |

| (HSMCI_DTOR) DTOCYC x 4096 More... | |

| #define | HSMCI_DTOR_DTOMUL_65536 (0x6u << 4) |

| (HSMCI_DTOR) DTOCYC x 65536 More... | |

| #define | HSMCI_DTOR_DTOMUL_Msk (0x7u << HSMCI_DTOR_DTOMUL_Pos) |

| (HSMCI_DTOR) Data Timeout Multiplier More... | |

| #define | HSMCI_DTOR_DTOMUL_Pos 4 |

| #define | HSMCI_FIFO_DATA(value) ((HSMCI_FIFO_DATA_Msk & ((value) << HSMCI_FIFO_DATA_Pos))) |

| #define | HSMCI_FIFO_DATA_Msk (0xffffffffu << HSMCI_FIFO_DATA_Pos) |

| (HSMCI_FIFO[256]) Data to Read or Data to Write More... | |

| #define | HSMCI_FIFO_DATA_Pos 0 |

| #define | HSMCI_IDR_ACKRCV (0x1u << 28) |

| (HSMCI_IDR) Boot Acknowledge Interrupt Disable More... | |

| #define | HSMCI_IDR_ACKRCVE (0x1u << 29) |

| (HSMCI_IDR) Boot Acknowledge Error Interrupt Disable More... | |

| #define | HSMCI_IDR_BLKE (0x1u << 3) |

| (HSMCI_IDR) Data Block Ended Interrupt Disable More... | |

| #define | HSMCI_IDR_BLKOVRE (0x1u << 24) |

| (HSMCI_IDR) DMA Block Overrun Error Interrupt Disable More... | |

| #define | HSMCI_IDR_CMDRDY (0x1u << 0) |

| (HSMCI_IDR) Command Ready Interrupt Disable More... | |

| #define | HSMCI_IDR_CSRCV (0x1u << 13) |

| (HSMCI_IDR) Completion Signal received interrupt Disable More... | |

| #define | HSMCI_IDR_CSTOE (0x1u << 23) |

| (HSMCI_IDR) Completion Signal Time out Error Interrupt Disable More... | |

| #define | HSMCI_IDR_DCRCE (0x1u << 21) |

| (HSMCI_IDR) Data CRC Error Interrupt Disable More... | |

| #define | HSMCI_IDR_DTIP (0x1u << 4) |

| (HSMCI_IDR) Data Transfer in Progress Interrupt Disable More... | |

| #define | HSMCI_IDR_DTOE (0x1u << 22) |

| (HSMCI_IDR) Data Time-out Error Interrupt Disable More... | |

| #define | HSMCI_IDR_FIFOEMPTY (0x1u << 26) |

| (HSMCI_IDR) FIFO empty Interrupt Disable More... | |

| #define | HSMCI_IDR_NOTBUSY (0x1u << 5) |

| (HSMCI_IDR) Data Not Busy Interrupt Disable More... | |

| #define | HSMCI_IDR_OVRE (0x1u << 30) |

| (HSMCI_IDR) Overrun Interrupt Disable More... | |

| #define | HSMCI_IDR_RCRCE (0x1u << 18) |

| (HSMCI_IDR) Response CRC Error Interrupt Disable More... | |

| #define | HSMCI_IDR_RDIRE (0x1u << 17) |

| (HSMCI_IDR) Response Direction Error Interrupt Disable More... | |

| #define | HSMCI_IDR_RENDE (0x1u << 19) |

| (HSMCI_IDR) Response End Bit Error Interrupt Disable More... | |

| #define | HSMCI_IDR_RINDE (0x1u << 16) |

| (HSMCI_IDR) Response Index Error Interrupt Disable More... | |

| #define | HSMCI_IDR_RTOE (0x1u << 20) |

| (HSMCI_IDR) Response Time-out Error Interrupt Disable More... | |

| #define | HSMCI_IDR_RXRDY (0x1u << 1) |

| (HSMCI_IDR) Receiver Ready Interrupt Disable More... | |

| #define | HSMCI_IDR_SDIOIRQA (0x1u << 8) |

| (HSMCI_IDR) SDIO Interrupt for Slot A Interrupt Disable More... | |

| #define | HSMCI_IDR_SDIOWAIT (0x1u << 12) |

| (HSMCI_IDR) SDIO Read Wait Operation Status Interrupt Disable More... | |

| #define | HSMCI_IDR_TXRDY (0x1u << 2) |

| (HSMCI_IDR) Transmit Ready Interrupt Disable More... | |

| #define | HSMCI_IDR_UNRE (0x1u << 31) |

| (HSMCI_IDR) Underrun Interrupt Disable More... | |

| #define | HSMCI_IDR_XFRDONE (0x1u << 27) |

| (HSMCI_IDR) Transfer Done Interrupt Disable More... | |

| #define | HSMCI_IER_ACKRCV (0x1u << 28) |

| (HSMCI_IER) Boot Acknowledge Interrupt Enable More... | |

| #define | HSMCI_IER_ACKRCVE (0x1u << 29) |

| (HSMCI_IER) Boot Acknowledge Error Interrupt Enable More... | |

| #define | HSMCI_IER_BLKE (0x1u << 3) |

| (HSMCI_IER) Data Block Ended Interrupt Enable More... | |

| #define | HSMCI_IER_BLKOVRE (0x1u << 24) |

| (HSMCI_IER) DMA Block Overrun Error Interrupt Enable More... | |

| #define | HSMCI_IER_CMDRDY (0x1u << 0) |

| (HSMCI_IER) Command Ready Interrupt Enable More... | |

| #define | HSMCI_IER_CSRCV (0x1u << 13) |

| (HSMCI_IER) Completion Signal Received Interrupt Enable More... | |

| #define | HSMCI_IER_CSTOE (0x1u << 23) |

| (HSMCI_IER) Completion Signal Timeout Error Interrupt Enable More... | |

| #define | HSMCI_IER_DCRCE (0x1u << 21) |

| (HSMCI_IER) Data CRC Error Interrupt Enable More... | |

| #define | HSMCI_IER_DTIP (0x1u << 4) |

| (HSMCI_IER) Data Transfer in Progress Interrupt Enable More... | |

| #define | HSMCI_IER_DTOE (0x1u << 22) |

| (HSMCI_IER) Data Time-out Error Interrupt Enable More... | |

| #define | HSMCI_IER_FIFOEMPTY (0x1u << 26) |

| (HSMCI_IER) FIFO empty Interrupt enable More... | |

| #define | HSMCI_IER_NOTBUSY (0x1u << 5) |

| (HSMCI_IER) Data Not Busy Interrupt Enable More... | |

| #define | HSMCI_IER_OVRE (0x1u << 30) |

| (HSMCI_IER) Overrun Interrupt Enable More... | |

| #define | HSMCI_IER_RCRCE (0x1u << 18) |

| (HSMCI_IER) Response CRC Error Interrupt Enable More... | |

| #define | HSMCI_IER_RDIRE (0x1u << 17) |

| (HSMCI_IER) Response Direction Error Interrupt Enable More... | |

| #define | HSMCI_IER_RENDE (0x1u << 19) |

| (HSMCI_IER) Response End Bit Error Interrupt Enable More... | |

| #define | HSMCI_IER_RINDE (0x1u << 16) |

| (HSMCI_IER) Response Index Error Interrupt Enable More... | |

| #define | HSMCI_IER_RTOE (0x1u << 20) |

| (HSMCI_IER) Response Time-out Error Interrupt Enable More... | |

| #define | HSMCI_IER_RXRDY (0x1u << 1) |

| (HSMCI_IER) Receiver Ready Interrupt Enable More... | |

| #define | HSMCI_IER_SDIOIRQA (0x1u << 8) |

| (HSMCI_IER) SDIO Interrupt for Slot A Interrupt Enable More... | |

| #define | HSMCI_IER_SDIOWAIT (0x1u << 12) |

| (HSMCI_IER) SDIO Read Wait Operation Status Interrupt Enable More... | |

| #define | HSMCI_IER_TXRDY (0x1u << 2) |

| (HSMCI_IER) Transmit Ready Interrupt Enable More... | |

| #define | HSMCI_IER_UNRE (0x1u << 31) |

| (HSMCI_IER) Underrun Interrupt Enable More... | |

| #define | HSMCI_IER_XFRDONE (0x1u << 27) |

| (HSMCI_IER) Transfer Done Interrupt enable More... | |

| #define | HSMCI_IMR_ACKRCV (0x1u << 28) |

| (HSMCI_IMR) Boot Operation Acknowledge Received Interrupt Mask More... | |

| #define | HSMCI_IMR_ACKRCVE (0x1u << 29) |

| (HSMCI_IMR) Boot Operation Acknowledge Error Interrupt Mask More... | |

| #define | HSMCI_IMR_BLKE (0x1u << 3) |

| (HSMCI_IMR) Data Block Ended Interrupt Mask More... | |

| #define | HSMCI_IMR_BLKOVRE (0x1u << 24) |

| (HSMCI_IMR) DMA Block Overrun Error Interrupt Mask More... | |

| #define | HSMCI_IMR_CMDRDY (0x1u << 0) |

| (HSMCI_IMR) Command Ready Interrupt Mask More... | |

| #define | HSMCI_IMR_CSRCV (0x1u << 13) |

| (HSMCI_IMR) Completion Signal Received Interrupt Mask More... | |

| #define | HSMCI_IMR_CSTOE (0x1u << 23) |

| (HSMCI_IMR) Completion Signal Time-out Error Interrupt Mask More... | |

| #define | HSMCI_IMR_DCRCE (0x1u << 21) |

| (HSMCI_IMR) Data CRC Error Interrupt Mask More... | |

| #define | HSMCI_IMR_DTIP (0x1u << 4) |

| (HSMCI_IMR) Data Transfer in Progress Interrupt Mask More... | |

| #define | HSMCI_IMR_DTOE (0x1u << 22) |

| (HSMCI_IMR) Data Time-out Error Interrupt Mask More... | |

| #define | HSMCI_IMR_FIFOEMPTY (0x1u << 26) |

| (HSMCI_IMR) FIFO Empty Interrupt Mask More... | |

| #define | HSMCI_IMR_NOTBUSY (0x1u << 5) |

| (HSMCI_IMR) Data Not Busy Interrupt Mask More... | |

| #define | HSMCI_IMR_OVRE (0x1u << 30) |

| (HSMCI_IMR) Overrun Interrupt Mask More... | |

| #define | HSMCI_IMR_RCRCE (0x1u << 18) |

| (HSMCI_IMR) Response CRC Error Interrupt Mask More... | |

| #define | HSMCI_IMR_RDIRE (0x1u << 17) |

| (HSMCI_IMR) Response Direction Error Interrupt Mask More... | |

| #define | HSMCI_IMR_RENDE (0x1u << 19) |

| (HSMCI_IMR) Response End Bit Error Interrupt Mask More... | |

| #define | HSMCI_IMR_RINDE (0x1u << 16) |

| (HSMCI_IMR) Response Index Error Interrupt Mask More... | |

| #define | HSMCI_IMR_RTOE (0x1u << 20) |

| (HSMCI_IMR) Response Time-out Error Interrupt Mask More... | |

| #define | HSMCI_IMR_RXRDY (0x1u << 1) |

| (HSMCI_IMR) Receiver Ready Interrupt Mask More... | |

| #define | HSMCI_IMR_SDIOIRQA (0x1u << 8) |

| (HSMCI_IMR) SDIO Interrupt for Slot A Interrupt Mask More... | |

| #define | HSMCI_IMR_SDIOWAIT (0x1u << 12) |

| (HSMCI_IMR) SDIO Read Wait Operation Status Interrupt Mask More... | |

| #define | HSMCI_IMR_TXRDY (0x1u << 2) |

| (HSMCI_IMR) Transmit Ready Interrupt Mask More... | |

| #define | HSMCI_IMR_UNRE (0x1u << 31) |

| (HSMCI_IMR) Underrun Interrupt Mask More... | |

| #define | HSMCI_IMR_XFRDONE (0x1u << 27) |

| (HSMCI_IMR) Transfer Done Interrupt Mask More... | |

| #define | HSMCI_MR_CLKDIV(value) ((HSMCI_MR_CLKDIV_Msk & ((value) << HSMCI_MR_CLKDIV_Pos))) |

| #define | HSMCI_MR_CLKDIV_Msk (0xffu << HSMCI_MR_CLKDIV_Pos) |

| (HSMCI_MR) Clock Divider More... | |

| #define | HSMCI_MR_CLKDIV_Pos 0 |

| #define | HSMCI_MR_CLKODD (0x1u << 16) |

| (HSMCI_MR) Clock divider is odd More... | |

| #define | HSMCI_MR_FBYTE (0x1u << 13) |

| (HSMCI_MR) Force Byte Transfer More... | |

| #define | HSMCI_MR_PADV (0x1u << 14) |

| (HSMCI_MR) Padding Value More... | |

| #define | HSMCI_MR_PWSDIV(value) ((HSMCI_MR_PWSDIV_Msk & ((value) << HSMCI_MR_PWSDIV_Pos))) |

| #define | HSMCI_MR_PWSDIV_Msk (0x7u << HSMCI_MR_PWSDIV_Pos) |

| (HSMCI_MR) Power Saving Divider More... | |

| #define | HSMCI_MR_PWSDIV_Pos 8 |

| #define | HSMCI_MR_RDPROOF (0x1u << 11) |

| (HSMCI_MR) Read Proof Enable More... | |

| #define | HSMCI_MR_WRPROOF (0x1u << 12) |

| (HSMCI_MR) Write Proof Enable More... | |

| #define | HSMCI_RDR_DATA_Msk (0xffffffffu << HSMCI_RDR_DATA_Pos) |

| (HSMCI_RDR) Data to Read More... | |

| #define | HSMCI_RDR_DATA_Pos 0 |

| #define | HSMCI_RSPR_RSP_Msk (0xffffffffu << HSMCI_RSPR_RSP_Pos) |

| (HSMCI_RSPR[4]) Response More... | |

| #define | HSMCI_RSPR_RSP_Pos 0 |

| #define | HSMCI_SDCR_SDCBUS(value) ((HSMCI_SDCR_SDCBUS_Msk & ((value) << HSMCI_SDCR_SDCBUS_Pos))) |

| #define | HSMCI_SDCR_SDCBUS_1 (0x0u << 6) |

| (HSMCI_SDCR) 1 bit More... | |

| #define | HSMCI_SDCR_SDCBUS_4 (0x2u << 6) |

| (HSMCI_SDCR) 4 bits More... | |

| #define | HSMCI_SDCR_SDCBUS_8 (0x3u << 6) |

| (HSMCI_SDCR) 8 bits More... | |

| #define | HSMCI_SDCR_SDCBUS_Msk (0x3u << HSMCI_SDCR_SDCBUS_Pos) |

| (HSMCI_SDCR) SDCard/SDIO Bus Width More... | |

| #define | HSMCI_SDCR_SDCBUS_Pos 6 |

| #define | HSMCI_SDCR_SDCSEL(value) ((HSMCI_SDCR_SDCSEL_Msk & ((value) << HSMCI_SDCR_SDCSEL_Pos))) |

| #define | HSMCI_SDCR_SDCSEL_Msk (0x3u << HSMCI_SDCR_SDCSEL_Pos) |

| (HSMCI_SDCR) SDCard/SDIO Slot More... | |

| #define | HSMCI_SDCR_SDCSEL_Pos 0 |

| #define | HSMCI_SDCR_SDCSEL_SLOTA (0x0u << 0) |

| (HSMCI_SDCR) Slot A is selected. More... | |

| #define | HSMCI_SR_ACKRCV (0x1u << 28) |

| (HSMCI_SR) Boot Operation Acknowledge Received (cleared on read) More... | |

| #define | HSMCI_SR_ACKRCVE (0x1u << 29) |

| (HSMCI_SR) Boot Operation Acknowledge Error (cleared on read) More... | |

| #define | HSMCI_SR_BLKE (0x1u << 3) |

| (HSMCI_SR) Data Block Ended (cleared on read) More... | |

| #define | HSMCI_SR_BLKOVRE (0x1u << 24) |

| (HSMCI_SR) DMA Block Overrun Error (cleared on read) More... | |

| #define | HSMCI_SR_CMDRDY (0x1u << 0) |

| (HSMCI_SR) Command Ready (cleared by writing in HSMCI_CMDR) More... | |

| #define | HSMCI_SR_CSRCV (0x1u << 13) |

| (HSMCI_SR) CE-ATA Completion Signal Received (cleared on read) More... | |

| #define | HSMCI_SR_CSTOE (0x1u << 23) |

| (HSMCI_SR) Completion Signal Time-out Error (cleared on read) More... | |

| #define | HSMCI_SR_DCRCE (0x1u << 21) |

| (HSMCI_SR) Data CRC Error (cleared on read) More... | |

| #define | HSMCI_SR_DTIP (0x1u << 4) |

| (HSMCI_SR) Data Transfer in Progress (cleared at the end of CRC16 calculation) More... | |

| #define | HSMCI_SR_DTOE (0x1u << 22) |

| (HSMCI_SR) Data Time-out Error (cleared on read) More... | |

| #define | HSMCI_SR_FIFOEMPTY (0x1u << 26) |

| (HSMCI_SR) FIFO empty flag More... | |

| #define | HSMCI_SR_NOTBUSY (0x1u << 5) |

| (HSMCI_SR) HSMCI Not Busy More... | |

| #define | HSMCI_SR_OVRE (0x1u << 30) |

| (HSMCI_SR) Overrun (if FERRCTRL = 1, cleared by writing in HSMCI_CMDR or cleared on read if FERRCTRL = 0) More... | |

| #define | HSMCI_SR_RCRCE (0x1u << 18) |

| (HSMCI_SR) Response CRC Error (cleared by writing in HSMCI_CMDR) More... | |

| #define | HSMCI_SR_RDIRE (0x1u << 17) |

| (HSMCI_SR) Response Direction Error (cleared by writing in HSMCI_CMDR) More... | |

| #define | HSMCI_SR_RENDE (0x1u << 19) |

| (HSMCI_SR) Response End Bit Error (cleared by writing in HSMCI_CMDR) More... | |

| #define | HSMCI_SR_RINDE (0x1u << 16) |

| (HSMCI_SR) Response Index Error (cleared by writing in HSMCI_CMDR) More... | |

| #define | HSMCI_SR_RTOE (0x1u << 20) |

| (HSMCI_SR) Response Time-out Error (cleared by writing in HSMCI_CMDR) More... | |

| #define | HSMCI_SR_RXRDY (0x1u << 1) |

| (HSMCI_SR) Receiver Ready (cleared by reading HSMCI_RDR) More... | |

| #define | HSMCI_SR_SDIOIRQA (0x1u << 8) |

| (HSMCI_SR) SDIO Interrupt for Slot A (cleared on read) More... | |

| #define | HSMCI_SR_SDIOWAIT (0x1u << 12) |

| (HSMCI_SR) SDIO Read Wait Operation Status More... | |

| #define | HSMCI_SR_TXRDY (0x1u << 2) |

| (HSMCI_SR) Transmit Ready (cleared by writing in HSMCI_TDR) More... | |

| #define | HSMCI_SR_UNRE (0x1u << 31) |

| (HSMCI_SR) Underrun (if FERRCTRL = 1, cleared by writing in HSMCI_CMDR or cleared on read if FERRCTRL = 0) More... | |

| #define | HSMCI_SR_XFRDONE (0x1u << 27) |

| (HSMCI_SR) Transfer Done flag More... | |

| #define | HSMCI_TDR_DATA(value) ((HSMCI_TDR_DATA_Msk & ((value) << HSMCI_TDR_DATA_Pos))) |

| #define | HSMCI_TDR_DATA_Msk (0xffffffffu << HSMCI_TDR_DATA_Pos) |

| (HSMCI_TDR) Data to Write More... | |

| #define | HSMCI_TDR_DATA_Pos 0 |

| #define | HSMCI_VERSION_MFN_Msk (0x7u << HSMCI_VERSION_MFN_Pos) |

| (HSMCI_VERSION) Metal Fix Number More... | |

| #define | HSMCI_VERSION_MFN_Pos 16 |

| #define | HSMCI_VERSION_VERSION_Msk (0xfffu << HSMCI_VERSION_VERSION_Pos) |

| (HSMCI_VERSION) Hardware Module Version More... | |

| #define | HSMCI_VERSION_VERSION_Pos 0 |

| #define | HSMCI_WPMR_WPEN (0x1u << 0) |

| (HSMCI_WPMR) Write Protect Enable More... | |

| #define | HSMCI_WPMR_WPKEY(value) ((HSMCI_WPMR_WPKEY_Msk & ((value) << HSMCI_WPMR_WPKEY_Pos))) |

| #define | HSMCI_WPMR_WPKEY_Msk (0xffffffu << HSMCI_WPMR_WPKEY_Pos) |

| (HSMCI_WPMR) Write Protect Key More... | |

| #define | HSMCI_WPMR_WPKEY_PASSWD (0x4D4349u << 8) |

| (HSMCI_WPMR) Writing any other value in this field aborts the write operation of the WPEN bit.Always reads as 0. More... | |

| #define | HSMCI_WPMR_WPKEY_Pos 8 |

| #define | HSMCI_WPSR_WPVS (0x1u << 0) |

| (HSMCI_WPSR) Write Protection Violation Status More... | |

| #define | HSMCI_WPSR_WPVSRC_Msk (0xffffu << HSMCI_WPSR_WPVSRC_Pos) |

| (HSMCI_WPSR) Write Protection Violation Source More... | |

| #define | HSMCI_WPSR_WPVSRC_Pos 8 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file utils/cmsis/same70/include/component/hsmci.h.