Chip-specific PLL definitions. More...

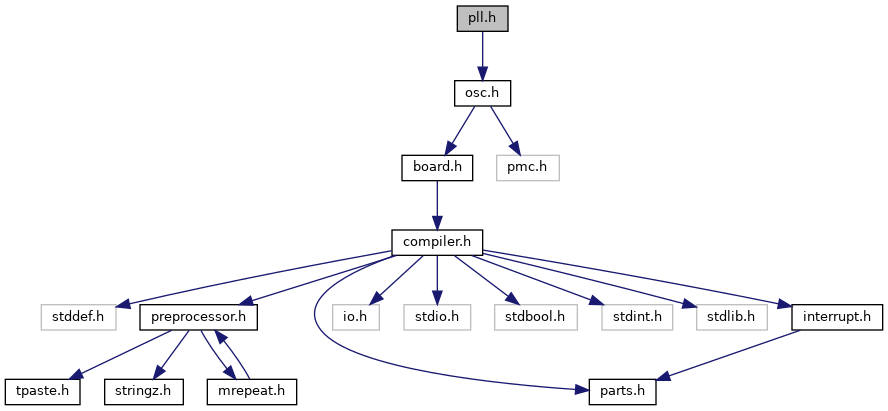

#include <osc.h>

Include dependency graph for same70/pll.h:

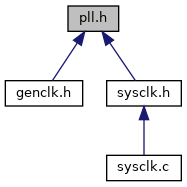

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | pll_config |

| Hardware-specific representation of PLL configuration. More... | |

Macros | |

| #define | CONFIG_PLL1_DIV 0 |

| #define | CONFIG_PLL1_MUL 0 |

| #define | CONFIG_PLL1_SOURCE PLL_SRC_MAINCK_XTAL |

| #define | PLL_COUNT 0x3fU |

| #define | PLL_INPUT_MAX_HZ 32000000 |

| #define | PLL_INPUT_MIN_HZ 3000000 |

| #define | PLL_OUTPUT_MAX_HZ 500000000 |

| #define | PLL_OUTPUT_MIN_HZ 160000000 |

| #define | PLL_UPLL_HZ 480000000 |

| #define | PLLA_ID 0 |

| #define | UPLL_ID 1 |

| USB UTMI PLL. More... | |

Chip-specific PLL characteristics | |

| #define | NR_PLLS 2 |

| Number of on-chip PLLs. More... | |

PLL configuration | |

| #define | pll_get_default_rate(pll_id) |

| Get the default rate in Hz of pll_id. More... | |

| #define | pll_config_defaults(cfg, pll_id) |

| Initialize PLL configuration using default parameters. More... | |

Enumerations | |

| enum | pll_source { PLL_SRC_MAINCK_4M_RC = OSC_MAINCK_4M_RC, PLL_SRC_MAINCK_8M_RC = OSC_MAINCK_8M_RC, PLL_SRC_MAINCK_12M_RC = OSC_MAINCK_12M_RC, PLL_SRC_MAINCK_XTAL = OSC_MAINCK_XTAL, PLL_SRC_MAINCK_BYPASS = OSC_MAINCK_BYPASS, PLL_NR_SOURCES } |

| PLL clock source. More... | |

Functions | |

| static void | pll_config_init (struct pll_config *p_cfg, enum pll_source e_src, uint32_t ul_div, uint32_t ul_mul) |

| static void | pll_config_read (struct pll_config *p_cfg, uint32_t ul_pll_id) |

| static void | pll_config_write (const struct pll_config *p_cfg, uint32_t ul_pll_id) |

| static void | pll_disable (uint32_t ul_pll_id) |

| static void | pll_enable (const struct pll_config *p_cfg, uint32_t ul_pll_id) |

| static uint32_t | pll_is_locked (uint32_t ul_pll_id) |

Interaction with the PLL hardware | |

| static void | pll_enable_source (enum pll_source e_src) |

| Enable the source of the pll. The source is enabled, if the source is not already running. More... | |

| static void | pll_enable_config_defaults (unsigned int ul_pll_id) |

| Enable the pll with the default configuration. PLL is enabled, if the PLL is not already locked. More... | |

Detailed Description

Chip-specific PLL definitions.

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file same70/pll.h.