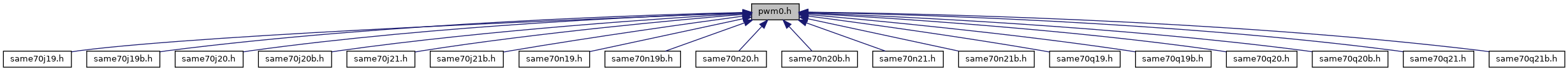

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | REG_PWM0_CCNT0 (*(__I uint32_t*)0x40020214U) |

| (PWM0) PWM Channel Counter Register (ch_num = 0) More... | |

| #define | REG_PWM0_CCNT1 (*(__I uint32_t*)0x40020234U) |

| (PWM0) PWM Channel Counter Register (ch_num = 1) More... | |

| #define | REG_PWM0_CCNT2 (*(__I uint32_t*)0x40020254U) |

| (PWM0) PWM Channel Counter Register (ch_num = 2) More... | |

| #define | REG_PWM0_CCNT3 (*(__I uint32_t*)0x40020274U) |

| (PWM0) PWM Channel Counter Register (ch_num = 3) More... | |

| #define | REG_PWM0_CDTY0 (*(__IO uint32_t*)0x40020204U) |

| (PWM0) PWM Channel Duty Cycle Register (ch_num = 0) More... | |

| #define | REG_PWM0_CDTY1 (*(__IO uint32_t*)0x40020224U) |

| (PWM0) PWM Channel Duty Cycle Register (ch_num = 1) More... | |

| #define | REG_PWM0_CDTY2 (*(__IO uint32_t*)0x40020244U) |

| (PWM0) PWM Channel Duty Cycle Register (ch_num = 2) More... | |

| #define | REG_PWM0_CDTY3 (*(__IO uint32_t*)0x40020264U) |

| (PWM0) PWM Channel Duty Cycle Register (ch_num = 3) More... | |

| #define | REG_PWM0_CDTYUPD0 (*(__O uint32_t*)0x40020208U) |

| (PWM0) PWM Channel Duty Cycle Update Register (ch_num = 0) More... | |

| #define | REG_PWM0_CDTYUPD1 (*(__O uint32_t*)0x40020228U) |

| (PWM0) PWM Channel Duty Cycle Update Register (ch_num = 1) More... | |

| #define | REG_PWM0_CDTYUPD2 (*(__O uint32_t*)0x40020248U) |

| (PWM0) PWM Channel Duty Cycle Update Register (ch_num = 2) More... | |

| #define | REG_PWM0_CDTYUPD3 (*(__O uint32_t*)0x40020268U) |

| (PWM0) PWM Channel Duty Cycle Update Register (ch_num = 3) More... | |

| #define | REG_PWM0_CLK (*(__IO uint32_t*)0x40020000U) |

| (PWM0) PWM Clock Register More... | |

| #define | REG_PWM0_CMPM0 (*(__IO uint32_t*)0x40020138U) |

| (PWM0) PWM Comparison 0 Mode Register More... | |

| #define | REG_PWM0_CMPM1 (*(__IO uint32_t*)0x40020148U) |

| (PWM0) PWM Comparison 1 Mode Register More... | |

| #define | REG_PWM0_CMPM2 (*(__IO uint32_t*)0x40020158U) |

| (PWM0) PWM Comparison 2 Mode Register More... | |

| #define | REG_PWM0_CMPM3 (*(__IO uint32_t*)0x40020168U) |

| (PWM0) PWM Comparison 3 Mode Register More... | |

| #define | REG_PWM0_CMPM4 (*(__IO uint32_t*)0x40020178U) |

| (PWM0) PWM Comparison 4 Mode Register More... | |

| #define | REG_PWM0_CMPM5 (*(__IO uint32_t*)0x40020188U) |

| (PWM0) PWM Comparison 5 Mode Register More... | |

| #define | REG_PWM0_CMPM6 (*(__IO uint32_t*)0x40020198U) |

| (PWM0) PWM Comparison 6 Mode Register More... | |

| #define | REG_PWM0_CMPM7 (*(__IO uint32_t*)0x400201A8U) |

| (PWM0) PWM Comparison 7 Mode Register More... | |

| #define | REG_PWM0_CMPMUPD0 (*(__O uint32_t*)0x4002013CU) |

| (PWM0) PWM Comparison 0 Mode Update Register More... | |

| #define | REG_PWM0_CMPMUPD1 (*(__O uint32_t*)0x4002014CU) |

| (PWM0) PWM Comparison 1 Mode Update Register More... | |

| #define | REG_PWM0_CMPMUPD2 (*(__O uint32_t*)0x4002015CU) |

| (PWM0) PWM Comparison 2 Mode Update Register More... | |

| #define | REG_PWM0_CMPMUPD3 (*(__O uint32_t*)0x4002016CU) |

| (PWM0) PWM Comparison 3 Mode Update Register More... | |

| #define | REG_PWM0_CMPMUPD4 (*(__O uint32_t*)0x4002017CU) |

| (PWM0) PWM Comparison 4 Mode Update Register More... | |

| #define | REG_PWM0_CMPMUPD5 (*(__O uint32_t*)0x4002018CU) |

| (PWM0) PWM Comparison 5 Mode Update Register More... | |

| #define | REG_PWM0_CMPMUPD6 (*(__O uint32_t*)0x4002019CU) |

| (PWM0) PWM Comparison 6 Mode Update Register More... | |

| #define | REG_PWM0_CMPMUPD7 (*(__O uint32_t*)0x400201ACU) |

| (PWM0) PWM Comparison 7 Mode Update Register More... | |

| #define | REG_PWM0_CMPV0 (*(__IO uint32_t*)0x40020130U) |

| (PWM0) PWM Comparison 0 Value Register More... | |

| #define | REG_PWM0_CMPV1 (*(__IO uint32_t*)0x40020140U) |

| (PWM0) PWM Comparison 1 Value Register More... | |

| #define | REG_PWM0_CMPV2 (*(__IO uint32_t*)0x40020150U) |

| (PWM0) PWM Comparison 2 Value Register More... | |

| #define | REG_PWM0_CMPV3 (*(__IO uint32_t*)0x40020160U) |

| (PWM0) PWM Comparison 3 Value Register More... | |

| #define | REG_PWM0_CMPV4 (*(__IO uint32_t*)0x40020170U) |

| (PWM0) PWM Comparison 4 Value Register More... | |

| #define | REG_PWM0_CMPV5 (*(__IO uint32_t*)0x40020180U) |

| (PWM0) PWM Comparison 5 Value Register More... | |

| #define | REG_PWM0_CMPV6 (*(__IO uint32_t*)0x40020190U) |

| (PWM0) PWM Comparison 6 Value Register More... | |

| #define | REG_PWM0_CMPV7 (*(__IO uint32_t*)0x400201A0U) |

| (PWM0) PWM Comparison 7 Value Register More... | |

| #define | REG_PWM0_CMPVUPD0 (*(__O uint32_t*)0x40020134U) |

| (PWM0) PWM Comparison 0 Value Update Register More... | |

| #define | REG_PWM0_CMPVUPD1 (*(__O uint32_t*)0x40020144U) |

| (PWM0) PWM Comparison 1 Value Update Register More... | |

| #define | REG_PWM0_CMPVUPD2 (*(__O uint32_t*)0x40020154U) |

| (PWM0) PWM Comparison 2 Value Update Register More... | |

| #define | REG_PWM0_CMPVUPD3 (*(__O uint32_t*)0x40020164U) |

| (PWM0) PWM Comparison 3 Value Update Register More... | |

| #define | REG_PWM0_CMPVUPD4 (*(__O uint32_t*)0x40020174U) |

| (PWM0) PWM Comparison 4 Value Update Register More... | |

| #define | REG_PWM0_CMPVUPD5 (*(__O uint32_t*)0x40020184U) |

| (PWM0) PWM Comparison 5 Value Update Register More... | |

| #define | REG_PWM0_CMPVUPD6 (*(__O uint32_t*)0x40020194U) |

| (PWM0) PWM Comparison 6 Value Update Register More... | |

| #define | REG_PWM0_CMPVUPD7 (*(__O uint32_t*)0x400201A4U) |

| (PWM0) PWM Comparison 7 Value Update Register More... | |

| #define | REG_PWM0_CMR0 (*(__IO uint32_t*)0x40020200U) |

| (PWM0) PWM Channel Mode Register (ch_num = 0) More... | |

| #define | REG_PWM0_CMR1 (*(__IO uint32_t*)0x40020220U) |

| (PWM0) PWM Channel Mode Register (ch_num = 1) More... | |

| #define | REG_PWM0_CMR2 (*(__IO uint32_t*)0x40020240U) |

| (PWM0) PWM Channel Mode Register (ch_num = 2) More... | |

| #define | REG_PWM0_CMR3 (*(__IO uint32_t*)0x40020260U) |

| (PWM0) PWM Channel Mode Register (ch_num = 3) More... | |

| #define | REG_PWM0_CMUPD0 (*(__O uint32_t*)0x40020400U) |

| (PWM0) PWM Channel Mode Update Register (ch_num = 0) More... | |

| #define | REG_PWM0_CMUPD1 (*(__O uint32_t*)0x40020420U) |

| (PWM0) PWM Channel Mode Update Register (ch_num = 1) More... | |

| #define | REG_PWM0_CMUPD2 (*(__O uint32_t*)0x40020440U) |

| (PWM0) PWM Channel Mode Update Register (ch_num = 2) More... | |

| #define | REG_PWM0_CMUPD3 (*(__O uint32_t*)0x40020460U) |

| (PWM0) PWM Channel Mode Update Register (ch_num = 3) More... | |

| #define | REG_PWM0_CPRD0 (*(__IO uint32_t*)0x4002020CU) |

| (PWM0) PWM Channel Period Register (ch_num = 0) More... | |

| #define | REG_PWM0_CPRD1 (*(__IO uint32_t*)0x4002022CU) |

| (PWM0) PWM Channel Period Register (ch_num = 1) More... | |

| #define | REG_PWM0_CPRD2 (*(__IO uint32_t*)0x4002024CU) |

| (PWM0) PWM Channel Period Register (ch_num = 2) More... | |

| #define | REG_PWM0_CPRD3 (*(__IO uint32_t*)0x4002026CU) |

| (PWM0) PWM Channel Period Register (ch_num = 3) More... | |

| #define | REG_PWM0_CPRDUPD0 (*(__O uint32_t*)0x40020210U) |

| (PWM0) PWM Channel Period Update Register (ch_num = 0) More... | |

| #define | REG_PWM0_CPRDUPD1 (*(__O uint32_t*)0x40020230U) |

| (PWM0) PWM Channel Period Update Register (ch_num = 1) More... | |

| #define | REG_PWM0_CPRDUPD2 (*(__O uint32_t*)0x40020250U) |

| (PWM0) PWM Channel Period Update Register (ch_num = 2) More... | |

| #define | REG_PWM0_CPRDUPD3 (*(__O uint32_t*)0x40020270U) |

| (PWM0) PWM Channel Period Update Register (ch_num = 3) More... | |

| #define | REG_PWM0_DIS (*(__O uint32_t*)0x40020008U) |

| (PWM0) PWM Disable Register More... | |

| #define | REG_PWM0_DMAR (*(__O uint32_t*)0x40020024U) |

| (PWM0) PWM DMA Register More... | |

| #define | REG_PWM0_DT0 (*(__IO uint32_t*)0x40020218U) |

| (PWM0) PWM Channel Dead Time Register (ch_num = 0) More... | |

| #define | REG_PWM0_DT1 (*(__IO uint32_t*)0x40020238U) |

| (PWM0) PWM Channel Dead Time Register (ch_num = 1) More... | |

| #define | REG_PWM0_DT2 (*(__IO uint32_t*)0x40020258U) |

| (PWM0) PWM Channel Dead Time Register (ch_num = 2) More... | |

| #define | REG_PWM0_DT3 (*(__IO uint32_t*)0x40020278U) |

| (PWM0) PWM Channel Dead Time Register (ch_num = 3) More... | |

| #define | REG_PWM0_DTUPD0 (*(__O uint32_t*)0x4002021CU) |

| (PWM0) PWM Channel Dead Time Update Register (ch_num = 0) More... | |

| #define | REG_PWM0_DTUPD1 (*(__O uint32_t*)0x4002023CU) |

| (PWM0) PWM Channel Dead Time Update Register (ch_num = 1) More... | |

| #define | REG_PWM0_DTUPD2 (*(__O uint32_t*)0x4002025CU) |

| (PWM0) PWM Channel Dead Time Update Register (ch_num = 2) More... | |

| #define | REG_PWM0_DTUPD3 (*(__O uint32_t*)0x4002027CU) |

| (PWM0) PWM Channel Dead Time Update Register (ch_num = 3) More... | |

| #define | REG_PWM0_ELMR (*(__IO uint32_t*)0x4002007CU) |

| (PWM0) PWM Event Line 0 Mode Register More... | |

| #define | REG_PWM0_ENA (*(__O uint32_t*)0x40020004U) |

| (PWM0) PWM Enable Register More... | |

| #define | REG_PWM0_ETRG1 (*(__IO uint32_t*)0x4002042CU) |

| (PWM0) PWM External Trigger Register (trg_num = 1) More... | |

| #define | REG_PWM0_ETRG2 (*(__IO uint32_t*)0x4002044CU) |

| (PWM0) PWM External Trigger Register (trg_num = 2) More... | |

| #define | REG_PWM0_FCR (*(__O uint32_t*)0x40020064U) |

| (PWM0) PWM Fault Clear Register More... | |

| #define | REG_PWM0_FMR (*(__IO uint32_t*)0x4002005CU) |

| (PWM0) PWM Fault Mode Register More... | |

| #define | REG_PWM0_FPE (*(__IO uint32_t*)0x4002006CU) |

| (PWM0) PWM Fault Protection Enable Register More... | |

| #define | REG_PWM0_FPV1 (*(__IO uint32_t*)0x40020068U) |

| (PWM0) PWM Fault Protection Value Register 1 More... | |

| #define | REG_PWM0_FPV2 (*(__IO uint32_t*)0x400200C0U) |

| (PWM0) PWM Fault Protection Value 2 Register More... | |

| #define | REG_PWM0_FSR (*(__I uint32_t*)0x40020060U) |

| (PWM0) PWM Fault Status Register More... | |

| #define | REG_PWM0_IDR1 (*(__O uint32_t*)0x40020014U) |

| (PWM0) PWM Interrupt Disable Register 1 More... | |

| #define | REG_PWM0_IDR2 (*(__O uint32_t*)0x40020038U) |

| (PWM0) PWM Interrupt Disable Register 2 More... | |

| #define | REG_PWM0_IER1 (*(__O uint32_t*)0x40020010U) |

| (PWM0) PWM Interrupt Enable Register 1 More... | |

| #define | REG_PWM0_IER2 (*(__O uint32_t*)0x40020034U) |

| (PWM0) PWM Interrupt Enable Register 2 More... | |

| #define | REG_PWM0_IMR1 (*(__I uint32_t*)0x40020018U) |

| (PWM0) PWM Interrupt Mask Register 1 More... | |

| #define | REG_PWM0_IMR2 (*(__I uint32_t*)0x4002003CU) |

| (PWM0) PWM Interrupt Mask Register 2 More... | |

| #define | REG_PWM0_ISR1 (*(__I uint32_t*)0x4002001CU) |

| (PWM0) PWM Interrupt Status Register 1 More... | |

| #define | REG_PWM0_ISR2 (*(__I uint32_t*)0x40020040U) |

| (PWM0) PWM Interrupt Status Register 2 More... | |

| #define | REG_PWM0_LEBR1 (*(__IO uint32_t*)0x40020430U) |

| (PWM0) PWM Leading-Edge Blanking Register (trg_num = 1) More... | |

| #define | REG_PWM0_LEBR2 (*(__IO uint32_t*)0x40020450U) |

| (PWM0) PWM Leading-Edge Blanking Register (trg_num = 2) More... | |

| #define | REG_PWM0_OOV (*(__IO uint32_t*)0x40020044U) |

| (PWM0) PWM Output Override Value Register More... | |

| #define | REG_PWM0_OS (*(__IO uint32_t*)0x40020048U) |

| (PWM0) PWM Output Selection Register More... | |

| #define | REG_PWM0_OSC (*(__O uint32_t*)0x40020050U) |

| (PWM0) PWM Output Selection Clear Register More... | |

| #define | REG_PWM0_OSCUPD (*(__O uint32_t*)0x40020058U) |

| (PWM0) PWM Output Selection Clear Update Register More... | |

| #define | REG_PWM0_OSS (*(__O uint32_t*)0x4002004CU) |

| (PWM0) PWM Output Selection Set Register More... | |

| #define | REG_PWM0_OSSUPD (*(__O uint32_t*)0x40020054U) |

| (PWM0) PWM Output Selection Set Update Register More... | |

| #define | REG_PWM0_SCM (*(__IO uint32_t*)0x40020020U) |

| (PWM0) PWM Sync Channels Mode Register More... | |

| #define | REG_PWM0_SCUC (*(__IO uint32_t*)0x40020028U) |

| (PWM0) PWM Sync Channels Update Control Register More... | |

| #define | REG_PWM0_SCUP (*(__IO uint32_t*)0x4002002CU) |

| (PWM0) PWM Sync Channels Update Period Register More... | |

| #define | REG_PWM0_SCUPUPD (*(__O uint32_t*)0x40020030U) |

| (PWM0) PWM Sync Channels Update Period Update Register More... | |

| #define | REG_PWM0_SMMR (*(__IO uint32_t*)0x400200B0U) |

| (PWM0) PWM Stepper Motor Mode Register More... | |

| #define | REG_PWM0_SR (*(__I uint32_t*)0x4002000CU) |

| (PWM0) PWM Status Register More... | |

| #define | REG_PWM0_SSPR (*(__IO uint32_t*)0x400200A0U) |

| (PWM0) PWM Spread Spectrum Register More... | |

| #define | REG_PWM0_SSPUP (*(__O uint32_t*)0x400200A4U) |

| (PWM0) PWM Spread Spectrum Update Register More... | |

| #define | REG_PWM0_VERSION (*(__I uint32_t*)0x400200FCU) |

| (PWM0) Version Register More... | |

| #define | REG_PWM0_WPCR (*(__O uint32_t*)0x400200E4U) |

| (PWM0) PWM Write Protection Control Register More... | |

| #define | REG_PWM0_WPSR (*(__I uint32_t*)0x400200E8U) |

| (PWM0) PWM Write Protection Status Register More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file pwm0.h.

Macro Definition Documentation

◆ REG_PWM0_CCNT0

| #define REG_PWM0_CCNT0 (*(__I uint32_t*)0x40020214U) |

◆ REG_PWM0_CCNT1

| #define REG_PWM0_CCNT1 (*(__I uint32_t*)0x40020234U) |

◆ REG_PWM0_CCNT2

| #define REG_PWM0_CCNT2 (*(__I uint32_t*)0x40020254U) |

◆ REG_PWM0_CCNT3

| #define REG_PWM0_CCNT3 (*(__I uint32_t*)0x40020274U) |

◆ REG_PWM0_CDTY0

| #define REG_PWM0_CDTY0 (*(__IO uint32_t*)0x40020204U) |

◆ REG_PWM0_CDTY1

| #define REG_PWM0_CDTY1 (*(__IO uint32_t*)0x40020224U) |

◆ REG_PWM0_CDTY2

| #define REG_PWM0_CDTY2 (*(__IO uint32_t*)0x40020244U) |

◆ REG_PWM0_CDTY3

| #define REG_PWM0_CDTY3 (*(__IO uint32_t*)0x40020264U) |

◆ REG_PWM0_CDTYUPD0

| #define REG_PWM0_CDTYUPD0 (*(__O uint32_t*)0x40020208U) |

◆ REG_PWM0_CDTYUPD1

| #define REG_PWM0_CDTYUPD1 (*(__O uint32_t*)0x40020228U) |

◆ REG_PWM0_CDTYUPD2

| #define REG_PWM0_CDTYUPD2 (*(__O uint32_t*)0x40020248U) |

◆ REG_PWM0_CDTYUPD3

| #define REG_PWM0_CDTYUPD3 (*(__O uint32_t*)0x40020268U) |

◆ REG_PWM0_CLK

| #define REG_PWM0_CLK (*(__IO uint32_t*)0x40020000U) |

◆ REG_PWM0_CMPM0

| #define REG_PWM0_CMPM0 (*(__IO uint32_t*)0x40020138U) |

◆ REG_PWM0_CMPM1

| #define REG_PWM0_CMPM1 (*(__IO uint32_t*)0x40020148U) |

◆ REG_PWM0_CMPM2

| #define REG_PWM0_CMPM2 (*(__IO uint32_t*)0x40020158U) |

◆ REG_PWM0_CMPM3

| #define REG_PWM0_CMPM3 (*(__IO uint32_t*)0x40020168U) |

◆ REG_PWM0_CMPM4

| #define REG_PWM0_CMPM4 (*(__IO uint32_t*)0x40020178U) |

◆ REG_PWM0_CMPM5

| #define REG_PWM0_CMPM5 (*(__IO uint32_t*)0x40020188U) |

◆ REG_PWM0_CMPM6

| #define REG_PWM0_CMPM6 (*(__IO uint32_t*)0x40020198U) |

◆ REG_PWM0_CMPM7

| #define REG_PWM0_CMPM7 (*(__IO uint32_t*)0x400201A8U) |

◆ REG_PWM0_CMPMUPD0

| #define REG_PWM0_CMPMUPD0 (*(__O uint32_t*)0x4002013CU) |

◆ REG_PWM0_CMPMUPD1

| #define REG_PWM0_CMPMUPD1 (*(__O uint32_t*)0x4002014CU) |

◆ REG_PWM0_CMPMUPD2

| #define REG_PWM0_CMPMUPD2 (*(__O uint32_t*)0x4002015CU) |

◆ REG_PWM0_CMPMUPD3

| #define REG_PWM0_CMPMUPD3 (*(__O uint32_t*)0x4002016CU) |

◆ REG_PWM0_CMPMUPD4

| #define REG_PWM0_CMPMUPD4 (*(__O uint32_t*)0x4002017CU) |

◆ REG_PWM0_CMPMUPD5

| #define REG_PWM0_CMPMUPD5 (*(__O uint32_t*)0x4002018CU) |

◆ REG_PWM0_CMPMUPD6

| #define REG_PWM0_CMPMUPD6 (*(__O uint32_t*)0x4002019CU) |

◆ REG_PWM0_CMPMUPD7

| #define REG_PWM0_CMPMUPD7 (*(__O uint32_t*)0x400201ACU) |

◆ REG_PWM0_CMPV0

| #define REG_PWM0_CMPV0 (*(__IO uint32_t*)0x40020130U) |

◆ REG_PWM0_CMPV1

| #define REG_PWM0_CMPV1 (*(__IO uint32_t*)0x40020140U) |

◆ REG_PWM0_CMPV2

| #define REG_PWM0_CMPV2 (*(__IO uint32_t*)0x40020150U) |

◆ REG_PWM0_CMPV3

| #define REG_PWM0_CMPV3 (*(__IO uint32_t*)0x40020160U) |

◆ REG_PWM0_CMPV4

| #define REG_PWM0_CMPV4 (*(__IO uint32_t*)0x40020170U) |

◆ REG_PWM0_CMPV5

| #define REG_PWM0_CMPV5 (*(__IO uint32_t*)0x40020180U) |

◆ REG_PWM0_CMPV6

| #define REG_PWM0_CMPV6 (*(__IO uint32_t*)0x40020190U) |

◆ REG_PWM0_CMPV7

| #define REG_PWM0_CMPV7 (*(__IO uint32_t*)0x400201A0U) |

◆ REG_PWM0_CMPVUPD0

| #define REG_PWM0_CMPVUPD0 (*(__O uint32_t*)0x40020134U) |

◆ REG_PWM0_CMPVUPD1

| #define REG_PWM0_CMPVUPD1 (*(__O uint32_t*)0x40020144U) |

◆ REG_PWM0_CMPVUPD2

| #define REG_PWM0_CMPVUPD2 (*(__O uint32_t*)0x40020154U) |

◆ REG_PWM0_CMPVUPD3

| #define REG_PWM0_CMPVUPD3 (*(__O uint32_t*)0x40020164U) |

◆ REG_PWM0_CMPVUPD4

| #define REG_PWM0_CMPVUPD4 (*(__O uint32_t*)0x40020174U) |

◆ REG_PWM0_CMPVUPD5

| #define REG_PWM0_CMPVUPD5 (*(__O uint32_t*)0x40020184U) |

◆ REG_PWM0_CMPVUPD6

| #define REG_PWM0_CMPVUPD6 (*(__O uint32_t*)0x40020194U) |

◆ REG_PWM0_CMPVUPD7

| #define REG_PWM0_CMPVUPD7 (*(__O uint32_t*)0x400201A4U) |

◆ REG_PWM0_CMR0

| #define REG_PWM0_CMR0 (*(__IO uint32_t*)0x40020200U) |

◆ REG_PWM0_CMR1

| #define REG_PWM0_CMR1 (*(__IO uint32_t*)0x40020220U) |

◆ REG_PWM0_CMR2

| #define REG_PWM0_CMR2 (*(__IO uint32_t*)0x40020240U) |

◆ REG_PWM0_CMR3

| #define REG_PWM0_CMR3 (*(__IO uint32_t*)0x40020260U) |

◆ REG_PWM0_CMUPD0

| #define REG_PWM0_CMUPD0 (*(__O uint32_t*)0x40020400U) |

◆ REG_PWM0_CMUPD1

| #define REG_PWM0_CMUPD1 (*(__O uint32_t*)0x40020420U) |

◆ REG_PWM0_CMUPD2

| #define REG_PWM0_CMUPD2 (*(__O uint32_t*)0x40020440U) |

◆ REG_PWM0_CMUPD3

| #define REG_PWM0_CMUPD3 (*(__O uint32_t*)0x40020460U) |

◆ REG_PWM0_CPRD0

| #define REG_PWM0_CPRD0 (*(__IO uint32_t*)0x4002020CU) |

◆ REG_PWM0_CPRD1

| #define REG_PWM0_CPRD1 (*(__IO uint32_t*)0x4002022CU) |

◆ REG_PWM0_CPRD2

| #define REG_PWM0_CPRD2 (*(__IO uint32_t*)0x4002024CU) |

◆ REG_PWM0_CPRD3

| #define REG_PWM0_CPRD3 (*(__IO uint32_t*)0x4002026CU) |

◆ REG_PWM0_CPRDUPD0

| #define REG_PWM0_CPRDUPD0 (*(__O uint32_t*)0x40020210U) |

◆ REG_PWM0_CPRDUPD1

| #define REG_PWM0_CPRDUPD1 (*(__O uint32_t*)0x40020230U) |

◆ REG_PWM0_CPRDUPD2

| #define REG_PWM0_CPRDUPD2 (*(__O uint32_t*)0x40020250U) |

◆ REG_PWM0_CPRDUPD3

| #define REG_PWM0_CPRDUPD3 (*(__O uint32_t*)0x40020270U) |

◆ REG_PWM0_DIS

| #define REG_PWM0_DIS (*(__O uint32_t*)0x40020008U) |

◆ REG_PWM0_DMAR

| #define REG_PWM0_DMAR (*(__O uint32_t*)0x40020024U) |

◆ REG_PWM0_DT0

| #define REG_PWM0_DT0 (*(__IO uint32_t*)0x40020218U) |

◆ REG_PWM0_DT1

| #define REG_PWM0_DT1 (*(__IO uint32_t*)0x40020238U) |

◆ REG_PWM0_DT2

| #define REG_PWM0_DT2 (*(__IO uint32_t*)0x40020258U) |

◆ REG_PWM0_DT3

| #define REG_PWM0_DT3 (*(__IO uint32_t*)0x40020278U) |

◆ REG_PWM0_DTUPD0

| #define REG_PWM0_DTUPD0 (*(__O uint32_t*)0x4002021CU) |

◆ REG_PWM0_DTUPD1

| #define REG_PWM0_DTUPD1 (*(__O uint32_t*)0x4002023CU) |

◆ REG_PWM0_DTUPD2

| #define REG_PWM0_DTUPD2 (*(__O uint32_t*)0x4002025CU) |

◆ REG_PWM0_DTUPD3

| #define REG_PWM0_DTUPD3 (*(__O uint32_t*)0x4002027CU) |

◆ REG_PWM0_ELMR

| #define REG_PWM0_ELMR (*(__IO uint32_t*)0x4002007CU) |

◆ REG_PWM0_ENA

| #define REG_PWM0_ENA (*(__O uint32_t*)0x40020004U) |

◆ REG_PWM0_ETRG1

| #define REG_PWM0_ETRG1 (*(__IO uint32_t*)0x4002042CU) |

◆ REG_PWM0_ETRG2

| #define REG_PWM0_ETRG2 (*(__IO uint32_t*)0x4002044CU) |

◆ REG_PWM0_FCR

| #define REG_PWM0_FCR (*(__O uint32_t*)0x40020064U) |

◆ REG_PWM0_FMR

| #define REG_PWM0_FMR (*(__IO uint32_t*)0x4002005CU) |

◆ REG_PWM0_FPE

| #define REG_PWM0_FPE (*(__IO uint32_t*)0x4002006CU) |

◆ REG_PWM0_FPV1

| #define REG_PWM0_FPV1 (*(__IO uint32_t*)0x40020068U) |

◆ REG_PWM0_FPV2

| #define REG_PWM0_FPV2 (*(__IO uint32_t*)0x400200C0U) |

◆ REG_PWM0_FSR

| #define REG_PWM0_FSR (*(__I uint32_t*)0x40020060U) |

◆ REG_PWM0_IDR1

| #define REG_PWM0_IDR1 (*(__O uint32_t*)0x40020014U) |

◆ REG_PWM0_IDR2

| #define REG_PWM0_IDR2 (*(__O uint32_t*)0x40020038U) |

◆ REG_PWM0_IER1

| #define REG_PWM0_IER1 (*(__O uint32_t*)0x40020010U) |

◆ REG_PWM0_IER2

| #define REG_PWM0_IER2 (*(__O uint32_t*)0x40020034U) |

◆ REG_PWM0_IMR1

| #define REG_PWM0_IMR1 (*(__I uint32_t*)0x40020018U) |

◆ REG_PWM0_IMR2

| #define REG_PWM0_IMR2 (*(__I uint32_t*)0x4002003CU) |

◆ REG_PWM0_ISR1

| #define REG_PWM0_ISR1 (*(__I uint32_t*)0x4002001CU) |

◆ REG_PWM0_ISR2

| #define REG_PWM0_ISR2 (*(__I uint32_t*)0x40020040U) |

◆ REG_PWM0_LEBR1

| #define REG_PWM0_LEBR1 (*(__IO uint32_t*)0x40020430U) |

◆ REG_PWM0_LEBR2

| #define REG_PWM0_LEBR2 (*(__IO uint32_t*)0x40020450U) |

◆ REG_PWM0_OOV

| #define REG_PWM0_OOV (*(__IO uint32_t*)0x40020044U) |

◆ REG_PWM0_OS

| #define REG_PWM0_OS (*(__IO uint32_t*)0x40020048U) |

◆ REG_PWM0_OSC

| #define REG_PWM0_OSC (*(__O uint32_t*)0x40020050U) |

◆ REG_PWM0_OSCUPD

| #define REG_PWM0_OSCUPD (*(__O uint32_t*)0x40020058U) |

◆ REG_PWM0_OSS

| #define REG_PWM0_OSS (*(__O uint32_t*)0x4002004CU) |

◆ REG_PWM0_OSSUPD

| #define REG_PWM0_OSSUPD (*(__O uint32_t*)0x40020054U) |

◆ REG_PWM0_SCM

| #define REG_PWM0_SCM (*(__IO uint32_t*)0x40020020U) |

◆ REG_PWM0_SCUC

| #define REG_PWM0_SCUC (*(__IO uint32_t*)0x40020028U) |

◆ REG_PWM0_SCUP

| #define REG_PWM0_SCUP (*(__IO uint32_t*)0x4002002CU) |

◆ REG_PWM0_SCUPUPD

| #define REG_PWM0_SCUPUPD (*(__O uint32_t*)0x40020030U) |

◆ REG_PWM0_SMMR

| #define REG_PWM0_SMMR (*(__IO uint32_t*)0x400200B0U) |

◆ REG_PWM0_SR

| #define REG_PWM0_SR (*(__I uint32_t*)0x4002000CU) |

◆ REG_PWM0_SSPR

| #define REG_PWM0_SSPR (*(__IO uint32_t*)0x400200A0U) |

◆ REG_PWM0_SSPUP

| #define REG_PWM0_SSPUP (*(__O uint32_t*)0x400200A4U) |

◆ REG_PWM0_VERSION

| #define REG_PWM0_VERSION (*(__I uint32_t*)0x400200FCU) |

◆ REG_PWM0_WPCR

| #define REG_PWM0_WPCR (*(__O uint32_t*)0x400200E4U) |