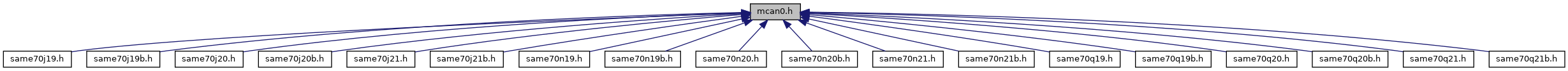

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | REG_MCAN0_BTP (*(__IO uint32_t*)0x4003001CU) |

| (MCAN0) Bit Timing and Prescaler Register More... | |

| #define | REG_MCAN0_CCCR (*(__IO uint32_t*)0x40030018U) |

| (MCAN0) CC Control Register More... | |

| #define | REG_MCAN0_CREL (*(__I uint32_t*)0x40030000U) |

| (MCAN0) Core Release Register More... | |

| #define | REG_MCAN0_CUST (*(__IO uint32_t*)0x40030008U) |

| (MCAN0) Customer Register More... | |

| #define | REG_MCAN0_DBTP (*(__IO uint32_t*)0x4003000CU) |

| (MCAN0) Data Bit Timing and Prescaler Register More... | |

| #define | REG_MCAN0_ECR (*(__I uint32_t*)0x40030040U) |

| (MCAN0) Error Counter Register More... | |

| #define | REG_MCAN0_ENDN (*(__I uint32_t*)0x40030004U) |

| (MCAN0) Endian Register More... | |

| #define | REG_MCAN0_FBTP (*(__IO uint32_t*)0x4003000CU) |

| (MCAN0) Fast Bit Timing and Prescaler Register More... | |

| #define | REG_MCAN0_GFC (*(__IO uint32_t*)0x40030080U) |

| (MCAN0) Global Filter Configuration Register More... | |

| #define | REG_MCAN0_HPMS (*(__I uint32_t*)0x40030094U) |

| (MCAN0) High Priority Message Status Register More... | |

| #define | REG_MCAN0_IE (*(__IO uint32_t*)0x40030054U) |

| (MCAN0) Interrupt Enable Register More... | |

| #define | REG_MCAN0_ILE (*(__IO uint32_t*)0x4003005CU) |

| (MCAN0) Interrupt Line Enable Register More... | |

| #define | REG_MCAN0_ILS (*(__IO uint32_t*)0x40030058U) |

| (MCAN0) Interrupt Line Select Register More... | |

| #define | REG_MCAN0_IR (*(__IO uint32_t*)0x40030050U) |

| (MCAN0) Interrupt Register More... | |

| #define | REG_MCAN0_NBTP (*(__IO uint32_t*)0x4003001CU) |

| (MCAN0) Nominal Bit Timing and Prescaler Register More... | |

| #define | REG_MCAN0_NDAT1 (*(__IO uint32_t*)0x40030098U) |

| (MCAN0) New Data 1 Register More... | |

| #define | REG_MCAN0_NDAT2 (*(__IO uint32_t*)0x4003009CU) |

| (MCAN0) New Data 2 Register More... | |

| #define | REG_MCAN0_PSR (*(__I uint32_t*)0x40030044U) |

| (MCAN0) Protocol Status Register More... | |

| #define | REG_MCAN0_RWD (*(__IO uint32_t*)0x40030014U) |

| (MCAN0) RAM Watchdog Register More... | |

| #define | REG_MCAN0_RXBC (*(__IO uint32_t*)0x400300ACU) |

| (MCAN0) Receive Rx Buffer Configuration Register More... | |

| #define | REG_MCAN0_RXESC (*(__IO uint32_t*)0x400300BCU) |

| (MCAN0) Receive Buffer / FIFO Element Size Configuration Register More... | |

| #define | REG_MCAN0_RXF0A (*(__IO uint32_t*)0x400300A8U) |

| (MCAN0) Receive FIFO 0 Acknowledge Register More... | |

| #define | REG_MCAN0_RXF0C (*(__IO uint32_t*)0x400300A0U) |

| (MCAN0) Receive FIFO 0 Configuration Register More... | |

| #define | REG_MCAN0_RXF0S (*(__I uint32_t*)0x400300A4U) |

| (MCAN0) Receive FIFO 0 Status Register More... | |

| #define | REG_MCAN0_RXF1A (*(__IO uint32_t*)0x400300B8U) |

| (MCAN0) Receive FIFO 1 Acknowledge Register More... | |

| #define | REG_MCAN0_RXF1C (*(__IO uint32_t*)0x400300B0U) |

| (MCAN0) Receive FIFO 1 Configuration Register More... | |

| #define | REG_MCAN0_RXF1S (*(__I uint32_t*)0x400300B4U) |

| (MCAN0) Receive FIFO 1 Status Register More... | |

| #define | REG_MCAN0_SIDFC (*(__IO uint32_t*)0x40030084U) |

| (MCAN0) Standard ID Filter Configuration Register More... | |

| #define | REG_MCAN0_TDCR (*(__IO uint32_t*)0x40030048U) |

| (MCAN0) Transmit Delay Compensation Register More... | |

| #define | REG_MCAN0_TEST (*(__IO uint32_t*)0x40030010U) |

| (MCAN0) Test Register More... | |

| #define | REG_MCAN0_TOCC (*(__IO uint32_t*)0x40030028U) |

| (MCAN0) Timeout Counter Configuration Register More... | |

| #define | REG_MCAN0_TOCV (*(__IO uint32_t*)0x4003002CU) |

| (MCAN0) Timeout Counter Value Register More... | |

| #define | REG_MCAN0_TSCC (*(__IO uint32_t*)0x40030020U) |

| (MCAN0) Timestamp Counter Configuration Register More... | |

| #define | REG_MCAN0_TSCV (*(__IO uint32_t*)0x40030024U) |

| (MCAN0) Timestamp Counter Value Register More... | |

| #define | REG_MCAN0_TXBAR (*(__IO uint32_t*)0x400300D0U) |

| (MCAN0) Transmit Buffer Add Request Register More... | |

| #define | REG_MCAN0_TXBC (*(__IO uint32_t*)0x400300C0U) |

| (MCAN0) Transmit Buffer Configuration Register More... | |

| #define | REG_MCAN0_TXBCF (*(__I uint32_t*)0x400300DCU) |

| (MCAN0) Transmit Buffer Cancellation Finished Register More... | |

| #define | REG_MCAN0_TXBCIE (*(__IO uint32_t*)0x400300E4U) |

| (MCAN0) Transmit Buffer Cancellation Finished Interrupt Enable Register More... | |

| #define | REG_MCAN0_TXBCR (*(__IO uint32_t*)0x400300D4U) |

| (MCAN0) Transmit Buffer Cancellation Request Register More... | |

| #define | REG_MCAN0_TXBRP (*(__I uint32_t*)0x400300CCU) |

| (MCAN0) Transmit Buffer Request Pending Register More... | |

| #define | REG_MCAN0_TXBTIE (*(__IO uint32_t*)0x400300E0U) |

| (MCAN0) Transmit Buffer Transmission Interrupt Enable Register More... | |

| #define | REG_MCAN0_TXBTO (*(__I uint32_t*)0x400300D8U) |

| (MCAN0) Transmit Buffer Transmission Occurred Register More... | |

| #define | REG_MCAN0_TXEFA (*(__IO uint32_t*)0x400300F8U) |

| (MCAN0) Transmit Event FIFO Acknowledge Register More... | |

| #define | REG_MCAN0_TXEFC (*(__IO uint32_t*)0x400300F0U) |

| (MCAN0) Transmit Event FIFO Configuration Register More... | |

| #define | REG_MCAN0_TXEFS (*(__I uint32_t*)0x400300F4U) |

| (MCAN0) Transmit Event FIFO Status Register More... | |

| #define | REG_MCAN0_TXESC (*(__IO uint32_t*)0x400300C8U) |

| (MCAN0) Transmit Buffer Element Size Configuration Register More... | |

| #define | REG_MCAN0_TXFQS (*(__I uint32_t*)0x400300C4U) |

| (MCAN0) Transmit FIFO/Queue Status Register More... | |

| #define | REG_MCAN0_XIDAM (*(__IO uint32_t*)0x40030090U) |

| (MCAN0) Extended ID AND Mask Register More... | |

| #define | REG_MCAN0_XIDFC (*(__IO uint32_t*)0x40030088U) |

| (MCAN0) Extended ID Filter Configuration Register More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file mcan0.h.

Macro Definition Documentation

◆ REG_MCAN0_BTP

| #define REG_MCAN0_BTP (*(__IO uint32_t*)0x4003001CU) |

◆ REG_MCAN0_CCCR

| #define REG_MCAN0_CCCR (*(__IO uint32_t*)0x40030018U) |

◆ REG_MCAN0_CREL

| #define REG_MCAN0_CREL (*(__I uint32_t*)0x40030000U) |

◆ REG_MCAN0_CUST

| #define REG_MCAN0_CUST (*(__IO uint32_t*)0x40030008U) |

◆ REG_MCAN0_DBTP

| #define REG_MCAN0_DBTP (*(__IO uint32_t*)0x4003000CU) |

◆ REG_MCAN0_ECR

| #define REG_MCAN0_ECR (*(__I uint32_t*)0x40030040U) |

◆ REG_MCAN0_ENDN

| #define REG_MCAN0_ENDN (*(__I uint32_t*)0x40030004U) |

◆ REG_MCAN0_FBTP

| #define REG_MCAN0_FBTP (*(__IO uint32_t*)0x4003000CU) |

◆ REG_MCAN0_GFC

| #define REG_MCAN0_GFC (*(__IO uint32_t*)0x40030080U) |

◆ REG_MCAN0_HPMS

| #define REG_MCAN0_HPMS (*(__I uint32_t*)0x40030094U) |

◆ REG_MCAN0_IE

| #define REG_MCAN0_IE (*(__IO uint32_t*)0x40030054U) |

◆ REG_MCAN0_ILE

| #define REG_MCAN0_ILE (*(__IO uint32_t*)0x4003005CU) |

◆ REG_MCAN0_ILS

| #define REG_MCAN0_ILS (*(__IO uint32_t*)0x40030058U) |

◆ REG_MCAN0_IR

| #define REG_MCAN0_IR (*(__IO uint32_t*)0x40030050U) |

◆ REG_MCAN0_NBTP

| #define REG_MCAN0_NBTP (*(__IO uint32_t*)0x4003001CU) |

◆ REG_MCAN0_NDAT1

| #define REG_MCAN0_NDAT1 (*(__IO uint32_t*)0x40030098U) |

◆ REG_MCAN0_NDAT2

| #define REG_MCAN0_NDAT2 (*(__IO uint32_t*)0x4003009CU) |

◆ REG_MCAN0_PSR

| #define REG_MCAN0_PSR (*(__I uint32_t*)0x40030044U) |

◆ REG_MCAN0_RWD

| #define REG_MCAN0_RWD (*(__IO uint32_t*)0x40030014U) |

◆ REG_MCAN0_RXBC

| #define REG_MCAN0_RXBC (*(__IO uint32_t*)0x400300ACU) |

◆ REG_MCAN0_RXESC

| #define REG_MCAN0_RXESC (*(__IO uint32_t*)0x400300BCU) |

◆ REG_MCAN0_RXF0A

| #define REG_MCAN0_RXF0A (*(__IO uint32_t*)0x400300A8U) |

◆ REG_MCAN0_RXF0C

| #define REG_MCAN0_RXF0C (*(__IO uint32_t*)0x400300A0U) |

◆ REG_MCAN0_RXF0S

| #define REG_MCAN0_RXF0S (*(__I uint32_t*)0x400300A4U) |

◆ REG_MCAN0_RXF1A

| #define REG_MCAN0_RXF1A (*(__IO uint32_t*)0x400300B8U) |

◆ REG_MCAN0_RXF1C

| #define REG_MCAN0_RXF1C (*(__IO uint32_t*)0x400300B0U) |

◆ REG_MCAN0_RXF1S

| #define REG_MCAN0_RXF1S (*(__I uint32_t*)0x400300B4U) |

◆ REG_MCAN0_SIDFC

| #define REG_MCAN0_SIDFC (*(__IO uint32_t*)0x40030084U) |

◆ REG_MCAN0_TDCR

| #define REG_MCAN0_TDCR (*(__IO uint32_t*)0x40030048U) |

◆ REG_MCAN0_TEST

| #define REG_MCAN0_TEST (*(__IO uint32_t*)0x40030010U) |

◆ REG_MCAN0_TOCC

| #define REG_MCAN0_TOCC (*(__IO uint32_t*)0x40030028U) |

◆ REG_MCAN0_TOCV

| #define REG_MCAN0_TOCV (*(__IO uint32_t*)0x4003002CU) |

◆ REG_MCAN0_TSCC

| #define REG_MCAN0_TSCC (*(__IO uint32_t*)0x40030020U) |

◆ REG_MCAN0_TSCV

| #define REG_MCAN0_TSCV (*(__IO uint32_t*)0x40030024U) |

◆ REG_MCAN0_TXBAR

| #define REG_MCAN0_TXBAR (*(__IO uint32_t*)0x400300D0U) |

◆ REG_MCAN0_TXBC

| #define REG_MCAN0_TXBC (*(__IO uint32_t*)0x400300C0U) |

◆ REG_MCAN0_TXBCF

| #define REG_MCAN0_TXBCF (*(__I uint32_t*)0x400300DCU) |

◆ REG_MCAN0_TXBCIE

| #define REG_MCAN0_TXBCIE (*(__IO uint32_t*)0x400300E4U) |

◆ REG_MCAN0_TXBCR

| #define REG_MCAN0_TXBCR (*(__IO uint32_t*)0x400300D4U) |

◆ REG_MCAN0_TXBRP

| #define REG_MCAN0_TXBRP (*(__I uint32_t*)0x400300CCU) |

◆ REG_MCAN0_TXBTIE

| #define REG_MCAN0_TXBTIE (*(__IO uint32_t*)0x400300E0U) |

◆ REG_MCAN0_TXBTO

| #define REG_MCAN0_TXBTO (*(__I uint32_t*)0x400300D8U) |

◆ REG_MCAN0_TXEFA

| #define REG_MCAN0_TXEFA (*(__IO uint32_t*)0x400300F8U) |

◆ REG_MCAN0_TXEFC

| #define REG_MCAN0_TXEFC (*(__IO uint32_t*)0x400300F0U) |

◆ REG_MCAN0_TXEFS

| #define REG_MCAN0_TXEFS (*(__I uint32_t*)0x400300F4U) |

◆ REG_MCAN0_TXESC

| #define REG_MCAN0_TXESC (*(__IO uint32_t*)0x400300C8U) |

◆ REG_MCAN0_TXFQS

| #define REG_MCAN0_TXFQS (*(__I uint32_t*)0x400300C4U) |

◆ REG_MCAN0_XIDAM

| #define REG_MCAN0_XIDAM (*(__IO uint32_t*)0x40030090U) |