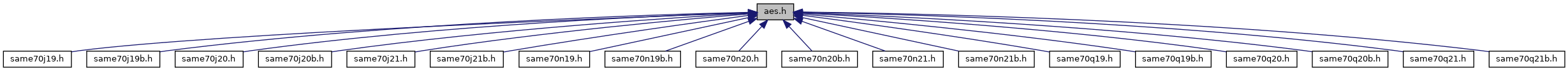

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Aes |

| Aes hardware registers. More... | |

Macros | |

| #define | AES_AADLENR_AADLEN(value) ((AES_AADLENR_AADLEN_Msk & ((value) << AES_AADLENR_AADLEN_Pos))) |

| #define | AES_AADLENR_AADLEN_Msk (0xffffffffu << AES_AADLENR_AADLEN_Pos) |

| (AES_AADLENR) Additional Authenticated Data Length More... | |

| #define | AES_AADLENR_AADLEN_Pos 0 |

| #define | AES_CLENR_CLEN(value) ((AES_CLENR_CLEN_Msk & ((value) << AES_CLENR_CLEN_Pos))) |

| #define | AES_CLENR_CLEN_Msk (0xffffffffu << AES_CLENR_CLEN_Pos) |

| (AES_CLENR) Plaintext/Ciphertext Length More... | |

| #define | AES_CLENR_CLEN_Pos 0 |

| #define | AES_CR_LOADSEED (0x1u << 16) |

| (AES_CR) Random Number Generator Seed Loading More... | |

| #define | AES_CR_START (0x1u << 0) |

| (AES_CR) Start Processing More... | |

| #define | AES_CR_SWRST (0x1u << 8) |

| (AES_CR) Software Reset More... | |

| #define | AES_CTRR_CTR_Msk (0xffffffffu << AES_CTRR_CTR_Pos) |

| (AES_CTRR) GCM Encryption Counter More... | |

| #define | AES_CTRR_CTR_Pos 0 |

| #define | AES_GCMHR_H(value) ((AES_GCMHR_H_Msk & ((value) << AES_GCMHR_H_Pos))) |

| #define | AES_GCMHR_H_Msk (0xffffffffu << AES_GCMHR_H_Pos) |

| (AES_GCMHR[4]) GCM H Word x More... | |

| #define | AES_GCMHR_H_Pos 0 |

| #define | AES_GHASHR_GHASH(value) ((AES_GHASHR_GHASH_Msk & ((value) << AES_GHASHR_GHASH_Pos))) |

| #define | AES_GHASHR_GHASH_Msk (0xffffffffu << AES_GHASHR_GHASH_Pos) |

| (AES_GHASHR[4]) Intermediate GCM Hash Word x More... | |

| #define | AES_GHASHR_GHASH_Pos 0 |

| #define | AES_IDATAR_IDATA(value) ((AES_IDATAR_IDATA_Msk & ((value) << AES_IDATAR_IDATA_Pos))) |

| #define | AES_IDATAR_IDATA_Msk (0xffffffffu << AES_IDATAR_IDATA_Pos) |

| (AES_IDATAR[4]) Input Data Word More... | |

| #define | AES_IDATAR_IDATA_Pos 0 |

| #define | AES_IDR_DATRDY (0x1u << 0) |

| (AES_IDR) Data Ready Interrupt Disable More... | |

| #define | AES_IDR_TAGRDY (0x1u << 16) |

| (AES_IDR) GCM Tag Ready Interrupt Disable More... | |

| #define | AES_IDR_URAD (0x1u << 8) |

| (AES_IDR) Unspecified Register Access Detection Interrupt Disable More... | |

| #define | AES_IER_DATRDY (0x1u << 0) |

| (AES_IER) Data Ready Interrupt Enable More... | |

| #define | AES_IER_TAGRDY (0x1u << 16) |

| (AES_IER) GCM Tag Ready Interrupt Enable More... | |

| #define | AES_IER_URAD (0x1u << 8) |

| (AES_IER) Unspecified Register Access Detection Interrupt Enable More... | |

| #define | AES_IMR_DATRDY (0x1u << 0) |

| (AES_IMR) Data Ready Interrupt Mask More... | |

| #define | AES_IMR_TAGRDY (0x1u << 16) |

| (AES_IMR) GCM Tag Ready Interrupt Mask More... | |

| #define | AES_IMR_URAD (0x1u << 8) |

| (AES_IMR) Unspecified Register Access Detection Interrupt Mask More... | |

| #define | AES_ISR_DATRDY (0x1u << 0) |

| (AES_ISR) Data Ready (cleared by setting bit START or bit SWRST in AES_CR or by reading AES_ODATARx) More... | |

| #define | AES_ISR_TAGRDY (0x1u << 16) |

| (AES_ISR) GCM Tag Ready More... | |

| #define | AES_ISR_URAD (0x1u << 8) |

| (AES_ISR) Unspecified Register Access Detection Status (cleared by writing SWRST in AES_CR) More... | |

| #define | AES_ISR_URAT_IDR_WR_PROCESSING (0x0u << 12) |

| (AES_ISR) Input Data Register written during the data processing when SMOD = 0x2 mode. More... | |

| #define | AES_ISR_URAT_MR_WR_PROCESSING (0x2u << 12) |

| (AES_ISR) Mode Register written during the data processing. More... | |

| #define | AES_ISR_URAT_MR_WR_SUBKGEN (0x4u << 12) |

| (AES_ISR) Mode Register written during the sub-keys generation. More... | |

| #define | AES_ISR_URAT_Msk (0xfu << AES_ISR_URAT_Pos) |

| (AES_ISR) Unspecified Register Access (cleared by writing SWRST in AES_CR) More... | |

| #define | AES_ISR_URAT_ODR_RD_PROCESSING (0x1u << 12) |

| (AES_ISR) Output Data Register read during the data processing. More... | |

| #define | AES_ISR_URAT_ODR_RD_SUBKGEN (0x3u << 12) |

| (AES_ISR) Output Data Register read during the sub-keys generation. More... | |

| #define | AES_ISR_URAT_Pos 12 |

| #define | AES_ISR_URAT_WOR_RD_ACCESS (0x5u << 12) |

| (AES_ISR) Write-only register read access. More... | |

| #define | AES_IVR_IV(value) ((AES_IVR_IV_Msk & ((value) << AES_IVR_IV_Pos))) |

| #define | AES_IVR_IV_Msk (0xffffffffu << AES_IVR_IV_Pos) |

| (AES_IVR[4]) Initialization Vector More... | |

| #define | AES_IVR_IV_Pos 0 |

| #define | AES_KEYWR_KEYW(value) ((AES_KEYWR_KEYW_Msk & ((value) << AES_KEYWR_KEYW_Pos))) |

| #define | AES_KEYWR_KEYW_Msk (0xffffffffu << AES_KEYWR_KEYW_Pos) |

| (AES_KEYWR[8]) Key Word More... | |

| #define | AES_KEYWR_KEYW_Pos 0 |

| #define | AES_MR_CFBS(value) ((AES_MR_CFBS_Msk & ((value) << AES_MR_CFBS_Pos))) |

| #define | AES_MR_CFBS_Msk (0x7u << AES_MR_CFBS_Pos) |

| (AES_MR) Cipher Feedback Data Size More... | |

| #define | AES_MR_CFBS_Pos 16 |

| #define | AES_MR_CFBS_SIZE_128BIT (0x0u << 16) |

| (AES_MR) 128-bit More... | |

| #define | AES_MR_CFBS_SIZE_16BIT (0x3u << 16) |

| (AES_MR) 16-bit More... | |

| #define | AES_MR_CFBS_SIZE_32BIT (0x2u << 16) |

| (AES_MR) 32-bit More... | |

| #define | AES_MR_CFBS_SIZE_64BIT (0x1u << 16) |

| (AES_MR) 64-bit More... | |

| #define | AES_MR_CFBS_SIZE_8BIT (0x4u << 16) |

| (AES_MR) 8-bit More... | |

| #define | AES_MR_CIPHER (0x1u << 0) |

| (AES_MR) Processing Mode More... | |

| #define | AES_MR_CKEY(value) ((AES_MR_CKEY_Msk & ((value) << AES_MR_CKEY_Pos))) |

| #define | AES_MR_CKEY_Msk (0xfu << AES_MR_CKEY_Pos) |

| (AES_MR) Key More... | |

| #define | AES_MR_CKEY_PASSWD (0xEu << 20) |

| (AES_MR) This field must be written with 0xE to allow CMTYPx bit configuration changes. Any other values will abort the write operation in CMTYPx bits.Always reads as 0. More... | |

| #define | AES_MR_CKEY_Pos 20 |

| #define | AES_MR_CMTYP1 (0x1u << 24) |

| (AES_MR) Countermeasure Type 1 More... | |

| #define | AES_MR_CMTYP1_NOPROT_EXTKEY (0x0u << 24) |

| (AES_MR) Countermeasure type 1 is disabled. More... | |

| #define | AES_MR_CMTYP1_PROT_EXTKEY (0x1u << 24) |

| (AES_MR) Countermeasure type 1 is enabled. More... | |

| #define | AES_MR_CMTYP2 (0x1u << 25) |

| (AES_MR) Countermeasure Type 2 More... | |

| #define | AES_MR_CMTYP2_NO_PAUSE (0x0u << 25) |

| (AES_MR) Countermeasure type 2 is disabled. More... | |

| #define | AES_MR_CMTYP2_PAUSE (0x1u << 25) |

| (AES_MR) Countermeasure type 2 is enabled. More... | |

| #define | AES_MR_CMTYP3 (0x1u << 26) |

| (AES_MR) Countermeasure Type 3 More... | |

| #define | AES_MR_CMTYP3_DUMMY (0x1u << 26) |

| (AES_MR) Countermeasure type 3 is enabled. More... | |

| #define | AES_MR_CMTYP3_NO_DUMMY (0x0u << 26) |

| (AES_MR) Countermeasure type 3 is disabled. More... | |

| #define | AES_MR_CMTYP4 (0x1u << 27) |

| (AES_MR) Countermeasure Type 4 More... | |

| #define | AES_MR_CMTYP4_NO_RESTART (0x0u << 27) |

| (AES_MR) Countermeasure type 4 is disabled. More... | |

| #define | AES_MR_CMTYP4_RESTART (0x1u << 27) |

| (AES_MR) Countermeasure type 4 is enabled. More... | |

| #define | AES_MR_CMTYP5 (0x1u << 28) |

| (AES_MR) Countermeasure Type 5 More... | |

| #define | AES_MR_CMTYP5_ADDACCESS (0x1u << 28) |

| (AES_MR) Countermeasure type 5 is enabled. More... | |

| #define | AES_MR_CMTYP5_NO_ADDACCESS (0x0u << 28) |

| (AES_MR) Countermeasure type 5 is disabled. More... | |

| #define | AES_MR_CMTYP6 (0x1u << 29) |

| (AES_MR) Countermeasure Type 6 More... | |

| #define | AES_MR_CMTYP6_IDLECURRENT (0x1u << 29) |

| (AES_MR) Countermeasure type 6 is enabled. More... | |

| #define | AES_MR_CMTYP6_NO_IDLECURRENT (0x0u << 29) |

| (AES_MR) Countermeasure type 6 is disabled. More... | |

| #define | AES_MR_DUALBUFF (0x1u << 3) |

| (AES_MR) Dual Input Buffer More... | |

| #define | AES_MR_DUALBUFF_ACTIVE (0x1u << 3) |

| (AES_MR) AES_IDATARx can be written during processing of previous block when SMOD = 0x2. It speeds up the overall runtime of large files. More... | |

| #define | AES_MR_DUALBUFF_INACTIVE (0x0u << 3) |

| (AES_MR) AES_IDATARx cannot be written during processing of previous block. More... | |

| #define | AES_MR_GTAGEN (0x1u << 1) |

| (AES_MR) GCM Automatic Tag Generation Enable More... | |

| #define | AES_MR_KEYSIZE(value) ((AES_MR_KEYSIZE_Msk & ((value) << AES_MR_KEYSIZE_Pos))) |

| #define | AES_MR_KEYSIZE_AES128 (0x0u << 10) |

| (AES_MR) AES Key Size is 128 bits More... | |

| #define | AES_MR_KEYSIZE_AES192 (0x1u << 10) |

| (AES_MR) AES Key Size is 192 bits More... | |

| #define | AES_MR_KEYSIZE_AES256 (0x2u << 10) |

| (AES_MR) AES Key Size is 256 bits More... | |

| #define | AES_MR_KEYSIZE_Msk (0x3u << AES_MR_KEYSIZE_Pos) |

| (AES_MR) Key Size More... | |

| #define | AES_MR_KEYSIZE_Pos 10 |

| #define | AES_MR_LOD (0x1u << 15) |

| (AES_MR) Last Output Data Mode More... | |

| #define | AES_MR_OPMOD(value) ((AES_MR_OPMOD_Msk & ((value) << AES_MR_OPMOD_Pos))) |

| #define | AES_MR_OPMOD_CBC (0x1u << 12) |

| (AES_MR) CBC: Cipher Block Chaining mode More... | |

| #define | AES_MR_OPMOD_CFB (0x3u << 12) |

| (AES_MR) CFB: Cipher Feedback mode More... | |

| #define | AES_MR_OPMOD_CTR (0x4u << 12) |

| (AES_MR) CTR: Counter mode (16-bit internal counter) More... | |

| #define | AES_MR_OPMOD_ECB (0x0u << 12) |

| (AES_MR) ECB: Electronic Code Book mode More... | |

| #define | AES_MR_OPMOD_GCM (0x5u << 12) |

| (AES_MR) GCM: Galois/Counter mode More... | |

| #define | AES_MR_OPMOD_Msk (0x7u << AES_MR_OPMOD_Pos) |

| (AES_MR) Operation Mode More... | |

| #define | AES_MR_OPMOD_OFB (0x2u << 12) |

| (AES_MR) OFB: Output Feedback mode More... | |

| #define | AES_MR_OPMOD_Pos 12 |

| #define | AES_MR_PROCDLY(value) ((AES_MR_PROCDLY_Msk & ((value) << AES_MR_PROCDLY_Pos))) |

| #define | AES_MR_PROCDLY_Msk (0xfu << AES_MR_PROCDLY_Pos) |

| (AES_MR) Processing Delay More... | |

| #define | AES_MR_PROCDLY_Pos 4 |

| #define | AES_MR_SMOD(value) ((AES_MR_SMOD_Msk & ((value) << AES_MR_SMOD_Pos))) |

| #define | AES_MR_SMOD_AUTO_START (0x1u << 8) |

| (AES_MR) Auto Mode More... | |

| #define | AES_MR_SMOD_IDATAR0_START (0x2u << 8) |

| (AES_MR) AES_IDATAR0 access only Auto Mode (DMA) More... | |

| #define | AES_MR_SMOD_MANUAL_START (0x0u << 8) |

| (AES_MR) Manual Mode More... | |

| #define | AES_MR_SMOD_Msk (0x3u << AES_MR_SMOD_Pos) |

| (AES_MR) Start Mode More... | |

| #define | AES_MR_SMOD_Pos 8 |

| #define | AES_ODATAR_ODATA_Msk (0xffffffffu << AES_ODATAR_ODATA_Pos) |

| (AES_ODATAR[4]) Output Data More... | |

| #define | AES_ODATAR_ODATA_Pos 0 |

| #define | AES_TAGR_TAG_Msk (0xffffffffu << AES_TAGR_TAG_Pos) |

| (AES_TAGR[4]) GCM Authentication Tag x More... | |

| #define | AES_TAGR_TAG_Pos 0 |

| #define | AES_VERSION_MFN_Msk (0x7u << AES_VERSION_MFN_Pos) |

| (AES_VERSION) Metal Fix Number More... | |

| #define | AES_VERSION_MFN_Pos 16 |

| #define | AES_VERSION_VERSION_Msk (0xfffu << AES_VERSION_VERSION_Pos) |

| (AES_VERSION) Version of the Hardware Module More... | |

| #define | AES_VERSION_VERSION_Pos 0 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file component/aes.h.