This file contains all the functions prototypes for the DMA firmware library. More...

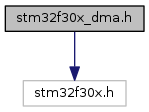

#include "stm32f30x.h"

Include dependency graph for stm32f30x_dma.h:

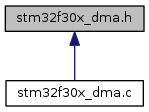

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | DMA_InitTypeDef |

| DMA Init structure definition. More... | |

Macros | |

| #define | DMA1_FLAG_GL1 ((uint32_t)0x00000001) |

| #define | DMA1_FLAG_GL2 ((uint32_t)0x00000010) |

| #define | DMA1_FLAG_GL3 ((uint32_t)0x00000100) |

| #define | DMA1_FLAG_GL4 ((uint32_t)0x00001000) |

| #define | DMA1_FLAG_GL5 ((uint32_t)0x00010000) |

| #define | DMA1_FLAG_GL6 ((uint32_t)0x00100000) |

| #define | DMA1_FLAG_GL7 ((uint32_t)0x01000000) |

| #define | DMA1_FLAG_HT1 ((uint32_t)0x00000004) |

| #define | DMA1_FLAG_HT2 ((uint32_t)0x00000040) |

| #define | DMA1_FLAG_HT3 ((uint32_t)0x00000400) |

| #define | DMA1_FLAG_HT4 ((uint32_t)0x00004000) |

| #define | DMA1_FLAG_HT5 ((uint32_t)0x00040000) |

| #define | DMA1_FLAG_HT6 ((uint32_t)0x00400000) |

| #define | DMA1_FLAG_HT7 ((uint32_t)0x04000000) |

| #define | DMA1_FLAG_TC1 ((uint32_t)0x00000002) |

| #define | DMA1_FLAG_TC2 ((uint32_t)0x00000020) |

| #define | DMA1_FLAG_TC3 ((uint32_t)0x00000200) |

| #define | DMA1_FLAG_TC4 ((uint32_t)0x00002000) |

| #define | DMA1_FLAG_TC5 ((uint32_t)0x00020000) |

| #define | DMA1_FLAG_TC6 ((uint32_t)0x00200000) |

| #define | DMA1_FLAG_TC7 ((uint32_t)0x02000000) |

| #define | DMA1_FLAG_TE1 ((uint32_t)0x00000008) |

| #define | DMA1_FLAG_TE2 ((uint32_t)0x00000080) |

| #define | DMA1_FLAG_TE3 ((uint32_t)0x00000800) |

| #define | DMA1_FLAG_TE4 ((uint32_t)0x00008000) |

| #define | DMA1_FLAG_TE5 ((uint32_t)0x00080000) |

| #define | DMA1_FLAG_TE6 ((uint32_t)0x00800000) |

| #define | DMA1_FLAG_TE7 ((uint32_t)0x08000000) |

| #define | DMA1_IT_GL1 ((uint32_t)0x00000001) |

| #define | DMA1_IT_GL2 ((uint32_t)0x00000010) |

| #define | DMA1_IT_GL3 ((uint32_t)0x00000100) |

| #define | DMA1_IT_GL4 ((uint32_t)0x00001000) |

| #define | DMA1_IT_GL5 ((uint32_t)0x00010000) |

| #define | DMA1_IT_GL6 ((uint32_t)0x00100000) |

| #define | DMA1_IT_GL7 ((uint32_t)0x01000000) |

| #define | DMA1_IT_HT1 ((uint32_t)0x00000004) |

| #define | DMA1_IT_HT2 ((uint32_t)0x00000040) |

| #define | DMA1_IT_HT3 ((uint32_t)0x00000400) |

| #define | DMA1_IT_HT4 ((uint32_t)0x00004000) |

| #define | DMA1_IT_HT5 ((uint32_t)0x00040000) |

| #define | DMA1_IT_HT6 ((uint32_t)0x00400000) |

| #define | DMA1_IT_HT7 ((uint32_t)0x04000000) |

| #define | DMA1_IT_TC1 ((uint32_t)0x00000002) |

| #define | DMA1_IT_TC2 ((uint32_t)0x00000020) |

| #define | DMA1_IT_TC3 ((uint32_t)0x00000200) |

| #define | DMA1_IT_TC4 ((uint32_t)0x00002000) |

| #define | DMA1_IT_TC5 ((uint32_t)0x00020000) |

| #define | DMA1_IT_TC6 ((uint32_t)0x00200000) |

| #define | DMA1_IT_TC7 ((uint32_t)0x02000000) |

| #define | DMA1_IT_TE1 ((uint32_t)0x00000008) |

| #define | DMA1_IT_TE2 ((uint32_t)0x00000080) |

| #define | DMA1_IT_TE3 ((uint32_t)0x00000800) |

| #define | DMA1_IT_TE4 ((uint32_t)0x00008000) |

| #define | DMA1_IT_TE5 ((uint32_t)0x00080000) |

| #define | DMA1_IT_TE6 ((uint32_t)0x00800000) |

| #define | DMA1_IT_TE7 ((uint32_t)0x08000000) |

| #define | DMA2_FLAG_GL1 ((uint32_t)0x10000001) |

| #define | DMA2_FLAG_GL2 ((uint32_t)0x10000010) |

| #define | DMA2_FLAG_GL3 ((uint32_t)0x10000100) |

| #define | DMA2_FLAG_GL4 ((uint32_t)0x10001000) |

| #define | DMA2_FLAG_GL5 ((uint32_t)0x10010000) |

| #define | DMA2_FLAG_HT1 ((uint32_t)0x10000004) |

| #define | DMA2_FLAG_HT2 ((uint32_t)0x10000040) |

| #define | DMA2_FLAG_HT3 ((uint32_t)0x10000400) |

| #define | DMA2_FLAG_HT4 ((uint32_t)0x10004000) |

| #define | DMA2_FLAG_HT5 ((uint32_t)0x10040000) |

| #define | DMA2_FLAG_TC1 ((uint32_t)0x10000002) |

| #define | DMA2_FLAG_TC2 ((uint32_t)0x10000020) |

| #define | DMA2_FLAG_TC3 ((uint32_t)0x10000200) |

| #define | DMA2_FLAG_TC4 ((uint32_t)0x10002000) |

| #define | DMA2_FLAG_TC5 ((uint32_t)0x10020000) |

| #define | DMA2_FLAG_TE1 ((uint32_t)0x10000008) |

| #define | DMA2_FLAG_TE2 ((uint32_t)0x10000080) |

| #define | DMA2_FLAG_TE3 ((uint32_t)0x10000800) |

| #define | DMA2_FLAG_TE4 ((uint32_t)0x10008000) |

| #define | DMA2_FLAG_TE5 ((uint32_t)0x10080000) |

| #define | DMA2_IT_GL1 ((uint32_t)0x10000001) |

| #define | DMA2_IT_GL2 ((uint32_t)0x10000010) |

| #define | DMA2_IT_GL3 ((uint32_t)0x10000100) |

| #define | DMA2_IT_GL4 ((uint32_t)0x10001000) |

| #define | DMA2_IT_GL5 ((uint32_t)0x10010000) |

| #define | DMA2_IT_HT1 ((uint32_t)0x10000004) |

| #define | DMA2_IT_HT2 ((uint32_t)0x10000040) |

| #define | DMA2_IT_HT3 ((uint32_t)0x10000400) |

| #define | DMA2_IT_HT4 ((uint32_t)0x10004000) |

| #define | DMA2_IT_HT5 ((uint32_t)0x10040000) |

| #define | DMA2_IT_TC1 ((uint32_t)0x10000002) |

| #define | DMA2_IT_TC2 ((uint32_t)0x10000020) |

| #define | DMA2_IT_TC3 ((uint32_t)0x10000200) |

| #define | DMA2_IT_TC4 ((uint32_t)0x10002000) |

| #define | DMA2_IT_TC5 ((uint32_t)0x10020000) |

| #define | DMA2_IT_TE1 ((uint32_t)0x10000008) |

| #define | DMA2_IT_TE2 ((uint32_t)0x10000080) |

| #define | DMA2_IT_TE3 ((uint32_t)0x10000800) |

| #define | DMA2_IT_TE4 ((uint32_t)0x10008000) |

| #define | DMA2_IT_TE5 ((uint32_t)0x10080000) |

| #define | DMA_DIR_PeripheralDST DMA_CCR_DIR |

| #define | DMA_DIR_PeripheralSRC ((uint32_t)0x00000000) |

| #define | DMA_IT_HT ((uint32_t)0x00000004) |

| #define | DMA_IT_TC ((uint32_t)0x00000002) |

| #define | DMA_IT_TE ((uint32_t)0x00000008) |

| #define | DMA_M2M_Disable ((uint32_t)0x00000000) |

| #define | DMA_M2M_Enable DMA_CCR_MEM2MEM |

| #define | DMA_MemoryDataSize_Byte ((uint32_t)0x00000000) |

| #define | DMA_MemoryDataSize_HalfWord DMA_CCR_MSIZE_0 |

| #define | DMA_MemoryDataSize_Word DMA_CCR_MSIZE_1 |

| #define | DMA_MemoryInc_Disable ((uint32_t)0x00000000) |

| #define | DMA_MemoryInc_Enable DMA_CCR_MINC |

| #define | DMA_Mode_Circular DMA_CCR_CIRC |

| #define | DMA_Mode_Normal ((uint32_t)0x00000000) |

| #define | DMA_PeripheralDataSize_Byte ((uint32_t)0x00000000) |

| #define | DMA_PeripheralDataSize_HalfWord DMA_CCR_PSIZE_0 |

| #define | DMA_PeripheralDataSize_Word DMA_CCR_PSIZE_1 |

| #define | DMA_PeripheralInc_Disable ((uint32_t)0x00000000) |

| #define | DMA_PeripheralInc_Enable DMA_CCR_PINC |

| #define | DMA_Priority_High DMA_CCR_PL_1 |

| #define | DMA_Priority_Low ((uint32_t)0x00000000) |

| #define | DMA_Priority_Medium DMA_CCR_PL_0 |

| #define | DMA_Priority_VeryHigh DMA_CCR_PL |

| #define | IS_DMA_ALL_PERIPH(PERIPH) |

| #define | IS_DMA_CLEAR_FLAG(FLAG) (((((FLAG) & 0xF0000000) == 0x00) || (((FLAG) & 0xEFF00000) == 0x00)) && ((FLAG) != 0x00)) |

| #define | IS_DMA_CLEAR_IT(IT) (((((IT) & 0xF0000000) == 0x00) || (((IT) & 0xEFF00000) == 0x00)) && ((IT) != 0x00)) |

| #define | IS_DMA_CONFIG_IT(IT) ((((IT) & 0xFFFFFFF1) == 0x00) && ((IT) != 0x00)) |

| #define | IS_DMA_DIR(DIR) |

| #define | IS_DMA_GET_FLAG(FLAG) |

| #define | IS_DMA_GET_IT(IT) |

| #define | IS_DMA_M2M_STATE(STATE) (((STATE) == DMA_M2M_Disable) || ((STATE) == DMA_M2M_Enable)) |

| #define | IS_DMA_MEMORY_DATA_SIZE(SIZE) |

| #define | IS_DMA_MEMORY_INC_STATE(STATE) |

| #define | IS_DMA_MODE(MODE) (((MODE) == DMA_Mode_Normal) || ((MODE) == DMA_Mode_Circular)) |

| #define | IS_DMA_PERIPHERAL_DATA_SIZE(SIZE) |

| #define | IS_DMA_PERIPHERAL_INC_STATE(STATE) |

| #define | IS_DMA_PRIORITY(PRIORITY) |

Functions | |

| void | DMA_ClearFlag (uint32_t DMAy_FLAG) |

| Clears the DMAy Channelx's pending flags. More... | |

| void | DMA_ClearITPendingBit (uint32_t DMAy_IT) |

| Clears the DMAy Channelx's interrupt pending bits. More... | |

| void | DMA_Cmd (DMA_Channel_TypeDef *DMAy_Channelx, FunctionalState NewState) |

| Enables or disables the specified DMAy Channelx. More... | |

| void | DMA_DeInit (DMA_Channel_TypeDef *DMAy_Channelx) |

| Deinitializes the DMAy Channelx registers to their default reset values. More... | |

| uint16_t | DMA_GetCurrDataCounter (DMA_Channel_TypeDef *DMAy_Channelx) |

| Returns the number of remaining data units in the current DMAy Channelx transfer. More... | |

| FlagStatus | DMA_GetFlagStatus (uint32_t DMAy_FLAG) |

| Checks whether the specified DMAy Channelx flag is set or not. More... | |

| ITStatus | DMA_GetITStatus (uint32_t DMAy_IT) |

| Checks whether the specified DMAy Channelx interrupt has occurred or not. More... | |

| void | DMA_Init (DMA_Channel_TypeDef *DMAy_Channelx, DMA_InitTypeDef *DMA_InitStruct) |

| Initializes the DMAy Channelx according to the specified parameters in the DMA_InitStruct. More... | |

| void | DMA_ITConfig (DMA_Channel_TypeDef *DMAy_Channelx, uint32_t DMA_IT, FunctionalState NewState) |

| Enables or disables the specified DMAy Channelx interrupts. More... | |

| void | DMA_SetCurrDataCounter (DMA_Channel_TypeDef *DMAy_Channelx, uint16_t DataNumber) |

| Sets the number of data units in the current DMAy Channelx transfer. More... | |

| void | DMA_StructInit (DMA_InitTypeDef *DMA_InitStruct) |

| Fills each DMA_InitStruct member with its default value. More... | |

Detailed Description

This file contains all the functions prototypes for the DMA firmware library.

- Version

- V1.1.1

- Date

- 04-April-2014

- Attention

© COPYRIGHT 2014 STMicroelectronics

Licensed under MCD-ST Liberty SW License Agreement V2, (the "License"); You may not use this file except in compliance with the License. You may obtain a copy of the License at:

http://www.st.com/software_license_agreement_liberty_v2

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

Definition in file stm32f30x_dma.h.