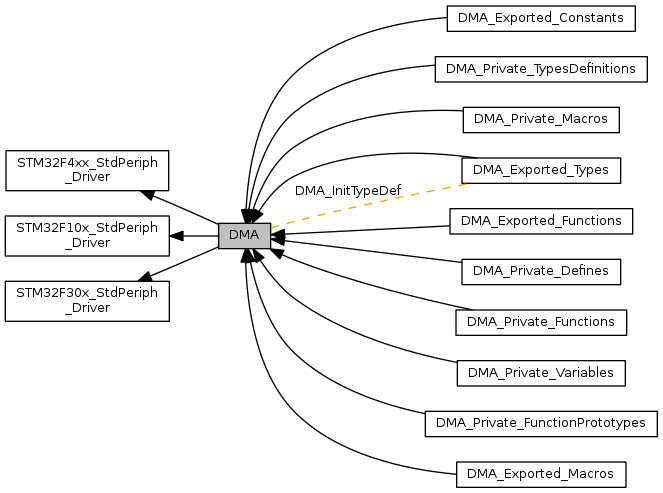

DMA driver modules. More...

|

Classes | |

| struct | DMA_InitTypeDef |

| DMA Init structure definition. More... | |

Functions | |

| void | DMA_ClearFlag (uint32_t DMAy_FLAG) |

| Clears the DMAy Channelx's pending flags. More... | |

| void | DMA_ClearFlag (DMA_Stream_TypeDef *DMAy_Streamx, uint32_t DMA_FLAG) |

| Clears the DMAy Streamx's pending flags. More... | |

| void | DMA_ClearITPendingBit (uint32_t DMAy_IT) |

| Clears the DMAy Channelx's interrupt pending bits. More... | |

| void | DMA_ClearITPendingBit (DMA_Stream_TypeDef *DMAy_Streamx, uint32_t DMA_IT) |

| Clears the DMAy Streamx's interrupt pending bits. More... | |

| void | DMA_Cmd (DMA_Channel_TypeDef *DMAy_Channelx, FunctionalState NewState) |

| Enables or disables the specified DMAy Channelx. More... | |

| void | DMA_Cmd (DMA_Stream_TypeDef *DMAy_Streamx, FunctionalState NewState) |

| Enables or disables the specified DMAy Streamx. More... | |

| void | DMA_DeInit (DMA_Channel_TypeDef *DMAy_Channelx) |

| Deinitializes the DMAy Channelx registers to their default reset values. More... | |

| void | DMA_DeInit (DMA_Stream_TypeDef *DMAy_Streamx) |

| Deinitialize the DMAy Streamx registers to their default reset values. More... | |

| void | DMA_DoubleBufferModeCmd (DMA_Stream_TypeDef *DMAy_Streamx, FunctionalState NewState) |

| Enables or disables the double buffer mode for the selected DMA stream. More... | |

| void | DMA_DoubleBufferModeConfig (DMA_Stream_TypeDef *DMAy_Streamx, uint32_t Memory1BaseAddr, uint32_t DMA_CurrentMemory) |

| Configures, when the DMAy Streamx is disabled, the double buffer mode and the current memory target. More... | |

| void | DMA_FlowControllerConfig (DMA_Stream_TypeDef *DMAy_Streamx, uint32_t DMA_FlowCtrl) |

| Configures, when the DMAy Streamx is disabled, the flow controller for the next transactions (Peripheral or Memory). More... | |

| FunctionalState | DMA_GetCmdStatus (DMA_Stream_TypeDef *DMAy_Streamx) |

| Returns the status of EN bit for the specified DMAy Streamx. More... | |

| uint16_t | DMA_GetCurrDataCounter (DMA_Channel_TypeDef *DMAy_Channelx) |

| Returns the number of remaining data units in the current DMAy Channelx transfer. More... | |

| uint16_t | DMA_GetCurrDataCounter (DMA_Stream_TypeDef *DMAy_Streamx) |

| Returns the number of remaining data units in the current DMAy Streamx transfer. More... | |

| uint32_t | DMA_GetCurrentMemoryTarget (DMA_Stream_TypeDef *DMAy_Streamx) |

| Returns the current memory target used by double buffer transfer. More... | |

| uint32_t | DMA_GetFIFOStatus (DMA_Stream_TypeDef *DMAy_Streamx) |

| Returns the current DMAy Streamx FIFO filled level. More... | |

| FlagStatus | DMA_GetFlagStatus (uint32_t DMAy_FLAG) |

| Checks whether the specified DMAy Channelx flag is set or not. More... | |

| FlagStatus | DMA_GetFlagStatus (DMA_Stream_TypeDef *DMAy_Streamx, uint32_t DMA_FLAG) |

| Checks whether the specified DMAy Streamx flag is set or not. More... | |

| ITStatus | DMA_GetITStatus (uint32_t DMAy_IT) |

| Checks whether the specified DMAy Channelx interrupt has occurred or not. More... | |

| ITStatus | DMA_GetITStatus (DMA_Stream_TypeDef *DMAy_Streamx, uint32_t DMA_IT) |

| Checks whether the specified DMAy Streamx interrupt has occurred or not. More... | |

| void | DMA_Init (DMA_Channel_TypeDef *DMAy_Channelx, DMA_InitTypeDef *DMA_InitStruct) |

| Initializes the DMAy Channelx according to the specified parameters in the DMA_InitStruct. More... | |

| void | DMA_Init (DMA_Stream_TypeDef *DMAy_Streamx, DMA_InitTypeDef *DMA_InitStruct) |

| Initializes the DMAy Streamx according to the specified parameters in the DMA_InitStruct structure. More... | |

| void | DMA_ITConfig (DMA_Channel_TypeDef *DMAy_Channelx, uint32_t DMA_IT, FunctionalState NewState) |

| Enables or disables the specified DMAy Channelx interrupts. More... | |

| void | DMA_ITConfig (DMA_Stream_TypeDef *DMAy_Streamx, uint32_t DMA_IT, FunctionalState NewState) |

| Enables or disables the specified DMAy Streamx interrupts. More... | |

| void | DMA_MemoryTargetConfig (DMA_Stream_TypeDef *DMAy_Streamx, uint32_t MemoryBaseAddr, uint32_t DMA_MemoryTarget) |

| Configures the Memory address for the next buffer transfer in double buffer mode (for dynamic use). This function can be called when the DMA Stream is enabled and when the transfer is ongoing. More... | |

| void | DMA_PeriphIncOffsetSizeConfig (DMA_Stream_TypeDef *DMAy_Streamx, uint32_t DMA_Pincos) |

| Configures, when the PINC (Peripheral Increment address mode) bit is set, if the peripheral address should be incremented with the data size (configured with PSIZE bits) or by a fixed offset equal to 4 (32-bit aligned addresses). More... | |

| void | DMA_SetCurrDataCounter (DMA_Channel_TypeDef *DMAy_Channelx, uint16_t DataNumber) |

| Sets the number of data units in the current DMAy Channelx transfer. More... | |

| void | DMA_SetCurrDataCounter (DMA_Stream_TypeDef *DMAy_Streamx, uint16_t Counter) |

| Writes the number of data units to be transferred on the DMAy Streamx. More... | |

Detailed Description

DMA driver modules.

Macro Definition Documentation

| #define CCR_CLEAR_MASK ((uint32_t)0xFFFF800F) /* DMA Channel config registers Masks */ |

Definition at line 87 of file stm32f30x_dma.c.

| #define DMA1_CHANNEL1_IT_MASK ((uint32_t)(DMA_ISR_GIF1 | DMA_ISR_TCIF1 | DMA_ISR_HTIF1 | DMA_ISR_TEIF1)) |

Definition at line 92 of file stm32f30x_dma.c.

| #define DMA1_CHANNEL2_IT_MASK ((uint32_t)(DMA_ISR_GIF2 | DMA_ISR_TCIF2 | DMA_ISR_HTIF2 | DMA_ISR_TEIF2)) |

Definition at line 93 of file stm32f30x_dma.c.

| #define DMA1_CHANNEL3_IT_MASK ((uint32_t)(DMA_ISR_GIF3 | DMA_ISR_TCIF3 | DMA_ISR_HTIF3 | DMA_ISR_TEIF3)) |

Definition at line 94 of file stm32f30x_dma.c.

| #define DMA1_CHANNEL4_IT_MASK ((uint32_t)(DMA_ISR_GIF4 | DMA_ISR_TCIF4 | DMA_ISR_HTIF4 | DMA_ISR_TEIF4)) |

Definition at line 95 of file stm32f30x_dma.c.

| #define DMA1_CHANNEL5_IT_MASK ((uint32_t)(DMA_ISR_GIF5 | DMA_ISR_TCIF5 | DMA_ISR_HTIF5 | DMA_ISR_TEIF5)) |

Definition at line 96 of file stm32f30x_dma.c.

| #define DMA1_CHANNEL6_IT_MASK ((uint32_t)(DMA_ISR_GIF6 | DMA_ISR_TCIF6 | DMA_ISR_HTIF6 | DMA_ISR_TEIF6)) |

Definition at line 97 of file stm32f30x_dma.c.

| #define DMA1_CHANNEL7_IT_MASK ((uint32_t)(DMA_ISR_GIF7 | DMA_ISR_TCIF7 | DMA_ISR_HTIF7 | DMA_ISR_TEIF7)) |

Definition at line 98 of file stm32f30x_dma.c.

| #define DMA2_CHANNEL1_IT_MASK ((uint32_t)(DMA_ISR_GIF1 | DMA_ISR_TCIF1 | DMA_ISR_HTIF1 | DMA_ISR_TEIF1)) |

Definition at line 101 of file stm32f30x_dma.c.

| #define DMA2_CHANNEL2_IT_MASK ((uint32_t)(DMA_ISR_GIF2 | DMA_ISR_TCIF2 | DMA_ISR_HTIF2 | DMA_ISR_TEIF2)) |

Definition at line 102 of file stm32f30x_dma.c.

| #define DMA2_CHANNEL3_IT_MASK ((uint32_t)(DMA_ISR_GIF3 | DMA_ISR_TCIF3 | DMA_ISR_HTIF3 | DMA_ISR_TEIF3)) |

Definition at line 103 of file stm32f30x_dma.c.

| #define DMA2_CHANNEL4_IT_MASK ((uint32_t)(DMA_ISR_GIF4 | DMA_ISR_TCIF4 | DMA_ISR_HTIF4 | DMA_ISR_TEIF4)) |

Definition at line 104 of file stm32f30x_dma.c.

| #define DMA2_CHANNEL5_IT_MASK ((uint32_t)(DMA_ISR_GIF5 | DMA_ISR_TCIF5 | DMA_ISR_HTIF5 | DMA_ISR_TEIF5)) |

Definition at line 105 of file stm32f30x_dma.c.

| #define DMA_Stream0_IT_MASK |

Definition at line 143 of file stm32f4xx_dma.c.

| #define DMA_Stream1_IT_MASK (uint32_t)(DMA_Stream0_IT_MASK << 6) |

Definition at line 147 of file stm32f4xx_dma.c.

| #define DMA_Stream2_IT_MASK (uint32_t)(DMA_Stream0_IT_MASK << 16) |

Definition at line 148 of file stm32f4xx_dma.c.

| #define DMA_Stream3_IT_MASK (uint32_t)(DMA_Stream0_IT_MASK << 22) |

Definition at line 149 of file stm32f4xx_dma.c.

| #define DMA_Stream4_IT_MASK (uint32_t)(DMA_Stream0_IT_MASK | (uint32_t)0x20000000) |

Definition at line 150 of file stm32f4xx_dma.c.

| #define DMA_Stream5_IT_MASK (uint32_t)(DMA_Stream1_IT_MASK | (uint32_t)0x20000000) |

Definition at line 151 of file stm32f4xx_dma.c.

| #define DMA_Stream6_IT_MASK (uint32_t)(DMA_Stream2_IT_MASK | (uint32_t)0x20000000) |

Definition at line 152 of file stm32f4xx_dma.c.

| #define DMA_Stream7_IT_MASK (uint32_t)(DMA_Stream3_IT_MASK | (uint32_t)0x20000000) |

Definition at line 153 of file stm32f4xx_dma.c.

| #define FLAG_Mask ((uint32_t)0x10000000) /* DMA2 FLAG mask */ |

Definition at line 88 of file stm32f30x_dma.c.

| #define HIGH_ISR_MASK (uint32_t)0x20000000 |

Definition at line 155 of file stm32f4xx_dma.c.

| #define RESERVED_MASK (uint32_t)0x0F7D0F7D |

Definition at line 156 of file stm32f4xx_dma.c.

| #define TRANSFER_IT_ENABLE_MASK |

Definition at line 140 of file stm32f4xx_dma.c.

| #define TRANSFER_IT_MASK (uint32_t)0x0F3C0F3C |

Definition at line 154 of file stm32f4xx_dma.c.

Function Documentation

| void DMA_ClearFlag | ( | uint32_t | DMAy_FLAG | ) |

Clears the DMAy Channelx's pending flags.

- Parameters

-

DMAy_FLAG specifies the flag to clear. This parameter can be any combination (for the same DMA) of the following values: - DMA1_FLAG_GL1: DMA1 Channel1 global flag.

- DMA1_FLAG_TC1: DMA1 Channel1 transfer complete flag.

- DMA1_FLAG_HT1: DMA1 Channel1 half transfer flag.

- DMA1_FLAG_TE1: DMA1 Channel1 transfer error flag.

- DMA1_FLAG_GL2: DMA1 Channel2 global flag.

- DMA1_FLAG_TC2: DMA1 Channel2 transfer complete flag.

- DMA1_FLAG_HT2: DMA1 Channel2 half transfer flag.

- DMA1_FLAG_TE2: DMA1 Channel2 transfer error flag.

- DMA1_FLAG_GL3: DMA1 Channel3 global flag.

- DMA1_FLAG_TC3: DMA1 Channel3 transfer complete flag.

- DMA1_FLAG_HT3: DMA1 Channel3 half transfer flag.

- DMA1_FLAG_TE3: DMA1 Channel3 transfer error flag.

- DMA1_FLAG_GL4: DMA1 Channel4 global flag.

- DMA1_FLAG_TC4: DMA1 Channel4 transfer complete flag.

- DMA1_FLAG_HT4: DMA1 Channel4 half transfer flag.

- DMA1_FLAG_TE4: DMA1 Channel4 transfer error flag.

- DMA1_FLAG_GL5: DMA1 Channel5 global flag.

- DMA1_FLAG_TC5: DMA1 Channel5 transfer complete flag.

- DMA1_FLAG_HT5: DMA1 Channel5 half transfer flag.

- DMA1_FLAG_TE5: DMA1 Channel5 transfer error flag.

- DMA1_FLAG_GL6: DMA1 Channel6 global flag.

- DMA1_FLAG_TC6: DMA1 Channel6 transfer complete flag.

- DMA1_FLAG_HT6: DMA1 Channel6 half transfer flag.

- DMA1_FLAG_TE6: DMA1 Channel6 transfer error flag.

- DMA1_FLAG_GL7: DMA1 Channel7 global flag.

- DMA1_FLAG_TC7: DMA1 Channel7 transfer complete flag.

- DMA1_FLAG_HT7: DMA1 Channel7 half transfer flag.

- DMA1_FLAG_TE7: DMA1 Channel7 transfer error flag.

- DMA2_FLAG_GL1: DMA2 Channel1 global flag.

- DMA2_FLAG_TC1: DMA2 Channel1 transfer complete flag.

- DMA2_FLAG_HT1: DMA2 Channel1 half transfer flag.

- DMA2_FLAG_TE1: DMA2 Channel1 transfer error flag.

- DMA2_FLAG_GL2: DMA2 Channel2 global flag.

- DMA2_FLAG_TC2: DMA2 Channel2 transfer complete flag.

- DMA2_FLAG_HT2: DMA2 Channel2 half transfer flag.

- DMA2_FLAG_TE2: DMA2 Channel2 transfer error flag.

- DMA2_FLAG_GL3: DMA2 Channel3 global flag.

- DMA2_FLAG_TC3: DMA2 Channel3 transfer complete flag.

- DMA2_FLAG_HT3: DMA2 Channel3 half transfer flag.

- DMA2_FLAG_TE3: DMA2 Channel3 transfer error flag.

- DMA2_FLAG_GL4: DMA2 Channel4 global flag.

- DMA2_FLAG_TC4: DMA2 Channel4 transfer complete flag.

- DMA2_FLAG_HT4: DMA2 Channel4 half transfer flag.

- DMA2_FLAG_TE4: DMA2 Channel4 transfer error flag.

- DMA2_FLAG_GL5: DMA2 Channel5 global flag.

- DMA2_FLAG_TC5: DMA2 Channel5 transfer complete flag.

- DMA2_FLAG_HT5: DMA2 Channel5 half transfer flag.

- DMA2_FLAG_TE5: DMA2 Channel5 transfer error flag.

- Return values

-

None

- Parameters

-

DMAy_FLAG specifies the flag to clear. This parameter can be any combination (for the same DMA) of the following values: - DMA1_FLAG_GL1: DMA1 Channel1 global flag.

- DMA1_FLAG_TC1: DMA1 Channel1 transfer complete flag.

- DMA1_FLAG_HT1: DMA1 Channel1 half transfer flag.

- DMA1_FLAG_TE1: DMA1 Channel1 transfer error flag.

- DMA1_FLAG_GL2: DMA1 Channel2 global flag.

- DMA1_FLAG_TC2: DMA1 Channel2 transfer complete flag.

- DMA1_FLAG_HT2: DMA1 Channel2 half transfer flag.

- DMA1_FLAG_TE2: DMA1 Channel2 transfer error flag.

- DMA1_FLAG_GL3: DMA1 Channel3 global flag.

- DMA1_FLAG_TC3: DMA1 Channel3 transfer complete flag.

- DMA1_FLAG_HT3: DMA1 Channel3 half transfer flag.

- DMA1_FLAG_TE3: DMA1 Channel3 transfer error flag.

- DMA1_FLAG_GL4: DMA1 Channel4 global flag.

- DMA1_FLAG_TC4: DMA1 Channel4 transfer complete flag.

- DMA1_FLAG_HT4: DMA1 Channel4 half transfer flag.

- DMA1_FLAG_TE4: DMA1 Channel4 transfer error flag.

- DMA1_FLAG_GL5: DMA1 Channel5 global flag.

- DMA1_FLAG_TC5: DMA1 Channel5 transfer complete flag.

- DMA1_FLAG_HT5: DMA1 Channel5 half transfer flag.

- DMA1_FLAG_TE5: DMA1 Channel5 transfer error flag.

- DMA1_FLAG_GL6: DMA1 Channel6 global flag.

- DMA1_FLAG_TC6: DMA1 Channel6 transfer complete flag.

- DMA1_FLAG_HT6: DMA1 Channel6 half transfer flag.

- DMA1_FLAG_TE6: DMA1 Channel6 transfer error flag.

- DMA1_FLAG_GL7: DMA1 Channel7 global flag.

- DMA1_FLAG_TC7: DMA1 Channel7 transfer complete flag.

- DMA1_FLAG_HT7: DMA1 Channel7 half transfer flag.

- DMA1_FLAG_TE7: DMA1 Channel7 transfer error flag.

- DMA2_FLAG_GL1: DMA2 Channel1 global flag.

- DMA2_FLAG_TC1: DMA2 Channel1 transfer complete flag.

- DMA2_FLAG_HT1: DMA2 Channel1 half transfer flag.

- DMA2_FLAG_TE1: DMA2 Channel1 transfer error flag.

- DMA2_FLAG_GL2: DMA2 Channel2 global flag.

- DMA2_FLAG_TC2: DMA2 Channel2 transfer complete flag.

- DMA2_FLAG_HT2: DMA2 Channel2 half transfer flag.

- DMA2_FLAG_TE2: DMA2 Channel2 transfer error flag.

- DMA2_FLAG_GL3: DMA2 Channel3 global flag.

- DMA2_FLAG_TC3: DMA2 Channel3 transfer complete flag.

- DMA2_FLAG_HT3: DMA2 Channel3 half transfer flag.

- DMA2_FLAG_TE3: DMA2 Channel3 transfer error flag.

- DMA2_FLAG_GL4: DMA2 Channel4 global flag.

- DMA2_FLAG_TC4: DMA2 Channel4 transfer complete flag.

- DMA2_FLAG_HT4: DMA2 Channel4 half transfer flag.

- DMA2_FLAG_TE4: DMA2 Channel4 transfer error flag.

- DMA2_FLAG_GL5: DMA2 Channel5 global flag.

- DMA2_FLAG_TC5: DMA2 Channel5 transfer complete flag.

- DMA2_FLAG_HT5: DMA2 Channel5 half transfer flag.

- DMA2_FLAG_TE5: DMA2 Channel5 transfer error flag.

- Note

- Clearing the Global flag (DMAy_FLAG_GLx) results in clearing all other flags relative to the same channel (Transfer Complete, Half-transfer Complete and Transfer Error flags: DMAy_FLAG_TCx, DMAy_FLAG_HTx and DMAy_FLAG_TEx).

- Return values

-

None

Definition at line 523 of file stm32f10x_dma.c.

| void DMA_ClearFlag | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| uint32_t | DMA_FLAG | ||

| ) |

Clears the DMAy Streamx's pending flags.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. DMA_FLAG specifies the flag to clear. This parameter can be any combination of the following values: - DMA_FLAG_TCIFx: Streamx transfer complete flag

- DMA_FLAG_HTIFx: Streamx half transfer complete flag

- DMA_FLAG_TEIFx: Streamx transfer error flag

- DMA_FLAG_DMEIFx: Streamx direct mode error flag

- DMA_FLAG_FEIFx: Streamx FIFO error flag Where x can be 0 to 7 to select the DMA Stream.

- Return values

-

None

Definition at line 1071 of file stm32f4xx_dma.c.

| void DMA_ClearITPendingBit | ( | uint32_t | DMAy_IT | ) |

Clears the DMAy Channelx's interrupt pending bits.

- Parameters

-

DMAy_IT specifies the DMAy interrupt pending bit to clear. This parameter can be any combination (for the same DMA) of the following values: - DMA1_IT_GL1: DMA1 Channel1 global interrupt.

- DMA1_IT_TC1: DMA1 Channel1 transfer complete interrupt.

- DMA1_IT_HT1: DMA1 Channel1 half transfer interrupt.

- DMA1_IT_TE1: DMA1 Channel1 transfer error interrupt.

- DMA1_IT_GL2: DMA1 Channel2 global interrupt.

- DMA1_IT_TC2: DMA1 Channel2 transfer complete interrupt.

- DMA1_IT_HT2: DMA1 Channel2 half transfer interrupt.

- DMA1_IT_TE2: DMA1 Channel2 transfer error interrupt.

- DMA1_IT_GL3: DMA1 Channel3 global interrupt.

- DMA1_IT_TC3: DMA1 Channel3 transfer complete interrupt.

- DMA1_IT_HT3: DMA1 Channel3 half transfer interrupt.

- DMA1_IT_TE3: DMA1 Channel3 transfer error interrupt.

- DMA1_IT_GL4: DMA1 Channel4 global interrupt.

- DMA1_IT_TC4: DMA1 Channel4 transfer complete interrupt.

- DMA1_IT_HT4: DMA1 Channel4 half transfer interrupt.

- DMA1_IT_TE4: DMA1 Channel4 transfer error interrupt.

- DMA1_IT_GL5: DMA1 Channel5 global interrupt.

- DMA1_IT_TC5: DMA1 Channel5 transfer complete interrupt.

- DMA1_IT_HT5: DMA1 Channel5 half transfer interrupt.

- DMA1_IT_TE5: DMA1 Channel5 transfer error interrupt.

- DMA1_IT_GL6: DMA1 Channel6 global interrupt.

- DMA1_IT_TC6: DMA1 Channel6 transfer complete interrupt.

- DMA1_IT_HT6: DMA1 Channel6 half transfer interrupt.

- DMA1_IT_TE6: DMA1 Channel6 transfer error interrupt.

- DMA1_IT_GL7: DMA1 Channel7 global interrupt.

- DMA1_IT_TC7: DMA1 Channel7 transfer complete interrupt.

- DMA1_IT_HT7: DMA1 Channel7 half transfer interrupt.

- DMA1_IT_TE7: DMA1 Channel7 transfer error interrupt.

- DMA2_IT_GL1: DMA2 Channel1 global interrupt.

- DMA2_IT_TC1: DMA2 Channel1 transfer complete interrupt.

- DMA2_IT_HT1: DMA2 Channel1 half transfer interrupt.

- DMA2_IT_TE1: DMA2 Channel1 transfer error interrupt.

- DMA2_IT_GL2: DMA2 Channel2 global interrupt.

- DMA2_IT_TC2: DMA2 Channel2 transfer complete interrupt.

- DMA2_IT_HT2: DMA2 Channel2 half transfer interrupt.

- DMA2_IT_TE2: DMA2 Channel2 transfer error interrupt.

- DMA2_IT_GL3: DMA2 Channel3 global interrupt.

- DMA2_IT_TC3: DMA2 Channel3 transfer complete interrupt.

- DMA2_IT_HT3: DMA2 Channel3 half transfer interrupt.

- DMA2_IT_TE3: DMA2 Channel3 transfer error interrupt.

- DMA2_IT_GL4: DMA2 Channel4 global interrupt.

- DMA2_IT_TC4: DMA2 Channel4 transfer complete interrupt.

- DMA2_IT_HT4: DMA2 Channel4 half transfer interrupt.

- DMA2_IT_TE4: DMA2 Channel4 transfer error interrupt.

- DMA2_IT_GL5: DMA2 Channel5 global interrupt.

- DMA2_IT_TC5: DMA2 Channel5 transfer complete interrupt.

- DMA2_IT_HT5: DMA2 Channel5 half transfer interrupt.

- DMA2_IT_TE5: DMA2 Channel5 transfer error interrupt.

- Return values

-

None

- Parameters

-

DMAy_IT specifies the DMAy interrupt pending bit to clear. This parameter can be any combination (for the same DMA) of the following values: - DMA1_IT_GL1: DMA1 Channel1 global interrupt.

- DMA1_IT_TC1: DMA1 Channel1 transfer complete interrupt.

- DMA1_IT_HT1: DMA1 Channel1 half transfer interrupt.

- DMA1_IT_TE1: DMA1 Channel1 transfer error interrupt.

- DMA1_IT_GL2: DMA1 Channel2 global interrupt.

- DMA1_IT_TC2: DMA1 Channel2 transfer complete interrupt.

- DMA1_IT_HT2: DMA1 Channel2 half transfer interrupt.

- DMA1_IT_TE2: DMA1 Channel2 transfer error interrupt.

- DMA1_IT_GL3: DMA1 Channel3 global interrupt.

- DMA1_IT_TC3: DMA1 Channel3 transfer complete interrupt.

- DMA1_IT_HT3: DMA1 Channel3 half transfer interrupt.

- DMA1_IT_TE3: DMA1 Channel3 transfer error interrupt.

- DMA1_IT_GL4: DMA1 Channel4 global interrupt.

- DMA1_IT_TC4: DMA1 Channel4 transfer complete interrupt.

- DMA1_IT_HT4: DMA1 Channel4 half transfer interrupt.

- DMA1_IT_TE4: DMA1 Channel4 transfer error interrupt.

- DMA1_IT_GL5: DMA1 Channel5 global interrupt.

- DMA1_IT_TC5: DMA1 Channel5 transfer complete interrupt.

- DMA1_IT_HT5: DMA1 Channel5 half transfer interrupt.

- DMA1_IT_TE5: DMA1 Channel5 transfer error interrupt.

- DMA1_IT_GL6: DMA1 Channel6 global interrupt.

- DMA1_IT_TC6: DMA1 Channel6 transfer complete interrupt.

- DMA1_IT_HT6: DMA1 Channel6 half transfer interrupt.

- DMA1_IT_TE6: DMA1 Channel6 transfer error interrupt.

- DMA1_IT_GL7: DMA1 Channel7 global interrupt.

- DMA1_IT_TC7: DMA1 Channel7 transfer complete interrupt.

- DMA1_IT_HT7: DMA1 Channel7 half transfer interrupt.

- DMA1_IT_TE7: DMA1 Channel7 transfer error interrupt.

- DMA2_IT_GL1: DMA2 Channel1 global interrupt.

- DMA2_IT_TC1: DMA2 Channel1 transfer complete interrupt.

- DMA2_IT_HT1: DMA2 Channel1 half transfer interrupt.

- DMA2_IT_TE1: DMA2 Channel1 transfer error interrupt.

- DMA2_IT_GL2: DMA2 Channel2 global interrupt.

- DMA2_IT_TC2: DMA2 Channel2 transfer complete interrupt.

- DMA2_IT_HT2: DMA2 Channel2 half transfer interrupt.

- DMA2_IT_TE2: DMA2 Channel2 transfer error interrupt.

- DMA2_IT_GL3: DMA2 Channel3 global interrupt.

- DMA2_IT_TC3: DMA2 Channel3 transfer complete interrupt.

- DMA2_IT_HT3: DMA2 Channel3 half transfer interrupt.

- DMA2_IT_TE3: DMA2 Channel3 transfer error interrupt.

- DMA2_IT_GL4: DMA2 Channel4 global interrupt.

- DMA2_IT_TC4: DMA2 Channel4 transfer complete interrupt.

- DMA2_IT_HT4: DMA2 Channel4 half transfer interrupt.

- DMA2_IT_TE4: DMA2 Channel4 transfer error interrupt.

- DMA2_IT_GL5: DMA2 Channel5 global interrupt.

- DMA2_IT_TC5: DMA2 Channel5 transfer complete interrupt.

- DMA2_IT_HT5: DMA2 Channel5 half transfer interrupt.

- DMA2_IT_TE5: DMA2 Channel5 transfer error interrupt.

- Note

- Clearing the Global interrupt (DMAy_IT_GLx) results in clearing all other interrupts relative to the same channel (Transfer Complete, Half-transfer Complete and Transfer Error interrupts: DMAy_IT_TCx, DMAy_IT_HTx and DMAy_IT_TEx).

- Return values

-

None

Definition at line 684 of file stm32f10x_dma.c.

| void DMA_ClearITPendingBit | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| uint32_t | DMA_IT | ||

| ) |

Clears the DMAy Streamx's interrupt pending bits.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. DMA_IT specifies the DMA interrupt pending bit to clear. This parameter can be any combination of the following values: - DMA_IT_TCIFx: Streamx transfer complete interrupt

- DMA_IT_HTIFx: Streamx half transfer complete interrupt

- DMA_IT_TEIFx: Streamx transfer error interrupt

- DMA_IT_DMEIFx: Streamx direct mode error interrupt

- DMA_IT_FEIFx: Streamx FIFO error interrupt Where x can be 0 to 7 to select the DMA Stream.

- Return values

-

None

Definition at line 1252 of file stm32f4xx_dma.c.

| void DMA_Cmd | ( | DMA_Channel_TypeDef * | DMAy_Channelx, |

| FunctionalState | NewState | ||

| ) |

Enables or disables the specified DMAy Channelx.

- Parameters

-

DMAy_Channelx where y can be 1 or 2 to select the DMA and x can be 1 to 7 for DMA1 and 1 to 5 for DMA2 to select the DMA Channel. NewState new state of the DMAy Channelx. This parameter can be: ENABLE or DISABLE.

- Return values

-

None

Definition at line 294 of file stm32f10x_dma.c.

| void DMA_Cmd | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| FunctionalState | NewState | ||

| ) |

Enables or disables the specified DMAy Streamx.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. NewState new state of the DMAy Streamx. This parameter can be: ENABLE or DISABLE.

- Note

- This function may be used to perform Pause-Resume operation. When a transfer is ongoing, calling this function to disable the Stream will cause the transfer to be paused. All configuration registers and the number of remaining data will be preserved. When calling again this function to re-enable the Stream, the transfer will be resumed from the point where it was paused.

- After configuring the DMA Stream (DMA_Init() function) and enabling the stream, it is recommended to check (or wait until) the DMA Stream is effectively enabled. A Stream may remain disabled if a configuration parameter is wrong. After disabling a DMA Stream, it is also recommended to check (or wait until) the DMA Stream is effectively disabled. If a Stream is disabled while a data transfer is ongoing, the current data will be transferred and the Stream will be effectively disabled only after the transfer of this single data is finished.

- Return values

-

None

Definition at line 478 of file stm32f4xx_dma.c.

| void DMA_DeInit | ( | DMA_Channel_TypeDef * | DMAy_Channelx | ) |

Deinitializes the DMAy Channelx registers to their default reset values.

- Parameters

-

DMAy_Channelx where y can be 1 or 2 to select the DMA and x can be 1 to 7 for DMA1 and 1 to 5 for DMA2 to select the DMA Channel.

- Return values

-

None

Definition at line 108 of file stm32f10x_dma.c.

| void DMA_DeInit | ( | DMA_Stream_TypeDef * | DMAy_Streamx | ) |

Deinitialize the DMAy Streamx registers to their default reset values.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream.

- Return values

-

None

Definition at line 196 of file stm32f4xx_dma.c.

| void DMA_DoubleBufferModeCmd | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| FunctionalState | NewState | ||

| ) |

Enables or disables the double buffer mode for the selected DMA stream.

- Note

- This function can be called only when the DMA Stream is disabled.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. NewState new state of the DMAy Streamx double buffer mode. This parameter can be: ENABLE or DISABLE.

- Return values

-

None

Definition at line 761 of file stm32f4xx_dma.c.

| void DMA_DoubleBufferModeConfig | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| uint32_t | Memory1BaseAddr, | ||

| uint32_t | DMA_CurrentMemory | ||

| ) |

Configures, when the DMAy Streamx is disabled, the double buffer mode and the current memory target.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. Memory1BaseAddr the base address of the second buffer (Memory 1) DMA_CurrentMemory specifies which memory will be first buffer for the transactions when the Stream will be enabled. This parameter can be one of the following values: - DMA_Memory_0: Memory 0 is the current buffer.

- DMA_Memory_1: Memory 1 is the current buffer.

- Note

- Memory0BaseAddr is set by the DMA structure configuration in DMA_Init().

- Return values

-

None

Definition at line 730 of file stm32f4xx_dma.c.

| void DMA_FlowControllerConfig | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| uint32_t | DMA_FlowCtrl | ||

| ) |

Configures, when the DMAy Streamx is disabled, the flow controller for the next transactions (Peripheral or Memory).

- Note

- Before enabling this feature, check if the used peripheral supports the Flow Controller mode or not.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. DMA_FlowCtrl specifies the DMA flow controller. This parameter can be one of the following values: - DMA_FlowCtrl_Memory: DMAy_Streamx transactions flow controller is the DMA controller.

- DMA_FlowCtrl_Peripheral: DMAy_Streamx transactions flow controller is the peripheral.

- Return values

-

None

Definition at line 550 of file stm32f4xx_dma.c.

| FunctionalState DMA_GetCmdStatus | ( | DMA_Stream_TypeDef * | DMAy_Streamx | ) |

Returns the status of EN bit for the specified DMAy Streamx.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream.

- Note

- After configuring the DMA Stream (DMA_Init() function) and enabling the stream, it is recommended to check (or wait until) the DMA Stream is effectively enabled. A Stream may remain disabled if a configuration parameter is wrong. After disabling a DMA Stream, it is also recommended to check (or wait until) the DMA Stream is effectively disabled. If a Stream is disabled while a data transfer is ongoing, the current data will be transferred and the Stream will be effectively disabled only after the transfer of this single data is finished.

- Return values

-

Current state of the DMAy Streamx (ENABLE or DISABLE).

Definition at line 943 of file stm32f4xx_dma.c.

| uint16_t DMA_GetCurrDataCounter | ( | DMA_Channel_TypeDef * | DMAy_Channelx | ) |

Returns the number of remaining data units in the current DMAy Channelx transfer.

- Parameters

-

DMAy_Channelx where y can be 1 or 2 to select the DMA and x can be 1 to 7 for DMA1 and 1 to 5 for DMA2 to select the DMA Channel.

- Return values

-

The number of remaining data units in the current DMAy Channelx transfer.

Definition at line 371 of file stm32f10x_dma.c.

| uint16_t DMA_GetCurrDataCounter | ( | DMA_Stream_TypeDef * | DMAy_Streamx | ) |

Returns the number of remaining data units in the current DMAy Streamx transfer.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream.

- Return values

-

The number of remaining data units in the current DMAy Streamx transfer.

Definition at line 647 of file stm32f4xx_dma.c.

| uint32_t DMA_GetCurrentMemoryTarget | ( | DMA_Stream_TypeDef * | DMAy_Streamx | ) |

Returns the current memory target used by double buffer transfer.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream.

- Return values

-

The memory target number: 0 for Memory0 or 1 for Memory1.

Definition at line 828 of file stm32f4xx_dma.c.

| uint32_t DMA_GetFIFOStatus | ( | DMA_Stream_TypeDef * | DMAy_Streamx | ) |

Returns the current DMAy Streamx FIFO filled level.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream.

- Return values

-

The FIFO filling state. - DMA_FIFOStatus_Less1QuarterFull: when FIFO is less than 1 quarter-full and not empty.

- DMA_FIFOStatus_1QuarterFull: if more than 1 quarter-full.

- DMA_FIFOStatus_HalfFull: if more than 1 half-full.

- DMA_FIFOStatus_3QuartersFull: if more than 3 quarters-full.

- DMA_FIFOStatus_Empty: when FIFO is empty

- DMA_FIFOStatus_Full: when FIFO is full

Definition at line 977 of file stm32f4xx_dma.c.

| FlagStatus DMA_GetFlagStatus | ( | uint32_t | DMAy_FLAG | ) |

Checks whether the specified DMAy Channelx flag is set or not.

- Parameters

-

DMAy_FLAG specifies the flag to check. This parameter can be one of the following values: - DMA1_FLAG_GL1: DMA1 Channel1 global flag.

- DMA1_FLAG_TC1: DMA1 Channel1 transfer complete flag.

- DMA1_FLAG_HT1: DMA1 Channel1 half transfer flag.

- DMA1_FLAG_TE1: DMA1 Channel1 transfer error flag.

- DMA1_FLAG_GL2: DMA1 Channel2 global flag.

- DMA1_FLAG_TC2: DMA1 Channel2 transfer complete flag.

- DMA1_FLAG_HT2: DMA1 Channel2 half transfer flag.

- DMA1_FLAG_TE2: DMA1 Channel2 transfer error flag.

- DMA1_FLAG_GL3: DMA1 Channel3 global flag.

- DMA1_FLAG_TC3: DMA1 Channel3 transfer complete flag.

- DMA1_FLAG_HT3: DMA1 Channel3 half transfer flag.

- DMA1_FLAG_TE3: DMA1 Channel3 transfer error flag.

- DMA1_FLAG_GL4: DMA1 Channel4 global flag.

- DMA1_FLAG_TC4: DMA1 Channel4 transfer complete flag.

- DMA1_FLAG_HT4: DMA1 Channel4 half transfer flag.

- DMA1_FLAG_TE4: DMA1 Channel4 transfer error flag.

- DMA1_FLAG_GL5: DMA1 Channel5 global flag.

- DMA1_FLAG_TC5: DMA1 Channel5 transfer complete flag.

- DMA1_FLAG_HT5: DMA1 Channel5 half transfer flag.

- DMA1_FLAG_TE5: DMA1 Channel5 transfer error flag.

- DMA1_FLAG_GL6: DMA1 Channel6 global flag.

- DMA1_FLAG_TC6: DMA1 Channel6 transfer complete flag.

- DMA1_FLAG_HT6: DMA1 Channel6 half transfer flag.

- DMA1_FLAG_TE6: DMA1 Channel6 transfer error flag.

- DMA1_FLAG_GL7: DMA1 Channel7 global flag.

- DMA1_FLAG_TC7: DMA1 Channel7 transfer complete flag.

- DMA1_FLAG_HT7: DMA1 Channel7 half transfer flag.

- DMA1_FLAG_TE7: DMA1 Channel7 transfer error flag.

- DMA2_FLAG_GL1: DMA2 Channel1 global flag.

- DMA2_FLAG_TC1: DMA2 Channel1 transfer complete flag.

- DMA2_FLAG_HT1: DMA2 Channel1 half transfer flag.

- DMA2_FLAG_TE1: DMA2 Channel1 transfer error flag.

- DMA2_FLAG_GL2: DMA2 Channel2 global flag.

- DMA2_FLAG_TC2: DMA2 Channel2 transfer complete flag.

- DMA2_FLAG_HT2: DMA2 Channel2 half transfer flag.

- DMA2_FLAG_TE2: DMA2 Channel2 transfer error flag.

- DMA2_FLAG_GL3: DMA2 Channel3 global flag.

- DMA2_FLAG_TC3: DMA2 Channel3 transfer complete flag.

- DMA2_FLAG_HT3: DMA2 Channel3 half transfer flag.

- DMA2_FLAG_TE3: DMA2 Channel3 transfer error flag.

- DMA2_FLAG_GL4: DMA2 Channel4 global flag.

- DMA2_FLAG_TC4: DMA2 Channel4 transfer complete flag.

- DMA2_FLAG_HT4: DMA2 Channel4 half transfer flag.

- DMA2_FLAG_TE4: DMA2 Channel4 transfer error flag.

- DMA2_FLAG_GL5: DMA2 Channel5 global flag.

- DMA2_FLAG_TC5: DMA2 Channel5 transfer complete flag.

- DMA2_FLAG_HT5: DMA2 Channel5 half transfer flag.

- DMA2_FLAG_TE5: DMA2 Channel5 transfer error flag.

- Return values

-

The new state of DMAy_FLAG (SET or RESET).

- Parameters

-

DMAy_FLAG specifies the flag to check. This parameter can be one of the following values: - DMA1_FLAG_GL1: DMA1 Channel1 global flag.

- DMA1_FLAG_TC1: DMA1 Channel1 transfer complete flag.

- DMA1_FLAG_HT1: DMA1 Channel1 half transfer flag.

- DMA1_FLAG_TE1: DMA1 Channel1 transfer error flag.

- DMA1_FLAG_GL2: DMA1 Channel2 global flag.

- DMA1_FLAG_TC2: DMA1 Channel2 transfer complete flag.

- DMA1_FLAG_HT2: DMA1 Channel2 half transfer flag.

- DMA1_FLAG_TE2: DMA1 Channel2 transfer error flag.

- DMA1_FLAG_GL3: DMA1 Channel3 global flag.

- DMA1_FLAG_TC3: DMA1 Channel3 transfer complete flag.

- DMA1_FLAG_HT3: DMA1 Channel3 half transfer flag.

- DMA1_FLAG_TE3: DMA1 Channel3 transfer error flag.

- DMA1_FLAG_GL4: DMA1 Channel4 global flag.

- DMA1_FLAG_TC4: DMA1 Channel4 transfer complete flag.

- DMA1_FLAG_HT4: DMA1 Channel4 half transfer flag.

- DMA1_FLAG_TE4: DMA1 Channel4 transfer error flag.

- DMA1_FLAG_GL5: DMA1 Channel5 global flag.

- DMA1_FLAG_TC5: DMA1 Channel5 transfer complete flag.

- DMA1_FLAG_HT5: DMA1 Channel5 half transfer flag.

- DMA1_FLAG_TE5: DMA1 Channel5 transfer error flag.

- DMA1_FLAG_GL6: DMA1 Channel6 global flag.

- DMA1_FLAG_TC6: DMA1 Channel6 transfer complete flag.

- DMA1_FLAG_HT6: DMA1 Channel6 half transfer flag.

- DMA1_FLAG_TE6: DMA1 Channel6 transfer error flag.

- DMA1_FLAG_GL7: DMA1 Channel7 global flag.

- DMA1_FLAG_TC7: DMA1 Channel7 transfer complete flag.

- DMA1_FLAG_HT7: DMA1 Channel7 half transfer flag.

- DMA1_FLAG_TE7: DMA1 Channel7 transfer error flag.

- DMA2_FLAG_GL1: DMA2 Channel1 global flag.

- DMA2_FLAG_TC1: DMA2 Channel1 transfer complete flag.

- DMA2_FLAG_HT1: DMA2 Channel1 half transfer flag.

- DMA2_FLAG_TE1: DMA2 Channel1 transfer error flag.

- DMA2_FLAG_GL2: DMA2 Channel2 global flag.

- DMA2_FLAG_TC2: DMA2 Channel2 transfer complete flag.

- DMA2_FLAG_HT2: DMA2 Channel2 half transfer flag.

- DMA2_FLAG_TE2: DMA2 Channel2 transfer error flag.

- DMA2_FLAG_GL3: DMA2 Channel3 global flag.

- DMA2_FLAG_TC3: DMA2 Channel3 transfer complete flag.

- DMA2_FLAG_HT3: DMA2 Channel3 half transfer flag.

- DMA2_FLAG_TE3: DMA2 Channel3 transfer error flag.

- DMA2_FLAG_GL4: DMA2 Channel4 global flag.

- DMA2_FLAG_TC4: DMA2 Channel4 transfer complete flag.

- DMA2_FLAG_HT4: DMA2 Channel4 half transfer flag.

- DMA2_FLAG_TE4: DMA2 Channel4 transfer error flag.

- DMA2_FLAG_GL5: DMA2 Channel5 global flag.

- DMA2_FLAG_TC5: DMA2 Channel5 transfer complete flag.

- DMA2_FLAG_HT5: DMA2 Channel5 half transfer flag.

- DMA2_FLAG_TE5: DMA2 Channel5 transfer error flag.

- Note

- The Global flag (DMAy_FLAG_GLx) is set whenever any of the other flags relative to the same channel is set (Transfer Complete, Half-transfer Complete or Transfer Error flags: DMAy_FLAG_TCx, DMAy_FLAG_HTx or DMAy_FLAG_TEx).

- Return values

-

The new state of DMAy_FLAG (SET or RESET).

Definition at line 433 of file stm32f10x_dma.c.

| FlagStatus DMA_GetFlagStatus | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| uint32_t | DMA_FLAG | ||

| ) |

Checks whether the specified DMAy Streamx flag is set or not.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. DMA_FLAG specifies the flag to check. This parameter can be one of the following values: - DMA_FLAG_TCIFx: Streamx transfer complete flag

- DMA_FLAG_HTIFx: Streamx half transfer complete flag

- DMA_FLAG_TEIFx: Streamx transfer error flag

- DMA_FLAG_DMEIFx: Streamx direct mode error flag

- DMA_FLAG_FEIFx: Streamx FIFO error flag Where x can be 0 to 7 to select the DMA Stream.

- Return values

-

The new state of DMA_FLAG (SET or RESET).

Definition at line 1004 of file stm32f4xx_dma.c.

| ITStatus DMA_GetITStatus | ( | uint32_t | DMAy_IT | ) |

Checks whether the specified DMAy Channelx interrupt has occurred or not.

- Parameters

-

DMAy_IT specifies the DMAy interrupt source to check. This parameter can be one of the following values: - DMA1_IT_GL1: DMA1 Channel1 global interrupt.

- DMA1_IT_TC1: DMA1 Channel1 transfer complete interrupt.

- DMA1_IT_HT1: DMA1 Channel1 half transfer interrupt.

- DMA1_IT_TE1: DMA1 Channel1 transfer error interrupt.

- DMA1_IT_GL2: DMA1 Channel2 global interrupt.

- DMA1_IT_TC2: DMA1 Channel2 transfer complete interrupt.

- DMA1_IT_HT2: DMA1 Channel2 half transfer interrupt.

- DMA1_IT_TE2: DMA1 Channel2 transfer error interrupt.

- DMA1_IT_GL3: DMA1 Channel3 global interrupt.

- DMA1_IT_TC3: DMA1 Channel3 transfer complete interrupt.

- DMA1_IT_HT3: DMA1 Channel3 half transfer interrupt.

- DMA1_IT_TE3: DMA1 Channel3 transfer error interrupt.

- DMA1_IT_GL4: DMA1 Channel4 global interrupt.

- DMA1_IT_TC4: DMA1 Channel4 transfer complete interrupt.

- DMA1_IT_HT4: DMA1 Channel4 half transfer interrupt.

- DMA1_IT_TE4: DMA1 Channel4 transfer error interrupt.

- DMA1_IT_GL5: DMA1 Channel5 global interrupt.

- DMA1_IT_TC5: DMA1 Channel5 transfer complete interrupt.

- DMA1_IT_HT5: DMA1 Channel5 half transfer interrupt.

- DMA1_IT_TE5: DMA1 Channel5 transfer error interrupt.

- DMA1_IT_GL6: DMA1 Channel6 global interrupt.

- DMA1_IT_TC6: DMA1 Channel6 transfer complete interrupt.

- DMA1_IT_HT6: DMA1 Channel6 half transfer interrupt.

- DMA1_IT_TE6: DMA1 Channel6 transfer error interrupt.

- DMA1_IT_GL7: DMA1 Channel7 global interrupt.

- DMA1_IT_TC7: DMA1 Channel7 transfer complete interrupt.

- DMA1_IT_HT7: DMA1 Channel7 half transfer interrupt.

- DMA1_IT_TE7: DMA1 Channel7 transfer error interrupt.

- DMA2_IT_GL1: DMA2 Channel1 global interrupt.

- DMA2_IT_TC1: DMA2 Channel1 transfer complete interrupt.

- DMA2_IT_HT1: DMA2 Channel1 half transfer interrupt.

- DMA2_IT_TE1: DMA2 Channel1 transfer error interrupt.

- DMA2_IT_GL2: DMA2 Channel2 global interrupt.

- DMA2_IT_TC2: DMA2 Channel2 transfer complete interrupt.

- DMA2_IT_HT2: DMA2 Channel2 half transfer interrupt.

- DMA2_IT_TE2: DMA2 Channel2 transfer error interrupt.

- DMA2_IT_GL3: DMA2 Channel3 global interrupt.

- DMA2_IT_TC3: DMA2 Channel3 transfer complete interrupt.

- DMA2_IT_HT3: DMA2 Channel3 half transfer interrupt.

- DMA2_IT_TE3: DMA2 Channel3 transfer error interrupt.

- DMA2_IT_GL4: DMA2 Channel4 global interrupt.

- DMA2_IT_TC4: DMA2 Channel4 transfer complete interrupt.

- DMA2_IT_HT4: DMA2 Channel4 half transfer interrupt.

- DMA2_IT_TE4: DMA2 Channel4 transfer error interrupt.

- DMA2_IT_GL5: DMA2 Channel5 global interrupt.

- DMA2_IT_TC5: DMA2 Channel5 transfer complete interrupt.

- DMA2_IT_HT5: DMA2 Channel5 half transfer interrupt.

- DMA2_IT_TE5: DMA2 Channel5 transfer error interrupt.

- Return values

-

The new state of DMAy_IT (SET or RESET).

- Parameters

-

DMAy_IT specifies the DMAy interrupt source to check. This parameter can be one of the following values: - DMA1_IT_GL1: DMA1 Channel1 global interrupt.

- DMA1_IT_TC1: DMA1 Channel1 transfer complete interrupt.

- DMA1_IT_HT1: DMA1 Channel1 half transfer interrupt.

- DMA1_IT_TE1: DMA1 Channel1 transfer error interrupt.

- DMA1_IT_GL2: DMA1 Channel2 global interrupt.

- DMA1_IT_TC2: DMA1 Channel2 transfer complete interrupt.

- DMA1_IT_HT2: DMA1 Channel2 half transfer interrupt.

- DMA1_IT_TE2: DMA1 Channel2 transfer error interrupt.

- DMA1_IT_GL3: DMA1 Channel3 global interrupt.

- DMA1_IT_TC3: DMA1 Channel3 transfer complete interrupt.

- DMA1_IT_HT3: DMA1 Channel3 half transfer interrupt.

- DMA1_IT_TE3: DMA1 Channel3 transfer error interrupt.

- DMA1_IT_GL4: DMA1 Channel4 global interrupt.

- DMA1_IT_TC4: DMA1 Channel4 transfer complete interrupt.

- DMA1_IT_HT4: DMA1 Channel4 half transfer interrupt.

- DMA1_IT_TE4: DMA1 Channel4 transfer error interrupt.

- DMA1_IT_GL5: DMA1 Channel5 global interrupt.

- DMA1_IT_TC5: DMA1 Channel5 transfer complete interrupt.

- DMA1_IT_HT5: DMA1 Channel5 half transfer interrupt.

- DMA1_IT_TE5: DMA1 Channel5 transfer error interrupt.

- DMA1_IT_GL6: DMA1 Channel6 global interrupt.

- DMA1_IT_TC6: DMA1 Channel6 transfer complete interrupt.

- DMA1_IT_HT6: DMA1 Channel6 half transfer interrupt.

- DMA1_IT_TE6: DMA1 Channel6 transfer error interrupt.

- DMA1_IT_GL7: DMA1 Channel7 global interrupt.

- DMA1_IT_TC7: DMA1 Channel7 transfer complete interrupt.

- DMA1_IT_HT7: DMA1 Channel7 half transfer interrupt.

- DMA1_IT_TE7: DMA1 Channel7 transfer error interrupt.

- DMA2_IT_GL1: DMA2 Channel1 global interrupt.

- DMA2_IT_TC1: DMA2 Channel1 transfer complete interrupt.

- DMA2_IT_HT1: DMA2 Channel1 half transfer interrupt.

- DMA2_IT_TE1: DMA2 Channel1 transfer error interrupt.

- DMA2_IT_GL2: DMA2 Channel2 global interrupt.

- DMA2_IT_TC2: DMA2 Channel2 transfer complete interrupt.

- DMA2_IT_HT2: DMA2 Channel2 half transfer interrupt.

- DMA2_IT_TE2: DMA2 Channel2 transfer error interrupt.

- DMA2_IT_GL3: DMA2 Channel3 global interrupt.

- DMA2_IT_TC3: DMA2 Channel3 transfer complete interrupt.

- DMA2_IT_HT3: DMA2 Channel3 half transfer interrupt.

- DMA2_IT_TE3: DMA2 Channel3 transfer error interrupt.

- DMA2_IT_GL4: DMA2 Channel4 global interrupt.

- DMA2_IT_TC4: DMA2 Channel4 transfer complete interrupt.

- DMA2_IT_HT4: DMA2 Channel4 half transfer interrupt.

- DMA2_IT_TE4: DMA2 Channel4 transfer error interrupt.

- DMA2_IT_GL5: DMA2 Channel5 global interrupt.

- DMA2_IT_TC5: DMA2 Channel5 transfer complete interrupt.

- DMA2_IT_HT5: DMA2 Channel5 half transfer interrupt.

- DMA2_IT_TE5: DMA2 Channel5 transfer error interrupt.

- Note

- The Global interrupt (DMAy_FLAG_GLx) is set whenever any of the other interrupts relative to the same channel is set (Transfer Complete, Half-transfer Complete or Transfer Error interrupts: DMAy_IT_TCx, DMAy_IT_HTx or DMAy_IT_TEx).

- Return values

-

The new state of DMAy_IT (SET or RESET).

Definition at line 595 of file stm32f10x_dma.c.

| ITStatus DMA_GetITStatus | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| uint32_t | DMA_IT | ||

| ) |

Checks whether the specified DMAy Streamx interrupt has occurred or not.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. DMA_IT specifies the DMA interrupt source to check. This parameter can be one of the following values: - DMA_IT_TCIFx: Streamx transfer complete interrupt

- DMA_IT_HTIFx: Streamx half transfer complete interrupt

- DMA_IT_TEIFx: Streamx transfer error interrupt

- DMA_IT_DMEIFx: Streamx direct mode error interrupt

- DMA_IT_FEIFx: Streamx FIFO error interrupt Where x can be 0 to 7 to select the DMA Stream.

- Return values

-

The new state of DMA_IT (SET or RESET).

Definition at line 1170 of file stm32f4xx_dma.c.

| void DMA_Init | ( | DMA_Channel_TypeDef * | DMAy_Channelx, |

| DMA_InitTypeDef * | DMA_InitStruct | ||

| ) |

Initializes the DMAy Channelx according to the specified parameters in the DMA_InitStruct.

- Parameters

-

DMAy_Channelx where y can be 1 or 2 to select the DMA and x can be 1 to 7 for DMA1 and 1 to 5 for DMA2 to select the DMA Channel. DMA_InitStruct pointer to a DMA_InitTypeDef structure that contains the configuration information for the specified DMA Channel.

- Return values

-

None

Definition at line 202 of file stm32f10x_dma.c.

| void DMA_Init | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| DMA_InitTypeDef * | DMA_InitStruct | ||

| ) |

Initializes the DMAy Streamx according to the specified parameters in the DMA_InitStruct structure.

- Note

- Before calling this function, it is recommended to check that the Stream is actually disabled using the function DMA_GetCmdStatus().

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. DMA_InitStruct pointer to a DMA_InitTypeDef structure that contains the configuration information for the specified DMA Stream.

- Return values

-

None

Definition at line 319 of file stm32f4xx_dma.c.

| void DMA_ITConfig | ( | DMA_Channel_TypeDef * | DMAy_Channelx, |

| uint32_t | DMA_IT, | ||

| FunctionalState | NewState | ||

| ) |

Enables or disables the specified DMAy Channelx interrupts.

- Parameters

-

DMAy_Channelx where y can be 1 or 2 to select the DMA and x can be 1 to 7 for DMA1 and 1 to 5 for DMA2 to select the DMA Channel. DMA_IT specifies the DMA interrupts sources to be enabled or disabled. This parameter can be any combination of the following values: - DMA_IT_TC: Transfer complete interrupt mask

- DMA_IT_HT: Half transfer interrupt mask

- DMA_IT_TE: Transfer error interrupt mask

NewState new state of the specified DMA interrupts. This parameter can be: ENABLE or DISABLE.

- Return values

-

None

Definition at line 326 of file stm32f10x_dma.c.

| void DMA_ITConfig | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| uint32_t | DMA_IT, | ||

| FunctionalState | NewState | ||

| ) |

Enables or disables the specified DMAy Streamx interrupts.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. DMA_IT specifies the DMA interrupt sources to be enabled or disabled. This parameter can be any combination of the following values: - DMA_IT_TC: Transfer complete interrupt mask

- DMA_IT_HT: Half transfer complete interrupt mask

- DMA_IT_TE: Transfer error interrupt mask

- DMA_IT_FE: FIFO error interrupt mask

NewState new state of the specified DMA interrupts. This parameter can be: ENABLE or DISABLE.

- Return values

-

None

Definition at line 1118 of file stm32f4xx_dma.c.

| void DMA_MemoryTargetConfig | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| uint32_t | MemoryBaseAddr, | ||

| uint32_t | DMA_MemoryTarget | ||

| ) |

Configures the Memory address for the next buffer transfer in double buffer mode (for dynamic use). This function can be called when the DMA Stream is enabled and when the transfer is ongoing.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. MemoryBaseAddr The base address of the target memory buffer DMA_MemoryTarget Next memory target to be used. This parameter can be one of the following values: - DMA_Memory_0: To use the memory address 0

- DMA_Memory_1: To use the memory address 1

- Note

- It is not allowed to modify the Base Address of a target Memory when this target is involved in the current transfer. ie. If the DMA Stream is currently transferring to/from Memory 1, then it not possible to modify Base address of Memory 1, but it is possible to modify Base address of Memory 0. To know which Memory is currently used, you can use the function DMA_GetCurrentMemoryTarget().

- Return values

-

None

Definition at line 802 of file stm32f4xx_dma.c.

| void DMA_PeriphIncOffsetSizeConfig | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| uint32_t | DMA_Pincos | ||

| ) |

Configures, when the PINC (Peripheral Increment address mode) bit is set, if the peripheral address should be incremented with the data size (configured with PSIZE bits) or by a fixed offset equal to 4 (32-bit aligned addresses).

- Note

- This function has no effect if the Peripheral Increment mode is disabled.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. DMA_Pincos specifies the Peripheral increment offset size. This parameter can be one of the following values: - DMA_PINCOS_Psize: Peripheral address increment is done accordingly to PSIZE parameter.

- DMA_PINCOS_WordAligned: Peripheral address increment offset is fixed to 4 (32-bit aligned addresses).

- Return values

-

None

Definition at line 514 of file stm32f4xx_dma.c.

| void DMA_SetCurrDataCounter | ( | DMA_Channel_TypeDef * | DMAy_Channelx, |

| uint16_t | DataNumber | ||

| ) |

Sets the number of data units in the current DMAy Channelx transfer.

- Parameters

-

DMAy_Channelx where y can be 1 or 2 to select the DMA and x can be 1 to 7 for DMA1 and 1 to 5 for DMA2 to select the DMA Channel. DataNumber The number of data units in the current DMAy Channelx transfer.

- Note

- This function can only be used when the DMAy_Channelx is disabled.

- Return values

-

None.

Definition at line 353 of file stm32f10x_dma.c.

| void DMA_SetCurrDataCounter | ( | DMA_Stream_TypeDef * | DMAy_Streamx, |

| uint16_t | Counter | ||

| ) |

Writes the number of data units to be transferred on the DMAy Streamx.

- Parameters

-

DMAy_Streamx where y can be 1 or 2 to select the DMA and x can be 0 to 7 to select the DMA Stream. Counter Number of data units to be transferred (from 0 to 65535) Number of data items depends only on the Peripheral data format.

- Note

- If Peripheral data format is Bytes: number of data units is equal to total number of bytes to be transferred.

- If Peripheral data format is Half-Word: number of data units is equal to total number of bytes to be transferred / 2.

- If Peripheral data format is Word: number of data units is equal to total number of bytes to be transferred / 4.

- In Memory-to-Memory transfer mode, the memory buffer pointed by DMAy_SxPAR register is considered as Peripheral.

- Return values

-

The number of remaining data units in the current DMAy Streamx transfer.

Definition at line 632 of file stm32f4xx_dma.c.