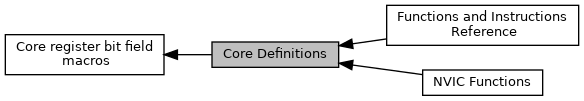

Definitions for base addresses, unions, and structures. More...

Modules | |

| Functions and Instructions Reference | |

| NVIC Functions | |

| Functions that manage interrupts and exceptions via the NVIC. | |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

| #define | SCS_BASE (0xE000E000UL) |

| #define | ITM_BASE (0xE0000000UL) |

| #define | DWT_BASE (0xE0001000UL) |

| #define | TPI_BASE (0xE0040000UL) |

| #define | CoreDebug_BASE (0xE000EDF0UL) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | ITM ((ITM_Type *) ITM_BASE ) |

| #define | DWT ((DWT_Type *) DWT_BASE ) |

| #define | TPI ((TPI_Type *) TPI_BASE ) |

| #define | CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

| #define | FPU_BASE (SCS_BASE + 0x0F30UL) |

| #define | FPU ((FPU_Type *) FPU_BASE ) |

Detailed Description

Definitions for base addresses, unions, and structures.

Macro Definition Documentation

◆ CoreDebug [1/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1127 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ CoreDebug [2/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1127 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ CoreDebug [3/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1127 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ CoreDebug [4/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1127 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ CoreDebug [5/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1202 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm23.h.

◆ CoreDebug [6/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1202 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ CoreDebug [7/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1202 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm23.h.

◆ CoreDebug [8/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1202 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm23.h.

◆ CoreDebug [9/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1374 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_sc300.h.

◆ CoreDebug [10/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1379 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_sc300.h.

◆ CoreDebug [11/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1379 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_sc300.h.

◆ CoreDebug [12/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1379 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_sc300.h.

◆ CoreDebug [13/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1391 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm3.h.

◆ CoreDebug [14/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1399 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm3.h.

◆ CoreDebug [15/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1399 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm3.h.

◆ CoreDebug [16/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1399 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm3.h.

◆ CoreDebug [17/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1561 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ CoreDebug [18/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1570 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ CoreDebug [19/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1570 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ CoreDebug [20/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1570 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ CoreDebug [21/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1570 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ CoreDebug [22/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1570 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ CoreDebug [23/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1778 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ CoreDebug [24/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1778 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ CoreDebug [25/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1778 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ CoreDebug [26/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1778 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ CoreDebug [27/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1784 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ CoreDebug [28/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE) |

Core Debug configuration struct

Definition at line 1784 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ CoreDebug [29/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1894 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ CoreDebug [30/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1969 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ CoreDebug [31/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1969 of file core_cm35p.h.

◆ CoreDebug [32/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1989 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ CoreDebug [33/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1989 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ CoreDebug [34/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 1989 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ CoreDebug [35/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 2050 of file core_armv81mml.h.

◆ CoreDebug [36/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 2064 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ CoreDebug [37/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 2064 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ CoreDebug [38/38]

| #define CoreDebug ((CoreDebug_Type *) CoreDebug_BASE ) |

Core Debug configuration struct

Definition at line 2064 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ CoreDebug_BASE [1/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1116 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ CoreDebug_BASE [2/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1116 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ CoreDebug_BASE [3/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1116 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ CoreDebug_BASE [4/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1116 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ CoreDebug_BASE [5/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1191 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ CoreDebug_BASE [6/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1191 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm23.h.

◆ CoreDebug_BASE [7/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1191 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm23.h.

◆ CoreDebug_BASE [8/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1191 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm23.h.

◆ CoreDebug_BASE [9/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1362 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_sc300.h.

◆ CoreDebug_BASE [10/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1367 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_sc300.h.

◆ CoreDebug_BASE [11/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1367 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_sc300.h.

◆ CoreDebug_BASE [12/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1367 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_sc300.h.

◆ CoreDebug_BASE [13/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1379 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm3.h.

◆ CoreDebug_BASE [14/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1387 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm3.h.

◆ CoreDebug_BASE [15/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1387 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm3.h.

◆ CoreDebug_BASE [16/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1387 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm3.h.

◆ CoreDebug_BASE [17/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1549 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ CoreDebug_BASE [18/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1558 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ CoreDebug_BASE [19/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1558 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ CoreDebug_BASE [20/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1558 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ CoreDebug_BASE [21/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1558 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ CoreDebug_BASE [22/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1558 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ CoreDebug_BASE [23/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1766 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ CoreDebug_BASE [24/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1766 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ CoreDebug_BASE [25/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1766 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ CoreDebug_BASE [26/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1766 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ CoreDebug_BASE [27/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1772 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ CoreDebug_BASE [28/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1772 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ CoreDebug_BASE [29/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1882 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ CoreDebug_BASE [30/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1957 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ CoreDebug_BASE [31/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1957 of file core_cm35p.h.

◆ CoreDebug_BASE [32/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1977 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ CoreDebug_BASE [33/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1977 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ CoreDebug_BASE [34/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 1977 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ CoreDebug_BASE [35/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 2038 of file core_armv81mml.h.

◆ CoreDebug_BASE [36/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 2052 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ CoreDebug_BASE [37/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 2052 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ CoreDebug_BASE [38/38]

| #define CoreDebug_BASE (0xE000EDF0UL) |

Core Debug Base Address

Definition at line 2052 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ DWT [1/38]

DWT configuration struct

Definition at line 1125 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ DWT [2/38]

DWT configuration struct

Definition at line 1125 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ DWT [3/38]

DWT configuration struct

Definition at line 1125 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ DWT [4/38]

DWT configuration struct

Definition at line 1125 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ DWT [5/38]

DWT configuration struct

Definition at line 1200 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm23.h.

◆ DWT [6/38]

DWT configuration struct

Definition at line 1200 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ DWT [7/38]

DWT configuration struct

Definition at line 1200 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm23.h.

◆ DWT [8/38]

DWT configuration struct

Definition at line 1200 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm23.h.

◆ DWT [9/38]

DWT configuration struct

Definition at line 1372 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_sc300.h.

◆ DWT [10/38]

DWT configuration struct

Definition at line 1377 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_sc300.h.

◆ DWT [11/38]

DWT configuration struct

Definition at line 1377 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_sc300.h.

◆ DWT [12/38]

DWT configuration struct

Definition at line 1377 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_sc300.h.

◆ DWT [13/38]

DWT configuration struct

Definition at line 1389 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm3.h.

◆ DWT [14/38]

DWT configuration struct

Definition at line 1397 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm3.h.

◆ DWT [15/38]

DWT configuration struct

Definition at line 1397 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm3.h.

◆ DWT [16/38]

DWT configuration struct

Definition at line 1397 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm3.h.

◆ DWT [17/38]

DWT configuration struct

Definition at line 1559 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ DWT [18/38]

DWT configuration struct

Definition at line 1568 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ DWT [19/38]

DWT configuration struct

Definition at line 1568 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ DWT [20/38]

DWT configuration struct

Definition at line 1568 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ DWT [21/38]

DWT configuration struct

Definition at line 1568 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ DWT [22/38]

DWT configuration struct

Definition at line 1568 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ DWT [23/38]

DWT configuration struct

Definition at line 1776 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ DWT [24/38]

DWT configuration struct

Definition at line 1776 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ DWT [25/38]

DWT configuration struct

Definition at line 1776 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ DWT [26/38]

DWT configuration struct

Definition at line 1776 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ DWT [27/38]

DWT configuration struct

Definition at line 1782 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ DWT [28/38]

DWT configuration struct

Definition at line 1782 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ DWT [29/38]

DWT configuration struct

Definition at line 1892 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ DWT [30/38]

DWT configuration struct

Definition at line 1967 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ DWT [31/38]

DWT configuration struct

Definition at line 1967 of file core_cm35p.h.

◆ DWT [32/38]

DWT configuration struct

Definition at line 1987 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ DWT [33/38]

DWT configuration struct

Definition at line 1987 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ DWT [34/38]

DWT configuration struct

Definition at line 1987 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ DWT [35/38]

DWT configuration struct

Definition at line 2048 of file core_armv81mml.h.

◆ DWT [36/38]

DWT configuration struct

Definition at line 2062 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ DWT [37/38]

DWT configuration struct

Definition at line 2062 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ DWT [38/38]

DWT configuration struct

Definition at line 2062 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ DWT_BASE [1/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1114 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ DWT_BASE [2/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1114 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ DWT_BASE [3/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1114 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ DWT_BASE [4/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1114 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mbl.h.

◆ DWT_BASE [5/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1189 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm23.h.

◆ DWT_BASE [6/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1189 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm23.h.

◆ DWT_BASE [7/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1189 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm23.h.

◆ DWT_BASE [8/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1189 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm23.h.

◆ DWT_BASE [9/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1360 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_sc300.h.

◆ DWT_BASE [10/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1365 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_sc300.h.

◆ DWT_BASE [11/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1365 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_sc300.h.

◆ DWT_BASE [12/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1365 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_sc300.h.

◆ DWT_BASE [13/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1377 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm3.h.

◆ DWT_BASE [14/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1385 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm3.h.

◆ DWT_BASE [15/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1385 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm3.h.

◆ DWT_BASE [16/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1385 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm3.h.

◆ DWT_BASE [17/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1547 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ DWT_BASE [18/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1556 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ DWT_BASE [19/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1556 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ DWT_BASE [20/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1556 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ DWT_BASE [21/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1556 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ DWT_BASE [22/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1556 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ DWT_BASE [23/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1764 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ DWT_BASE [24/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1764 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ DWT_BASE [25/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1764 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ DWT_BASE [26/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1764 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ DWT_BASE [27/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1770 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ DWT_BASE [28/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1770 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ DWT_BASE [29/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1880 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ DWT_BASE [30/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1955 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ DWT_BASE [31/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1955 of file core_cm35p.h.

◆ DWT_BASE [32/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1975 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ DWT_BASE [33/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1975 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ DWT_BASE [34/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 1975 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ DWT_BASE [35/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 2036 of file core_armv81mml.h.

◆ DWT_BASE [36/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 2050 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ DWT_BASE [37/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 2050 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ DWT_BASE [38/38]

| #define DWT_BASE (0xE0001000UL) |

DWT Base Address

Definition at line 2050 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU [1/22]

Floating Point Unit

Definition at line 1569 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU [2/22]

Floating Point Unit

Definition at line 1578 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU [3/22]

Floating Point Unit

Definition at line 1578 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU [4/22]

Floating Point Unit

Definition at line 1578 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU [5/22]

Floating Point Unit

Definition at line 1578 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU [6/22]

Floating Point Unit

Definition at line 1578 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU [7/22]

Floating Point Unit

Definition at line 1786 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU [8/22]

Floating Point Unit

Definition at line 1786 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU [9/22]

Floating Point Unit

Definition at line 1786 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU [10/22]

Floating Point Unit

Definition at line 1786 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU [11/22]

Floating Point Unit

Definition at line 1792 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU [12/22]

Floating Point Unit

Definition at line 1792 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU [13/22]

Floating Point Unit

Definition at line 1907 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU [14/22]

Floating Point Unit

Definition at line 1982 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU [15/22]

Floating Point Unit

Definition at line 1982 of file core_cm35p.h.

◆ FPU [16/22]

Floating Point Unit

Definition at line 2002 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU [17/22]

Floating Point Unit

Definition at line 2002 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU [18/22]

Floating Point Unit

Definition at line 2002 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU [19/22]

Floating Point Unit

Definition at line 2063 of file core_armv81mml.h.

◆ FPU [20/22]

Floating Point Unit

Definition at line 2077 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU [21/22]

Floating Point Unit

Definition at line 2077 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU [22/22]

Floating Point Unit

Definition at line 2077 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_BASE [1/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1568 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_BASE [2/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1577 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_BASE [3/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1577 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_BASE [4/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1577 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_BASE [5/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1577 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_BASE [6/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1577 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ FPU_BASE [7/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1785 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_BASE [8/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1785 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_BASE [9/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1785 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_BASE [10/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1785 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_BASE [11/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1791 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ FPU_BASE [12/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1791 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ FPU_BASE [13/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1906 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_BASE [14/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1981 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_BASE [15/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 1981 of file core_cm35p.h.

◆ FPU_BASE [16/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 2001 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_BASE [17/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 2001 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_BASE [18/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 2001 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ FPU_BASE [19/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 2062 of file core_armv81mml.h.

◆ FPU_BASE [20/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 2076 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_BASE [21/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 2076 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ FPU_BASE [22/22]

| #define FPU_BASE (SCS_BASE + 0x0F30UL) |

Floating Point Unit

Definition at line 2076 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ ITM [1/30]

ITM configuration struct

Definition at line 1371 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_sc300.h.

◆ ITM [2/30]

ITM configuration struct

Definition at line 1376 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_sc300.h.

◆ ITM [3/30]

ITM configuration struct

Definition at line 1376 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_sc300.h.

◆ ITM [4/30]

ITM configuration struct

Definition at line 1376 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_sc300.h.

◆ ITM [5/30]

ITM configuration struct

Definition at line 1388 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm3.h.

◆ ITM [6/30]

ITM configuration struct

Definition at line 1396 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm3.h.

◆ ITM [7/30]

ITM configuration struct

Definition at line 1396 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm3.h.

◆ ITM [8/30]

ITM configuration struct

Definition at line 1396 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm3.h.

◆ ITM [9/30]

ITM configuration struct

Definition at line 1558 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm4.h.

◆ ITM [10/30]

ITM configuration struct

Definition at line 1567 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm4.h.

◆ ITM [11/30]

ITM configuration struct

Definition at line 1567 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ ITM [12/30]

ITM configuration struct

Definition at line 1567 of file stm32f469/stm32f469i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ ITM [13/30]

ITM configuration struct

Definition at line 1567 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm4.h.

◆ ITM [14/30]

ITM configuration struct

Definition at line 1567 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm4.h.

◆ ITM [15/30]

ITM configuration struct

Definition at line 1775 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm7.h.

◆ ITM [16/30]

ITM configuration struct

Definition at line 1775 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ ITM [17/30]

ITM configuration struct

Definition at line 1775 of file stm32h747/stm32h747i-disco/CM7/Drivers/CMSIS/Include/core_cm7.h.

◆ ITM [18/30]

ITM configuration struct

Definition at line 1775 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm7.h.

◆ ITM [19/30]

ITM configuration struct

Definition at line 1781 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm7.h.

◆ ITM [20/30]

ITM configuration struct

Definition at line 1781 of file imxrt1050/imxrt1050-evkb/CMSIS/core_cm7.h.

◆ ITM [21/30]

ITM configuration struct

Definition at line 1891 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_armv8mml.h.

◆ ITM [22/30]

ITM configuration struct

Definition at line 1966 of file stm32h735/stm32h735g-dk/Drivers/CMSIS/Include/core_cm33.h.

◆ ITM [23/30]

ITM configuration struct

Definition at line 1966 of file core_cm35p.h.

◆ ITM [24/30]

ITM configuration struct

Definition at line 1986 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_armv8mml.h.

◆ ITM [25/30]

ITM configuration struct

Definition at line 1986 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ ITM [26/30]

ITM configuration struct

Definition at line 1986 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_armv8mml.h.

◆ ITM [27/30]

ITM configuration struct

Definition at line 2047 of file core_armv81mml.h.

◆ ITM [28/30]

ITM configuration struct

Definition at line 2061 of file stm32f411/stm32f411e-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ ITM [29/30]

ITM configuration struct

Definition at line 2061 of file stm32f769/stm32f769i-disco/Drivers/CMSIS/Include/core_cm33.h.

◆ ITM [30/30]

ITM configuration struct

Definition at line 2061 of file stm32f407/stm32f407g-disc1/Drivers/CMSIS/Include/core_cm33.h.

◆ ITM_BASE [1/30]