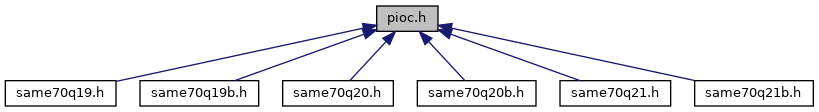

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | REG_PIOC_ABCDSR (*(__IO uint32_t*)0x400E1270U) |

| (PIOC) Peripheral Select Register More... | |

| #define | REG_PIOC_AIMDR (*(__O uint32_t*)0x400E12B4U) |

| (PIOC) Additional Interrupt Modes Disable Register More... | |

| #define | REG_PIOC_AIMER (*(__O uint32_t*)0x400E12B0U) |

| (PIOC) Additional Interrupt Modes Enable Register More... | |

| #define | REG_PIOC_AIMMR (*(__I uint32_t*)0x400E12B8U) |

| (PIOC) Additional Interrupt Modes Mask Register More... | |

| #define | REG_PIOC_CODR (*(__O uint32_t*)0x400E1234U) |

| (PIOC) Clear Output Data Register More... | |

| #define | REG_PIOC_DRIVER (*(__IO uint32_t*)0x400E1318U) |

| (PIOC) PIO I/O Drive Register More... | |

| #define | REG_PIOC_ELSR (*(__I uint32_t*)0x400E12C8U) |

| (PIOC) Edge/Level Status Register More... | |

| #define | REG_PIOC_ESR (*(__O uint32_t*)0x400E12C0U) |

| (PIOC) Edge Select Register More... | |

| #define | REG_PIOC_FELLSR (*(__O uint32_t*)0x400E12D0U) |

| (PIOC) Falling Edge/Low-Level Select Register More... | |

| #define | REG_PIOC_FRLHSR (*(__I uint32_t*)0x400E12D8U) |

| (PIOC) Fall/Rise - Low/High Status Register More... | |

| #define | REG_PIOC_IDR (*(__O uint32_t*)0x400E1244U) |

| (PIOC) Interrupt Disable Register More... | |

| #define | REG_PIOC_IER (*(__O uint32_t*)0x400E1240U) |

| (PIOC) Interrupt Enable Register More... | |

| #define | REG_PIOC_IFDR (*(__O uint32_t*)0x400E1224U) |

| (PIOC) Glitch Input Filter Disable Register More... | |

| #define | REG_PIOC_IFER (*(__O uint32_t*)0x400E1220U) |

| (PIOC) Glitch Input Filter Enable Register More... | |

| #define | REG_PIOC_IFSCDR (*(__O uint32_t*)0x400E1280U) |

| (PIOC) Input Filter Slow Clock Disable Register More... | |

| #define | REG_PIOC_IFSCER (*(__O uint32_t*)0x400E1284U) |

| (PIOC) Input Filter Slow Clock Enable Register More... | |

| #define | REG_PIOC_IFSCSR (*(__I uint32_t*)0x400E1288U) |

| (PIOC) Input Filter Slow Clock Status Register More... | |

| #define | REG_PIOC_IFSR (*(__I uint32_t*)0x400E1228U) |

| (PIOC) Glitch Input Filter Status Register More... | |

| #define | REG_PIOC_IMR (*(__I uint32_t*)0x400E1248U) |

| (PIOC) Interrupt Mask Register More... | |

| #define | REG_PIOC_ISR (*(__I uint32_t*)0x400E124CU) |

| (PIOC) Interrupt Status Register More... | |

| #define | REG_PIOC_KDR (*(__IO uint32_t*)0x400E1328U) |

| (PIOC) Keypad Controller Debouncing Register More... | |

| #define | REG_PIOC_KER (*(__IO uint32_t*)0x400E1320U) |

| (PIOC) Keypad Controller Enable Register More... | |

| #define | REG_PIOC_KIDR (*(__O uint32_t*)0x400E1334U) |

| (PIOC) Keypad Controller Interrupt Disable Register More... | |

| #define | REG_PIOC_KIER (*(__O uint32_t*)0x400E1330U) |

| (PIOC) Keypad Controller Interrupt Enable Register More... | |

| #define | REG_PIOC_KIMR (*(__I uint32_t*)0x400E1338U) |

| (PIOC) Keypad Controller Interrupt Mask Register More... | |

| #define | REG_PIOC_KKPR (*(__I uint32_t*)0x400E1340U) |

| (PIOC) Keypad Controller Key Press Register More... | |

| #define | REG_PIOC_KKRR (*(__I uint32_t*)0x400E1344U) |

| (PIOC) Keypad Controller Key Release Register More... | |

| #define | REG_PIOC_KRCR (*(__IO uint32_t*)0x400E1324U) |

| (PIOC) Keypad Controller Row Column Register More... | |

| #define | REG_PIOC_KSR (*(__I uint32_t*)0x400E133CU) |

| (PIOC) Keypad Controller Status Register More... | |

| #define | REG_PIOC_LOCKSR (*(__I uint32_t*)0x400E12E0U) |

| (PIOC) Lock Status More... | |

| #define | REG_PIOC_LSR (*(__O uint32_t*)0x400E12C4U) |

| (PIOC) Level Select Register More... | |

| #define | REG_PIOC_MDDR (*(__O uint32_t*)0x400E1254U) |

| (PIOC) Multi-driver Disable Register More... | |

| #define | REG_PIOC_MDER (*(__O uint32_t*)0x400E1250U) |

| (PIOC) Multi-driver Enable Register More... | |

| #define | REG_PIOC_MDSR (*(__I uint32_t*)0x400E1258U) |

| (PIOC) Multi-driver Status Register More... | |

| #define | REG_PIOC_ODR (*(__O uint32_t*)0x400E1214U) |

| (PIOC) Output Disable Register More... | |

| #define | REG_PIOC_ODSR (*(__IO uint32_t*)0x400E1238U) |

| (PIOC) Output Data Status Register More... | |

| #define | REG_PIOC_OER (*(__O uint32_t*)0x400E1210U) |

| (PIOC) Output Enable Register More... | |

| #define | REG_PIOC_OSR (*(__I uint32_t*)0x400E1218U) |

| (PIOC) Output Status Register More... | |

| #define | REG_PIOC_OWDR (*(__O uint32_t*)0x400E12A4U) |

| (PIOC) Output Write Disable More... | |

| #define | REG_PIOC_OWER (*(__O uint32_t*)0x400E12A0U) |

| (PIOC) Output Write Enable More... | |

| #define | REG_PIOC_OWSR (*(__I uint32_t*)0x400E12A8U) |

| (PIOC) Output Write Status Register More... | |

| #define | REG_PIOC_PCIDR (*(__O uint32_t*)0x400E1358U) |

| (PIOC) Parallel Capture Interrupt Disable Register More... | |

| #define | REG_PIOC_PCIER (*(__O uint32_t*)0x400E1354U) |

| (PIOC) Parallel Capture Interrupt Enable Register More... | |

| #define | REG_PIOC_PCIMR (*(__I uint32_t*)0x400E135CU) |

| (PIOC) Parallel Capture Interrupt Mask Register More... | |

| #define | REG_PIOC_PCISR (*(__I uint32_t*)0x400E1360U) |

| (PIOC) Parallel Capture Interrupt Status Register More... | |

| #define | REG_PIOC_PCMR (*(__IO uint32_t*)0x400E1350U) |

| (PIOC) Parallel Capture Mode Register More... | |

| #define | REG_PIOC_PCRHR (*(__I uint32_t*)0x400E1364U) |

| (PIOC) Parallel Capture Reception Holding Register More... | |

| #define | REG_PIOC_PDR (*(__O uint32_t*)0x400E1204U) |

| (PIOC) PIO Disable Register More... | |

| #define | REG_PIOC_PDSR (*(__I uint32_t*)0x400E123CU) |

| (PIOC) Pin Data Status Register More... | |

| #define | REG_PIOC_PER (*(__O uint32_t*)0x400E1200U) |

| (PIOC) PIO Enable Register More... | |

| #define | REG_PIOC_PPDDR (*(__O uint32_t*)0x400E1290U) |

| (PIOC) Pad Pull-down Disable Register More... | |

| #define | REG_PIOC_PPDER (*(__O uint32_t*)0x400E1294U) |

| (PIOC) Pad Pull-down Enable Register More... | |

| #define | REG_PIOC_PPDSR (*(__I uint32_t*)0x400E1298U) |

| (PIOC) Pad Pull-down Status Register More... | |

| #define | REG_PIOC_PSR (*(__I uint32_t*)0x400E1208U) |

| (PIOC) PIO Status Register More... | |

| #define | REG_PIOC_PUDR (*(__O uint32_t*)0x400E1260U) |

| (PIOC) Pull-up Disable Register More... | |

| #define | REG_PIOC_PUER (*(__O uint32_t*)0x400E1264U) |

| (PIOC) Pull-up Enable Register More... | |

| #define | REG_PIOC_PUSR (*(__I uint32_t*)0x400E1268U) |

| (PIOC) Pad Pull-up Status Register More... | |

| #define | REG_PIOC_REHLSR (*(__O uint32_t*)0x400E12D4U) |

| (PIOC) Rising Edge/High-Level Select Register More... | |

| #define | REG_PIOC_SCDR (*(__IO uint32_t*)0x400E128CU) |

| (PIOC) Slow Clock Divider Debouncing Register More... | |

| #define | REG_PIOC_SCHMITT (*(__IO uint32_t*)0x400E1300U) |

| (PIOC) Schmitt Trigger Register More... | |

| #define | REG_PIOC_SODR (*(__O uint32_t*)0x400E1230U) |

| (PIOC) Set Output Data Register More... | |

| #define | REG_PIOC_VERSION (*(__I uint32_t*)0x400E12FCU) |

| (PIOC) Version Register More... | |

| #define | REG_PIOC_WPMR (*(__IO uint32_t*)0x400E12E4U) |

| (PIOC) Write Protection Mode Register More... | |

| #define | REG_PIOC_WPSR (*(__I uint32_t*)0x400E12E8U) |

| (PIOC) Write Protection Status Register More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file pioc.h.

Macro Definition Documentation

◆ REG_PIOC_ABCDSR

| #define REG_PIOC_ABCDSR (*(__IO uint32_t*)0x400E1270U) |

◆ REG_PIOC_AIMDR

| #define REG_PIOC_AIMDR (*(__O uint32_t*)0x400E12B4U) |

◆ REG_PIOC_AIMER

| #define REG_PIOC_AIMER (*(__O uint32_t*)0x400E12B0U) |

◆ REG_PIOC_AIMMR

| #define REG_PIOC_AIMMR (*(__I uint32_t*)0x400E12B8U) |

◆ REG_PIOC_CODR

| #define REG_PIOC_CODR (*(__O uint32_t*)0x400E1234U) |

◆ REG_PIOC_DRIVER

| #define REG_PIOC_DRIVER (*(__IO uint32_t*)0x400E1318U) |

◆ REG_PIOC_ELSR

| #define REG_PIOC_ELSR (*(__I uint32_t*)0x400E12C8U) |

◆ REG_PIOC_ESR

| #define REG_PIOC_ESR (*(__O uint32_t*)0x400E12C0U) |

◆ REG_PIOC_FELLSR

| #define REG_PIOC_FELLSR (*(__O uint32_t*)0x400E12D0U) |

◆ REG_PIOC_FRLHSR

| #define REG_PIOC_FRLHSR (*(__I uint32_t*)0x400E12D8U) |

◆ REG_PIOC_IDR

| #define REG_PIOC_IDR (*(__O uint32_t*)0x400E1244U) |

◆ REG_PIOC_IER

| #define REG_PIOC_IER (*(__O uint32_t*)0x400E1240U) |

◆ REG_PIOC_IFDR

| #define REG_PIOC_IFDR (*(__O uint32_t*)0x400E1224U) |

◆ REG_PIOC_IFER

| #define REG_PIOC_IFER (*(__O uint32_t*)0x400E1220U) |

◆ REG_PIOC_IFSCDR

| #define REG_PIOC_IFSCDR (*(__O uint32_t*)0x400E1280U) |

◆ REG_PIOC_IFSCER

| #define REG_PIOC_IFSCER (*(__O uint32_t*)0x400E1284U) |

◆ REG_PIOC_IFSCSR

| #define REG_PIOC_IFSCSR (*(__I uint32_t*)0x400E1288U) |

◆ REG_PIOC_IFSR

| #define REG_PIOC_IFSR (*(__I uint32_t*)0x400E1228U) |

◆ REG_PIOC_IMR

| #define REG_PIOC_IMR (*(__I uint32_t*)0x400E1248U) |

◆ REG_PIOC_ISR

| #define REG_PIOC_ISR (*(__I uint32_t*)0x400E124CU) |

◆ REG_PIOC_KDR

| #define REG_PIOC_KDR (*(__IO uint32_t*)0x400E1328U) |

◆ REG_PIOC_KER

| #define REG_PIOC_KER (*(__IO uint32_t*)0x400E1320U) |

◆ REG_PIOC_KIDR

| #define REG_PIOC_KIDR (*(__O uint32_t*)0x400E1334U) |

◆ REG_PIOC_KIER

| #define REG_PIOC_KIER (*(__O uint32_t*)0x400E1330U) |

◆ REG_PIOC_KIMR

| #define REG_PIOC_KIMR (*(__I uint32_t*)0x400E1338U) |

◆ REG_PIOC_KKPR

| #define REG_PIOC_KKPR (*(__I uint32_t*)0x400E1340U) |

◆ REG_PIOC_KKRR

| #define REG_PIOC_KKRR (*(__I uint32_t*)0x400E1344U) |

◆ REG_PIOC_KRCR

| #define REG_PIOC_KRCR (*(__IO uint32_t*)0x400E1324U) |

◆ REG_PIOC_KSR

| #define REG_PIOC_KSR (*(__I uint32_t*)0x400E133CU) |

◆ REG_PIOC_LOCKSR

| #define REG_PIOC_LOCKSR (*(__I uint32_t*)0x400E12E0U) |

◆ REG_PIOC_LSR

| #define REG_PIOC_LSR (*(__O uint32_t*)0x400E12C4U) |

◆ REG_PIOC_MDDR

| #define REG_PIOC_MDDR (*(__O uint32_t*)0x400E1254U) |

◆ REG_PIOC_MDER

| #define REG_PIOC_MDER (*(__O uint32_t*)0x400E1250U) |

◆ REG_PIOC_MDSR

| #define REG_PIOC_MDSR (*(__I uint32_t*)0x400E1258U) |

◆ REG_PIOC_ODR

| #define REG_PIOC_ODR (*(__O uint32_t*)0x400E1214U) |

◆ REG_PIOC_ODSR

| #define REG_PIOC_ODSR (*(__IO uint32_t*)0x400E1238U) |

◆ REG_PIOC_OER

| #define REG_PIOC_OER (*(__O uint32_t*)0x400E1210U) |

◆ REG_PIOC_OSR

| #define REG_PIOC_OSR (*(__I uint32_t*)0x400E1218U) |

◆ REG_PIOC_OWDR

| #define REG_PIOC_OWDR (*(__O uint32_t*)0x400E12A4U) |

◆ REG_PIOC_OWER

| #define REG_PIOC_OWER (*(__O uint32_t*)0x400E12A0U) |

◆ REG_PIOC_OWSR

| #define REG_PIOC_OWSR (*(__I uint32_t*)0x400E12A8U) |

◆ REG_PIOC_PCIDR

| #define REG_PIOC_PCIDR (*(__O uint32_t*)0x400E1358U) |

◆ REG_PIOC_PCIER

| #define REG_PIOC_PCIER (*(__O uint32_t*)0x400E1354U) |

◆ REG_PIOC_PCIMR

| #define REG_PIOC_PCIMR (*(__I uint32_t*)0x400E135CU) |

◆ REG_PIOC_PCISR

| #define REG_PIOC_PCISR (*(__I uint32_t*)0x400E1360U) |

◆ REG_PIOC_PCMR

| #define REG_PIOC_PCMR (*(__IO uint32_t*)0x400E1350U) |

◆ REG_PIOC_PCRHR

| #define REG_PIOC_PCRHR (*(__I uint32_t*)0x400E1364U) |

◆ REG_PIOC_PDR

| #define REG_PIOC_PDR (*(__O uint32_t*)0x400E1204U) |

◆ REG_PIOC_PDSR

| #define REG_PIOC_PDSR (*(__I uint32_t*)0x400E123CU) |

◆ REG_PIOC_PER

| #define REG_PIOC_PER (*(__O uint32_t*)0x400E1200U) |

◆ REG_PIOC_PPDDR

| #define REG_PIOC_PPDDR (*(__O uint32_t*)0x400E1290U) |

◆ REG_PIOC_PPDER

| #define REG_PIOC_PPDER (*(__O uint32_t*)0x400E1294U) |

◆ REG_PIOC_PPDSR

| #define REG_PIOC_PPDSR (*(__I uint32_t*)0x400E1298U) |

◆ REG_PIOC_PSR

| #define REG_PIOC_PSR (*(__I uint32_t*)0x400E1208U) |

◆ REG_PIOC_PUDR

| #define REG_PIOC_PUDR (*(__O uint32_t*)0x400E1260U) |

◆ REG_PIOC_PUER

| #define REG_PIOC_PUER (*(__O uint32_t*)0x400E1264U) |

◆ REG_PIOC_PUSR

| #define REG_PIOC_PUSR (*(__I uint32_t*)0x400E1268U) |

◆ REG_PIOC_REHLSR

| #define REG_PIOC_REHLSR (*(__O uint32_t*)0x400E12D4U) |

◆ REG_PIOC_SCDR

| #define REG_PIOC_SCDR (*(__IO uint32_t*)0x400E128CU) |

◆ REG_PIOC_SCHMITT

| #define REG_PIOC_SCHMITT (*(__IO uint32_t*)0x400E1300U) |

◆ REG_PIOC_SODR

| #define REG_PIOC_SODR (*(__O uint32_t*)0x400E1230U) |

◆ REG_PIOC_VERSION

| #define REG_PIOC_VERSION (*(__I uint32_t*)0x400E12FCU) |

◆ REG_PIOC_WPMR

| #define REG_PIOC_WPMR (*(__IO uint32_t*)0x400E12E4U) |