SAMV70/SAMV71/SAME70/SAMS70-XULTRA board mpu config. More...

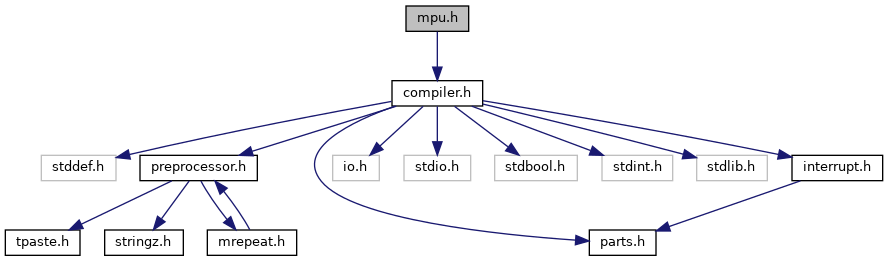

#include "compiler.h"

Include dependency graph for mpu.h:

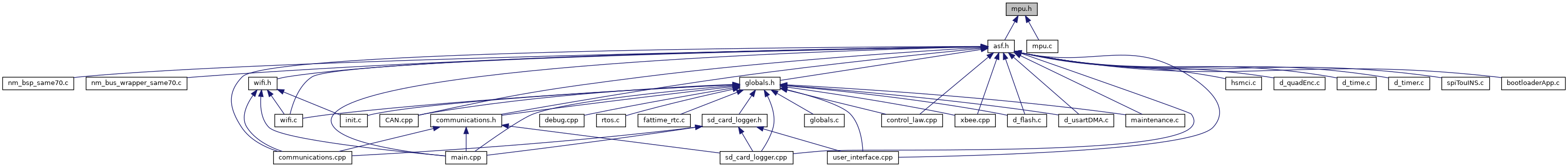

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | ARM_MODE_USR 0x10 |

| #define | DTCM_END_ADDRESS 0x203FFFFFUL |

| #define | DTCM_START_ADDRESS 0x20000000UL |

| #define | EXT_EBI_END_ADDRESS 0x6FFFFFFFUL |

| #define | EXT_EBI_START_ADDRESS 0x60000000UL |

| #define | IFLASH_END_ADDRESS 0x005FFFFFUL |

| #define | IFLASH_PRIVILEGE_END_ADDRESS (IFLASH_START_ADDRESS + 0xFFF) |

| #define | IFLASH_PRIVILEGE_START_ADDRESS (IFLASH_START_ADDRESS) |

| #define | IFLASH_START_ADDRESS 0x00400000UL |

| #define | IFLASH_UNPRIVILEGE_END_ADDRESS (IFLASH_END_ADDRESS) |

| #define | IFLASH_UNPRIVILEGE_START_ADDRESS (IFLASH_PRIVILEGE_END_ADDRESS + 1) |

| #define | INNER_NORMAL_WB_NWA_TYPE(x) (( 0x04 << MPU_RASR_TEX_Pos ) | ( ENABLE << MPU_RASR_C_Pos ) | ( ENABLE << MPU_RASR_B_Pos ) | ( x << MPU_RASR_S_Pos )) |

| #define | INNER_NORMAL_WB_RWA_TYPE(x) (( 0x04 << MPU_RASR_TEX_Pos ) | ( DISABLE << MPU_RASR_C_Pos ) | ( ENABLE << MPU_RASR_B_Pos ) | ( x << MPU_RASR_S_Pos )) |

| #define | ITCM_END_ADDRESS 0x003FFFFFUL |

| #define | ITCM_START_ADDRESS 0x00000000UL |

| #define | MPU_AP_FULL_ACCESS ( 0x03 << MPU_RASR_AP_Pos ) |

| #define | MPU_AP_NO_ACCESS ( 0x00 << MPU_RASR_AP_Pos ) |

| #define | MPU_AP_PRIVILEGED_READ_WRITE ( 0x01 << MPU_RASR_AP_Pos ) |

| #define | MPU_AP_PRIVILEGED_READONLY ( 0x05 << MPU_RASR_AP_Pos ) |

| #define | MPU_AP_READONLY ( 0x06 << MPU_RASR_AP_Pos ) |

| #define | MPU_AP_READONLY2 ( 0x07 << MPU_RASR_AP_Pos ) |

| #define | MPU_AP_RES ( 0x04 << MPU_RASR_AP_Pos ) |

| #define | MPU_AP_UNPRIVILEGED_READONLY ( 0x02 << MPU_RASR_AP_Pos ) |

| #define | MPU_DEFAULT_DTCM_REGION ( 3 ) |

| #define | MPU_DEFAULT_IFLASH_REGION ( 2 ) |

| #define | MPU_DEFAULT_ITCM_REGION ( 1 ) |

| #define | MPU_DEFAULT_SDRAM_REGION ( 8 ) |

| #define | MPU_DEFAULT_SRAM_REGION_1 ( 4 ) |

| #define | MPU_DEFAULT_SRAM_REGION_2 ( 5 ) |

| #define | MPU_ENABLE ( 0x1 << MPU_CTRL_ENABLE_Pos) |

| #define | MPU_EXT_EBI_REGION ( 7 ) |

| #define | MPU_HFNMIENA ( 0x1 << MPU_CTRL_HFNMIENA_Pos ) |

| #define | MPU_PERIPHERALS_REGION ( 6 ) |

| #define | MPU_PRIVDEFENA ( 0x1 << MPU_CTRL_PRIVDEFENA_Pos ) |

| #define | MPU_QSPIMEM_REGION ( 9 ) |

| #define | MPU_REGION_BUFFERABLE ( 0x01 << MPU_RASR_B_Pos ) |

| #define | MPU_REGION_CACHEABLE ( 0x01 << MPU_RASR_C_Pos ) |

| #define | MPU_REGION_DISABLE ( 0x0 ) |

| #define | MPU_REGION_ENABLE ( 0x01 ) |

| #define | MPU_REGION_EXECUTE_NEVER ( 0x01 << MPU_RASR_XN_Pos ) |

| #define | MPU_REGION_SHAREABLE ( 0x01 << MPU_RASR_S_Pos ) |

| #define | MPU_REGION_VALID ( 0x10 ) |

| #define | MPU_TEX_B000 ( 0x01 << MPU_RASR_TEX_Pos ) |

| #define | MPU_TEX_B001 ( 0x01 << MPU_RASR_TEX_Pos ) |

| #define | MPU_TEX_B010 ( 0x01 << MPU_RASR_TEX_Pos ) |

| #define | MPU_TEX_B011 ( 0x01 << MPU_RASR_TEX_Pos ) |

| #define | MPU_TEX_B100 ( 0x01 << MPU_RASR_TEX_Pos ) |

| #define | MPU_TEX_B101 ( 0x01 << MPU_RASR_TEX_Pos ) |

| #define | MPU_TEX_B110 ( 0x01 << MPU_RASR_TEX_Pos ) |

| #define | MPU_TEX_B111 ( 0x01 << MPU_RASR_TEX_Pos ) |

| #define | MPU_USBHSRAM_REGION ( 10 ) |

| #define | NON_SHAREABLE 0 |

| #define | PERIPHERALS_END_ADDRESS 0x5FFFFFFFUL |

| #define | PERIPHERALS_START_ADDRESS 0x40000000UL |

| #define | PRIVILEGE_MODE 0 |

| #define | QSPI_END_ADDRESS 0x9FFFFFFFUL |

| #define | QSPI_START_ADDRESS 0x80000000UL |

| #define | SDRAM_END_ADDRESS 0x7FFFFFFFUL |

| #define | SDRAM_START_ADDRESS 0x70000000UL |

| #define | SHAREABLE 1 |

| #define | SHAREABLE_DEVICE_TYPE (( 0x00 << MPU_RASR_TEX_Pos ) | ( DISABLE << MPU_RASR_C_Pos ) | ( ENABLE << MPU_RASR_B_Pos )) |

| #define | SRAM_END_ADDRESS 0x2045FFFFUL |

| #define | SRAM_FIRST_END_ADDRESS (SRAM_FIRST_START_ADDRESS + 0x3FFFF) |

| #define | SRAM_FIRST_START_ADDRESS (SRAM_START_ADDRESS) |

| #define | SRAM_SECOND_END_ADDRESS (SRAM_END_ADDRESS) |

| #define | SRAM_SECOND_START_ADDRESS (SRAM_FIRST_END_ADDRESS + 1) |

| #define | SRAM_START_ADDRESS 0x20400000UL |

| #define | STRONGLY_ORDERED_SHAREABLE_TYPE (( 0x00 << MPU_RASR_TEX_Pos ) | ( DISABLE << MPU_RASR_C_Pos ) | ( DISABLE << MPU_RASR_B_Pos )) |

| #define | USBHSRAM_END_ADDRESS 0xA01FFFFFUL |

| #define | USBHSRAM_START_ADDRESS 0xA0100000UL |

| #define | USER_MODE 1 |

Functions | |

| uint32_t | mpu_cal_mpu_region_size (uint32_t dw_actual_size_in_bytes) |

| Calculate region size for the RASR. More... | |

| void | mpu_disable_region (void) |

| Disable the current active region. More... | |

| void | mpu_enable (uint32_t dw_mpu_enable) |

| Enables the MPU module. More... | |

| void | mpu_set_region (uint32_t dw_region_base_addr, uint32_t dw_region_attr) |

| Setup a memory region. More... | |

| void | mpu_set_region_num (uint32_t dw_region_num) |

| Set active memory region. More... | |

| void | mpu_update_regions (uint32_t dw_region_num, uint32_t dw_region_base_addr, uint32_t dw_region_attr) |

| Update MPU regions. More... | |

Detailed Description

SAMV70/SAMV71/SAME70/SAMS70-XULTRA board mpu config.

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file mpu.h.

Macro Definition Documentation

◆ ARM_MODE_USR

◆ DTCM_END_ADDRESS

◆ DTCM_START_ADDRESS

◆ EXT_EBI_END_ADDRESS

◆ EXT_EBI_START_ADDRESS

◆ IFLASH_END_ADDRESS

◆ IFLASH_PRIVILEGE_END_ADDRESS

| #define IFLASH_PRIVILEGE_END_ADDRESS (IFLASH_START_ADDRESS + 0xFFF) |

◆ IFLASH_PRIVILEGE_START_ADDRESS

| #define IFLASH_PRIVILEGE_START_ADDRESS (IFLASH_START_ADDRESS) |

◆ IFLASH_START_ADDRESS

◆ IFLASH_UNPRIVILEGE_END_ADDRESS

| #define IFLASH_UNPRIVILEGE_END_ADDRESS (IFLASH_END_ADDRESS) |

◆ IFLASH_UNPRIVILEGE_START_ADDRESS

| #define IFLASH_UNPRIVILEGE_START_ADDRESS (IFLASH_PRIVILEGE_END_ADDRESS + 1) |

◆ INNER_NORMAL_WB_NWA_TYPE

| #define INNER_NORMAL_WB_NWA_TYPE | ( | x | ) | (( 0x04 << MPU_RASR_TEX_Pos ) | ( ENABLE << MPU_RASR_C_Pos ) | ( ENABLE << MPU_RASR_B_Pos ) | ( x << MPU_RASR_S_Pos )) |

◆ INNER_NORMAL_WB_RWA_TYPE

| #define INNER_NORMAL_WB_RWA_TYPE | ( | x | ) | (( 0x04 << MPU_RASR_TEX_Pos ) | ( DISABLE << MPU_RASR_C_Pos ) | ( ENABLE << MPU_RASR_B_Pos ) | ( x << MPU_RASR_S_Pos )) |

◆ ITCM_END_ADDRESS

◆ ITCM_START_ADDRESS

◆ MPU_AP_FULL_ACCESS

◆ MPU_AP_NO_ACCESS

◆ MPU_AP_PRIVILEGED_READ_WRITE

| #define MPU_AP_PRIVILEGED_READ_WRITE ( 0x01 << MPU_RASR_AP_Pos ) |

◆ MPU_AP_PRIVILEGED_READONLY

◆ MPU_AP_READONLY

◆ MPU_AP_READONLY2

◆ MPU_AP_RES

◆ MPU_AP_UNPRIVILEGED_READONLY

| #define MPU_AP_UNPRIVILEGED_READONLY ( 0x02 << MPU_RASR_AP_Pos ) |

◆ MPU_DEFAULT_DTCM_REGION

◆ MPU_DEFAULT_IFLASH_REGION

◆ MPU_DEFAULT_ITCM_REGION

◆ MPU_DEFAULT_SDRAM_REGION

◆ MPU_DEFAULT_SRAM_REGION_1

◆ MPU_DEFAULT_SRAM_REGION_2

◆ MPU_ENABLE

◆ MPU_EXT_EBI_REGION

◆ MPU_HFNMIENA

◆ MPU_PERIPHERALS_REGION

◆ MPU_PRIVDEFENA

◆ MPU_QSPIMEM_REGION

◆ MPU_REGION_BUFFERABLE

◆ MPU_REGION_CACHEABLE

◆ MPU_REGION_DISABLE

◆ MPU_REGION_ENABLE

◆ MPU_REGION_EXECUTE_NEVER

◆ MPU_REGION_SHAREABLE

◆ MPU_REGION_VALID

◆ MPU_TEX_B000

◆ MPU_TEX_B001

◆ MPU_TEX_B010

◆ MPU_TEX_B011

◆ MPU_TEX_B100

◆ MPU_TEX_B101

◆ MPU_TEX_B110

◆ MPU_TEX_B111

◆ MPU_USBHSRAM_REGION

◆ NON_SHAREABLE

◆ PERIPHERALS_END_ADDRESS

◆ PERIPHERALS_START_ADDRESS

◆ PRIVILEGE_MODE

◆ QSPI_END_ADDRESS

◆ QSPI_START_ADDRESS

◆ SDRAM_END_ADDRESS

◆ SDRAM_START_ADDRESS

◆ SHAREABLE

◆ SHAREABLE_DEVICE_TYPE

| #define SHAREABLE_DEVICE_TYPE (( 0x00 << MPU_RASR_TEX_Pos ) | ( DISABLE << MPU_RASR_C_Pos ) | ( ENABLE << MPU_RASR_B_Pos )) |

◆ SRAM_END_ADDRESS

◆ SRAM_FIRST_END_ADDRESS

| #define SRAM_FIRST_END_ADDRESS (SRAM_FIRST_START_ADDRESS + 0x3FFFF) |

◆ SRAM_FIRST_START_ADDRESS

| #define SRAM_FIRST_START_ADDRESS (SRAM_START_ADDRESS) |

◆ SRAM_SECOND_END_ADDRESS

| #define SRAM_SECOND_END_ADDRESS (SRAM_END_ADDRESS) |

◆ SRAM_SECOND_START_ADDRESS

| #define SRAM_SECOND_START_ADDRESS (SRAM_FIRST_END_ADDRESS + 1) |

◆ SRAM_START_ADDRESS

◆ STRONGLY_ORDERED_SHAREABLE_TYPE

| #define STRONGLY_ORDERED_SHAREABLE_TYPE (( 0x00 << MPU_RASR_TEX_Pos ) | ( DISABLE << MPU_RASR_C_Pos ) | ( DISABLE << MPU_RASR_B_Pos )) |