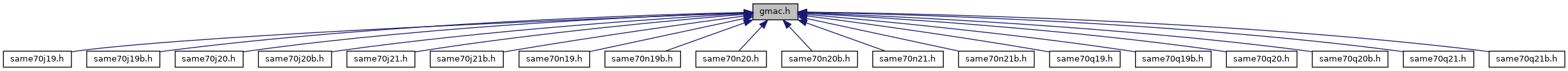

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Gmac |

| struct | GmacSa |

| GmacSa hardware registers. More... | |

Macros | |

| #define | GMAC_AE_AER_Msk (0x3ffu << GMAC_AE_AER_Pos) |

| (GMAC_AE) Alignment Errors More... | |

| #define | GMAC_AE_AER_Pos 0 |

| #define | GMAC_BCFR_BFRX_Msk (0xffffffffu << GMAC_BCFR_BFRX_Pos) |

| (GMAC_BCFR) Broadcast Frames Received without Error More... | |

| #define | GMAC_BCFR_BFRX_Pos 0 |

| #define | GMAC_BCFT_BFTX_Msk (0xffffffffu << GMAC_BCFT_BFTX_Pos) |

| (GMAC_BCFT) Broadcast Frames Transmitted without Error More... | |

| #define | GMAC_BCFT_BFTX_Pos 0 |

| #define | GMAC_BFR64_NFRX_Msk (0xffffffffu << GMAC_BFR64_NFRX_Pos) |

| (GMAC_BFR64) 64 Byte Frames Received without Error More... | |

| #define | GMAC_BFR64_NFRX_Pos 0 |

| #define | GMAC_BFT64_NFTX_Msk (0xffffffffu << GMAC_BFT64_NFTX_Pos) |

| (GMAC_BFT64) 64 Byte Frames Transmitted without Error More... | |

| #define | GMAC_BFT64_NFTX_Pos 0 |

| #define | GMAC_CBSCR_QAE (0x1u << 1) |

| (GMAC_CBSCR) Queue A CBS Enable More... | |

| #define | GMAC_CBSCR_QBE (0x1u << 0) |

| (GMAC_CBSCR) Queue B CBS Enable More... | |

| #define | GMAC_CBSISQA_IS(value) ((GMAC_CBSISQA_IS_Msk & ((value) << GMAC_CBSISQA_IS_Pos))) |

| #define | GMAC_CBSISQA_IS_Msk (0xffffffffu << GMAC_CBSISQA_IS_Pos) |

| (GMAC_CBSISQA) IdleSlope More... | |

| #define | GMAC_CBSISQA_IS_Pos 0 |

| #define | GMAC_CBSISQB_IS(value) ((GMAC_CBSISQB_IS_Msk & ((value) << GMAC_CBSISQB_IS_Pos))) |

| #define | GMAC_CBSISQB_IS_Msk (0xffffffffu << GMAC_CBSISQB_IS_Pos) |

| (GMAC_CBSISQB) IdleSlope More... | |

| #define | GMAC_CBSISQB_IS_Pos 0 |

| #define | GMAC_CSE_CSR_Msk (0x3ffu << GMAC_CSE_CSR_Pos) |

| (GMAC_CSE) Carrier Sense Error More... | |

| #define | GMAC_CSE_CSR_Pos 0 |

| #define | GMAC_DCFGR_DDRP (0x1u << 24) |

| (GMAC_DCFGR) DMA Discard Receive Packets More... | |

| #define | GMAC_DCFGR_DRBS(value) ((GMAC_DCFGR_DRBS_Msk & ((value) << GMAC_DCFGR_DRBS_Pos))) |

| #define | GMAC_DCFGR_DRBS_Msk (0xffu << GMAC_DCFGR_DRBS_Pos) |

| (GMAC_DCFGR) DMA Receive Buffer Size More... | |

| #define | GMAC_DCFGR_DRBS_Pos 16 |

| #define | GMAC_DCFGR_ESMA (0x1u << 6) |

| (GMAC_DCFGR) Endian Swap Mode Enable for Management Descriptor Accesses More... | |

| #define | GMAC_DCFGR_ESPA (0x1u << 7) |

| (GMAC_DCFGR) Endian Swap Mode Enable for Packet Data Accesses More... | |

| #define | GMAC_DCFGR_FBLDO(value) ((GMAC_DCFGR_FBLDO_Msk & ((value) << GMAC_DCFGR_FBLDO_Pos))) |

| #define | GMAC_DCFGR_FBLDO_INCR16 (0x10u << 0) |

| (GMAC_DCFGR) 1xxxx: Attempt to use INCR16 AHB bursts More... | |

| #define | GMAC_DCFGR_FBLDO_INCR4 (0x4u << 0) |

| (GMAC_DCFGR) 001xx: Attempt to use INCR4 AHB bursts (Default) More... | |

| #define | GMAC_DCFGR_FBLDO_INCR8 (0x8u << 0) |

| (GMAC_DCFGR) 01xxx: Attempt to use INCR8 AHB bursts More... | |

| #define | GMAC_DCFGR_FBLDO_Msk (0x1fu << GMAC_DCFGR_FBLDO_Pos) |

| (GMAC_DCFGR) Fixed Burst Length for DMA Data Operations: More... | |

| #define | GMAC_DCFGR_FBLDO_Pos 0 |

| #define | GMAC_DCFGR_FBLDO_SINGLE (0x1u << 0) |

| (GMAC_DCFGR) 00001: Always use SINGLE AHB bursts More... | |

| #define | GMAC_DCFGR_RXBMS(value) ((GMAC_DCFGR_RXBMS_Msk & ((value) << GMAC_DCFGR_RXBMS_Pos))) |

| #define | GMAC_DCFGR_RXBMS_EIGHTH (0x0u << 8) |

| (GMAC_DCFGR) 4/8 Kbyte Memory Size More... | |

| #define | GMAC_DCFGR_RXBMS_FULL (0x3u << 8) |

| (GMAC_DCFGR) 4 Kbytes Memory Size More... | |

| #define | GMAC_DCFGR_RXBMS_HALF (0x2u << 8) |

| (GMAC_DCFGR) 4/2 Kbytes Memory Size More... | |

| #define | GMAC_DCFGR_RXBMS_Msk (0x3u << GMAC_DCFGR_RXBMS_Pos) |

| (GMAC_DCFGR) Receiver Packet Buffer Memory Size Select More... | |

| #define | GMAC_DCFGR_RXBMS_Pos 8 |

| #define | GMAC_DCFGR_RXBMS_QUARTER (0x1u << 8) |

| (GMAC_DCFGR) 4/4 Kbytes Memory Size More... | |

| #define | GMAC_DCFGR_TXCOEN (0x1u << 11) |

| (GMAC_DCFGR) Transmitter Checksum Generation Offload Enable More... | |

| #define | GMAC_DCFGR_TXPBMS (0x1u << 10) |

| (GMAC_DCFGR) Transmitter Packet Buffer Memory Size Select More... | |

| #define | GMAC_DTF_DEFT_Msk (0x3ffffu << GMAC_DTF_DEFT_Pos) |

| (GMAC_DTF) Deferred Transmission More... | |

| #define | GMAC_DTF_DEFT_Pos 0 |

| #define | GMAC_EC_XCOL_Msk (0x3ffu << GMAC_EC_XCOL_Pos) |

| (GMAC_EC) Excessive Collisions More... | |

| #define | GMAC_EC_XCOL_Pos 0 |

| #define | GMAC_EFRN_RUD_Msk (0x3fffffffu << GMAC_EFRN_RUD_Pos) |

| (GMAC_EFRN) Register Update More... | |

| #define | GMAC_EFRN_RUD_Pos 0 |

| #define | GMAC_EFRSH_RUD_Msk (0xffffu << GMAC_EFRSH_RUD_Pos) |

| (GMAC_EFRSH) Register Update More... | |

| #define | GMAC_EFRSH_RUD_Pos 0 |

| #define | GMAC_EFRSL_RUD_Msk (0xffffffffu << GMAC_EFRSL_RUD_Pos) |

| (GMAC_EFRSL) Register Update More... | |

| #define | GMAC_EFRSL_RUD_Pos 0 |

| #define | GMAC_EFTN_RUD_Msk (0x3fffffffu << GMAC_EFTN_RUD_Pos) |

| (GMAC_EFTN) Register Update More... | |

| #define | GMAC_EFTN_RUD_Pos 0 |

| #define | GMAC_EFTSH_RUD_Msk (0xffffu << GMAC_EFTSH_RUD_Pos) |

| (GMAC_EFTSH) Register Update More... | |

| #define | GMAC_EFTSH_RUD_Pos 0 |

| #define | GMAC_EFTSL_RUD_Msk (0xffffffffu << GMAC_EFTSL_RUD_Pos) |

| (GMAC_EFTSL) Register Update More... | |

| #define | GMAC_EFTSL_RUD_Pos 0 |

| #define | GMAC_FCSE_FCKR_Msk (0x3ffu << GMAC_FCSE_FCKR_Pos) |

| (GMAC_FCSE) Frame Check Sequence Errors More... | |

| #define | GMAC_FCSE_FCKR_Pos 0 |

| #define | GMAC_FR_FRX_Msk (0xffffffffu << GMAC_FR_FRX_Pos) |

| (GMAC_FR) Frames Received without Error More... | |

| #define | GMAC_FR_FRX_Pos 0 |

| #define | GMAC_FT_FTX_Msk (0xffffffffu << GMAC_FT_FTX_Pos) |

| (GMAC_FT) Frames Transmitted without Error More... | |

| #define | GMAC_FT_FTX_Pos 0 |

| #define | GMAC_GTBFT1518_NFTX_Msk (0xffffffffu << GMAC_GTBFT1518_NFTX_Pos) |

| (GMAC_GTBFT1518) Greater than 1518 Byte Frames Transmitted without Error More... | |

| #define | GMAC_GTBFT1518_NFTX_Pos 0 |

| #define | GMAC_HRB_ADDR(value) ((GMAC_HRB_ADDR_Msk & ((value) << GMAC_HRB_ADDR_Pos))) |

| #define | GMAC_HRB_ADDR_Msk (0xffffffffu << GMAC_HRB_ADDR_Pos) |

| (GMAC_HRB) Hash Address More... | |

| #define | GMAC_HRB_ADDR_Pos 0 |

| #define | GMAC_HRT_ADDR(value) ((GMAC_HRT_ADDR_Msk & ((value) << GMAC_HRT_ADDR_Pos))) |

| #define | GMAC_HRT_ADDR_Msk (0xffffffffu << GMAC_HRT_ADDR_Pos) |

| (GMAC_HRT) Hash Address More... | |

| #define | GMAC_HRT_ADDR_Pos 0 |

| #define | GMAC_IDR_DRQFR (0x1u << 18) |

| (GMAC_IDR) PTP Delay Request Frame Received More... | |

| #define | GMAC_IDR_DRQFT (0x1u << 20) |

| (GMAC_IDR) PTP Delay Request Frame Transmitted More... | |

| #define | GMAC_IDR_EXINT (0x1u << 15) |

| (GMAC_IDR) External Interrupt More... | |

| #define | GMAC_IDR_HRESP (0x1u << 11) |

| (GMAC_IDR) HRESP Not OK More... | |

| #define | GMAC_IDR_MFS (0x1u << 0) |

| (GMAC_IDR) Management Frame Sent More... | |

| #define | GMAC_IDR_PDRQFR (0x1u << 22) |

| (GMAC_IDR) PDelay Request Frame Received More... | |

| #define | GMAC_IDR_PDRQFT (0x1u << 24) |

| (GMAC_IDR) PDelay Request Frame Transmitted More... | |

| #define | GMAC_IDR_PDRSFR (0x1u << 23) |

| (GMAC_IDR) PDelay Response Frame Received More... | |

| #define | GMAC_IDR_PDRSFT (0x1u << 25) |

| (GMAC_IDR) PDelay Response Frame Transmitted More... | |

| #define | GMAC_IDR_PFNZ (0x1u << 12) |

| (GMAC_IDR) Pause Frame with Non-zero Pause Quantum Received More... | |

| #define | GMAC_IDR_PFTR (0x1u << 14) |

| (GMAC_IDR) Pause Frame Transmitted More... | |

| #define | GMAC_IDR_PTZ (0x1u << 13) |

| (GMAC_IDR) Pause Time Zero More... | |

| #define | GMAC_IDR_RCOMP (0x1u << 1) |

| (GMAC_IDR) Receive Complete More... | |

| #define | GMAC_IDR_RLEX (0x1u << 5) |

| (GMAC_IDR) Retry Limit Exceeded or Late Collision More... | |

| #define | GMAC_IDR_ROVR (0x1u << 10) |

| (GMAC_IDR) Receive Overrun More... | |

| #define | GMAC_IDR_RXUBR (0x1u << 2) |

| (GMAC_IDR) RX Used Bit Read More... | |

| #define | GMAC_IDR_SFR (0x1u << 19) |

| (GMAC_IDR) PTP Sync Frame Received More... | |

| #define | GMAC_IDR_SFT (0x1u << 21) |

| (GMAC_IDR) PTP Sync Frame Transmitted More... | |

| #define | GMAC_IDR_SRI (0x1u << 26) |

| (GMAC_IDR) TSU Seconds Register Increment More... | |

| #define | GMAC_IDR_TCOMP (0x1u << 7) |

| (GMAC_IDR) Transmit Complete More... | |

| #define | GMAC_IDR_TFC (0x1u << 6) |

| (GMAC_IDR) Transmit Frame Corruption Due to AHB Error More... | |

| #define | GMAC_IDR_TUR (0x1u << 4) |

| (GMAC_IDR) Transmit Underrun More... | |

| #define | GMAC_IDR_TXUBR (0x1u << 3) |

| (GMAC_IDR) TX Used Bit Read More... | |

| #define | GMAC_IDR_WOL (0x1u << 28) |

| (GMAC_IDR) Wake On LAN More... | |

| #define | GMAC_IDRPQ_HRESP (0x1u << 11) |

| (GMAC_IDRPQ[5]) HRESP Not OK More... | |

| #define | GMAC_IDRPQ_RCOMP (0x1u << 1) |

| (GMAC_IDRPQ[5]) Receive Complete More... | |

| #define | GMAC_IDRPQ_RLEX (0x1u << 5) |

| (GMAC_IDRPQ[5]) Retry Limit Exceeded or Late Collision More... | |

| #define | GMAC_IDRPQ_ROVR (0x1u << 10) |

| (GMAC_IDRPQ[5]) Receive Overrun More... | |

| #define | GMAC_IDRPQ_RXUBR (0x1u << 2) |

| (GMAC_IDRPQ[5]) RX Used Bit Read More... | |

| #define | GMAC_IDRPQ_TCOMP (0x1u << 7) |

| (GMAC_IDRPQ[5]) Transmit Complete More... | |

| #define | GMAC_IDRPQ_TFC (0x1u << 6) |

| (GMAC_IDRPQ[5]) Transmit Frame Corruption Due to AHB Error More... | |

| #define | GMAC_IER_DRQFR (0x1u << 18) |

| (GMAC_IER) PTP Delay Request Frame Received More... | |

| #define | GMAC_IER_DRQFT (0x1u << 20) |

| (GMAC_IER) PTP Delay Request Frame Transmitted More... | |

| #define | GMAC_IER_EXINT (0x1u << 15) |

| (GMAC_IER) External Interrupt More... | |

| #define | GMAC_IER_HRESP (0x1u << 11) |

| (GMAC_IER) HRESP Not OK More... | |

| #define | GMAC_IER_MFS (0x1u << 0) |

| (GMAC_IER) Management Frame Sent More... | |

| #define | GMAC_IER_PDRQFR (0x1u << 22) |

| (GMAC_IER) PDelay Request Frame Received More... | |

| #define | GMAC_IER_PDRQFT (0x1u << 24) |

| (GMAC_IER) PDelay Request Frame Transmitted More... | |

| #define | GMAC_IER_PDRSFR (0x1u << 23) |

| (GMAC_IER) PDelay Response Frame Received More... | |

| #define | GMAC_IER_PDRSFT (0x1u << 25) |

| (GMAC_IER) PDelay Response Frame Transmitted More... | |

| #define | GMAC_IER_PFNZ (0x1u << 12) |

| (GMAC_IER) Pause Frame with Non-zero Pause Quantum Received More... | |

| #define | GMAC_IER_PFTR (0x1u << 14) |

| (GMAC_IER) Pause Frame Transmitted More... | |

| #define | GMAC_IER_PTZ (0x1u << 13) |

| (GMAC_IER) Pause Time Zero More... | |

| #define | GMAC_IER_RCOMP (0x1u << 1) |

| (GMAC_IER) Receive Complete More... | |

| #define | GMAC_IER_RLEX (0x1u << 5) |

| (GMAC_IER) Retry Limit Exceeded or Late Collision More... | |

| #define | GMAC_IER_ROVR (0x1u << 10) |

| (GMAC_IER) Receive Overrun More... | |

| #define | GMAC_IER_RXUBR (0x1u << 2) |

| (GMAC_IER) RX Used Bit Read More... | |

| #define | GMAC_IER_SFR (0x1u << 19) |

| (GMAC_IER) PTP Sync Frame Received More... | |

| #define | GMAC_IER_SFT (0x1u << 21) |

| (GMAC_IER) PTP Sync Frame Transmitted More... | |

| #define | GMAC_IER_SRI (0x1u << 26) |

| (GMAC_IER) TSU Seconds Register Increment More... | |

| #define | GMAC_IER_TCOMP (0x1u << 7) |

| (GMAC_IER) Transmit Complete More... | |

| #define | GMAC_IER_TFC (0x1u << 6) |

| (GMAC_IER) Transmit Frame Corruption Due to AHB Error More... | |

| #define | GMAC_IER_TUR (0x1u << 4) |

| (GMAC_IER) Transmit Underrun More... | |

| #define | GMAC_IER_TXUBR (0x1u << 3) |

| (GMAC_IER) TX Used Bit Read More... | |

| #define | GMAC_IER_WOL (0x1u << 28) |

| (GMAC_IER) Wake On LAN More... | |

| #define | GMAC_IERPQ_HRESP (0x1u << 11) |

| (GMAC_IERPQ[5]) HRESP Not OK More... | |

| #define | GMAC_IERPQ_RCOMP (0x1u << 1) |

| (GMAC_IERPQ[5]) Receive Complete More... | |

| #define | GMAC_IERPQ_RLEX (0x1u << 5) |

| (GMAC_IERPQ[5]) Retry Limit Exceeded or Late Collision More... | |

| #define | GMAC_IERPQ_ROVR (0x1u << 10) |

| (GMAC_IERPQ[5]) Receive Overrun More... | |

| #define | GMAC_IERPQ_RXUBR (0x1u << 2) |

| (GMAC_IERPQ[5]) RX Used Bit Read More... | |

| #define | GMAC_IERPQ_TCOMP (0x1u << 7) |

| (GMAC_IERPQ[5]) Transmit Complete More... | |

| #define | GMAC_IERPQ_TFC (0x1u << 6) |

| (GMAC_IERPQ[5]) Transmit Frame Corruption Due to AHB Error More... | |

| #define | GMAC_IHCE_HCKER_Msk (0xffu << GMAC_IHCE_HCKER_Pos) |

| (GMAC_IHCE) IP Header Checksum Errors More... | |

| #define | GMAC_IHCE_HCKER_Pos 0 |

| #define | GMAC_IMR_DRQFR (0x1u << 18) |

| (GMAC_IMR) PTP Delay Request Frame Received More... | |

| #define | GMAC_IMR_DRQFT (0x1u << 20) |

| (GMAC_IMR) PTP Delay Request Frame Transmitted More... | |

| #define | GMAC_IMR_EXINT (0x1u << 15) |

| (GMAC_IMR) External Interrupt More... | |

| #define | GMAC_IMR_HRESP (0x1u << 11) |

| (GMAC_IMR) HRESP Not OK More... | |

| #define | GMAC_IMR_MFS (0x1u << 0) |

| (GMAC_IMR) Management Frame Sent More... | |

| #define | GMAC_IMR_PDRQFR (0x1u << 22) |

| (GMAC_IMR) PDelay Request Frame Received More... | |

| #define | GMAC_IMR_PDRQFT (0x1u << 24) |

| (GMAC_IMR) PDelay Request Frame Transmitted More... | |

| #define | GMAC_IMR_PDRSFR (0x1u << 23) |

| (GMAC_IMR) PDelay Response Frame Received More... | |

| #define | GMAC_IMR_PDRSFT (0x1u << 25) |

| (GMAC_IMR) PDelay Response Frame Transmitted More... | |

| #define | GMAC_IMR_PFNZ (0x1u << 12) |

| (GMAC_IMR) Pause Frame with Non-zero Pause Quantum Received More... | |

| #define | GMAC_IMR_PFTR (0x1u << 14) |

| (GMAC_IMR) Pause Frame Transmitted More... | |

| #define | GMAC_IMR_PTZ (0x1u << 13) |

| (GMAC_IMR) Pause Time Zero More... | |

| #define | GMAC_IMR_RCOMP (0x1u << 1) |

| (GMAC_IMR) Receive Complete More... | |

| #define | GMAC_IMR_RLEX (0x1u << 5) |

| (GMAC_IMR) Retry Limit Exceeded More... | |

| #define | GMAC_IMR_ROVR (0x1u << 10) |

| (GMAC_IMR) Receive Overrun More... | |

| #define | GMAC_IMR_RXUBR (0x1u << 2) |

| (GMAC_IMR) RX Used Bit Read More... | |

| #define | GMAC_IMR_SFR (0x1u << 19) |

| (GMAC_IMR) PTP Sync Frame Received More... | |

| #define | GMAC_IMR_SFT (0x1u << 21) |

| (GMAC_IMR) PTP Sync Frame Transmitted More... | |

| #define | GMAC_IMR_SRI (0x1u << 26) |

| (GMAC_IMR) TSU Seconds Register Increment More... | |

| #define | GMAC_IMR_TCOMP (0x1u << 7) |

| (GMAC_IMR) Transmit Complete More... | |

| #define | GMAC_IMR_TFC (0x1u << 6) |

| (GMAC_IMR) Transmit Frame Corruption Due to AHB Error More... | |

| #define | GMAC_IMR_TUR (0x1u << 4) |

| (GMAC_IMR) Transmit Underrun More... | |

| #define | GMAC_IMR_TXUBR (0x1u << 3) |

| (GMAC_IMR) TX Used Bit Read More... | |

| #define | GMAC_IMR_WOL (0x1u << 28) |

| (GMAC_IMR) Wake On LAN More... | |

| #define | GMAC_IMRPQ_AHB (0x1u << 6) |

| (GMAC_IMRPQ[5]) AHB Error More... | |

| #define | GMAC_IMRPQ_HRESP (0x1u << 11) |

| (GMAC_IMRPQ[5]) HRESP Not OK More... | |

| #define | GMAC_IMRPQ_RCOMP (0x1u << 1) |

| (GMAC_IMRPQ[5]) Receive Complete More... | |

| #define | GMAC_IMRPQ_RLEX (0x1u << 5) |

| (GMAC_IMRPQ[5]) Retry Limit Exceeded or Late Collision More... | |

| #define | GMAC_IMRPQ_ROVR (0x1u << 10) |

| (GMAC_IMRPQ[5]) Receive Overrun More... | |

| #define | GMAC_IMRPQ_RXUBR (0x1u << 2) |

| (GMAC_IMRPQ[5]) RX Used Bit Read More... | |

| #define | GMAC_IMRPQ_TCOMP (0x1u << 7) |

| (GMAC_IMRPQ[5]) Transmit Complete More... | |

| #define | GMAC_IPGS_FL(value) ((GMAC_IPGS_FL_Msk & ((value) << GMAC_IPGS_FL_Pos))) |

| #define | GMAC_IPGS_FL_Msk (0xffffu << GMAC_IPGS_FL_Pos) |

| (GMAC_IPGS) Frame Length More... | |

| #define | GMAC_IPGS_FL_Pos 0 |

| #define | GMAC_ISR_DRQFR (0x1u << 18) |

| (GMAC_ISR) PTP Delay Request Frame Received More... | |

| #define | GMAC_ISR_DRQFT (0x1u << 20) |

| (GMAC_ISR) PTP Delay Request Frame Transmitted More... | |

| #define | GMAC_ISR_HRESP (0x1u << 11) |

| (GMAC_ISR) HRESP Not OK More... | |

| #define | GMAC_ISR_MFS (0x1u << 0) |

| (GMAC_ISR) Management Frame Sent More... | |

| #define | GMAC_ISR_PDRQFR (0x1u << 22) |

| (GMAC_ISR) PDelay Request Frame Received More... | |

| #define | GMAC_ISR_PDRQFT (0x1u << 24) |

| (GMAC_ISR) PDelay Request Frame Transmitted More... | |

| #define | GMAC_ISR_PDRSFR (0x1u << 23) |

| (GMAC_ISR) PDelay Response Frame Received More... | |

| #define | GMAC_ISR_PDRSFT (0x1u << 25) |

| (GMAC_ISR) PDelay Response Frame Transmitted More... | |

| #define | GMAC_ISR_PFNZ (0x1u << 12) |

| (GMAC_ISR) Pause Frame with Non-zero Pause Quantum Received More... | |

| #define | GMAC_ISR_PFTR (0x1u << 14) |

| (GMAC_ISR) Pause Frame Transmitted More... | |

| #define | GMAC_ISR_PTZ (0x1u << 13) |

| (GMAC_ISR) Pause Time Zero More... | |

| #define | GMAC_ISR_RCOMP (0x1u << 1) |

| (GMAC_ISR) Receive Complete More... | |

| #define | GMAC_ISR_RLEX (0x1u << 5) |

| (GMAC_ISR) Retry Limit Exceeded More... | |

| #define | GMAC_ISR_ROVR (0x1u << 10) |

| (GMAC_ISR) Receive Overrun More... | |

| #define | GMAC_ISR_RXUBR (0x1u << 2) |

| (GMAC_ISR) RX Used Bit Read More... | |

| #define | GMAC_ISR_SFR (0x1u << 19) |

| (GMAC_ISR) PTP Sync Frame Received More... | |

| #define | GMAC_ISR_SFT (0x1u << 21) |

| (GMAC_ISR) PTP Sync Frame Transmitted More... | |

| #define | GMAC_ISR_SRI (0x1u << 26) |

| (GMAC_ISR) TSU Seconds Register Increment More... | |

| #define | GMAC_ISR_TCOMP (0x1u << 7) |

| (GMAC_ISR) Transmit Complete More... | |

| #define | GMAC_ISR_TFC (0x1u << 6) |

| (GMAC_ISR) Transmit Frame Corruption Due to AHB Error More... | |

| #define | GMAC_ISR_TUR (0x1u << 4) |

| (GMAC_ISR) Transmit Underrun More... | |

| #define | GMAC_ISR_TXUBR (0x1u << 3) |

| (GMAC_ISR) TX Used Bit Read More... | |

| #define | GMAC_ISR_WOL (0x1u << 28) |

| (GMAC_ISR) Wake On LAN More... | |

| #define | GMAC_ISRPQ_HRESP (0x1u << 11) |

| (GMAC_ISRPQ[5]) HRESP Not OK More... | |

| #define | GMAC_ISRPQ_RCOMP (0x1u << 1) |

| (GMAC_ISRPQ[5]) Receive Complete More... | |

| #define | GMAC_ISRPQ_RLEX (0x1u << 5) |

| (GMAC_ISRPQ[5]) Retry Limit Exceeded or Late Collision More... | |

| #define | GMAC_ISRPQ_ROVR (0x1u << 10) |

| (GMAC_ISRPQ[5]) Receive Overrun More... | |

| #define | GMAC_ISRPQ_RXUBR (0x1u << 2) |

| (GMAC_ISRPQ[5]) RX Used Bit Read More... | |

| #define | GMAC_ISRPQ_TCOMP (0x1u << 7) |

| (GMAC_ISRPQ[5]) Transmit Complete More... | |

| #define | GMAC_ISRPQ_TFC (0x1u << 6) |

| (GMAC_ISRPQ[5]) Transmit Frame Corruption Due to AHB Error More... | |

| #define | GMAC_JR_JRX_Msk (0x3ffu << GMAC_JR_JRX_Pos) |

| (GMAC_JR) Jabbers Received More... | |

| #define | GMAC_JR_JRX_Pos 0 |

| #define | GMAC_LC_LCOL_Msk (0x3ffu << GMAC_LC_LCOL_Pos) |

| (GMAC_LC) Late Collisions More... | |

| #define | GMAC_LC_LCOL_Pos 0 |

| #define | GMAC_LFFE_LFER_Msk (0x3ffu << GMAC_LFFE_LFER_Pos) |

| (GMAC_LFFE) Length Field Frame Errors More... | |

| #define | GMAC_LFFE_LFER_Pos 0 |

| #define | GMAC_MAN_CLTTO (0x1u << 30) |

| (GMAC_MAN) Clause 22 Operation More... | |

| #define | GMAC_MAN_DATA(value) ((GMAC_MAN_DATA_Msk & ((value) << GMAC_MAN_DATA_Pos))) |

| #define | GMAC_MAN_DATA_Msk (0xffffu << GMAC_MAN_DATA_Pos) |

| (GMAC_MAN) PHY Data More... | |

| #define | GMAC_MAN_DATA_Pos 0 |

| #define | GMAC_MAN_OP(value) ((GMAC_MAN_OP_Msk & ((value) << GMAC_MAN_OP_Pos))) |

| #define | GMAC_MAN_OP_Msk (0x3u << GMAC_MAN_OP_Pos) |

| (GMAC_MAN) Operation More... | |

| #define | GMAC_MAN_OP_Pos 28 |

| #define | GMAC_MAN_PHYA(value) ((GMAC_MAN_PHYA_Msk & ((value) << GMAC_MAN_PHYA_Pos))) |

| #define | GMAC_MAN_PHYA_Msk (0x1fu << GMAC_MAN_PHYA_Pos) |

| (GMAC_MAN) PHY Address More... | |

| #define | GMAC_MAN_PHYA_Pos 23 |

| #define | GMAC_MAN_REGA(value) ((GMAC_MAN_REGA_Msk & ((value) << GMAC_MAN_REGA_Pos))) |

| #define | GMAC_MAN_REGA_Msk (0x1fu << GMAC_MAN_REGA_Pos) |

| (GMAC_MAN) Register Address More... | |

| #define | GMAC_MAN_REGA_Pos 18 |

| #define | GMAC_MAN_WTN(value) ((GMAC_MAN_WTN_Msk & ((value) << GMAC_MAN_WTN_Pos))) |

| #define | GMAC_MAN_WTN_Msk (0x3u << GMAC_MAN_WTN_Pos) |

| (GMAC_MAN) Write Ten More... | |

| #define | GMAC_MAN_WTN_Pos 16 |

| #define | GMAC_MAN_WZO (0x1u << 31) |

| (GMAC_MAN) Write ZERO More... | |

| #define | GMAC_MCF_MCOL_Msk (0x3ffffu << GMAC_MCF_MCOL_Pos) |

| (GMAC_MCF) Multiple Collision More... | |

| #define | GMAC_MCF_MCOL_Pos 0 |

| #define | GMAC_MFR_MFRX_Msk (0xffffffffu << GMAC_MFR_MFRX_Pos) |

| (GMAC_MFR) Multicast Frames Received without Error More... | |

| #define | GMAC_MFR_MFRX_Pos 0 |

| #define | GMAC_MFT_MFTX_Msk (0xffffffffu << GMAC_MFT_MFTX_Pos) |

| (GMAC_MFT) Multicast Frames Transmitted without Error More... | |

| #define | GMAC_MFT_MFTX_Pos 0 |

| #define | GMAC_MID_MID_Msk (0xffffu << GMAC_MID_MID_Pos) |

| (GMAC_MID) Module Identification Number More... | |

| #define | GMAC_MID_MID_Pos 16 |

| #define | GMAC_MID_MREV_Msk (0xffffu << GMAC_MID_MREV_Pos) |

| (GMAC_MID) Module Revision More... | |

| #define | GMAC_MID_MREV_Pos 0 |

| #define | GMAC_NCFGR_CAF (0x1u << 4) |

| (GMAC_NCFGR) Copy All Frames More... | |

| #define | GMAC_NCFGR_CLK(value) ((GMAC_NCFGR_CLK_Msk & ((value) << GMAC_NCFGR_CLK_Pos))) |

| #define | GMAC_NCFGR_CLK_MCK_16 (0x1u << 18) |

| (GMAC_NCFGR) MCK divided by 16 (MCK up to 40 MHz) More... | |

| #define | GMAC_NCFGR_CLK_MCK_32 (0x2u << 18) |

| (GMAC_NCFGR) MCK divided by 32 (MCK up to 80 MHz) More... | |

| #define | GMAC_NCFGR_CLK_MCK_48 (0x3u << 18) |

| (GMAC_NCFGR) MCK divided by 48 (MCK up to 120 MHz) More... | |

| #define | GMAC_NCFGR_CLK_MCK_64 (0x4u << 18) |

| (GMAC_NCFGR) MCK divided by 64 (MCK up to 160 MHz) More... | |

| #define | GMAC_NCFGR_CLK_MCK_8 (0x0u << 18) |

| (GMAC_NCFGR) MCK divided by 8 (MCK up to 20 MHz) More... | |

| #define | GMAC_NCFGR_CLK_MCK_96 (0x5u << 18) |

| (GMAC_NCFGR) MCK divided by 96 (MCK up to 240 MHz) More... | |

| #define | GMAC_NCFGR_CLK_Msk (0x7u << GMAC_NCFGR_CLK_Pos) |

| (GMAC_NCFGR) MDC CLock Division More... | |

| #define | GMAC_NCFGR_CLK_Pos 18 |

| #define | GMAC_NCFGR_DBW(value) ((GMAC_NCFGR_DBW_Msk & ((value) << GMAC_NCFGR_DBW_Pos))) |

| #define | GMAC_NCFGR_DBW_Msk (0x3u << GMAC_NCFGR_DBW_Pos) |

| (GMAC_NCFGR) Data Bus Width More... | |

| #define | GMAC_NCFGR_DBW_Pos 21 |

| #define | GMAC_NCFGR_DCPF (0x1u << 23) |

| (GMAC_NCFGR) Disable Copy of Pause Frames More... | |

| #define | GMAC_NCFGR_DNVLAN (0x1u << 2) |

| (GMAC_NCFGR) Discard Non-VLAN FRAMES More... | |

| #define | GMAC_NCFGR_EFRHD (0x1u << 25) |

| (GMAC_NCFGR) Enable Frames Received in Half Duplex More... | |

| #define | GMAC_NCFGR_FD (0x1u << 1) |

| (GMAC_NCFGR) Full Duplex More... | |

| #define | GMAC_NCFGR_IPGSEN (0x1u << 28) |

| (GMAC_NCFGR) IP Stretch Enable More... | |

| #define | GMAC_NCFGR_IRXER (0x1u << 30) |

| (GMAC_NCFGR) Ignore IPG GRXER More... | |

| #define | GMAC_NCFGR_IRXFCS (0x1u << 26) |

| (GMAC_NCFGR) Ignore RX FCS More... | |

| #define | GMAC_NCFGR_JFRAME (0x1u << 3) |

| (GMAC_NCFGR) Jumbo Frame Size More... | |

| #define | GMAC_NCFGR_LFERD (0x1u << 16) |

| (GMAC_NCFGR) Length Field Error Frame Discard More... | |

| #define | GMAC_NCFGR_MAXFS (0x1u << 8) |

| (GMAC_NCFGR) 1536 Maximum Frame Size More... | |

| #define | GMAC_NCFGR_MTIHEN (0x1u << 6) |

| (GMAC_NCFGR) Multicast Hash Enable More... | |

| #define | GMAC_NCFGR_NBC (0x1u << 5) |

| (GMAC_NCFGR) No Broadcast More... | |

| #define | GMAC_NCFGR_PEN (0x1u << 13) |

| (GMAC_NCFGR) Pause Enable More... | |

| #define | GMAC_NCFGR_RFCS (0x1u << 17) |

| (GMAC_NCFGR) Remove FCS More... | |

| #define | GMAC_NCFGR_RTY (0x1u << 12) |

| (GMAC_NCFGR) Retry Test More... | |

| #define | GMAC_NCFGR_RXBP (0x1u << 29) |

| (GMAC_NCFGR) Receive Bad Preamble More... | |

| #define | GMAC_NCFGR_RXBUFO(value) ((GMAC_NCFGR_RXBUFO_Msk & ((value) << GMAC_NCFGR_RXBUFO_Pos))) |

| #define | GMAC_NCFGR_RXBUFO_Msk (0x3u << GMAC_NCFGR_RXBUFO_Pos) |

| (GMAC_NCFGR) Receive Buffer Offset More... | |

| #define | GMAC_NCFGR_RXBUFO_Pos 14 |

| #define | GMAC_NCFGR_RXCOEN (0x1u << 24) |

| (GMAC_NCFGR) Receive Checksum Offload Enable More... | |

| #define | GMAC_NCFGR_SPD (0x1u << 0) |

| (GMAC_NCFGR) Speed More... | |

| #define | GMAC_NCFGR_UNIHEN (0x1u << 7) |

| (GMAC_NCFGR) Unicast Hash Enable More... | |

| #define | GMAC_NCR_BP (0x1u << 8) |

| (GMAC_NCR) Back pressure More... | |

| #define | GMAC_NCR_CLRSTAT (0x1u << 5) |

| (GMAC_NCR) Clear Statistics Registers More... | |

| #define | GMAC_NCR_ENPBPR (0x1u << 16) |

| (GMAC_NCR) Enable PFC Priority-based Pause Reception More... | |

| #define | GMAC_NCR_FNP (0x1u << 18) |

| (GMAC_NCR) Flush Next Packet More... | |

| #define | GMAC_NCR_INCSTAT (0x1u << 6) |

| (GMAC_NCR) Increment Statistics Registers More... | |

| #define | GMAC_NCR_LBL (0x1u << 1) |

| (GMAC_NCR) Loop Back Local More... | |

| #define | GMAC_NCR_MPE (0x1u << 4) |

| (GMAC_NCR) Management Port Enable More... | |

| #define | GMAC_NCR_RXEN (0x1u << 2) |

| (GMAC_NCR) Receive Enable More... | |

| #define | GMAC_NCR_SRTSM (0x1u << 15) |

| (GMAC_NCR) Store Receive Time Stamp to Memory More... | |

| #define | GMAC_NCR_THALT (0x1u << 10) |

| (GMAC_NCR) Transmit Halt More... | |

| #define | GMAC_NCR_TSTART (0x1u << 9) |

| (GMAC_NCR) Start Transmission More... | |

| #define | GMAC_NCR_TXEN (0x1u << 3) |

| (GMAC_NCR) Transmit Enable More... | |

| #define | GMAC_NCR_TXPBPF (0x1u << 17) |

| (GMAC_NCR) Transmit PFC Priority-based Pause Frame More... | |

| #define | GMAC_NCR_TXPF (0x1u << 11) |

| (GMAC_NCR) Transmit Pause Frame More... | |

| #define | GMAC_NCR_TXZQPF (0x1u << 12) |

| (GMAC_NCR) Transmit Zero Quantum Pause Frame More... | |

| #define | GMAC_NCR_WESTAT (0x1u << 7) |

| (GMAC_NCR) Write Enable for Statistics Registers More... | |

| #define | GMAC_NSC_NANOSEC(value) ((GMAC_NSC_NANOSEC_Msk & ((value) << GMAC_NSC_NANOSEC_Pos))) |

| #define | GMAC_NSC_NANOSEC_Msk (0x3fffffu << GMAC_NSC_NANOSEC_Pos) |

| (GMAC_NSC) 1588 Timer Nanosecond Comparison Value More... | |

| #define | GMAC_NSC_NANOSEC_Pos 0 |

| #define | GMAC_NSR_IDLE (0x1u << 2) |

| (GMAC_NSR) PHY Management Logic Idle More... | |

| #define | GMAC_NSR_MDIO (0x1u << 1) |

| (GMAC_NSR) MDIO Input Status More... | |

| #define | GMAC_OFR_OFRX_Msk (0x3ffu << GMAC_OFR_OFRX_Pos) |

| (GMAC_OFR) Oversized Frames Received More... | |

| #define | GMAC_OFR_OFRX_Pos 0 |

| #define | GMAC_ORHI_RXO_Msk (0xffffu << GMAC_ORHI_RXO_Pos) |

| (GMAC_ORHI) Received Octets More... | |

| #define | GMAC_ORHI_RXO_Pos 0 |

| #define | GMAC_ORLO_RXO_Msk (0xffffffffu << GMAC_ORLO_RXO_Pos) |

| (GMAC_ORLO) Received Octets More... | |

| #define | GMAC_ORLO_RXO_Pos 0 |

| #define | GMAC_OTHI_TXO_Msk (0xffffu << GMAC_OTHI_TXO_Pos) |

| (GMAC_OTHI) Transmitted Octets More... | |

| #define | GMAC_OTHI_TXO_Pos 0 |

| #define | GMAC_OTLO_TXO_Msk (0xffffffffu << GMAC_OTLO_TXO_Pos) |

| (GMAC_OTLO) Transmitted Octets More... | |

| #define | GMAC_OTLO_TXO_Pos 0 |

| #define | GMAC_PEFRN_RUD_Msk (0x3fffffffu << GMAC_PEFRN_RUD_Pos) |

| (GMAC_PEFRN) Register Update More... | |

| #define | GMAC_PEFRN_RUD_Pos 0 |

| #define | GMAC_PEFRSH_RUD_Msk (0xffffu << GMAC_PEFRSH_RUD_Pos) |

| (GMAC_PEFRSH) Register Update More... | |

| #define | GMAC_PEFRSH_RUD_Pos 0 |

| #define | GMAC_PEFRSL_RUD_Msk (0xffffffffu << GMAC_PEFRSL_RUD_Pos) |

| (GMAC_PEFRSL) Register Update More... | |

| #define | GMAC_PEFRSL_RUD_Pos 0 |

| #define | GMAC_PEFTN_RUD_Msk (0x3fffffffu << GMAC_PEFTN_RUD_Pos) |

| (GMAC_PEFTN) Register Update More... | |

| #define | GMAC_PEFTN_RUD_Pos 0 |

| #define | GMAC_PEFTSH_RUD_Msk (0xffffu << GMAC_PEFTSH_RUD_Pos) |

| (GMAC_PEFTSH) Register Update More... | |

| #define | GMAC_PEFTSH_RUD_Pos 0 |

| #define | GMAC_PEFTSL_RUD_Msk (0xffffffffu << GMAC_PEFTSL_RUD_Pos) |

| (GMAC_PEFTSL) Register Update More... | |

| #define | GMAC_PEFTSL_RUD_Pos 0 |

| #define | GMAC_PFR_PFRX_Msk (0xffffu << GMAC_PFR_PFRX_Pos) |

| (GMAC_PFR) Pause Frames Received Register More... | |

| #define | GMAC_PFR_PFRX_Pos 0 |

| #define | GMAC_PFT_PFTX_Msk (0xffffu << GMAC_PFT_PFTX_Pos) |

| (GMAC_PFT) Pause Frames Transmitted Register More... | |

| #define | GMAC_PFT_PFTX_Pos 0 |

| #define | GMAC_RBQB_ADDR(value) ((GMAC_RBQB_ADDR_Msk & ((value) << GMAC_RBQB_ADDR_Pos))) |

| #define | GMAC_RBQB_ADDR_Msk (0x3fffffffu << GMAC_RBQB_ADDR_Pos) |

| (GMAC_RBQB) Receive Buffer Queue Base Address More... | |

| #define | GMAC_RBQB_ADDR_Pos 2 |

| #define | GMAC_RBQBAPQ_RXBQBA(value) ((GMAC_RBQBAPQ_RXBQBA_Msk & ((value) << GMAC_RBQBAPQ_RXBQBA_Pos))) |

| #define | GMAC_RBQBAPQ_RXBQBA_Msk (0x3fffffffu << GMAC_RBQBAPQ_RXBQBA_Pos) |

| (GMAC_RBQBAPQ[5]) Receive Buffer Queue Base Address More... | |

| #define | GMAC_RBQBAPQ_RXBQBA_Pos 2 |

| #define | GMAC_RBSRPQ_RBS(value) ((GMAC_RBSRPQ_RBS_Msk & ((value) << GMAC_RBSRPQ_RBS_Pos))) |

| #define | GMAC_RBSRPQ_RBS_Msk (0xffffu << GMAC_RBSRPQ_RBS_Pos) |

| (GMAC_RBSRPQ[5]) Receive Buffer Size More... | |

| #define | GMAC_RBSRPQ_RBS_Pos 0 |

| #define | GMAC_RJFML_FML(value) ((GMAC_RJFML_FML_Msk & ((value) << GMAC_RJFML_FML_Pos))) |

| #define | GMAC_RJFML_FML_Msk (0x3fffu << GMAC_RJFML_FML_Pos) |

| (GMAC_RJFML) Frame Max Length More... | |

| #define | GMAC_RJFML_FML_Pos 0 |

| #define | GMAC_ROE_RXOVR_Msk (0x3ffu << GMAC_ROE_RXOVR_Pos) |

| (GMAC_ROE) Receive Overruns More... | |

| #define | GMAC_ROE_RXOVR_Pos 0 |

| #define | GMAC_RPQ_RPQ_Msk (0xffffu << GMAC_RPQ_RPQ_Pos) |

| (GMAC_RPQ) Received Pause Quantum More... | |

| #define | GMAC_RPQ_RPQ_Pos 0 |

| #define | GMAC_RPSF_ENRXP (0x1u << 31) |

| (GMAC_RPSF) Enable RX Partial Store and Forward Operation More... | |

| #define | GMAC_RPSF_RPB1ADR(value) ((GMAC_RPSF_RPB1ADR_Msk & ((value) << GMAC_RPSF_RPB1ADR_Pos))) |

| #define | GMAC_RPSF_RPB1ADR_Msk (0xfffu << GMAC_RPSF_RPB1ADR_Pos) |

| (GMAC_RPSF) Receive Partial Store and Forward Address More... | |

| #define | GMAC_RPSF_RPB1ADR_Pos 0 |

| #define | GMAC_RRE_RXRER_Msk (0x3ffffu << GMAC_RRE_RXRER_Pos) |

| (GMAC_RRE) Receive Resource Errors More... | |

| #define | GMAC_RRE_RXRER_Pos 0 |

| #define | GMAC_RSE_RXSE_Msk (0x3ffu << GMAC_RSE_RXSE_Pos) |

| (GMAC_RSE) Receive Symbol Errors More... | |

| #define | GMAC_RSE_RXSE_Pos 0 |

| #define | GMAC_RSR_BNA (0x1u << 0) |

| (GMAC_RSR) Buffer Not Available More... | |

| #define | GMAC_RSR_HNO (0x1u << 3) |

| (GMAC_RSR) HRESP Not OK More... | |

| #define | GMAC_RSR_REC (0x1u << 1) |

| (GMAC_RSR) Frame Received More... | |

| #define | GMAC_RSR_RXOVR (0x1u << 2) |

| (GMAC_RSR) Receive Overrun More... | |

| #define | GMAC_RXLPI_COUNT_Msk (0xffffu << GMAC_RXLPI_COUNT_Pos) |

| (GMAC_RXLPI) Count of RX LPI transitions (cleared on read) More... | |

| #define | GMAC_RXLPI_COUNT_Pos 0 |

| #define | GMAC_RXLPITIME_LPITIME_Msk (0xffffffu << GMAC_RXLPITIME_LPITIME_Pos) |

| (GMAC_RXLPITIME) Time in LPI (cleared on read) More... | |

| #define | GMAC_RXLPITIME_LPITIME_Pos 0 |

| #define | GMAC_SAB_ADDR(value) ((GMAC_SAB_ADDR_Msk & ((value) << GMAC_SAB_ADDR_Pos))) |

| #define | GMAC_SAB_ADDR_Msk (0xffffffffu << GMAC_SAB_ADDR_Pos) |

| (GMAC_SAB) Specific Address 1 More... | |

| #define | GMAC_SAB_ADDR_Pos 0 |

| #define | GMAC_SAMB1_ADDR(value) ((GMAC_SAMB1_ADDR_Msk & ((value) << GMAC_SAMB1_ADDR_Pos))) |

| #define | GMAC_SAMB1_ADDR_Msk (0xffffffffu << GMAC_SAMB1_ADDR_Pos) |

| (GMAC_SAMB1) Specific Address 1 Mask More... | |

| #define | GMAC_SAMB1_ADDR_Pos 0 |

| #define | GMAC_SAMT1_ADDR(value) ((GMAC_SAMT1_ADDR_Msk & ((value) << GMAC_SAMT1_ADDR_Pos))) |

| #define | GMAC_SAMT1_ADDR_Msk (0xffffu << GMAC_SAMT1_ADDR_Pos) |

| (GMAC_SAMT1) Specific Address 1 Mask More... | |

| #define | GMAC_SAMT1_ADDR_Pos 0 |

| #define | GMAC_SAT_ADDR(value) ((GMAC_SAT_ADDR_Msk & ((value) << GMAC_SAT_ADDR_Pos))) |

| #define | GMAC_SAT_ADDR_Msk (0xffffu << GMAC_SAT_ADDR_Pos) |

| (GMAC_SAT) Specific Address 1 More... | |

| #define | GMAC_SAT_ADDR_Pos 0 |

| #define | GMAC_SCF_SCOL_Msk (0x3ffffu << GMAC_SCF_SCOL_Pos) |

| (GMAC_SCF) Single Collision More... | |

| #define | GMAC_SCF_SCOL_Pos 0 |

| #define | GMAC_SCH_SEC(value) ((GMAC_SCH_SEC_Msk & ((value) << GMAC_SCH_SEC_Pos))) |

| #define | GMAC_SCH_SEC_Msk (0xffffu << GMAC_SCH_SEC_Pos) |

| (GMAC_SCH) 1588 Timer Second Comparison Value More... | |

| #define | GMAC_SCH_SEC_Pos 0 |

| #define | GMAC_SCL_SEC(value) ((GMAC_SCL_SEC_Msk & ((value) << GMAC_SCL_SEC_Pos))) |

| #define | GMAC_SCL_SEC_Msk (0xffffffffu << GMAC_SCL_SEC_Pos) |

| (GMAC_SCL) 1588 Timer Second Comparison Value More... | |

| #define | GMAC_SCL_SEC_Pos 0 |

| #define | GMAC_ST1RPQ_DSTCE (0x1u << 28) |

| (GMAC_ST1RPQ[4]) Differentiated Services or Traffic Class Match Enable More... | |

| #define | GMAC_ST1RPQ_DSTCM(value) ((GMAC_ST1RPQ_DSTCM_Msk & ((value) << GMAC_ST1RPQ_DSTCM_Pos))) |

| #define | GMAC_ST1RPQ_DSTCM_Msk (0xffu << GMAC_ST1RPQ_DSTCM_Pos) |

| (GMAC_ST1RPQ[4]) Differentiated Services or Traffic Class Match More... | |

| #define | GMAC_ST1RPQ_DSTCM_Pos 4 |

| #define | GMAC_ST1RPQ_QNB(value) ((GMAC_ST1RPQ_QNB_Msk & ((value) << GMAC_ST1RPQ_QNB_Pos))) |

| #define | GMAC_ST1RPQ_QNB_Msk (0x7u << GMAC_ST1RPQ_QNB_Pos) |

| (GMAC_ST1RPQ[4]) Queue Number (0-5) More... | |

| #define | GMAC_ST1RPQ_QNB_Pos 0 |

| #define | GMAC_ST1RPQ_UDPE (0x1u << 29) |

| (GMAC_ST1RPQ[4]) UDP Port Match Enable More... | |

| #define | GMAC_ST1RPQ_UDPM(value) ((GMAC_ST1RPQ_UDPM_Msk & ((value) << GMAC_ST1RPQ_UDPM_Pos))) |

| #define | GMAC_ST1RPQ_UDPM_Msk (0xffffu << GMAC_ST1RPQ_UDPM_Pos) |

| (GMAC_ST1RPQ[4]) UDP Port Match More... | |

| #define | GMAC_ST1RPQ_UDPM_Pos 12 |

| #define | GMAC_ST2CW00_COMPVAL(value) ((GMAC_ST2CW00_COMPVAL_Msk & ((value) << GMAC_ST2CW00_COMPVAL_Pos))) |

| #define | GMAC_ST2CW00_COMPVAL_Msk (0xffffu << GMAC_ST2CW00_COMPVAL_Pos) |

| (GMAC_ST2CW00) Compare Value More... | |

| #define | GMAC_ST2CW00_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW00_MASKVAL(value) ((GMAC_ST2CW00_MASKVAL_Msk & ((value) << GMAC_ST2CW00_MASKVAL_Pos))) |

| #define | GMAC_ST2CW00_MASKVAL_Msk (0xffffu << GMAC_ST2CW00_MASKVAL_Pos) |

| (GMAC_ST2CW00) Mask Value More... | |

| #define | GMAC_ST2CW00_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW010_COMPVAL(value) ((GMAC_ST2CW010_COMPVAL_Msk & ((value) << GMAC_ST2CW010_COMPVAL_Pos))) |

| #define | GMAC_ST2CW010_COMPVAL_Msk (0xffffu << GMAC_ST2CW010_COMPVAL_Pos) |

| (GMAC_ST2CW010) Compare Value More... | |

| #define | GMAC_ST2CW010_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW010_MASKVAL(value) ((GMAC_ST2CW010_MASKVAL_Msk & ((value) << GMAC_ST2CW010_MASKVAL_Pos))) |

| #define | GMAC_ST2CW010_MASKVAL_Msk (0xffffu << GMAC_ST2CW010_MASKVAL_Pos) |

| (GMAC_ST2CW010) Mask Value More... | |

| #define | GMAC_ST2CW010_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW011_COMPVAL(value) ((GMAC_ST2CW011_COMPVAL_Msk & ((value) << GMAC_ST2CW011_COMPVAL_Pos))) |

| #define | GMAC_ST2CW011_COMPVAL_Msk (0xffffu << GMAC_ST2CW011_COMPVAL_Pos) |

| (GMAC_ST2CW011) Compare Value More... | |

| #define | GMAC_ST2CW011_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW011_MASKVAL(value) ((GMAC_ST2CW011_MASKVAL_Msk & ((value) << GMAC_ST2CW011_MASKVAL_Pos))) |

| #define | GMAC_ST2CW011_MASKVAL_Msk (0xffffu << GMAC_ST2CW011_MASKVAL_Pos) |

| (GMAC_ST2CW011) Mask Value More... | |

| #define | GMAC_ST2CW011_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW012_COMPVAL(value) ((GMAC_ST2CW012_COMPVAL_Msk & ((value) << GMAC_ST2CW012_COMPVAL_Pos))) |

| #define | GMAC_ST2CW012_COMPVAL_Msk (0xffffu << GMAC_ST2CW012_COMPVAL_Pos) |

| (GMAC_ST2CW012) Compare Value More... | |

| #define | GMAC_ST2CW012_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW012_MASKVAL(value) ((GMAC_ST2CW012_MASKVAL_Msk & ((value) << GMAC_ST2CW012_MASKVAL_Pos))) |

| #define | GMAC_ST2CW012_MASKVAL_Msk (0xffffu << GMAC_ST2CW012_MASKVAL_Pos) |

| (GMAC_ST2CW012) Mask Value More... | |

| #define | GMAC_ST2CW012_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW013_COMPVAL(value) ((GMAC_ST2CW013_COMPVAL_Msk & ((value) << GMAC_ST2CW013_COMPVAL_Pos))) |

| #define | GMAC_ST2CW013_COMPVAL_Msk (0xffffu << GMAC_ST2CW013_COMPVAL_Pos) |

| (GMAC_ST2CW013) Compare Value More... | |

| #define | GMAC_ST2CW013_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW013_MASKVAL(value) ((GMAC_ST2CW013_MASKVAL_Msk & ((value) << GMAC_ST2CW013_MASKVAL_Pos))) |

| #define | GMAC_ST2CW013_MASKVAL_Msk (0xffffu << GMAC_ST2CW013_MASKVAL_Pos) |

| (GMAC_ST2CW013) Mask Value More... | |

| #define | GMAC_ST2CW013_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW014_COMPVAL(value) ((GMAC_ST2CW014_COMPVAL_Msk & ((value) << GMAC_ST2CW014_COMPVAL_Pos))) |

| #define | GMAC_ST2CW014_COMPVAL_Msk (0xffffu << GMAC_ST2CW014_COMPVAL_Pos) |

| (GMAC_ST2CW014) Compare Value More... | |

| #define | GMAC_ST2CW014_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW014_MASKVAL(value) ((GMAC_ST2CW014_MASKVAL_Msk & ((value) << GMAC_ST2CW014_MASKVAL_Pos))) |

| #define | GMAC_ST2CW014_MASKVAL_Msk (0xffffu << GMAC_ST2CW014_MASKVAL_Pos) |

| (GMAC_ST2CW014) Mask Value More... | |

| #define | GMAC_ST2CW014_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW015_COMPVAL(value) ((GMAC_ST2CW015_COMPVAL_Msk & ((value) << GMAC_ST2CW015_COMPVAL_Pos))) |

| #define | GMAC_ST2CW015_COMPVAL_Msk (0xffffu << GMAC_ST2CW015_COMPVAL_Pos) |

| (GMAC_ST2CW015) Compare Value More... | |

| #define | GMAC_ST2CW015_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW015_MASKVAL(value) ((GMAC_ST2CW015_MASKVAL_Msk & ((value) << GMAC_ST2CW015_MASKVAL_Pos))) |

| #define | GMAC_ST2CW015_MASKVAL_Msk (0xffffu << GMAC_ST2CW015_MASKVAL_Pos) |

| (GMAC_ST2CW015) Mask Value More... | |

| #define | GMAC_ST2CW015_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW016_COMPVAL(value) ((GMAC_ST2CW016_COMPVAL_Msk & ((value) << GMAC_ST2CW016_COMPVAL_Pos))) |

| #define | GMAC_ST2CW016_COMPVAL_Msk (0xffffu << GMAC_ST2CW016_COMPVAL_Pos) |

| (GMAC_ST2CW016) Compare Value More... | |

| #define | GMAC_ST2CW016_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW016_MASKVAL(value) ((GMAC_ST2CW016_MASKVAL_Msk & ((value) << GMAC_ST2CW016_MASKVAL_Pos))) |

| #define | GMAC_ST2CW016_MASKVAL_Msk (0xffffu << GMAC_ST2CW016_MASKVAL_Pos) |

| (GMAC_ST2CW016) Mask Value More... | |

| #define | GMAC_ST2CW016_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW017_COMPVAL(value) ((GMAC_ST2CW017_COMPVAL_Msk & ((value) << GMAC_ST2CW017_COMPVAL_Pos))) |

| #define | GMAC_ST2CW017_COMPVAL_Msk (0xffffu << GMAC_ST2CW017_COMPVAL_Pos) |

| (GMAC_ST2CW017) Compare Value More... | |

| #define | GMAC_ST2CW017_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW017_MASKVAL(value) ((GMAC_ST2CW017_MASKVAL_Msk & ((value) << GMAC_ST2CW017_MASKVAL_Pos))) |

| #define | GMAC_ST2CW017_MASKVAL_Msk (0xffffu << GMAC_ST2CW017_MASKVAL_Pos) |

| (GMAC_ST2CW017) Mask Value More... | |

| #define | GMAC_ST2CW017_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW018_COMPVAL(value) ((GMAC_ST2CW018_COMPVAL_Msk & ((value) << GMAC_ST2CW018_COMPVAL_Pos))) |

| #define | GMAC_ST2CW018_COMPVAL_Msk (0xffffu << GMAC_ST2CW018_COMPVAL_Pos) |

| (GMAC_ST2CW018) Compare Value More... | |

| #define | GMAC_ST2CW018_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW018_MASKVAL(value) ((GMAC_ST2CW018_MASKVAL_Msk & ((value) << GMAC_ST2CW018_MASKVAL_Pos))) |

| #define | GMAC_ST2CW018_MASKVAL_Msk (0xffffu << GMAC_ST2CW018_MASKVAL_Pos) |

| (GMAC_ST2CW018) Mask Value More... | |

| #define | GMAC_ST2CW018_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW019_COMPVAL(value) ((GMAC_ST2CW019_COMPVAL_Msk & ((value) << GMAC_ST2CW019_COMPVAL_Pos))) |

| #define | GMAC_ST2CW019_COMPVAL_Msk (0xffffu << GMAC_ST2CW019_COMPVAL_Pos) |

| (GMAC_ST2CW019) Compare Value More... | |

| #define | GMAC_ST2CW019_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW019_MASKVAL(value) ((GMAC_ST2CW019_MASKVAL_Msk & ((value) << GMAC_ST2CW019_MASKVAL_Pos))) |

| #define | GMAC_ST2CW019_MASKVAL_Msk (0xffffu << GMAC_ST2CW019_MASKVAL_Pos) |

| (GMAC_ST2CW019) Mask Value More... | |

| #define | GMAC_ST2CW019_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW01_COMPVAL(value) ((GMAC_ST2CW01_COMPVAL_Msk & ((value) << GMAC_ST2CW01_COMPVAL_Pos))) |

| #define | GMAC_ST2CW01_COMPVAL_Msk (0xffffu << GMAC_ST2CW01_COMPVAL_Pos) |

| (GMAC_ST2CW01) Compare Value More... | |

| #define | GMAC_ST2CW01_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW01_MASKVAL(value) ((GMAC_ST2CW01_MASKVAL_Msk & ((value) << GMAC_ST2CW01_MASKVAL_Pos))) |

| #define | GMAC_ST2CW01_MASKVAL_Msk (0xffffu << GMAC_ST2CW01_MASKVAL_Pos) |

| (GMAC_ST2CW01) Mask Value More... | |

| #define | GMAC_ST2CW01_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW020_COMPVAL(value) ((GMAC_ST2CW020_COMPVAL_Msk & ((value) << GMAC_ST2CW020_COMPVAL_Pos))) |

| #define | GMAC_ST2CW020_COMPVAL_Msk (0xffffu << GMAC_ST2CW020_COMPVAL_Pos) |

| (GMAC_ST2CW020) Compare Value More... | |

| #define | GMAC_ST2CW020_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW020_MASKVAL(value) ((GMAC_ST2CW020_MASKVAL_Msk & ((value) << GMAC_ST2CW020_MASKVAL_Pos))) |

| #define | GMAC_ST2CW020_MASKVAL_Msk (0xffffu << GMAC_ST2CW020_MASKVAL_Pos) |

| (GMAC_ST2CW020) Mask Value More... | |

| #define | GMAC_ST2CW020_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW021_COMPVAL(value) ((GMAC_ST2CW021_COMPVAL_Msk & ((value) << GMAC_ST2CW021_COMPVAL_Pos))) |

| #define | GMAC_ST2CW021_COMPVAL_Msk (0xffffu << GMAC_ST2CW021_COMPVAL_Pos) |

| (GMAC_ST2CW021) Compare Value More... | |

| #define | GMAC_ST2CW021_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW021_MASKVAL(value) ((GMAC_ST2CW021_MASKVAL_Msk & ((value) << GMAC_ST2CW021_MASKVAL_Pos))) |

| #define | GMAC_ST2CW021_MASKVAL_Msk (0xffffu << GMAC_ST2CW021_MASKVAL_Pos) |

| (GMAC_ST2CW021) Mask Value More... | |

| #define | GMAC_ST2CW021_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW022_COMPVAL(value) ((GMAC_ST2CW022_COMPVAL_Msk & ((value) << GMAC_ST2CW022_COMPVAL_Pos))) |

| #define | GMAC_ST2CW022_COMPVAL_Msk (0xffffu << GMAC_ST2CW022_COMPVAL_Pos) |

| (GMAC_ST2CW022) Compare Value More... | |

| #define | GMAC_ST2CW022_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW022_MASKVAL(value) ((GMAC_ST2CW022_MASKVAL_Msk & ((value) << GMAC_ST2CW022_MASKVAL_Pos))) |

| #define | GMAC_ST2CW022_MASKVAL_Msk (0xffffu << GMAC_ST2CW022_MASKVAL_Pos) |

| (GMAC_ST2CW022) Mask Value More... | |

| #define | GMAC_ST2CW022_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW023_COMPVAL(value) ((GMAC_ST2CW023_COMPVAL_Msk & ((value) << GMAC_ST2CW023_COMPVAL_Pos))) |

| #define | GMAC_ST2CW023_COMPVAL_Msk (0xffffu << GMAC_ST2CW023_COMPVAL_Pos) |

| (GMAC_ST2CW023) Compare Value More... | |

| #define | GMAC_ST2CW023_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW023_MASKVAL(value) ((GMAC_ST2CW023_MASKVAL_Msk & ((value) << GMAC_ST2CW023_MASKVAL_Pos))) |

| #define | GMAC_ST2CW023_MASKVAL_Msk (0xffffu << GMAC_ST2CW023_MASKVAL_Pos) |

| (GMAC_ST2CW023) Mask Value More... | |

| #define | GMAC_ST2CW023_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW02_COMPVAL(value) ((GMAC_ST2CW02_COMPVAL_Msk & ((value) << GMAC_ST2CW02_COMPVAL_Pos))) |

| #define | GMAC_ST2CW02_COMPVAL_Msk (0xffffu << GMAC_ST2CW02_COMPVAL_Pos) |

| (GMAC_ST2CW02) Compare Value More... | |

| #define | GMAC_ST2CW02_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW02_MASKVAL(value) ((GMAC_ST2CW02_MASKVAL_Msk & ((value) << GMAC_ST2CW02_MASKVAL_Pos))) |

| #define | GMAC_ST2CW02_MASKVAL_Msk (0xffffu << GMAC_ST2CW02_MASKVAL_Pos) |

| (GMAC_ST2CW02) Mask Value More... | |

| #define | GMAC_ST2CW02_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW03_COMPVAL(value) ((GMAC_ST2CW03_COMPVAL_Msk & ((value) << GMAC_ST2CW03_COMPVAL_Pos))) |

| #define | GMAC_ST2CW03_COMPVAL_Msk (0xffffu << GMAC_ST2CW03_COMPVAL_Pos) |

| (GMAC_ST2CW03) Compare Value More... | |

| #define | GMAC_ST2CW03_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW03_MASKVAL(value) ((GMAC_ST2CW03_MASKVAL_Msk & ((value) << GMAC_ST2CW03_MASKVAL_Pos))) |

| #define | GMAC_ST2CW03_MASKVAL_Msk (0xffffu << GMAC_ST2CW03_MASKVAL_Pos) |

| (GMAC_ST2CW03) Mask Value More... | |

| #define | GMAC_ST2CW03_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW04_COMPVAL(value) ((GMAC_ST2CW04_COMPVAL_Msk & ((value) << GMAC_ST2CW04_COMPVAL_Pos))) |

| #define | GMAC_ST2CW04_COMPVAL_Msk (0xffffu << GMAC_ST2CW04_COMPVAL_Pos) |

| (GMAC_ST2CW04) Compare Value More... | |

| #define | GMAC_ST2CW04_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW04_MASKVAL(value) ((GMAC_ST2CW04_MASKVAL_Msk & ((value) << GMAC_ST2CW04_MASKVAL_Pos))) |

| #define | GMAC_ST2CW04_MASKVAL_Msk (0xffffu << GMAC_ST2CW04_MASKVAL_Pos) |

| (GMAC_ST2CW04) Mask Value More... | |

| #define | GMAC_ST2CW04_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW05_COMPVAL(value) ((GMAC_ST2CW05_COMPVAL_Msk & ((value) << GMAC_ST2CW05_COMPVAL_Pos))) |

| #define | GMAC_ST2CW05_COMPVAL_Msk (0xffffu << GMAC_ST2CW05_COMPVAL_Pos) |

| (GMAC_ST2CW05) Compare Value More... | |

| #define | GMAC_ST2CW05_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW05_MASKVAL(value) ((GMAC_ST2CW05_MASKVAL_Msk & ((value) << GMAC_ST2CW05_MASKVAL_Pos))) |

| #define | GMAC_ST2CW05_MASKVAL_Msk (0xffffu << GMAC_ST2CW05_MASKVAL_Pos) |

| (GMAC_ST2CW05) Mask Value More... | |

| #define | GMAC_ST2CW05_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW06_COMPVAL(value) ((GMAC_ST2CW06_COMPVAL_Msk & ((value) << GMAC_ST2CW06_COMPVAL_Pos))) |

| #define | GMAC_ST2CW06_COMPVAL_Msk (0xffffu << GMAC_ST2CW06_COMPVAL_Pos) |

| (GMAC_ST2CW06) Compare Value More... | |

| #define | GMAC_ST2CW06_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW06_MASKVAL(value) ((GMAC_ST2CW06_MASKVAL_Msk & ((value) << GMAC_ST2CW06_MASKVAL_Pos))) |

| #define | GMAC_ST2CW06_MASKVAL_Msk (0xffffu << GMAC_ST2CW06_MASKVAL_Pos) |

| (GMAC_ST2CW06) Mask Value More... | |

| #define | GMAC_ST2CW06_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW07_COMPVAL(value) ((GMAC_ST2CW07_COMPVAL_Msk & ((value) << GMAC_ST2CW07_COMPVAL_Pos))) |

| #define | GMAC_ST2CW07_COMPVAL_Msk (0xffffu << GMAC_ST2CW07_COMPVAL_Pos) |

| (GMAC_ST2CW07) Compare Value More... | |

| #define | GMAC_ST2CW07_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW07_MASKVAL(value) ((GMAC_ST2CW07_MASKVAL_Msk & ((value) << GMAC_ST2CW07_MASKVAL_Pos))) |

| #define | GMAC_ST2CW07_MASKVAL_Msk (0xffffu << GMAC_ST2CW07_MASKVAL_Pos) |

| (GMAC_ST2CW07) Mask Value More... | |

| #define | GMAC_ST2CW07_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW08_COMPVAL(value) ((GMAC_ST2CW08_COMPVAL_Msk & ((value) << GMAC_ST2CW08_COMPVAL_Pos))) |

| #define | GMAC_ST2CW08_COMPVAL_Msk (0xffffu << GMAC_ST2CW08_COMPVAL_Pos) |

| (GMAC_ST2CW08) Compare Value More... | |

| #define | GMAC_ST2CW08_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW08_MASKVAL(value) ((GMAC_ST2CW08_MASKVAL_Msk & ((value) << GMAC_ST2CW08_MASKVAL_Pos))) |

| #define | GMAC_ST2CW08_MASKVAL_Msk (0xffffu << GMAC_ST2CW08_MASKVAL_Pos) |

| (GMAC_ST2CW08) Mask Value More... | |

| #define | GMAC_ST2CW08_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW09_COMPVAL(value) ((GMAC_ST2CW09_COMPVAL_Msk & ((value) << GMAC_ST2CW09_COMPVAL_Pos))) |

| #define | GMAC_ST2CW09_COMPVAL_Msk (0xffffu << GMAC_ST2CW09_COMPVAL_Pos) |

| (GMAC_ST2CW09) Compare Value More... | |

| #define | GMAC_ST2CW09_COMPVAL_Pos 16 |

| #define | GMAC_ST2CW09_MASKVAL(value) ((GMAC_ST2CW09_MASKVAL_Msk & ((value) << GMAC_ST2CW09_MASKVAL_Pos))) |

| #define | GMAC_ST2CW09_MASKVAL_Msk (0xffffu << GMAC_ST2CW09_MASKVAL_Pos) |

| (GMAC_ST2CW09) Mask Value More... | |

| #define | GMAC_ST2CW09_MASKVAL_Pos 0 |

| #define | GMAC_ST2CW10_OFFSSTRT(value) ((GMAC_ST2CW10_OFFSSTRT_Msk & ((value) << GMAC_ST2CW10_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW10_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW10) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW10_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW10) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW10_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW10) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW10_OFFSSTRT_Msk (0x3u << GMAC_ST2CW10_OFFSSTRT_Pos) |

| (GMAC_ST2CW10) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW10_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW10_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW10) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW10_OFFSVAL(value) ((GMAC_ST2CW10_OFFSVAL_Msk & ((value) << GMAC_ST2CW10_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW10_OFFSVAL_Msk (0x7fu << GMAC_ST2CW10_OFFSVAL_Pos) |

| (GMAC_ST2CW10) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW10_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW110_OFFSSTRT(value) ((GMAC_ST2CW110_OFFSSTRT_Msk & ((value) << GMAC_ST2CW110_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW110_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW110) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW110_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW110) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW110_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW110) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW110_OFFSSTRT_Msk (0x3u << GMAC_ST2CW110_OFFSSTRT_Pos) |

| (GMAC_ST2CW110) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW110_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW110_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW110) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW110_OFFSVAL(value) ((GMAC_ST2CW110_OFFSVAL_Msk & ((value) << GMAC_ST2CW110_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW110_OFFSVAL_Msk (0x7fu << GMAC_ST2CW110_OFFSVAL_Pos) |

| (GMAC_ST2CW110) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW110_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW111_OFFSSTRT(value) ((GMAC_ST2CW111_OFFSSTRT_Msk & ((value) << GMAC_ST2CW111_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW111_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW111) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW111_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW111) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW111_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW111) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW111_OFFSSTRT_Msk (0x3u << GMAC_ST2CW111_OFFSSTRT_Pos) |

| (GMAC_ST2CW111) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW111_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW111_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW111) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW111_OFFSVAL(value) ((GMAC_ST2CW111_OFFSVAL_Msk & ((value) << GMAC_ST2CW111_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW111_OFFSVAL_Msk (0x7fu << GMAC_ST2CW111_OFFSVAL_Pos) |

| (GMAC_ST2CW111) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW111_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW112_OFFSSTRT(value) ((GMAC_ST2CW112_OFFSSTRT_Msk & ((value) << GMAC_ST2CW112_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW112_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW112) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW112_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW112) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW112_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW112) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW112_OFFSSTRT_Msk (0x3u << GMAC_ST2CW112_OFFSSTRT_Pos) |

| (GMAC_ST2CW112) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW112_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW112_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW112) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW112_OFFSVAL(value) ((GMAC_ST2CW112_OFFSVAL_Msk & ((value) << GMAC_ST2CW112_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW112_OFFSVAL_Msk (0x7fu << GMAC_ST2CW112_OFFSVAL_Pos) |

| (GMAC_ST2CW112) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW112_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW113_OFFSSTRT(value) ((GMAC_ST2CW113_OFFSSTRT_Msk & ((value) << GMAC_ST2CW113_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW113_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW113) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW113_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW113) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW113_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW113) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW113_OFFSSTRT_Msk (0x3u << GMAC_ST2CW113_OFFSSTRT_Pos) |

| (GMAC_ST2CW113) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW113_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW113_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW113) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW113_OFFSVAL(value) ((GMAC_ST2CW113_OFFSVAL_Msk & ((value) << GMAC_ST2CW113_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW113_OFFSVAL_Msk (0x7fu << GMAC_ST2CW113_OFFSVAL_Pos) |

| (GMAC_ST2CW113) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW113_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW114_OFFSSTRT(value) ((GMAC_ST2CW114_OFFSSTRT_Msk & ((value) << GMAC_ST2CW114_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW114_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW114) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW114_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW114) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW114_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW114) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW114_OFFSSTRT_Msk (0x3u << GMAC_ST2CW114_OFFSSTRT_Pos) |

| (GMAC_ST2CW114) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW114_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW114_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW114) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW114_OFFSVAL(value) ((GMAC_ST2CW114_OFFSVAL_Msk & ((value) << GMAC_ST2CW114_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW114_OFFSVAL_Msk (0x7fu << GMAC_ST2CW114_OFFSVAL_Pos) |

| (GMAC_ST2CW114) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW114_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW115_OFFSSTRT(value) ((GMAC_ST2CW115_OFFSSTRT_Msk & ((value) << GMAC_ST2CW115_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW115_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW115) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW115_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW115) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW115_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW115) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW115_OFFSSTRT_Msk (0x3u << GMAC_ST2CW115_OFFSSTRT_Pos) |

| (GMAC_ST2CW115) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW115_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW115_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW115) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW115_OFFSVAL(value) ((GMAC_ST2CW115_OFFSVAL_Msk & ((value) << GMAC_ST2CW115_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW115_OFFSVAL_Msk (0x7fu << GMAC_ST2CW115_OFFSVAL_Pos) |

| (GMAC_ST2CW115) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW115_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW116_OFFSSTRT(value) ((GMAC_ST2CW116_OFFSSTRT_Msk & ((value) << GMAC_ST2CW116_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW116_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW116) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW116_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW116) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW116_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW116) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW116_OFFSSTRT_Msk (0x3u << GMAC_ST2CW116_OFFSSTRT_Pos) |

| (GMAC_ST2CW116) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW116_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW116_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW116) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW116_OFFSVAL(value) ((GMAC_ST2CW116_OFFSVAL_Msk & ((value) << GMAC_ST2CW116_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW116_OFFSVAL_Msk (0x7fu << GMAC_ST2CW116_OFFSVAL_Pos) |

| (GMAC_ST2CW116) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW116_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW117_OFFSSTRT(value) ((GMAC_ST2CW117_OFFSSTRT_Msk & ((value) << GMAC_ST2CW117_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW117_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW117) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW117_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW117) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW117_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW117) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW117_OFFSSTRT_Msk (0x3u << GMAC_ST2CW117_OFFSSTRT_Pos) |

| (GMAC_ST2CW117) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW117_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW117_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW117) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW117_OFFSVAL(value) ((GMAC_ST2CW117_OFFSVAL_Msk & ((value) << GMAC_ST2CW117_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW117_OFFSVAL_Msk (0x7fu << GMAC_ST2CW117_OFFSVAL_Pos) |

| (GMAC_ST2CW117) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW117_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW118_OFFSSTRT(value) ((GMAC_ST2CW118_OFFSSTRT_Msk & ((value) << GMAC_ST2CW118_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW118_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW118) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW118_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW118) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW118_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW118) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW118_OFFSSTRT_Msk (0x3u << GMAC_ST2CW118_OFFSSTRT_Pos) |

| (GMAC_ST2CW118) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW118_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW118_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW118) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW118_OFFSVAL(value) ((GMAC_ST2CW118_OFFSVAL_Msk & ((value) << GMAC_ST2CW118_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW118_OFFSVAL_Msk (0x7fu << GMAC_ST2CW118_OFFSVAL_Pos) |

| (GMAC_ST2CW118) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW118_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW119_OFFSSTRT(value) ((GMAC_ST2CW119_OFFSSTRT_Msk & ((value) << GMAC_ST2CW119_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW119_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW119) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW119_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW119) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW119_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW119) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW119_OFFSSTRT_Msk (0x3u << GMAC_ST2CW119_OFFSSTRT_Pos) |

| (GMAC_ST2CW119) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW119_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW119_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW119) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW119_OFFSVAL(value) ((GMAC_ST2CW119_OFFSVAL_Msk & ((value) << GMAC_ST2CW119_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW119_OFFSVAL_Msk (0x7fu << GMAC_ST2CW119_OFFSVAL_Pos) |

| (GMAC_ST2CW119) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW119_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW11_OFFSSTRT(value) ((GMAC_ST2CW11_OFFSSTRT_Msk & ((value) << GMAC_ST2CW11_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW11_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW11) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW11_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW11) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW11_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW11) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW11_OFFSSTRT_Msk (0x3u << GMAC_ST2CW11_OFFSSTRT_Pos) |

| (GMAC_ST2CW11) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW11_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW11_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW11) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW11_OFFSVAL(value) ((GMAC_ST2CW11_OFFSVAL_Msk & ((value) << GMAC_ST2CW11_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW11_OFFSVAL_Msk (0x7fu << GMAC_ST2CW11_OFFSVAL_Pos) |

| (GMAC_ST2CW11) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW11_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW120_OFFSSTRT(value) ((GMAC_ST2CW120_OFFSSTRT_Msk & ((value) << GMAC_ST2CW120_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW120_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW120) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW120_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW120) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW120_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW120) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW120_OFFSSTRT_Msk (0x3u << GMAC_ST2CW120_OFFSSTRT_Pos) |

| (GMAC_ST2CW120) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW120_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW120_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW120) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW120_OFFSVAL(value) ((GMAC_ST2CW120_OFFSVAL_Msk & ((value) << GMAC_ST2CW120_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW120_OFFSVAL_Msk (0x7fu << GMAC_ST2CW120_OFFSVAL_Pos) |

| (GMAC_ST2CW120) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW120_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW121_OFFSSTRT(value) ((GMAC_ST2CW121_OFFSSTRT_Msk & ((value) << GMAC_ST2CW121_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW121_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW121) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW121_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW121) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW121_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW121) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW121_OFFSSTRT_Msk (0x3u << GMAC_ST2CW121_OFFSSTRT_Pos) |

| (GMAC_ST2CW121) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW121_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW121_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW121) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW121_OFFSVAL(value) ((GMAC_ST2CW121_OFFSVAL_Msk & ((value) << GMAC_ST2CW121_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW121_OFFSVAL_Msk (0x7fu << GMAC_ST2CW121_OFFSVAL_Pos) |

| (GMAC_ST2CW121) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW121_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW122_OFFSSTRT(value) ((GMAC_ST2CW122_OFFSSTRT_Msk & ((value) << GMAC_ST2CW122_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW122_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW122) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW122_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW122) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW122_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW122) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW122_OFFSSTRT_Msk (0x3u << GMAC_ST2CW122_OFFSSTRT_Pos) |

| (GMAC_ST2CW122) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW122_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW122_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW122) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW122_OFFSVAL(value) ((GMAC_ST2CW122_OFFSVAL_Msk & ((value) << GMAC_ST2CW122_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW122_OFFSVAL_Msk (0x7fu << GMAC_ST2CW122_OFFSVAL_Pos) |

| (GMAC_ST2CW122) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW122_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW123_OFFSSTRT(value) ((GMAC_ST2CW123_OFFSSTRT_Msk & ((value) << GMAC_ST2CW123_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW123_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW123) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW123_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW123) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW123_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW123) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW123_OFFSSTRT_Msk (0x3u << GMAC_ST2CW123_OFFSSTRT_Pos) |

| (GMAC_ST2CW123) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW123_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW123_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW123) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW123_OFFSVAL(value) ((GMAC_ST2CW123_OFFSVAL_Msk & ((value) << GMAC_ST2CW123_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW123_OFFSVAL_Msk (0x7fu << GMAC_ST2CW123_OFFSVAL_Pos) |

| (GMAC_ST2CW123) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW123_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW12_OFFSSTRT(value) ((GMAC_ST2CW12_OFFSSTRT_Msk & ((value) << GMAC_ST2CW12_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW12_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW12) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW12_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW12) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW12_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW12) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW12_OFFSSTRT_Msk (0x3u << GMAC_ST2CW12_OFFSSTRT_Pos) |

| (GMAC_ST2CW12) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW12_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW12_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW12) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW12_OFFSVAL(value) ((GMAC_ST2CW12_OFFSVAL_Msk & ((value) << GMAC_ST2CW12_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW12_OFFSVAL_Msk (0x7fu << GMAC_ST2CW12_OFFSVAL_Pos) |

| (GMAC_ST2CW12) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW12_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW13_OFFSSTRT(value) ((GMAC_ST2CW13_OFFSSTRT_Msk & ((value) << GMAC_ST2CW13_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW13_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW13) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW13_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW13) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW13_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW13) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW13_OFFSSTRT_Msk (0x3u << GMAC_ST2CW13_OFFSSTRT_Pos) |

| (GMAC_ST2CW13) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW13_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW13_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW13) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW13_OFFSVAL(value) ((GMAC_ST2CW13_OFFSVAL_Msk & ((value) << GMAC_ST2CW13_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW13_OFFSVAL_Msk (0x7fu << GMAC_ST2CW13_OFFSVAL_Pos) |

| (GMAC_ST2CW13) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW13_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW14_OFFSSTRT(value) ((GMAC_ST2CW14_OFFSSTRT_Msk & ((value) << GMAC_ST2CW14_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW14_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW14) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW14_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW14) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW14_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW14) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW14_OFFSSTRT_Msk (0x3u << GMAC_ST2CW14_OFFSSTRT_Pos) |

| (GMAC_ST2CW14) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW14_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW14_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW14) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW14_OFFSVAL(value) ((GMAC_ST2CW14_OFFSVAL_Msk & ((value) << GMAC_ST2CW14_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW14_OFFSVAL_Msk (0x7fu << GMAC_ST2CW14_OFFSVAL_Pos) |

| (GMAC_ST2CW14) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW14_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW15_OFFSSTRT(value) ((GMAC_ST2CW15_OFFSSTRT_Msk & ((value) << GMAC_ST2CW15_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW15_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW15) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW15_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW15) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW15_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW15) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW15_OFFSSTRT_Msk (0x3u << GMAC_ST2CW15_OFFSSTRT_Pos) |

| (GMAC_ST2CW15) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW15_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW15_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW15) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW15_OFFSVAL(value) ((GMAC_ST2CW15_OFFSVAL_Msk & ((value) << GMAC_ST2CW15_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW15_OFFSVAL_Msk (0x7fu << GMAC_ST2CW15_OFFSVAL_Pos) |

| (GMAC_ST2CW15) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW15_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW16_OFFSSTRT(value) ((GMAC_ST2CW16_OFFSSTRT_Msk & ((value) << GMAC_ST2CW16_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW16_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW16) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW16_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW16) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW16_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW16) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW16_OFFSSTRT_Msk (0x3u << GMAC_ST2CW16_OFFSSTRT_Pos) |

| (GMAC_ST2CW16) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW16_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW16_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW16) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW16_OFFSVAL(value) ((GMAC_ST2CW16_OFFSVAL_Msk & ((value) << GMAC_ST2CW16_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW16_OFFSVAL_Msk (0x7fu << GMAC_ST2CW16_OFFSVAL_Pos) |

| (GMAC_ST2CW16) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW16_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW17_OFFSSTRT(value) ((GMAC_ST2CW17_OFFSSTRT_Msk & ((value) << GMAC_ST2CW17_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW17_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW17) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW17_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW17) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW17_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW17) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW17_OFFSSTRT_Msk (0x3u << GMAC_ST2CW17_OFFSSTRT_Pos) |

| (GMAC_ST2CW17) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW17_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW17_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW17) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW17_OFFSVAL(value) ((GMAC_ST2CW17_OFFSVAL_Msk & ((value) << GMAC_ST2CW17_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW17_OFFSVAL_Msk (0x7fu << GMAC_ST2CW17_OFFSVAL_Pos) |

| (GMAC_ST2CW17) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW17_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW18_OFFSSTRT(value) ((GMAC_ST2CW18_OFFSSTRT_Msk & ((value) << GMAC_ST2CW18_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW18_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW18) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW18_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW18) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW18_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW18) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW18_OFFSSTRT_Msk (0x3u << GMAC_ST2CW18_OFFSSTRT_Pos) |

| (GMAC_ST2CW18) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW18_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW18_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW18) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW18_OFFSVAL(value) ((GMAC_ST2CW18_OFFSVAL_Msk & ((value) << GMAC_ST2CW18_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW18_OFFSVAL_Msk (0x7fu << GMAC_ST2CW18_OFFSVAL_Pos) |

| (GMAC_ST2CW18) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW18_OFFSVAL_Pos 0 |

| #define | GMAC_ST2CW19_OFFSSTRT(value) ((GMAC_ST2CW19_OFFSSTRT_Msk & ((value) << GMAC_ST2CW19_OFFSSTRT_Pos))) |

| #define | GMAC_ST2CW19_OFFSSTRT_ETHERTYPE (0x1u << 7) |

| (GMAC_ST2CW19) Offset from the byte after the EtherType field More... | |

| #define | GMAC_ST2CW19_OFFSSTRT_FRAMESTART (0x0u << 7) |

| (GMAC_ST2CW19) Offset from the start of the frame More... | |

| #define | GMAC_ST2CW19_OFFSSTRT_IP (0x2u << 7) |

| (GMAC_ST2CW19) Offset from the byte after the IP header field More... | |

| #define | GMAC_ST2CW19_OFFSSTRT_Msk (0x3u << GMAC_ST2CW19_OFFSSTRT_Pos) |

| (GMAC_ST2CW19) Ethernet Frame Offset Start More... | |

| #define | GMAC_ST2CW19_OFFSSTRT_Pos 7 |

| #define | GMAC_ST2CW19_OFFSSTRT_TCP_UDP (0x3u << 7) |

| (GMAC_ST2CW19) Offset from the byte after the TCP/UDP header field More... | |

| #define | GMAC_ST2CW19_OFFSVAL(value) ((GMAC_ST2CW19_OFFSVAL_Msk & ((value) << GMAC_ST2CW19_OFFSVAL_Pos))) |

| #define | GMAC_ST2CW19_OFFSVAL_Msk (0x7fu << GMAC_ST2CW19_OFFSVAL_Pos) |

| (GMAC_ST2CW19) Offset Value in Bytes More... | |

| #define | GMAC_ST2CW19_OFFSVAL_Pos 0 |