|

Macros | |

| #define | __CM4_REV 0x0001 |

| Configuration of the Cortex-M4 Processor and Core Peripherals. More... | |

| #define | __FPU_PRESENT 1 |

| #define | __MPU_PRESENT 0 |

| Configuration of the Cortex-M3 Processor and Core Peripherals. More... | |

| #define | __MPU_PRESENT 1 |

| #define | __NVIC_PRIO_BITS 4 |

| #define | __NVIC_PRIO_BITS 4 |

| #define | __Vendor_SysTickConfig 0 |

| #define | __Vendor_SysTickConfig 0 |

Typedefs | |

| typedef enum IRQn | IRQn_Type |

| STM32F10x Interrupt Number Definition, according to the selected device in Library_configuration_section. More... | |

| typedef enum IRQn | IRQn_Type |

| STM32F4XX Interrupt Number Definition, according to the selected device in Library_configuration_section. More... | |

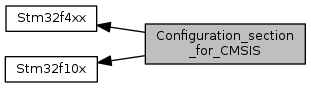

Detailed Description

Macro Definition Documentation

| #define __CM4_REV 0x0001 |

Configuration of the Cortex-M4 Processor and Core Peripherals.

Core revision r0p1

Definition at line 176 of file stm32f4xx.h.

| #define __FPU_PRESENT 1 |

FPU present

Definition at line 180 of file stm32f4xx.h.

| #define __MPU_PRESENT 0 |

Configuration of the Cortex-M3 Processor and Core Peripherals.

Other STM32 devices does not provide an MPU

Definition at line 158 of file stm32f10x.h.

| #define __MPU_PRESENT 1 |

STM32F4XX provides an MPU

Definition at line 177 of file stm32f4xx.h.

| #define __NVIC_PRIO_BITS 4 |

STM32 uses 4 Bits for the Priority Levels

Definition at line 160 of file stm32f10x.h.

| #define __NVIC_PRIO_BITS 4 |

STM32F4XX uses 4 Bits for the Priority Levels

Definition at line 178 of file stm32f4xx.h.

| #define __Vendor_SysTickConfig 0 |

Set to 1 if different SysTick Config is used

Definition at line 161 of file stm32f10x.h.

| #define __Vendor_SysTickConfig 0 |

Set to 1 if different SysTick Config is used

Definition at line 179 of file stm32f4xx.h.

Typedef Documentation

STM32F10x Interrupt Number Definition, according to the selected device in Library_configuration_section.

STM32F4XX Interrupt Number Definition, according to the selected device in Library_configuration_section.

Enumeration Type Documentation

| enum IRQn |

STM32F10x Interrupt Number Definition, according to the selected device in Library_configuration_section.

Definition at line 167 of file stm32f10x.h.

| enum IRQn |

STM32F4XX Interrupt Number Definition, according to the selected device in Library_configuration_section.

Definition at line 186 of file stm32f4xx.h.