Go to the source code of this file.

Functions | |

| int | ath5k_hw_get_isr (struct ath5k_hw *ah, enum ath5k_int *interrupt_mask) |

| u32 | ath5k_hw_get_rxdp (struct ath5k_hw *ah) |

| u32 | ath5k_hw_get_txdp (struct ath5k_hw *ah, unsigned int queue) |

| bool | ath5k_hw_is_intr_pending (struct ath5k_hw *ah) |

| enum ath5k_int | ath5k_hw_set_imr (struct ath5k_hw *ah, enum ath5k_int new_mask) |

| void | ath5k_hw_set_rxdp (struct ath5k_hw *ah, u32 phys_addr) |

| int | ath5k_hw_set_txdp (struct ath5k_hw *ah, unsigned int queue, u32 phys_addr) |

| void | ath5k_hw_start_rx_dma (struct ath5k_hw *ah) |

| int | ath5k_hw_start_tx_dma (struct ath5k_hw *ah, unsigned int queue) |

| int | ath5k_hw_stop_rx_dma (struct ath5k_hw *ah) |

| int | ath5k_hw_stop_tx_dma (struct ath5k_hw *ah, unsigned int queue) |

| int | ath5k_hw_update_tx_triglevel (struct ath5k_hw *ah, bool increase) |

Function Documentation

| int ath5k_hw_get_isr | ( | struct ath5k_hw * | ah, |

| enum ath5k_int * | interrupt_mask | ||

| ) |

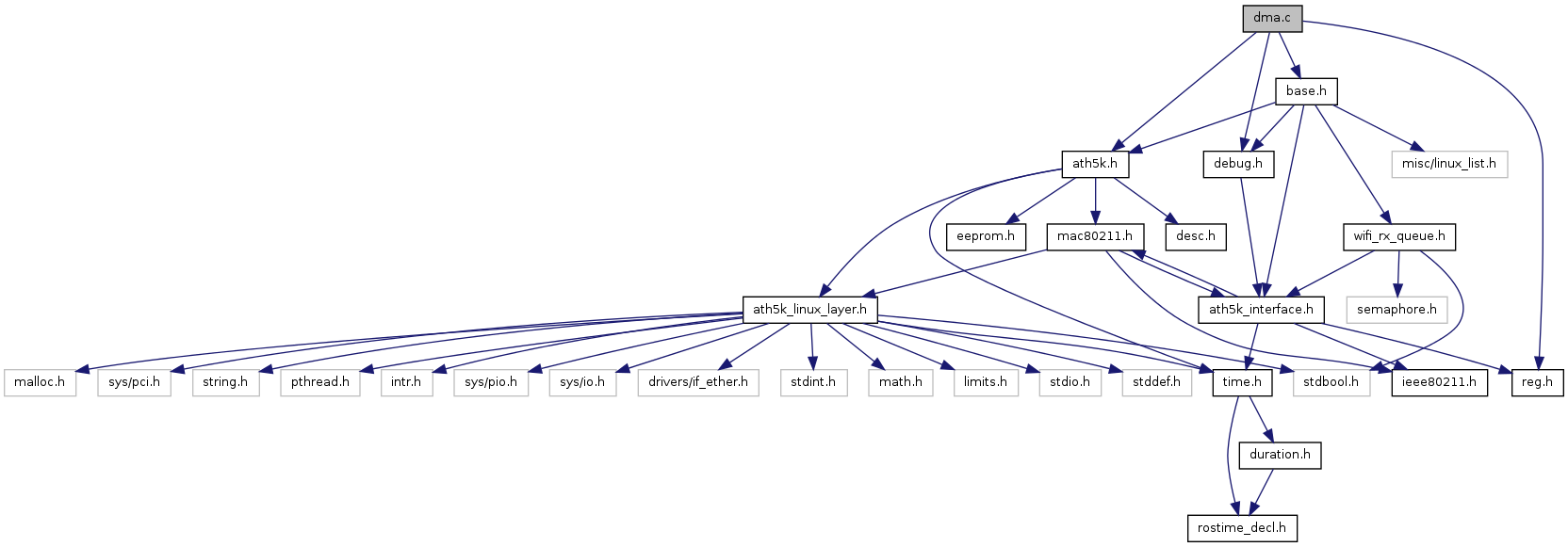

Definition at line 505 of file MaRTE_OS/hwi/ath5k_raw/module/dma.c.

| u32 ath5k_hw_get_rxdp | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_get_rxdp - Get RX Descriptor's address

: The &struct ath5k_hw

Definition at line 115 of file MaRTE_OS/hwi/ath5k_raw/module/dma.c.

| u32 ath5k_hw_get_txdp | ( | struct ath5k_hw * | ah, |

| unsigned int | queue | ||

| ) |

ath5k_hw_get_txdp - Get TX Descriptor's address for a specific queue

: The &struct ath5k_hw : The hw queue number

Get TX descriptor's address for a specific queue. For 5210 we ignore the queue number and use tx queue type since we only have 2 queues. We use TXDP0 for normal data queue and TXDP1 for beacon queue. For newer chips with QCU/DCU we just read the corresponding TXDP register.

XXX: Is TXDP read and clear ?

Definition at line 327 of file MaRTE_OS/hwi/ath5k_raw/module/dma.c.

| bool ath5k_hw_is_intr_pending | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_is_intr_pending - Check if we have pending interrupts

: The &struct ath5k_hw

Check if we have pending interrupts to process. Returns 1 if we have pending interrupts and 0 if we haven't.

Definition at line 483 of file MaRTE_OS/hwi/ath5k_raw/module/dma.c.

| enum ath5k_int ath5k_hw_set_imr | ( | struct ath5k_hw * | ah, |

| enum ath5k_int | new_mask | ||

| ) |

ath5k_hw_set_imr - Set interrupt mask

: The &struct ath5k_hw : The new interrupt mask to be set

Set the interrupt mask in hw to save interrupts. We do that by mapping ath5k_int bits to hw-specific bits to remove abstraction and writing Interrupt Mask Register.

Definition at line 651 of file MaRTE_OS/hwi/ath5k_raw/module/dma.c.

| void ath5k_hw_set_rxdp | ( | struct ath5k_hw * | ah, |

| u32 | phys_addr | ||

| ) |

ath5k_hw_set_rxdp - Set RX Descriptor's address

: The &struct ath5k_hw : RX descriptor address

XXX: Should we check if rx is enabled before setting rxdp ?

Definition at line 128 of file MaRTE_OS/hwi/ath5k_raw/module/dma.c.

| int ath5k_hw_set_txdp | ( | struct ath5k_hw * | ah, |

| unsigned int | queue, | ||

| u32 | phys_addr | ||

| ) |

ath5k_hw_set_txdp - Set TX Descriptor's address for a specific queue

: The &struct ath5k_hw : The hw queue number

Set TX descriptor's address for a specific queue. For 5210 we ignore the queue number and we use tx queue type since we only have 2 queues so as above we use TXDP0 for normal data queue and TXDP1 for beacon queue. For newer chips with QCU/DCU we just set the corresponding TXDP register. Returns -EINVAL if queue type is invalid for 5210 and -EIO if queue is still active.

Definition at line 370 of file MaRTE_OS/hwi/ath5k_raw/module/dma.c.

| void ath5k_hw_start_rx_dma | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_start_rx_dma - Start DMA receive

: The &struct ath5k_hw

Definition at line 80 of file MaRTE_OS/hwi/ath5k_raw/module/dma.c.

| int ath5k_hw_start_tx_dma | ( | struct ath5k_hw * | ah, |

| unsigned int | queue | ||

| ) |

ath5k_hw_start_tx_dma - Start DMA transmit for a specific queue

: The &struct ath5k_hw : The hw queue number

Start DMA transmit for a specific queue and since 5210 doesn't have QCU/DCU, set up queue parameters for 5210 here based on queue type (one queue for normal data and one queue for beacons). For queue setup on newer chips check out qcu.c. Returns -EINVAL if queue number is out of range or if queue is already disabled.

NOTE: Must be called after setting up tx control descriptor for that queue (see below).

Definition at line 155 of file MaRTE_OS/hwi/ath5k_raw/module/dma.c.

| int ath5k_hw_stop_rx_dma | ( | struct ath5k_hw * | ah | ) |

ath5k_hw_stop_rx_dma - Stop DMA receive

: The &struct ath5k_hw

Definition at line 92 of file MaRTE_OS/hwi/ath5k_raw/module/dma.c.

| int ath5k_hw_stop_tx_dma | ( | struct ath5k_hw * | ah, |

| unsigned int | queue | ||

| ) |

ath5k_hw_stop_tx_dma - Stop DMA transmit on a specific queue

: The &struct ath5k_hw : The hw queue number

Stop DMA transmit on a specific hw queue and drain queue so we don't have any pending frames. Returns -EBUSY if we still have pending frames, -EINVAL if queue number is out of range.

Definition at line 215 of file MaRTE_OS/hwi/ath5k_raw/module/dma.c.

| int ath5k_hw_update_tx_triglevel | ( | struct ath5k_hw * | ah, |

| bool | increase | ||

| ) |

ath5k_hw_update_tx_triglevel - Update tx trigger level

: The &struct ath5k_hw : Flag to force increase of trigger level

This function increases/decreases the tx trigger level for the tx fifo buffer (aka FIFO threshold) that is used to indicate when PCU flushes the buffer and transmits it's data. Lowering this results sending small frames more quickly but can lead to tx underruns, raising it a lot can result other problems (i think bmiss is related). Right now we start with the lowest possible (64Bytes) and if we get tx underrun we increase it using the increase flag. Returns -EIO if we have have reached maximum/minimum.

XXX: Link this with tx DMA size ? XXX: Use it to save interrupts ? TODO: Needs testing, i think it's related to bmiss...

Definition at line 429 of file MaRTE_OS/hwi/ath5k_raw/module/dma.c.