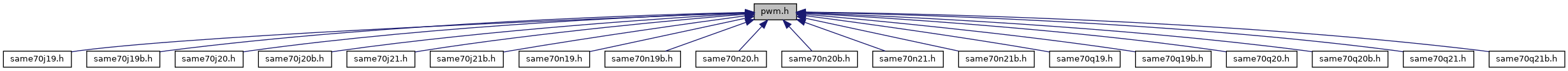

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Pwm |

| struct | PwmCh_num |

| PwmCh_num hardware registers. More... | |

| struct | PwmCmp |

| PwmCmp hardware registers. More... | |

Macros | |

| #define | PWM_CCNT_CNT_Msk (0xffffffu << PWM_CCNT_CNT_Pos) |

| (PWM_CCNT) Channel Counter Register More... | |

| #define | PWM_CCNT_CNT_Pos 0 |

| #define | PWM_CDTY_CDTY(value) ((PWM_CDTY_CDTY_Msk & ((value) << PWM_CDTY_CDTY_Pos))) |

| #define | PWM_CDTY_CDTY_Msk (0xffffffu << PWM_CDTY_CDTY_Pos) |

| (PWM_CDTY) Channel Duty-Cycle More... | |

| #define | PWM_CDTY_CDTY_Pos 0 |

| #define | PWM_CDTYUPD_CDTYUPD(value) ((PWM_CDTYUPD_CDTYUPD_Msk & ((value) << PWM_CDTYUPD_CDTYUPD_Pos))) |

| #define | PWM_CDTYUPD_CDTYUPD_Msk (0xffffffu << PWM_CDTYUPD_CDTYUPD_Pos) |

| (PWM_CDTYUPD) Channel Duty-Cycle Update More... | |

| #define | PWM_CDTYUPD_CDTYUPD_Pos 0 |

| #define | PWM_CLK_DIVA(value) ((PWM_CLK_DIVA_Msk & ((value) << PWM_CLK_DIVA_Pos))) |

| #define | PWM_CLK_DIVA_CLKA_POFF (0x0u << 0) |

| (PWM_CLK) CLKA clock is turned off More... | |

| #define | PWM_CLK_DIVA_Msk (0xffu << PWM_CLK_DIVA_Pos) |

| (PWM_CLK) CLKA Divide Factor More... | |

| #define | PWM_CLK_DIVA_Pos 0 |

| #define | PWM_CLK_DIVA_PREA (0x1u << 0) |

| (PWM_CLK) CLKA clock is clock selected by PREA More... | |

| #define | PWM_CLK_DIVB(value) ((PWM_CLK_DIVB_Msk & ((value) << PWM_CLK_DIVB_Pos))) |

| #define | PWM_CLK_DIVB_CLKB_POFF (0x0u << 16) |

| (PWM_CLK) CLKB clock is turned off More... | |

| #define | PWM_CLK_DIVB_Msk (0xffu << PWM_CLK_DIVB_Pos) |

| (PWM_CLK) CLKB Divide Factor More... | |

| #define | PWM_CLK_DIVB_Pos 16 |

| #define | PWM_CLK_DIVB_PREB (0x1u << 16) |

| (PWM_CLK) CLKB clock is clock selected by PREB More... | |

| #define | PWM_CLK_PREA(value) ((PWM_CLK_PREA_Msk & ((value) << PWM_CLK_PREA_Pos))) |

| #define | PWM_CLK_PREA_CLK (0x0u << 8) |

| (PWM_CLK) Peripheral clock More... | |

| #define | PWM_CLK_PREA_CLK_DIV1024 (0xAu << 8) |

| (PWM_CLK) Peripheral clock/1024 More... | |

| #define | PWM_CLK_PREA_CLK_DIV128 (0x7u << 8) |

| (PWM_CLK) Peripheral clock/128 More... | |

| #define | PWM_CLK_PREA_CLK_DIV16 (0x4u << 8) |

| (PWM_CLK) Peripheral clock/16 More... | |

| #define | PWM_CLK_PREA_CLK_DIV2 (0x1u << 8) |

| (PWM_CLK) Peripheral clock/2 More... | |

| #define | PWM_CLK_PREA_CLK_DIV256 (0x8u << 8) |

| (PWM_CLK) Peripheral clock/256 More... | |

| #define | PWM_CLK_PREA_CLK_DIV32 (0x5u << 8) |

| (PWM_CLK) Peripheral clock/32 More... | |

| #define | PWM_CLK_PREA_CLK_DIV4 (0x2u << 8) |

| (PWM_CLK) Peripheral clock/4 More... | |

| #define | PWM_CLK_PREA_CLK_DIV512 (0x9u << 8) |

| (PWM_CLK) Peripheral clock/512 More... | |

| #define | PWM_CLK_PREA_CLK_DIV64 (0x6u << 8) |

| (PWM_CLK) Peripheral clock/64 More... | |

| #define | PWM_CLK_PREA_CLK_DIV8 (0x3u << 8) |

| (PWM_CLK) Peripheral clock/8 More... | |

| #define | PWM_CLK_PREA_Msk (0xfu << PWM_CLK_PREA_Pos) |

| (PWM_CLK) CLKA Source Clock Selection More... | |

| #define | PWM_CLK_PREA_Pos 8 |

| #define | PWM_CLK_PREB(value) ((PWM_CLK_PREB_Msk & ((value) << PWM_CLK_PREB_Pos))) |

| #define | PWM_CLK_PREB_CLK (0x0u << 24) |

| (PWM_CLK) Peripheral clock More... | |

| #define | PWM_CLK_PREB_CLK_DIV1024 (0xAu << 24) |

| (PWM_CLK) Peripheral clock/1024 More... | |

| #define | PWM_CLK_PREB_CLK_DIV128 (0x7u << 24) |

| (PWM_CLK) Peripheral clock/128 More... | |

| #define | PWM_CLK_PREB_CLK_DIV16 (0x4u << 24) |

| (PWM_CLK) Peripheral clock/16 More... | |

| #define | PWM_CLK_PREB_CLK_DIV2 (0x1u << 24) |

| (PWM_CLK) Peripheral clock/2 More... | |

| #define | PWM_CLK_PREB_CLK_DIV256 (0x8u << 24) |

| (PWM_CLK) Peripheral clock/256 More... | |

| #define | PWM_CLK_PREB_CLK_DIV32 (0x5u << 24) |

| (PWM_CLK) Peripheral clock/32 More... | |

| #define | PWM_CLK_PREB_CLK_DIV4 (0x2u << 24) |

| (PWM_CLK) Peripheral clock/4 More... | |

| #define | PWM_CLK_PREB_CLK_DIV512 (0x9u << 24) |

| (PWM_CLK) Peripheral clock/512 More... | |

| #define | PWM_CLK_PREB_CLK_DIV64 (0x6u << 24) |

| (PWM_CLK) Peripheral clock/64 More... | |

| #define | PWM_CLK_PREB_CLK_DIV8 (0x3u << 24) |

| (PWM_CLK) Peripheral clock/8 More... | |

| #define | PWM_CLK_PREB_Msk (0xfu << PWM_CLK_PREB_Pos) |

| (PWM_CLK) CLKB Source Clock Selection More... | |

| #define | PWM_CLK_PREB_Pos 24 |

| #define | PWM_CMPM_CEN (0x1u << 0) |

| (PWM_CMPM) Comparison x Enable More... | |

| #define | PWM_CMPM_CPR(value) ((PWM_CMPM_CPR_Msk & ((value) << PWM_CMPM_CPR_Pos))) |

| #define | PWM_CMPM_CPR_Msk (0xfu << PWM_CMPM_CPR_Pos) |

| (PWM_CMPM) Comparison x Period More... | |

| #define | PWM_CMPM_CPR_Pos 8 |

| #define | PWM_CMPM_CPRCNT(value) ((PWM_CMPM_CPRCNT_Msk & ((value) << PWM_CMPM_CPRCNT_Pos))) |

| #define | PWM_CMPM_CPRCNT_Msk (0xfu << PWM_CMPM_CPRCNT_Pos) |

| (PWM_CMPM) Comparison x Period Counter More... | |

| #define | PWM_CMPM_CPRCNT_Pos 12 |

| #define | PWM_CMPM_CTR(value) ((PWM_CMPM_CTR_Msk & ((value) << PWM_CMPM_CTR_Pos))) |

| #define | PWM_CMPM_CTR_Msk (0xfu << PWM_CMPM_CTR_Pos) |

| (PWM_CMPM) Comparison x Trigger More... | |

| #define | PWM_CMPM_CTR_Pos 4 |

| #define | PWM_CMPM_CUPR(value) ((PWM_CMPM_CUPR_Msk & ((value) << PWM_CMPM_CUPR_Pos))) |

| #define | PWM_CMPM_CUPR_Msk (0xfu << PWM_CMPM_CUPR_Pos) |

| (PWM_CMPM) Comparison x Update Period More... | |

| #define | PWM_CMPM_CUPR_Pos 16 |

| #define | PWM_CMPM_CUPRCNT(value) ((PWM_CMPM_CUPRCNT_Msk & ((value) << PWM_CMPM_CUPRCNT_Pos))) |

| #define | PWM_CMPM_CUPRCNT_Msk (0xfu << PWM_CMPM_CUPRCNT_Pos) |

| (PWM_CMPM) Comparison x Update Period Counter More... | |

| #define | PWM_CMPM_CUPRCNT_Pos 20 |

| #define | PWM_CMPMUPD_CENUPD (0x1u << 0) |

| (PWM_CMPMUPD) Comparison x Enable Update More... | |

| #define | PWM_CMPMUPD_CPRUPD(value) ((PWM_CMPMUPD_CPRUPD_Msk & ((value) << PWM_CMPMUPD_CPRUPD_Pos))) |

| #define | PWM_CMPMUPD_CPRUPD_Msk (0xfu << PWM_CMPMUPD_CPRUPD_Pos) |

| (PWM_CMPMUPD) Comparison x Period Update More... | |

| #define | PWM_CMPMUPD_CPRUPD_Pos 8 |

| #define | PWM_CMPMUPD_CTRUPD(value) ((PWM_CMPMUPD_CTRUPD_Msk & ((value) << PWM_CMPMUPD_CTRUPD_Pos))) |

| #define | PWM_CMPMUPD_CTRUPD_Msk (0xfu << PWM_CMPMUPD_CTRUPD_Pos) |

| (PWM_CMPMUPD) Comparison x Trigger Update More... | |

| #define | PWM_CMPMUPD_CTRUPD_Pos 4 |

| #define | PWM_CMPMUPD_CUPRUPD(value) ((PWM_CMPMUPD_CUPRUPD_Msk & ((value) << PWM_CMPMUPD_CUPRUPD_Pos))) |

| #define | PWM_CMPMUPD_CUPRUPD_Msk (0xfu << PWM_CMPMUPD_CUPRUPD_Pos) |

| (PWM_CMPMUPD) Comparison x Update Period Update More... | |

| #define | PWM_CMPMUPD_CUPRUPD_Pos 16 |

| #define | PWM_CMPV_CV(value) ((PWM_CMPV_CV_Msk & ((value) << PWM_CMPV_CV_Pos))) |

| #define | PWM_CMPV_CV_Msk (0xffffffu << PWM_CMPV_CV_Pos) |

| (PWM_CMPV) Comparison x Value More... | |

| #define | PWM_CMPV_CV_Pos 0 |

| #define | PWM_CMPV_CVM (0x1u << 24) |

| (PWM_CMPV) Comparison x Value Mode More... | |

| #define | PWM_CMPVUPD_CVMUPD (0x1u << 24) |

| (PWM_CMPVUPD) Comparison x Value Mode Update More... | |

| #define | PWM_CMPVUPD_CVUPD(value) ((PWM_CMPVUPD_CVUPD_Msk & ((value) << PWM_CMPVUPD_CVUPD_Pos))) |

| #define | PWM_CMPVUPD_CVUPD_Msk (0xffffffu << PWM_CMPVUPD_CVUPD_Pos) |

| (PWM_CMPVUPD) Comparison x Value Update More... | |

| #define | PWM_CMPVUPD_CVUPD_Pos 0 |

| #define | PWM_CMR_CALG (0x1u << 8) |

| (PWM_CMR) Channel Alignment More... | |

| #define | PWM_CMR_CES (0x1u << 10) |

| (PWM_CMR) Counter Event Selection More... | |

| #define | PWM_CMR_CPOL (0x1u << 9) |

| (PWM_CMR) Channel Polarity More... | |

| #define | PWM_CMR_CPRE(value) ((PWM_CMR_CPRE_Msk & ((value) << PWM_CMR_CPRE_Pos))) |

| #define | PWM_CMR_CPRE_CLKA (0xBu << 0) |

| (PWM_CMR) Clock A More... | |

| #define | PWM_CMR_CPRE_CLKB (0xCu << 0) |

| (PWM_CMR) Clock B More... | |

| #define | PWM_CMR_CPRE_MCK (0x0u << 0) |

| (PWM_CMR) Peripheral clock More... | |

| #define | PWM_CMR_CPRE_MCK_DIV_1024 (0xAu << 0) |

| (PWM_CMR) Peripheral clock/1024 More... | |

| #define | PWM_CMR_CPRE_MCK_DIV_128 (0x7u << 0) |

| (PWM_CMR) Peripheral clock/128 More... | |

| #define | PWM_CMR_CPRE_MCK_DIV_16 (0x4u << 0) |

| (PWM_CMR) Peripheral clock/16 More... | |

| #define | PWM_CMR_CPRE_MCK_DIV_2 (0x1u << 0) |

| (PWM_CMR) Peripheral clock/2 More... | |

| #define | PWM_CMR_CPRE_MCK_DIV_256 (0x8u << 0) |

| (PWM_CMR) Peripheral clock/256 More... | |

| #define | PWM_CMR_CPRE_MCK_DIV_32 (0x5u << 0) |

| (PWM_CMR) Peripheral clock/32 More... | |

| #define | PWM_CMR_CPRE_MCK_DIV_4 (0x2u << 0) |

| (PWM_CMR) Peripheral clock/4 More... | |

| #define | PWM_CMR_CPRE_MCK_DIV_512 (0x9u << 0) |

| (PWM_CMR) Peripheral clock/512 More... | |

| #define | PWM_CMR_CPRE_MCK_DIV_64 (0x6u << 0) |

| (PWM_CMR) Peripheral clock/64 More... | |

| #define | PWM_CMR_CPRE_MCK_DIV_8 (0x3u << 0) |

| (PWM_CMR) Peripheral clock/8 More... | |

| #define | PWM_CMR_CPRE_Msk (0xfu << PWM_CMR_CPRE_Pos) |

| (PWM_CMR) Channel Pre-scaler More... | |

| #define | PWM_CMR_CPRE_Pos 0 |

| #define | PWM_CMR_DPOLI (0x1u << 12) |

| (PWM_CMR) Disabled Polarity Inverted More... | |

| #define | PWM_CMR_DTE (0x1u << 16) |

| (PWM_CMR) Dead-Time Generator Enable More... | |

| #define | PWM_CMR_DTHI (0x1u << 17) |

| (PWM_CMR) Dead-Time PWMHx Output Inverted More... | |

| #define | PWM_CMR_DTLI (0x1u << 18) |

| (PWM_CMR) Dead-Time PWMLx Output Inverted More... | |

| #define | PWM_CMR_PPM (0x1u << 19) |

| (PWM_CMR) Push-Pull Mode More... | |

| #define | PWM_CMR_TCTS (0x1u << 13) |

| (PWM_CMR) Timer Counter Trigger Selection More... | |

| #define | PWM_CMR_UPDS (0x1u << 11) |

| (PWM_CMR) Update Selection More... | |

| #define | PWM_CMUPD0_CPOLINVUP (0x1u << 13) |

| (PWM_CMUPD0) Channel Polarity Inversion Update More... | |

| #define | PWM_CMUPD0_CPOLUP (0x1u << 9) |

| (PWM_CMUPD0) Channel Polarity Update More... | |

| #define | PWM_CMUPD1_CPOLINVUP (0x1u << 13) |

| (PWM_CMUPD1) Channel Polarity Inversion Update More... | |

| #define | PWM_CMUPD1_CPOLUP (0x1u << 9) |

| (PWM_CMUPD1) Channel Polarity Update More... | |

| #define | PWM_CMUPD2_CPOLINVUP (0x1u << 13) |

| (PWM_CMUPD2) Channel Polarity Inversion Update More... | |

| #define | PWM_CMUPD2_CPOLUP (0x1u << 9) |

| (PWM_CMUPD2) Channel Polarity Update More... | |

| #define | PWM_CMUPD3_CPOLINVUP (0x1u << 13) |

| (PWM_CMUPD3) Channel Polarity Inversion Update More... | |

| #define | PWM_CMUPD3_CPOLUP (0x1u << 9) |

| (PWM_CMUPD3) Channel Polarity Update More... | |

| #define | PWM_CPRD_CPRD(value) ((PWM_CPRD_CPRD_Msk & ((value) << PWM_CPRD_CPRD_Pos))) |

| #define | PWM_CPRD_CPRD_Msk (0xffffffu << PWM_CPRD_CPRD_Pos) |

| (PWM_CPRD) Channel Period More... | |

| #define | PWM_CPRD_CPRD_Pos 0 |

| #define | PWM_CPRDUPD_CPRDUPD(value) ((PWM_CPRDUPD_CPRDUPD_Msk & ((value) << PWM_CPRDUPD_CPRDUPD_Pos))) |

| #define | PWM_CPRDUPD_CPRDUPD_Msk (0xffffffu << PWM_CPRDUPD_CPRDUPD_Pos) |

| (PWM_CPRDUPD) Channel Period Update More... | |

| #define | PWM_CPRDUPD_CPRDUPD_Pos 0 |

| #define | PWM_DIS_CHID0 (0x1u << 0) |

| (PWM_DIS) Channel ID More... | |

| #define | PWM_DIS_CHID1 (0x1u << 1) |

| (PWM_DIS) Channel ID More... | |

| #define | PWM_DIS_CHID2 (0x1u << 2) |

| (PWM_DIS) Channel ID More... | |

| #define | PWM_DIS_CHID3 (0x1u << 3) |

| (PWM_DIS) Channel ID More... | |

| #define | PWM_DMAR_DMADUTY(value) ((PWM_DMAR_DMADUTY_Msk & ((value) << PWM_DMAR_DMADUTY_Pos))) |

| #define | PWM_DMAR_DMADUTY_Msk (0xffffffu << PWM_DMAR_DMADUTY_Pos) |

| (PWM_DMAR) Duty-Cycle Holding Register for DMA Access More... | |

| #define | PWM_DMAR_DMADUTY_Pos 0 |

| #define | PWM_DT_DTH(value) ((PWM_DT_DTH_Msk & ((value) << PWM_DT_DTH_Pos))) |

| #define | PWM_DT_DTH_Msk (0xffffu << PWM_DT_DTH_Pos) |

| (PWM_DT) Dead-Time Value for PWMHx Output More... | |

| #define | PWM_DT_DTH_Pos 0 |

| #define | PWM_DT_DTL(value) ((PWM_DT_DTL_Msk & ((value) << PWM_DT_DTL_Pos))) |

| #define | PWM_DT_DTL_Msk (0xffffu << PWM_DT_DTL_Pos) |

| (PWM_DT) Dead-Time Value for PWMLx Output More... | |

| #define | PWM_DT_DTL_Pos 16 |

| #define | PWM_DTUPD_DTHUPD(value) ((PWM_DTUPD_DTHUPD_Msk & ((value) << PWM_DTUPD_DTHUPD_Pos))) |

| #define | PWM_DTUPD_DTHUPD_Msk (0xffffu << PWM_DTUPD_DTHUPD_Pos) |

| (PWM_DTUPD) Dead-Time Value Update for PWMHx Output More... | |

| #define | PWM_DTUPD_DTHUPD_Pos 0 |

| #define | PWM_DTUPD_DTLUPD(value) ((PWM_DTUPD_DTLUPD_Msk & ((value) << PWM_DTUPD_DTLUPD_Pos))) |

| #define | PWM_DTUPD_DTLUPD_Msk (0xffffu << PWM_DTUPD_DTLUPD_Pos) |

| (PWM_DTUPD) Dead-Time Value Update for PWMLx Output More... | |

| #define | PWM_DTUPD_DTLUPD_Pos 16 |

| #define | PWM_ELMR_CSEL0 (0x1u << 0) |

| (PWM_ELMR[8]) Comparison 0 Selection More... | |

| #define | PWM_ELMR_CSEL1 (0x1u << 1) |

| (PWM_ELMR[8]) Comparison 1 Selection More... | |

| #define | PWM_ELMR_CSEL2 (0x1u << 2) |

| (PWM_ELMR[8]) Comparison 2 Selection More... | |

| #define | PWM_ELMR_CSEL3 (0x1u << 3) |

| (PWM_ELMR[8]) Comparison 3 Selection More... | |

| #define | PWM_ELMR_CSEL4 (0x1u << 4) |

| (PWM_ELMR[8]) Comparison 4 Selection More... | |

| #define | PWM_ELMR_CSEL5 (0x1u << 5) |

| (PWM_ELMR[8]) Comparison 5 Selection More... | |

| #define | PWM_ELMR_CSEL6 (0x1u << 6) |

| (PWM_ELMR[8]) Comparison 6 Selection More... | |

| #define | PWM_ELMR_CSEL7 (0x1u << 7) |

| (PWM_ELMR[8]) Comparison 7 Selection More... | |

| #define | PWM_ENA_CHID0 (0x1u << 0) |

| (PWM_ENA) Channel ID More... | |

| #define | PWM_ENA_CHID1 (0x1u << 1) |

| (PWM_ENA) Channel ID More... | |

| #define | PWM_ENA_CHID2 (0x1u << 2) |

| (PWM_ENA) Channel ID More... | |

| #define | PWM_ENA_CHID3 (0x1u << 3) |

| (PWM_ENA) Channel ID More... | |

| #define | PWM_ETRG1_MAXCNT(value) ((PWM_ETRG1_MAXCNT_Msk & ((value) << PWM_ETRG1_MAXCNT_Pos))) |

| #define | PWM_ETRG1_MAXCNT_Msk (0xffffffu << PWM_ETRG1_MAXCNT_Pos) |

| (PWM_ETRG1) Maximum Counter value More... | |

| #define | PWM_ETRG1_MAXCNT_Pos 0 |

| #define | PWM_ETRG1_RFEN (0x1u << 31) |

| (PWM_ETRG1) Recoverable Fault Enable More... | |

| #define | PWM_ETRG1_TRGEDGE (0x1u << 28) |

| (PWM_ETRG1) Edge Selection More... | |

| #define | PWM_ETRG1_TRGEDGE_FALLING_ZERO (0x0u << 28) |

| (PWM_ETRG1) TRGMODE = 1: TRGINx event detection on falling edge.TRGMODE = 2, 3: TRGINx active level is 0 More... | |

| #define | PWM_ETRG1_TRGEDGE_RISING_ONE (0x1u << 28) |

| (PWM_ETRG1) TRGMODE = 1: TRGINx event detection on rising edge.TRGMODE = 2, 3: TRGINx active level is 1 More... | |

| #define | PWM_ETRG1_TRGFILT (0x1u << 29) |

| (PWM_ETRG1) Filtered input More... | |

| #define | PWM_ETRG1_TRGMODE(value) ((PWM_ETRG1_TRGMODE_Msk & ((value) << PWM_ETRG1_TRGMODE_Pos))) |

| #define | PWM_ETRG1_TRGMODE_MODE1 (0x1u << 24) |

| (PWM_ETRG1) External PWM Reset Mode More... | |

| #define | PWM_ETRG1_TRGMODE_MODE2 (0x2u << 24) |

| (PWM_ETRG1) External PWM Start Mode More... | |

| #define | PWM_ETRG1_TRGMODE_MODE3 (0x3u << 24) |

| (PWM_ETRG1) Cycle-by-cycle Duty Mode More... | |

| #define | PWM_ETRG1_TRGMODE_Msk (0x3u << PWM_ETRG1_TRGMODE_Pos) |

| (PWM_ETRG1) External Trigger Mode More... | |

| #define | PWM_ETRG1_TRGMODE_OFF (0x0u << 24) |

| (PWM_ETRG1) External trigger is not enabled. More... | |

| #define | PWM_ETRG1_TRGMODE_Pos 24 |

| #define | PWM_ETRG1_TRGSRC (0x1u << 30) |

| (PWM_ETRG1) Trigger Source More... | |

| #define | PWM_ETRG2_MAXCNT(value) ((PWM_ETRG2_MAXCNT_Msk & ((value) << PWM_ETRG2_MAXCNT_Pos))) |

| #define | PWM_ETRG2_MAXCNT_Msk (0xffffffu << PWM_ETRG2_MAXCNT_Pos) |

| (PWM_ETRG2) Maximum Counter value More... | |

| #define | PWM_ETRG2_MAXCNT_Pos 0 |

| #define | PWM_ETRG2_RFEN (0x1u << 31) |

| (PWM_ETRG2) Recoverable Fault Enable More... | |

| #define | PWM_ETRG2_TRGEDGE (0x1u << 28) |

| (PWM_ETRG2) Edge Selection More... | |

| #define | PWM_ETRG2_TRGEDGE_FALLING_ZERO (0x0u << 28) |

| (PWM_ETRG2) TRGMODE = 1: TRGINx event detection on falling edge.TRGMODE = 2, 3: TRGINx active level is 0 More... | |

| #define | PWM_ETRG2_TRGEDGE_RISING_ONE (0x1u << 28) |

| (PWM_ETRG2) TRGMODE = 1: TRGINx event detection on rising edge.TRGMODE = 2, 3: TRGINx active level is 1 More... | |

| #define | PWM_ETRG2_TRGFILT (0x1u << 29) |

| (PWM_ETRG2) Filtered input More... | |

| #define | PWM_ETRG2_TRGMODE(value) ((PWM_ETRG2_TRGMODE_Msk & ((value) << PWM_ETRG2_TRGMODE_Pos))) |

| #define | PWM_ETRG2_TRGMODE_MODE1 (0x1u << 24) |

| (PWM_ETRG2) External PWM Reset Mode More... | |

| #define | PWM_ETRG2_TRGMODE_MODE2 (0x2u << 24) |

| (PWM_ETRG2) External PWM Start Mode More... | |

| #define | PWM_ETRG2_TRGMODE_MODE3 (0x3u << 24) |

| (PWM_ETRG2) Cycle-by-cycle Duty Mode More... | |

| #define | PWM_ETRG2_TRGMODE_Msk (0x3u << PWM_ETRG2_TRGMODE_Pos) |

| (PWM_ETRG2) External Trigger Mode More... | |

| #define | PWM_ETRG2_TRGMODE_OFF (0x0u << 24) |

| (PWM_ETRG2) External trigger is not enabled. More... | |

| #define | PWM_ETRG2_TRGMODE_Pos 24 |

| #define | PWM_ETRG2_TRGSRC (0x1u << 30) |

| (PWM_ETRG2) Trigger Source More... | |

| #define | PWM_FCR_FCLR(value) ((PWM_FCR_FCLR_Msk & ((value) << PWM_FCR_FCLR_Pos))) |

| #define | PWM_FCR_FCLR_Msk (0xffu << PWM_FCR_FCLR_Pos) |

| (PWM_FCR) Fault Clear More... | |

| #define | PWM_FCR_FCLR_Pos 0 |

| #define | PWM_FMR_FFIL(value) ((PWM_FMR_FFIL_Msk & ((value) << PWM_FMR_FFIL_Pos))) |

| #define | PWM_FMR_FFIL_Msk (0xffu << PWM_FMR_FFIL_Pos) |

| (PWM_FMR) Fault Filtering More... | |

| #define | PWM_FMR_FFIL_Pos 16 |

| #define | PWM_FMR_FMOD(value) ((PWM_FMR_FMOD_Msk & ((value) << PWM_FMR_FMOD_Pos))) |

| #define | PWM_FMR_FMOD_Msk (0xffu << PWM_FMR_FMOD_Pos) |

| (PWM_FMR) Fault Activation Mode More... | |

| #define | PWM_FMR_FMOD_Pos 8 |

| #define | PWM_FMR_FPOL(value) ((PWM_FMR_FPOL_Msk & ((value) << PWM_FMR_FPOL_Pos))) |

| #define | PWM_FMR_FPOL_Msk (0xffu << PWM_FMR_FPOL_Pos) |

| (PWM_FMR) Fault Polarity More... | |

| #define | PWM_FMR_FPOL_Pos 0 |

| #define | PWM_FPE_FPE0(value) ((PWM_FPE_FPE0_Msk & ((value) << PWM_FPE_FPE0_Pos))) |

| #define | PWM_FPE_FPE0_Msk (0xffu << PWM_FPE_FPE0_Pos) |

| (PWM_FPE) Fault Protection Enable for channel 0 More... | |

| #define | PWM_FPE_FPE0_Pos 0 |

| #define | PWM_FPE_FPE1(value) ((PWM_FPE_FPE1_Msk & ((value) << PWM_FPE_FPE1_Pos))) |

| #define | PWM_FPE_FPE1_Msk (0xffu << PWM_FPE_FPE1_Pos) |

| (PWM_FPE) Fault Protection Enable for channel 1 More... | |

| #define | PWM_FPE_FPE1_Pos 8 |

| #define | PWM_FPE_FPE2(value) ((PWM_FPE_FPE2_Msk & ((value) << PWM_FPE_FPE2_Pos))) |

| #define | PWM_FPE_FPE2_Msk (0xffu << PWM_FPE_FPE2_Pos) |

| (PWM_FPE) Fault Protection Enable for channel 2 More... | |

| #define | PWM_FPE_FPE2_Pos 16 |

| #define | PWM_FPE_FPE3(value) ((PWM_FPE_FPE3_Msk & ((value) << PWM_FPE_FPE3_Pos))) |

| #define | PWM_FPE_FPE3_Msk (0xffu << PWM_FPE_FPE3_Pos) |

| (PWM_FPE) Fault Protection Enable for channel 3 More... | |

| #define | PWM_FPE_FPE3_Pos 24 |

| #define | PWM_FPV1_FPVH0 (0x1u << 0) |

| (PWM_FPV1) Fault Protection Value for PWMH output on channel 0 More... | |

| #define | PWM_FPV1_FPVH1 (0x1u << 1) |

| (PWM_FPV1) Fault Protection Value for PWMH output on channel 1 More... | |

| #define | PWM_FPV1_FPVH2 (0x1u << 2) |

| (PWM_FPV1) Fault Protection Value for PWMH output on channel 2 More... | |

| #define | PWM_FPV1_FPVH3 (0x1u << 3) |

| (PWM_FPV1) Fault Protection Value for PWMH output on channel 3 More... | |

| #define | PWM_FPV1_FPVL0 (0x1u << 16) |

| (PWM_FPV1) Fault Protection Value for PWML output on channel 0 More... | |

| #define | PWM_FPV1_FPVL1 (0x1u << 17) |

| (PWM_FPV1) Fault Protection Value for PWML output on channel 1 More... | |

| #define | PWM_FPV1_FPVL2 (0x1u << 18) |

| (PWM_FPV1) Fault Protection Value for PWML output on channel 2 More... | |

| #define | PWM_FPV1_FPVL3 (0x1u << 19) |

| (PWM_FPV1) Fault Protection Value for PWML output on channel 3 More... | |

| #define | PWM_FPV2_FPZH0 (0x1u << 0) |

| (PWM_FPV2) Fault Protection to Hi-Z for PWMH output on channel 0 More... | |

| #define | PWM_FPV2_FPZH1 (0x1u << 1) |

| (PWM_FPV2) Fault Protection to Hi-Z for PWMH output on channel 1 More... | |

| #define | PWM_FPV2_FPZH2 (0x1u << 2) |

| (PWM_FPV2) Fault Protection to Hi-Z for PWMH output on channel 2 More... | |

| #define | PWM_FPV2_FPZH3 (0x1u << 3) |

| (PWM_FPV2) Fault Protection to Hi-Z for PWMH output on channel 3 More... | |

| #define | PWM_FPV2_FPZL0 (0x1u << 16) |

| (PWM_FPV2) Fault Protection to Hi-Z for PWML output on channel 0 More... | |

| #define | PWM_FPV2_FPZL1 (0x1u << 17) |

| (PWM_FPV2) Fault Protection to Hi-Z for PWML output on channel 1 More... | |

| #define | PWM_FPV2_FPZL2 (0x1u << 18) |

| (PWM_FPV2) Fault Protection to Hi-Z for PWML output on channel 2 More... | |

| #define | PWM_FPV2_FPZL3 (0x1u << 19) |

| (PWM_FPV2) Fault Protection to Hi-Z for PWML output on channel 3 More... | |

| #define | PWM_FSR_FIV_Msk (0xffu << PWM_FSR_FIV_Pos) |

| (PWM_FSR) Fault Input Value More... | |

| #define | PWM_FSR_FIV_Pos 0 |

| #define | PWM_FSR_FS_Msk (0xffu << PWM_FSR_FS_Pos) |

| (PWM_FSR) Fault Status More... | |

| #define | PWM_FSR_FS_Pos 8 |

| #define | PWM_IDR1_CHID0 (0x1u << 0) |

| (PWM_IDR1) Counter Event on Channel 0 Interrupt Disable More... | |

| #define | PWM_IDR1_CHID1 (0x1u << 1) |

| (PWM_IDR1) Counter Event on Channel 1 Interrupt Disable More... | |

| #define | PWM_IDR1_CHID2 (0x1u << 2) |

| (PWM_IDR1) Counter Event on Channel 2 Interrupt Disable More... | |

| #define | PWM_IDR1_CHID3 (0x1u << 3) |

| (PWM_IDR1) Counter Event on Channel 3 Interrupt Disable More... | |

| #define | PWM_IDR1_FCHID0 (0x1u << 16) |

| (PWM_IDR1) Fault Protection Trigger on Channel 0 Interrupt Disable More... | |

| #define | PWM_IDR1_FCHID1 (0x1u << 17) |

| (PWM_IDR1) Fault Protection Trigger on Channel 1 Interrupt Disable More... | |

| #define | PWM_IDR1_FCHID2 (0x1u << 18) |

| (PWM_IDR1) Fault Protection Trigger on Channel 2 Interrupt Disable More... | |

| #define | PWM_IDR1_FCHID3 (0x1u << 19) |

| (PWM_IDR1) Fault Protection Trigger on Channel 3 Interrupt Disable More... | |

| #define | PWM_IDR2_CMPM0 (0x1u << 8) |

| (PWM_IDR2) Comparison 0 Match Interrupt Disable More... | |

| #define | PWM_IDR2_CMPM1 (0x1u << 9) |

| (PWM_IDR2) Comparison 1 Match Interrupt Disable More... | |

| #define | PWM_IDR2_CMPM2 (0x1u << 10) |

| (PWM_IDR2) Comparison 2 Match Interrupt Disable More... | |

| #define | PWM_IDR2_CMPM3 (0x1u << 11) |

| (PWM_IDR2) Comparison 3 Match Interrupt Disable More... | |

| #define | PWM_IDR2_CMPM4 (0x1u << 12) |

| (PWM_IDR2) Comparison 4 Match Interrupt Disable More... | |

| #define | PWM_IDR2_CMPM5 (0x1u << 13) |

| (PWM_IDR2) Comparison 5 Match Interrupt Disable More... | |

| #define | PWM_IDR2_CMPM6 (0x1u << 14) |

| (PWM_IDR2) Comparison 6 Match Interrupt Disable More... | |

| #define | PWM_IDR2_CMPM7 (0x1u << 15) |

| (PWM_IDR2) Comparison 7 Match Interrupt Disable More... | |

| #define | PWM_IDR2_CMPU0 (0x1u << 16) |

| (PWM_IDR2) Comparison 0 Update Interrupt Disable More... | |

| #define | PWM_IDR2_CMPU1 (0x1u << 17) |

| (PWM_IDR2) Comparison 1 Update Interrupt Disable More... | |

| #define | PWM_IDR2_CMPU2 (0x1u << 18) |

| (PWM_IDR2) Comparison 2 Update Interrupt Disable More... | |

| #define | PWM_IDR2_CMPU3 (0x1u << 19) |

| (PWM_IDR2) Comparison 3 Update Interrupt Disable More... | |

| #define | PWM_IDR2_CMPU4 (0x1u << 20) |

| (PWM_IDR2) Comparison 4 Update Interrupt Disable More... | |

| #define | PWM_IDR2_CMPU5 (0x1u << 21) |

| (PWM_IDR2) Comparison 5 Update Interrupt Disable More... | |

| #define | PWM_IDR2_CMPU6 (0x1u << 22) |

| (PWM_IDR2) Comparison 6 Update Interrupt Disable More... | |

| #define | PWM_IDR2_CMPU7 (0x1u << 23) |

| (PWM_IDR2) Comparison 7 Update Interrupt Disable More... | |

| #define | PWM_IDR2_UNRE (0x1u << 3) |

| (PWM_IDR2) Synchronous Channels Update Underrun Error Interrupt Disable More... | |

| #define | PWM_IDR2_WRDY (0x1u << 0) |

| (PWM_IDR2) Write Ready for Synchronous Channels Update Interrupt Disable More... | |

| #define | PWM_IER1_CHID0 (0x1u << 0) |

| (PWM_IER1) Counter Event on Channel 0 Interrupt Enable More... | |

| #define | PWM_IER1_CHID1 (0x1u << 1) |

| (PWM_IER1) Counter Event on Channel 1 Interrupt Enable More... | |

| #define | PWM_IER1_CHID2 (0x1u << 2) |

| (PWM_IER1) Counter Event on Channel 2 Interrupt Enable More... | |

| #define | PWM_IER1_CHID3 (0x1u << 3) |

| (PWM_IER1) Counter Event on Channel 3 Interrupt Enable More... | |

| #define | PWM_IER1_FCHID0 (0x1u << 16) |

| (PWM_IER1) Fault Protection Trigger on Channel 0 Interrupt Enable More... | |

| #define | PWM_IER1_FCHID1 (0x1u << 17) |

| (PWM_IER1) Fault Protection Trigger on Channel 1 Interrupt Enable More... | |

| #define | PWM_IER1_FCHID2 (0x1u << 18) |

| (PWM_IER1) Fault Protection Trigger on Channel 2 Interrupt Enable More... | |

| #define | PWM_IER1_FCHID3 (0x1u << 19) |

| (PWM_IER1) Fault Protection Trigger on Channel 3 Interrupt Enable More... | |

| #define | PWM_IER2_CMPM0 (0x1u << 8) |

| (PWM_IER2) Comparison 0 Match Interrupt Enable More... | |

| #define | PWM_IER2_CMPM1 (0x1u << 9) |

| (PWM_IER2) Comparison 1 Match Interrupt Enable More... | |

| #define | PWM_IER2_CMPM2 (0x1u << 10) |

| (PWM_IER2) Comparison 2 Match Interrupt Enable More... | |

| #define | PWM_IER2_CMPM3 (0x1u << 11) |

| (PWM_IER2) Comparison 3 Match Interrupt Enable More... | |

| #define | PWM_IER2_CMPM4 (0x1u << 12) |

| (PWM_IER2) Comparison 4 Match Interrupt Enable More... | |

| #define | PWM_IER2_CMPM5 (0x1u << 13) |

| (PWM_IER2) Comparison 5 Match Interrupt Enable More... | |

| #define | PWM_IER2_CMPM6 (0x1u << 14) |

| (PWM_IER2) Comparison 6 Match Interrupt Enable More... | |

| #define | PWM_IER2_CMPM7 (0x1u << 15) |

| (PWM_IER2) Comparison 7 Match Interrupt Enable More... | |

| #define | PWM_IER2_CMPU0 (0x1u << 16) |

| (PWM_IER2) Comparison 0 Update Interrupt Enable More... | |

| #define | PWM_IER2_CMPU1 (0x1u << 17) |

| (PWM_IER2) Comparison 1 Update Interrupt Enable More... | |

| #define | PWM_IER2_CMPU2 (0x1u << 18) |

| (PWM_IER2) Comparison 2 Update Interrupt Enable More... | |

| #define | PWM_IER2_CMPU3 (0x1u << 19) |

| (PWM_IER2) Comparison 3 Update Interrupt Enable More... | |

| #define | PWM_IER2_CMPU4 (0x1u << 20) |

| (PWM_IER2) Comparison 4 Update Interrupt Enable More... | |

| #define | PWM_IER2_CMPU5 (0x1u << 21) |

| (PWM_IER2) Comparison 5 Update Interrupt Enable More... | |

| #define | PWM_IER2_CMPU6 (0x1u << 22) |

| (PWM_IER2) Comparison 6 Update Interrupt Enable More... | |

| #define | PWM_IER2_CMPU7 (0x1u << 23) |

| (PWM_IER2) Comparison 7 Update Interrupt Enable More... | |

| #define | PWM_IER2_UNRE (0x1u << 3) |

| (PWM_IER2) Synchronous Channels Update Underrun Error Interrupt Enable More... | |

| #define | PWM_IER2_WRDY (0x1u << 0) |

| (PWM_IER2) Write Ready for Synchronous Channels Update Interrupt Enable More... | |

| #define | PWM_IMR1_CHID0 (0x1u << 0) |

| (PWM_IMR1) Counter Event on Channel 0 Interrupt Mask More... | |

| #define | PWM_IMR1_CHID1 (0x1u << 1) |

| (PWM_IMR1) Counter Event on Channel 1 Interrupt Mask More... | |

| #define | PWM_IMR1_CHID2 (0x1u << 2) |

| (PWM_IMR1) Counter Event on Channel 2 Interrupt Mask More... | |

| #define | PWM_IMR1_CHID3 (0x1u << 3) |

| (PWM_IMR1) Counter Event on Channel 3 Interrupt Mask More... | |

| #define | PWM_IMR1_FCHID0 (0x1u << 16) |

| (PWM_IMR1) Fault Protection Trigger on Channel 0 Interrupt Mask More... | |

| #define | PWM_IMR1_FCHID1 (0x1u << 17) |

| (PWM_IMR1) Fault Protection Trigger on Channel 1 Interrupt Mask More... | |

| #define | PWM_IMR1_FCHID2 (0x1u << 18) |

| (PWM_IMR1) Fault Protection Trigger on Channel 2 Interrupt Mask More... | |

| #define | PWM_IMR1_FCHID3 (0x1u << 19) |

| (PWM_IMR1) Fault Protection Trigger on Channel 3 Interrupt Mask More... | |

| #define | PWM_IMR2_CMPM0 (0x1u << 8) |

| (PWM_IMR2) Comparison 0 Match Interrupt Mask More... | |

| #define | PWM_IMR2_CMPM1 (0x1u << 9) |

| (PWM_IMR2) Comparison 1 Match Interrupt Mask More... | |

| #define | PWM_IMR2_CMPM2 (0x1u << 10) |

| (PWM_IMR2) Comparison 2 Match Interrupt Mask More... | |

| #define | PWM_IMR2_CMPM3 (0x1u << 11) |

| (PWM_IMR2) Comparison 3 Match Interrupt Mask More... | |

| #define | PWM_IMR2_CMPM4 (0x1u << 12) |

| (PWM_IMR2) Comparison 4 Match Interrupt Mask More... | |

| #define | PWM_IMR2_CMPM5 (0x1u << 13) |

| (PWM_IMR2) Comparison 5 Match Interrupt Mask More... | |

| #define | PWM_IMR2_CMPM6 (0x1u << 14) |

| (PWM_IMR2) Comparison 6 Match Interrupt Mask More... | |

| #define | PWM_IMR2_CMPM7 (0x1u << 15) |

| (PWM_IMR2) Comparison 7 Match Interrupt Mask More... | |

| #define | PWM_IMR2_CMPU0 (0x1u << 16) |

| (PWM_IMR2) Comparison 0 Update Interrupt Mask More... | |

| #define | PWM_IMR2_CMPU1 (0x1u << 17) |

| (PWM_IMR2) Comparison 1 Update Interrupt Mask More... | |

| #define | PWM_IMR2_CMPU2 (0x1u << 18) |

| (PWM_IMR2) Comparison 2 Update Interrupt Mask More... | |

| #define | PWM_IMR2_CMPU3 (0x1u << 19) |

| (PWM_IMR2) Comparison 3 Update Interrupt Mask More... | |

| #define | PWM_IMR2_CMPU4 (0x1u << 20) |

| (PWM_IMR2) Comparison 4 Update Interrupt Mask More... | |

| #define | PWM_IMR2_CMPU5 (0x1u << 21) |

| (PWM_IMR2) Comparison 5 Update Interrupt Mask More... | |

| #define | PWM_IMR2_CMPU6 (0x1u << 22) |

| (PWM_IMR2) Comparison 6 Update Interrupt Mask More... | |

| #define | PWM_IMR2_CMPU7 (0x1u << 23) |

| (PWM_IMR2) Comparison 7 Update Interrupt Mask More... | |

| #define | PWM_IMR2_UNRE (0x1u << 3) |

| (PWM_IMR2) Synchronous Channels Update Underrun Error Interrupt Mask More... | |

| #define | PWM_IMR2_WRDY (0x1u << 0) |

| (PWM_IMR2) Write Ready for Synchronous Channels Update Interrupt Mask More... | |

| #define | PWM_ISR1_CHID0 (0x1u << 0) |

| (PWM_ISR1) Counter Event on Channel 0 More... | |

| #define | PWM_ISR1_CHID1 (0x1u << 1) |

| (PWM_ISR1) Counter Event on Channel 1 More... | |

| #define | PWM_ISR1_CHID2 (0x1u << 2) |

| (PWM_ISR1) Counter Event on Channel 2 More... | |

| #define | PWM_ISR1_CHID3 (0x1u << 3) |

| (PWM_ISR1) Counter Event on Channel 3 More... | |

| #define | PWM_ISR1_FCHID0 (0x1u << 16) |

| (PWM_ISR1) Fault Protection Trigger on Channel 0 More... | |

| #define | PWM_ISR1_FCHID1 (0x1u << 17) |

| (PWM_ISR1) Fault Protection Trigger on Channel 1 More... | |

| #define | PWM_ISR1_FCHID2 (0x1u << 18) |

| (PWM_ISR1) Fault Protection Trigger on Channel 2 More... | |

| #define | PWM_ISR1_FCHID3 (0x1u << 19) |

| (PWM_ISR1) Fault Protection Trigger on Channel 3 More... | |

| #define | PWM_ISR2_CMPM0 (0x1u << 8) |

| (PWM_ISR2) Comparison 0 Match More... | |

| #define | PWM_ISR2_CMPM1 (0x1u << 9) |

| (PWM_ISR2) Comparison 1 Match More... | |

| #define | PWM_ISR2_CMPM2 (0x1u << 10) |

| (PWM_ISR2) Comparison 2 Match More... | |

| #define | PWM_ISR2_CMPM3 (0x1u << 11) |

| (PWM_ISR2) Comparison 3 Match More... | |

| #define | PWM_ISR2_CMPM4 (0x1u << 12) |

| (PWM_ISR2) Comparison 4 Match More... | |

| #define | PWM_ISR2_CMPM5 (0x1u << 13) |

| (PWM_ISR2) Comparison 5 Match More... | |

| #define | PWM_ISR2_CMPM6 (0x1u << 14) |

| (PWM_ISR2) Comparison 6 Match More... | |

| #define | PWM_ISR2_CMPM7 (0x1u << 15) |

| (PWM_ISR2) Comparison 7 Match More... | |

| #define | PWM_ISR2_CMPU0 (0x1u << 16) |

| (PWM_ISR2) Comparison 0 Update More... | |

| #define | PWM_ISR2_CMPU1 (0x1u << 17) |

| (PWM_ISR2) Comparison 1 Update More... | |

| #define | PWM_ISR2_CMPU2 (0x1u << 18) |

| (PWM_ISR2) Comparison 2 Update More... | |

| #define | PWM_ISR2_CMPU3 (0x1u << 19) |

| (PWM_ISR2) Comparison 3 Update More... | |

| #define | PWM_ISR2_CMPU4 (0x1u << 20) |

| (PWM_ISR2) Comparison 4 Update More... | |

| #define | PWM_ISR2_CMPU5 (0x1u << 21) |

| (PWM_ISR2) Comparison 5 Update More... | |

| #define | PWM_ISR2_CMPU6 (0x1u << 22) |

| (PWM_ISR2) Comparison 6 Update More... | |

| #define | PWM_ISR2_CMPU7 (0x1u << 23) |

| (PWM_ISR2) Comparison 7 Update More... | |

| #define | PWM_ISR2_UNRE (0x1u << 3) |

| (PWM_ISR2) Synchronous Channels Update Underrun Error More... | |

| #define | PWM_ISR2_WRDY (0x1u << 0) |

| (PWM_ISR2) Write Ready for Synchronous Channels Update More... | |

| #define | PWM_LEBR1_LEBDELAY(value) ((PWM_LEBR1_LEBDELAY_Msk & ((value) << PWM_LEBR1_LEBDELAY_Pos))) |

| #define | PWM_LEBR1_LEBDELAY_Msk (0x7fu << PWM_LEBR1_LEBDELAY_Pos) |

| (PWM_LEBR1) Leading-Edge Blanking Delay for TRGINx More... | |

| #define | PWM_LEBR1_LEBDELAY_Pos 0 |

| #define | PWM_LEBR1_PWMHFEN (0x1u << 18) |

| (PWM_LEBR1) PWMH Falling Edge Enable More... | |

| #define | PWM_LEBR1_PWMHREN (0x1u << 19) |

| (PWM_LEBR1) PWMH Rising Edge Enable More... | |

| #define | PWM_LEBR1_PWMLFEN (0x1u << 16) |

| (PWM_LEBR1) PWML Falling Edge Enable More... | |

| #define | PWM_LEBR1_PWMLREN (0x1u << 17) |

| (PWM_LEBR1) PWML Rising Edge Enable More... | |

| #define | PWM_LEBR2_LEBDELAY(value) ((PWM_LEBR2_LEBDELAY_Msk & ((value) << PWM_LEBR2_LEBDELAY_Pos))) |

| #define | PWM_LEBR2_LEBDELAY_Msk (0x7fu << PWM_LEBR2_LEBDELAY_Pos) |

| (PWM_LEBR2) Leading-Edge Blanking Delay for TRGINx More... | |

| #define | PWM_LEBR2_LEBDELAY_Pos 0 |

| #define | PWM_LEBR2_PWMHFEN (0x1u << 18) |

| (PWM_LEBR2) PWMH Falling Edge Enable More... | |

| #define | PWM_LEBR2_PWMHREN (0x1u << 19) |

| (PWM_LEBR2) PWMH Rising Edge Enable More... | |

| #define | PWM_LEBR2_PWMLFEN (0x1u << 16) |

| (PWM_LEBR2) PWML Falling Edge Enable More... | |

| #define | PWM_LEBR2_PWMLREN (0x1u << 17) |

| (PWM_LEBR2) PWML Rising Edge Enable More... | |

| #define | PWM_OOV_OOVH0 (0x1u << 0) |

| (PWM_OOV) Output Override Value for PWMH output of the channel 0 More... | |

| #define | PWM_OOV_OOVH1 (0x1u << 1) |

| (PWM_OOV) Output Override Value for PWMH output of the channel 1 More... | |

| #define | PWM_OOV_OOVH2 (0x1u << 2) |

| (PWM_OOV) Output Override Value for PWMH output of the channel 2 More... | |

| #define | PWM_OOV_OOVH3 (0x1u << 3) |

| (PWM_OOV) Output Override Value for PWMH output of the channel 3 More... | |

| #define | PWM_OOV_OOVL0 (0x1u << 16) |

| (PWM_OOV) Output Override Value for PWML output of the channel 0 More... | |

| #define | PWM_OOV_OOVL1 (0x1u << 17) |

| (PWM_OOV) Output Override Value for PWML output of the channel 1 More... | |

| #define | PWM_OOV_OOVL2 (0x1u << 18) |

| (PWM_OOV) Output Override Value for PWML output of the channel 2 More... | |

| #define | PWM_OOV_OOVL3 (0x1u << 19) |

| (PWM_OOV) Output Override Value for PWML output of the channel 3 More... | |

| #define | PWM_OS_OSH0 (0x1u << 0) |

| (PWM_OS) Output Selection for PWMH output of the channel 0 More... | |

| #define | PWM_OS_OSH1 (0x1u << 1) |

| (PWM_OS) Output Selection for PWMH output of the channel 1 More... | |

| #define | PWM_OS_OSH2 (0x1u << 2) |

| (PWM_OS) Output Selection for PWMH output of the channel 2 More... | |

| #define | PWM_OS_OSH3 (0x1u << 3) |

| (PWM_OS) Output Selection for PWMH output of the channel 3 More... | |

| #define | PWM_OS_OSL0 (0x1u << 16) |

| (PWM_OS) Output Selection for PWML output of the channel 0 More... | |

| #define | PWM_OS_OSL1 (0x1u << 17) |

| (PWM_OS) Output Selection for PWML output of the channel 1 More... | |

| #define | PWM_OS_OSL2 (0x1u << 18) |

| (PWM_OS) Output Selection for PWML output of the channel 2 More... | |

| #define | PWM_OS_OSL3 (0x1u << 19) |

| (PWM_OS) Output Selection for PWML output of the channel 3 More... | |

| #define | PWM_OSC_OSCH0 (0x1u << 0) |

| (PWM_OSC) Output Selection Clear for PWMH output of the channel 0 More... | |

| #define | PWM_OSC_OSCH1 (0x1u << 1) |

| (PWM_OSC) Output Selection Clear for PWMH output of the channel 1 More... | |

| #define | PWM_OSC_OSCH2 (0x1u << 2) |

| (PWM_OSC) Output Selection Clear for PWMH output of the channel 2 More... | |

| #define | PWM_OSC_OSCH3 (0x1u << 3) |

| (PWM_OSC) Output Selection Clear for PWMH output of the channel 3 More... | |

| #define | PWM_OSC_OSCL0 (0x1u << 16) |

| (PWM_OSC) Output Selection Clear for PWML output of the channel 0 More... | |

| #define | PWM_OSC_OSCL1 (0x1u << 17) |

| (PWM_OSC) Output Selection Clear for PWML output of the channel 1 More... | |

| #define | PWM_OSC_OSCL2 (0x1u << 18) |

| (PWM_OSC) Output Selection Clear for PWML output of the channel 2 More... | |

| #define | PWM_OSC_OSCL3 (0x1u << 19) |

| (PWM_OSC) Output Selection Clear for PWML output of the channel 3 More... | |

| #define | PWM_OSCUPD_OSCUPH0 (0x1u << 0) |

| (PWM_OSCUPD) Output Selection Clear for PWMH output of the channel 0 More... | |

| #define | PWM_OSCUPD_OSCUPH1 (0x1u << 1) |

| (PWM_OSCUPD) Output Selection Clear for PWMH output of the channel 1 More... | |

| #define | PWM_OSCUPD_OSCUPH2 (0x1u << 2) |

| (PWM_OSCUPD) Output Selection Clear for PWMH output of the channel 2 More... | |

| #define | PWM_OSCUPD_OSCUPH3 (0x1u << 3) |

| (PWM_OSCUPD) Output Selection Clear for PWMH output of the channel 3 More... | |

| #define | PWM_OSCUPD_OSCUPL0 (0x1u << 16) |

| (PWM_OSCUPD) Output Selection Clear for PWML output of the channel 0 More... | |

| #define | PWM_OSCUPD_OSCUPL1 (0x1u << 17) |

| (PWM_OSCUPD) Output Selection Clear for PWML output of the channel 1 More... | |

| #define | PWM_OSCUPD_OSCUPL2 (0x1u << 18) |

| (PWM_OSCUPD) Output Selection Clear for PWML output of the channel 2 More... | |

| #define | PWM_OSCUPD_OSCUPL3 (0x1u << 19) |

| (PWM_OSCUPD) Output Selection Clear for PWML output of the channel 3 More... | |

| #define | PWM_OSS_OSSH0 (0x1u << 0) |

| (PWM_OSS) Output Selection Set for PWMH output of the channel 0 More... | |

| #define | PWM_OSS_OSSH1 (0x1u << 1) |

| (PWM_OSS) Output Selection Set for PWMH output of the channel 1 More... | |

| #define | PWM_OSS_OSSH2 (0x1u << 2) |

| (PWM_OSS) Output Selection Set for PWMH output of the channel 2 More... | |

| #define | PWM_OSS_OSSH3 (0x1u << 3) |

| (PWM_OSS) Output Selection Set for PWMH output of the channel 3 More... | |

| #define | PWM_OSS_OSSL0 (0x1u << 16) |

| (PWM_OSS) Output Selection Set for PWML output of the channel 0 More... | |

| #define | PWM_OSS_OSSL1 (0x1u << 17) |

| (PWM_OSS) Output Selection Set for PWML output of the channel 1 More... | |

| #define | PWM_OSS_OSSL2 (0x1u << 18) |

| (PWM_OSS) Output Selection Set for PWML output of the channel 2 More... | |

| #define | PWM_OSS_OSSL3 (0x1u << 19) |

| (PWM_OSS) Output Selection Set for PWML output of the channel 3 More... | |

| #define | PWM_OSSUPD_OSSUPH0 (0x1u << 0) |

| (PWM_OSSUPD) Output Selection Set for PWMH output of the channel 0 More... | |

| #define | PWM_OSSUPD_OSSUPH1 (0x1u << 1) |

| (PWM_OSSUPD) Output Selection Set for PWMH output of the channel 1 More... | |

| #define | PWM_OSSUPD_OSSUPH2 (0x1u << 2) |

| (PWM_OSSUPD) Output Selection Set for PWMH output of the channel 2 More... | |

| #define | PWM_OSSUPD_OSSUPH3 (0x1u << 3) |

| (PWM_OSSUPD) Output Selection Set for PWMH output of the channel 3 More... | |

| #define | PWM_OSSUPD_OSSUPL0 (0x1u << 16) |

| (PWM_OSSUPD) Output Selection Set for PWML output of the channel 0 More... | |

| #define | PWM_OSSUPD_OSSUPL1 (0x1u << 17) |

| (PWM_OSSUPD) Output Selection Set for PWML output of the channel 1 More... | |

| #define | PWM_OSSUPD_OSSUPL2 (0x1u << 18) |

| (PWM_OSSUPD) Output Selection Set for PWML output of the channel 2 More... | |

| #define | PWM_OSSUPD_OSSUPL3 (0x1u << 19) |

| (PWM_OSSUPD) Output Selection Set for PWML output of the channel 3 More... | |

| #define | PWM_SCM_PTRCS(value) ((PWM_SCM_PTRCS_Msk & ((value) << PWM_SCM_PTRCS_Pos))) |

| #define | PWM_SCM_PTRCS_Msk (0x7u << PWM_SCM_PTRCS_Pos) |

| (PWM_SCM) DMA Transfer Request Comparison Selection More... | |

| #define | PWM_SCM_PTRCS_Pos 21 |

| #define | PWM_SCM_PTRM (0x1u << 20) |

| (PWM_SCM) DMA Transfer Request Mode More... | |

| #define | PWM_SCM_SYNC0 (0x1u << 0) |

| (PWM_SCM) Synchronous Channel 0 More... | |

| #define | PWM_SCM_SYNC1 (0x1u << 1) |

| (PWM_SCM) Synchronous Channel 1 More... | |

| #define | PWM_SCM_SYNC2 (0x1u << 2) |

| (PWM_SCM) Synchronous Channel 2 More... | |

| #define | PWM_SCM_SYNC3 (0x1u << 3) |

| (PWM_SCM) Synchronous Channel 3 More... | |

| #define | PWM_SCM_UPDM(value) ((PWM_SCM_UPDM_Msk & ((value) << PWM_SCM_UPDM_Pos))) |

| #define | PWM_SCM_UPDM_MODE0 (0x0u << 16) |

| (PWM_SCM) Manual write of double buffer registers and manual update of synchronous channels More... | |

| #define | PWM_SCM_UPDM_MODE1 (0x1u << 16) |

| (PWM_SCM) Manual write of double buffer registers and automatic update of synchronous channels More... | |

| #define | PWM_SCM_UPDM_MODE2 (0x2u << 16) |

| (PWM_SCM) Automatic write of duty-cycle update registers by the DMA and automatic update of synchronous channels More... | |

| #define | PWM_SCM_UPDM_Msk (0x3u << PWM_SCM_UPDM_Pos) |

| (PWM_SCM) Synchronous Channels Update Mode More... | |

| #define | PWM_SCM_UPDM_Pos 16 |

| #define | PWM_SCUC_UPDULOCK (0x1u << 0) |

| (PWM_SCUC) Synchronous Channels Update Unlock More... | |

| #define | PWM_SCUP_UPR(value) ((PWM_SCUP_UPR_Msk & ((value) << PWM_SCUP_UPR_Pos))) |

| #define | PWM_SCUP_UPR_Msk (0xfu << PWM_SCUP_UPR_Pos) |

| (PWM_SCUP) Update Period More... | |

| #define | PWM_SCUP_UPR_Pos 0 |

| #define | PWM_SCUP_UPRCNT(value) ((PWM_SCUP_UPRCNT_Msk & ((value) << PWM_SCUP_UPRCNT_Pos))) |

| #define | PWM_SCUP_UPRCNT_Msk (0xfu << PWM_SCUP_UPRCNT_Pos) |

| (PWM_SCUP) Update Period Counter More... | |

| #define | PWM_SCUP_UPRCNT_Pos 4 |

| #define | PWM_SCUPUPD_UPRUPD(value) ((PWM_SCUPUPD_UPRUPD_Msk & ((value) << PWM_SCUPUPD_UPRUPD_Pos))) |

| #define | PWM_SCUPUPD_UPRUPD_Msk (0xfu << PWM_SCUPUPD_UPRUPD_Pos) |

| (PWM_SCUPUPD) Update Period Update More... | |

| #define | PWM_SCUPUPD_UPRUPD_Pos 0 |

| #define | PWM_SMMR_DOWN0 (0x1u << 16) |

| (PWM_SMMR) DOWN Count More... | |

| #define | PWM_SMMR_DOWN1 (0x1u << 17) |

| (PWM_SMMR) DOWN Count More... | |

| #define | PWM_SMMR_GCEN0 (0x1u << 0) |

| (PWM_SMMR) Gray Count ENable More... | |

| #define | PWM_SMMR_GCEN1 (0x1u << 1) |

| (PWM_SMMR) Gray Count ENable More... | |

| #define | PWM_SR_CHID0 (0x1u << 0) |

| (PWM_SR) Channel ID More... | |

| #define | PWM_SR_CHID1 (0x1u << 1) |

| (PWM_SR) Channel ID More... | |

| #define | PWM_SR_CHID2 (0x1u << 2) |

| (PWM_SR) Channel ID More... | |

| #define | PWM_SR_CHID3 (0x1u << 3) |

| (PWM_SR) Channel ID More... | |

| #define | PWM_SSPR_SPRD(value) ((PWM_SSPR_SPRD_Msk & ((value) << PWM_SSPR_SPRD_Pos))) |

| #define | PWM_SSPR_SPRD_Msk (0xffffffu << PWM_SSPR_SPRD_Pos) |

| (PWM_SSPR) Spread Spectrum Limit Value More... | |

| #define | PWM_SSPR_SPRD_Pos 0 |

| #define | PWM_SSPR_SPRDM (0x1u << 24) |

| (PWM_SSPR) Spread Spectrum Counter Mode More... | |

| #define | PWM_SSPUP_SPRDUP(value) ((PWM_SSPUP_SPRDUP_Msk & ((value) << PWM_SSPUP_SPRDUP_Pos))) |

| #define | PWM_SSPUP_SPRDUP_Msk (0xffffffu << PWM_SSPUP_SPRDUP_Pos) |

| (PWM_SSPUP) Spread Spectrum Limit Value Update More... | |

| #define | PWM_SSPUP_SPRDUP_Pos 0 |

| #define | PWM_VERSION_MFN_Msk (0x7u << PWM_VERSION_MFN_Pos) |

| (PWM_VERSION) Metal Fix Number More... | |

| #define | PWM_VERSION_MFN_Pos 16 |

| #define | PWM_VERSION_VERSION_Msk (0xfffu << PWM_VERSION_VERSION_Pos) |

| (PWM_VERSION) Version of the Hardware Module More... | |

| #define | PWM_VERSION_VERSION_Pos 0 |

| #define | PWM_WPCR_WPCMD(value) ((PWM_WPCR_WPCMD_Msk & ((value) << PWM_WPCR_WPCMD_Pos))) |

| #define | PWM_WPCR_WPCMD_DISABLE_SW_PROT (0x0u << 0) |

| (PWM_WPCR) Disables the software write protection of the register groups of which the bit WPRGx is at '1'. More... | |

| #define | PWM_WPCR_WPCMD_ENABLE_HW_PROT (0x2u << 0) |

| (PWM_WPCR) Enables the hardware write protection of the register groups of which the bit WPRGx is at '1'. Only a hardware reset of the PWM controller can disable the hardware write protection. Moreover, to meet security requirements, the PIO lines associated with the PWM can not be configured through the PIO interface. More... | |

| #define | PWM_WPCR_WPCMD_ENABLE_SW_PROT (0x1u << 0) |

| (PWM_WPCR) Enables the software write protection of the register groups of which the bit WPRGx is at '1'. More... | |

| #define | PWM_WPCR_WPCMD_Msk (0x3u << PWM_WPCR_WPCMD_Pos) |

| (PWM_WPCR) Write Protection Command More... | |

| #define | PWM_WPCR_WPCMD_Pos 0 |

| #define | PWM_WPCR_WPKEY(value) ((PWM_WPCR_WPKEY_Msk & ((value) << PWM_WPCR_WPKEY_Pos))) |

| #define | PWM_WPCR_WPKEY_Msk (0xffffffu << PWM_WPCR_WPKEY_Pos) |

| (PWM_WPCR) Write Protection Key More... | |

| #define | PWM_WPCR_WPKEY_PASSWD (0x50574Du << 8) |

| (PWM_WPCR) Writing any other value in this field aborts the write operation of the WPCMD field.Always reads as 0 More... | |

| #define | PWM_WPCR_WPKEY_Pos 8 |

| #define | PWM_WPCR_WPRG0 (0x1u << 2) |

| (PWM_WPCR) Write Protection Register Group 0 More... | |

| #define | PWM_WPCR_WPRG1 (0x1u << 3) |

| (PWM_WPCR) Write Protection Register Group 1 More... | |

| #define | PWM_WPCR_WPRG2 (0x1u << 4) |

| (PWM_WPCR) Write Protection Register Group 2 More... | |

| #define | PWM_WPCR_WPRG3 (0x1u << 5) |

| (PWM_WPCR) Write Protection Register Group 3 More... | |

| #define | PWM_WPCR_WPRG4 (0x1u << 6) |

| (PWM_WPCR) Write Protection Register Group 4 More... | |

| #define | PWM_WPCR_WPRG5 (0x1u << 7) |

| (PWM_WPCR) Write Protection Register Group 5 More... | |

| #define | PWM_WPSR_WPHWS0 (0x1u << 8) |

| (PWM_WPSR) Write Protect HW Status More... | |

| #define | PWM_WPSR_WPHWS1 (0x1u << 9) |

| (PWM_WPSR) Write Protect HW Status More... | |

| #define | PWM_WPSR_WPHWS2 (0x1u << 10) |

| (PWM_WPSR) Write Protect HW Status More... | |

| #define | PWM_WPSR_WPHWS3 (0x1u << 11) |

| (PWM_WPSR) Write Protect HW Status More... | |

| #define | PWM_WPSR_WPHWS4 (0x1u << 12) |

| (PWM_WPSR) Write Protect HW Status More... | |

| #define | PWM_WPSR_WPHWS5 (0x1u << 13) |

| (PWM_WPSR) Write Protect HW Status More... | |

| #define | PWM_WPSR_WPSWS0 (0x1u << 0) |

| (PWM_WPSR) Write Protect SW Status More... | |

| #define | PWM_WPSR_WPSWS1 (0x1u << 1) |

| (PWM_WPSR) Write Protect SW Status More... | |

| #define | PWM_WPSR_WPSWS2 (0x1u << 2) |

| (PWM_WPSR) Write Protect SW Status More... | |

| #define | PWM_WPSR_WPSWS3 (0x1u << 3) |

| (PWM_WPSR) Write Protect SW Status More... | |

| #define | PWM_WPSR_WPSWS4 (0x1u << 4) |

| (PWM_WPSR) Write Protect SW Status More... | |

| #define | PWM_WPSR_WPSWS5 (0x1u << 5) |

| (PWM_WPSR) Write Protect SW Status More... | |

| #define | PWM_WPSR_WPVS (0x1u << 7) |

| (PWM_WPSR) Write Protect Violation Status More... | |

| #define | PWM_WPSR_WPVSRC_Msk (0xffffu << PWM_WPSR_WPVSRC_Pos) |

| (PWM_WPSR) Write Protect Violation Source More... | |

| #define | PWM_WPSR_WPVSRC_Pos 16 |

| #define | PWMCH_NUM_NUMBER 4 |

| #define | PWMCMP_NUMBER 8 |

| Pwm hardware registers. More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file pwm.h.