Go to the source code of this file.

Macros | |

| #define | REG_SSC_CMR (*(__IO uint32_t*)0x40004004U) |

| (SSC) Clock Mode Register More... | |

| #define | REG_SSC_CR (*(__O uint32_t*)0x40004000U) |

| (SSC) Control Register More... | |

| #define | REG_SSC_IDR (*(__O uint32_t*)0x40004048U) |

| (SSC) Interrupt Disable Register More... | |

| #define | REG_SSC_IER (*(__O uint32_t*)0x40004044U) |

| (SSC) Interrupt Enable Register More... | |

| #define | REG_SSC_IMR (*(__I uint32_t*)0x4000404CU) |

| (SSC) Interrupt Mask Register More... | |

| #define | REG_SSC_RC0R (*(__IO uint32_t*)0x40004038U) |

| (SSC) Receive Compare 0 Register More... | |

| #define | REG_SSC_RC1R (*(__IO uint32_t*)0x4000403CU) |

| (SSC) Receive Compare 1 Register More... | |

| #define | REG_SSC_RCMR (*(__IO uint32_t*)0x40004010U) |

| (SSC) Receive Clock Mode Register More... | |

| #define | REG_SSC_RFMR (*(__IO uint32_t*)0x40004014U) |

| (SSC) Receive Frame Mode Register More... | |

| #define | REG_SSC_RHR (*(__I uint32_t*)0x40004020U) |

| (SSC) Receive Holding Register More... | |

| #define | REG_SSC_RSHR (*(__I uint32_t*)0x40004030U) |

| (SSC) Receive Sync. Holding Register More... | |

| #define | REG_SSC_SR (*(__I uint32_t*)0x40004040U) |

| (SSC) Status Register More... | |

| #define | REG_SSC_TCMR (*(__IO uint32_t*)0x40004018U) |

| (SSC) Transmit Clock Mode Register More... | |

| #define | REG_SSC_TFMR (*(__IO uint32_t*)0x4000401CU) |

| (SSC) Transmit Frame Mode Register More... | |

| #define | REG_SSC_THR (*(__O uint32_t*)0x40004024U) |

| (SSC) Transmit Holding Register More... | |

| #define | REG_SSC_TSHR (*(__IO uint32_t*)0x40004034U) |

| (SSC) Transmit Sync. Holding Register More... | |

| #define | REG_SSC_VERSION (*(__I uint32_t*)0x400040FCU) |

| (SSC) Version Register More... | |

| #define | REG_SSC_WPMR (*(__IO uint32_t*)0x400040E4U) |

| (SSC) Write Protection Mode Register More... | |

| #define | REG_SSC_WPSR (*(__I uint32_t*)0x400040E8U) |

| (SSC) Write Protection Status Register More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

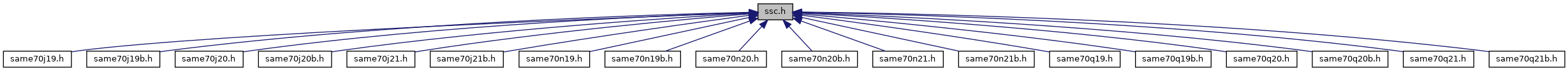

Definition in file instance/ssc.h.

Macro Definition Documentation

◆ REG_SSC_CMR

| #define REG_SSC_CMR (*(__IO uint32_t*)0x40004004U) |

(SSC) Clock Mode Register

Definition at line 61 of file instance/ssc.h.

◆ REG_SSC_CR

| #define REG_SSC_CR (*(__O uint32_t*)0x40004000U) |

(SSC) Control Register

Definition at line 60 of file instance/ssc.h.

◆ REG_SSC_IDR

| #define REG_SSC_IDR (*(__O uint32_t*)0x40004048U) |

(SSC) Interrupt Disable Register

Definition at line 74 of file instance/ssc.h.

◆ REG_SSC_IER

| #define REG_SSC_IER (*(__O uint32_t*)0x40004044U) |

(SSC) Interrupt Enable Register

Definition at line 73 of file instance/ssc.h.

◆ REG_SSC_IMR

| #define REG_SSC_IMR (*(__I uint32_t*)0x4000404CU) |

(SSC) Interrupt Mask Register

Definition at line 75 of file instance/ssc.h.

◆ REG_SSC_RC0R

| #define REG_SSC_RC0R (*(__IO uint32_t*)0x40004038U) |

(SSC) Receive Compare 0 Register

Definition at line 70 of file instance/ssc.h.

◆ REG_SSC_RC1R

| #define REG_SSC_RC1R (*(__IO uint32_t*)0x4000403CU) |

(SSC) Receive Compare 1 Register

Definition at line 71 of file instance/ssc.h.

◆ REG_SSC_RCMR

| #define REG_SSC_RCMR (*(__IO uint32_t*)0x40004010U) |

(SSC) Receive Clock Mode Register

Definition at line 62 of file instance/ssc.h.

◆ REG_SSC_RFMR

| #define REG_SSC_RFMR (*(__IO uint32_t*)0x40004014U) |

(SSC) Receive Frame Mode Register

Definition at line 63 of file instance/ssc.h.

◆ REG_SSC_RHR

| #define REG_SSC_RHR (*(__I uint32_t*)0x40004020U) |

(SSC) Receive Holding Register

Definition at line 66 of file instance/ssc.h.

◆ REG_SSC_RSHR

| #define REG_SSC_RSHR (*(__I uint32_t*)0x40004030U) |

(SSC) Receive Sync. Holding Register

Definition at line 68 of file instance/ssc.h.

◆ REG_SSC_SR

| #define REG_SSC_SR (*(__I uint32_t*)0x40004040U) |

(SSC) Status Register

Definition at line 72 of file instance/ssc.h.

◆ REG_SSC_TCMR

| #define REG_SSC_TCMR (*(__IO uint32_t*)0x40004018U) |

(SSC) Transmit Clock Mode Register

Definition at line 64 of file instance/ssc.h.

◆ REG_SSC_TFMR

| #define REG_SSC_TFMR (*(__IO uint32_t*)0x4000401CU) |

(SSC) Transmit Frame Mode Register

Definition at line 65 of file instance/ssc.h.

◆ REG_SSC_THR

| #define REG_SSC_THR (*(__O uint32_t*)0x40004024U) |

(SSC) Transmit Holding Register

Definition at line 67 of file instance/ssc.h.

◆ REG_SSC_TSHR

| #define REG_SSC_TSHR (*(__IO uint32_t*)0x40004034U) |

(SSC) Transmit Sync. Holding Register

Definition at line 69 of file instance/ssc.h.

◆ REG_SSC_VERSION

| #define REG_SSC_VERSION (*(__I uint32_t*)0x400040FCU) |

(SSC) Version Register

Definition at line 78 of file instance/ssc.h.

◆ REG_SSC_WPMR

| #define REG_SSC_WPMR (*(__IO uint32_t*)0x400040E4U) |

(SSC) Write Protection Mode Register

Definition at line 76 of file instance/ssc.h.

◆ REG_SSC_WPSR

| #define REG_SSC_WPSR (*(__I uint32_t*)0x400040E8U) |

(SSC) Write Protection Status Register

Definition at line 77 of file instance/ssc.h.