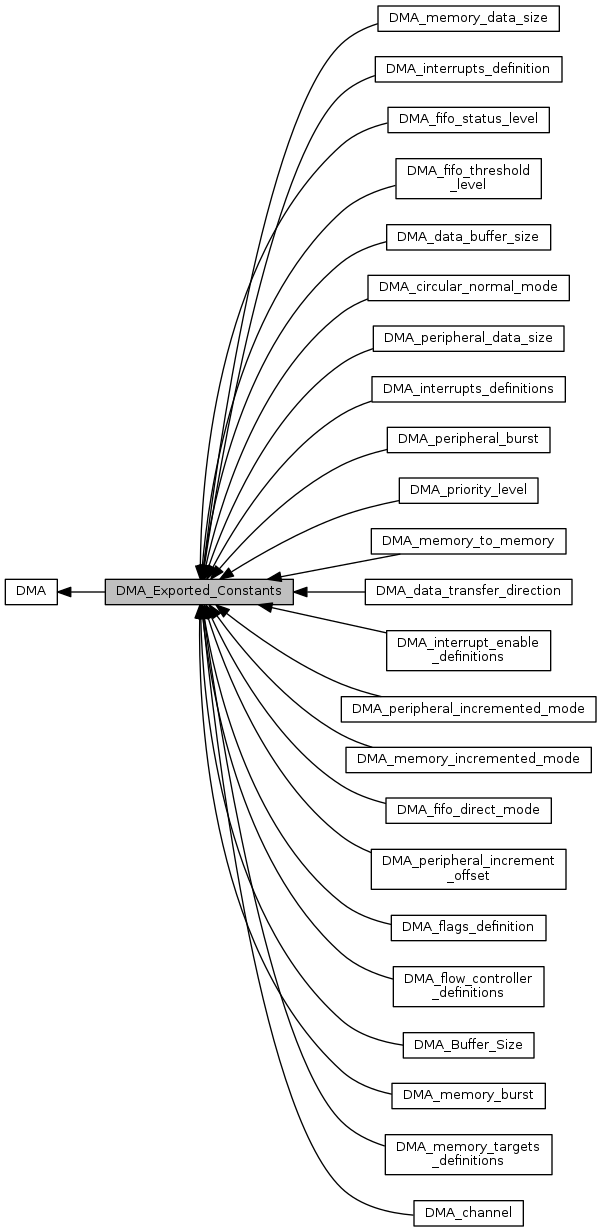

Collaboration diagram for DMA_Exported_Constants:

|

Macros | |

| #define | IS_DMA_ALL_CONTROLLER(CONTROLLER) |

| #define | IS_DMA_ALL_PERIPH(PERIPH) |

| #define | IS_DMA_ALL_PERIPH(PERIPH) |

| #define | IS_DMA_ALL_PERIPH(PERIPH) |

Detailed Description

Macro Definition Documentation

| #define IS_DMA_ALL_CONTROLLER | ( | CONTROLLER | ) |

Value:

Definition at line 135 of file stm32f4xx_dma.h.

| #define IS_DMA_ALL_PERIPH | ( | PERIPH | ) |

Value:

(((PERIPH) == DMA1_Channel1) || \

((PERIPH) == DMA1_Channel2) || \

((PERIPH) == DMA1_Channel3) || \

((PERIPH) == DMA1_Channel4) || \

((PERIPH) == DMA1_Channel5) || \

((PERIPH) == DMA1_Channel6) || \

((PERIPH) == DMA1_Channel7) || \

((PERIPH) == DMA2_Channel1) || \

((PERIPH) == DMA2_Channel2) || \

((PERIPH) == DMA2_Channel3) || \

((PERIPH) == DMA2_Channel4) || \

((PERIPH) == DMA2_Channel5))

Definition at line 95 of file stm32f10x_dma.h.

| #define IS_DMA_ALL_PERIPH | ( | PERIPH | ) |

Value:

(((PERIPH) == DMA1_Channel1) || \

((PERIPH) == DMA1_Channel2) || \

((PERIPH) == DMA1_Channel3) || \

((PERIPH) == DMA1_Channel4) || \

((PERIPH) == DMA1_Channel5) || \

((PERIPH) == DMA1_Channel6) || \

((PERIPH) == DMA1_Channel7) || \

((PERIPH) == DMA2_Channel1) || \

((PERIPH) == DMA2_Channel2) || \

((PERIPH) == DMA2_Channel3) || \

((PERIPH) == DMA2_Channel4) || \

((PERIPH) == DMA2_Channel5))

Definition at line 96 of file stm32f30x_dma.h.

| #define IS_DMA_ALL_PERIPH | ( | PERIPH | ) |

Value:

(((PERIPH) == DMA1_Stream0) || \

((PERIPH) == DMA1_Stream1) || \

((PERIPH) == DMA1_Stream2) || \

((PERIPH) == DMA1_Stream3) || \

((PERIPH) == DMA1_Stream4) || \

((PERIPH) == DMA1_Stream5) || \

((PERIPH) == DMA1_Stream6) || \

((PERIPH) == DMA1_Stream7) || \

((PERIPH) == DMA2_Stream0) || \

((PERIPH) == DMA2_Stream1) || \

((PERIPH) == DMA2_Stream2) || \

((PERIPH) == DMA2_Stream3) || \

((PERIPH) == DMA2_Stream4) || \

((PERIPH) == DMA2_Stream5) || \

((PERIPH) == DMA2_Stream6) || \

((PERIPH) == DMA2_Stream7))

Definition at line 118 of file stm32f4xx_dma.h.