VL53L1 Register Map definitions. More...

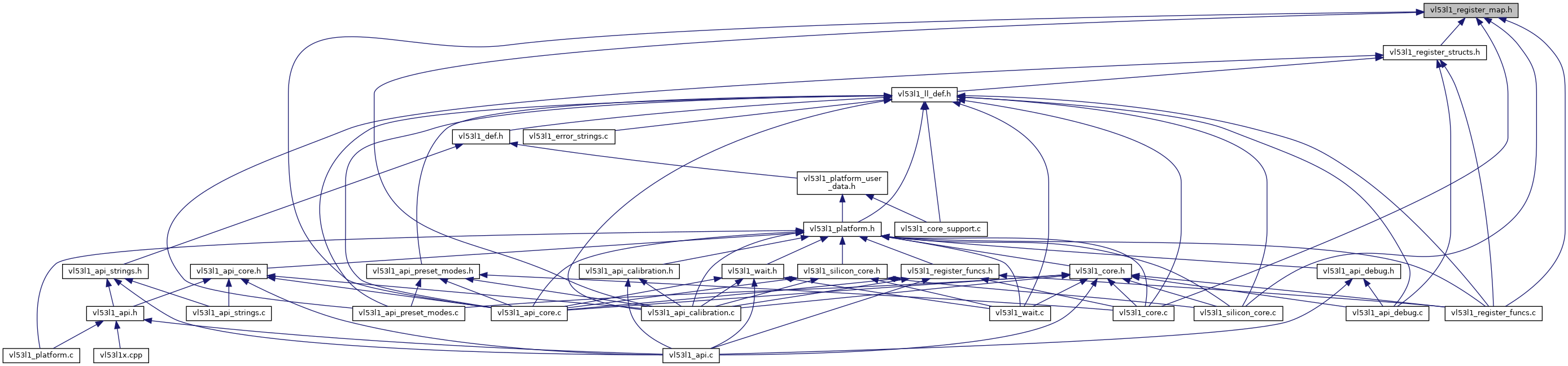

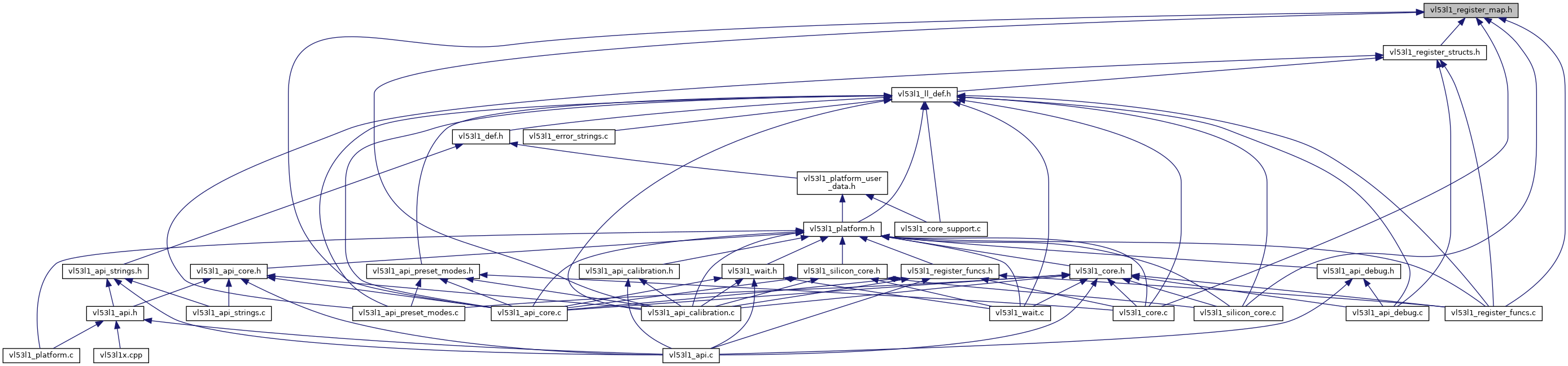

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Detailed Description

VL53L1 Register Map definitions.

Definition in file vl53l1_register_map.h.

VL53L1 Register Map definitions. More...

Go to the source code of this file.

VL53L1 Register Map definitions.

Definition in file vl53l1_register_map.h.