Header file of SMBUS HAL module. More...

#include "stm32f7xx_hal_def.h"

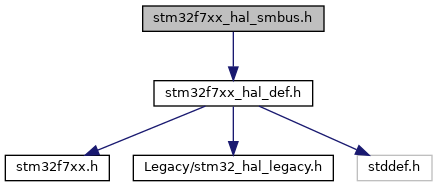

Include dependency graph for stm32f7xx_hal_smbus.h:

Go to the source code of this file.

Classes | |

| struct | __SMBUS_HandleTypeDef |

| SMBUS handle Structure definition. More... | |

| struct | SMBUS_InitTypeDef |

| SMBUS Configuration Structure definition. More... | |

Macros | |

| #define | __HAL_SMBUS_CLEAR_FLAG(__HANDLE__, __FLAG__) ((__HANDLE__)->Instance->ICR = (__FLAG__)) |

| Clear the SMBUS pending flags which are cleared by writing 1 in a specific bit. More... | |

| #define | __HAL_SMBUS_DISABLE(__HANDLE__) (CLEAR_BIT((__HANDLE__)->Instance->CR1, I2C_CR1_PE)) |

| Disable the specified SMBUS peripheral. More... | |

| #define | __HAL_SMBUS_DISABLE_IT(__HANDLE__, __INTERRUPT__) ((__HANDLE__)->Instance->CR1 &= (~(__INTERRUPT__))) |

| Disable the specified SMBUS interrupts. More... | |

| #define | __HAL_SMBUS_ENABLE(__HANDLE__) (SET_BIT((__HANDLE__)->Instance->CR1, I2C_CR1_PE)) |

| Enable the specified SMBUS peripheral. More... | |

| #define | __HAL_SMBUS_ENABLE_IT(__HANDLE__, __INTERRUPT__) ((__HANDLE__)->Instance->CR1 |= (__INTERRUPT__)) |

| Enable the specified SMBUS interrupts. More... | |

| #define | __HAL_SMBUS_GENERATE_NACK(__HANDLE__) (SET_BIT((__HANDLE__)->Instance->CR2, I2C_CR2_NACK)) |

| Generate a Non-Acknowledge SMBUS peripheral in Slave mode. More... | |

| #define | __HAL_SMBUS_GET_FLAG(__HANDLE__, __FLAG__) (((((__HANDLE__)->Instance->ISR) & ((__FLAG__) & SMBUS_FLAG_MASK)) == ((__FLAG__) & SMBUS_FLAG_MASK)) ? SET : RESET) |

| #define | __HAL_SMBUS_GET_IT_SOURCE(__HANDLE__, __INTERRUPT__) ((((__HANDLE__)->Instance->CR1 & (__INTERRUPT__)) == (__INTERRUPT__)) ? SET : RESET) |

| Check whether the specified SMBUS interrupt source is enabled or not. More... | |

| #define | __HAL_SMBUS_RESET_HANDLE_STATE(__HANDLE__) ((__HANDLE__)->State = HAL_SMBUS_STATE_RESET) |

| Reset SMBUS handle state. More... | |

| #define | HAL_SMBUS_ERROR_ACKF (0x00000004U) |

| #define | HAL_SMBUS_ERROR_ALERT (0x00000040U) |

| #define | HAL_SMBUS_ERROR_ARLO (0x00000002U) |

| #define | HAL_SMBUS_ERROR_BERR (0x00000001U) |

| #define | HAL_SMBUS_ERROR_BUSTIMEOUT (0x00000020U) |

| #define | HAL_SMBUS_ERROR_HALTIMEOUT (0x00000010U) |

| #define | HAL_SMBUS_ERROR_INVALID_PARAM (0x00000200U) |

| #define | HAL_SMBUS_ERROR_NONE (0x00000000U) |

| #define | HAL_SMBUS_ERROR_OVR (0x00000008U) |

| #define | HAL_SMBUS_ERROR_PECERR (0x00000080U) |

| #define | HAL_SMBUS_STATE_BUSY (0x00000002U) |

| #define | HAL_SMBUS_STATE_ERROR (0x00000004U) |

| #define | HAL_SMBUS_STATE_LISTEN (0x00000008U) |

| #define | HAL_SMBUS_STATE_MASTER_BUSY_RX (0x00000022U) |

| #define | HAL_SMBUS_STATE_MASTER_BUSY_TX (0x00000012U) |

| #define | HAL_SMBUS_STATE_READY (0x00000001U) |

| #define | HAL_SMBUS_STATE_RESET (0x00000000U) |

| #define | HAL_SMBUS_STATE_SLAVE_BUSY_RX (0x00000042U) |

| #define | HAL_SMBUS_STATE_SLAVE_BUSY_TX (0x00000032U) |

| #define | HAL_SMBUS_STATE_TIMEOUT (0x00000003U) |

| #define | IS_SMBUS_ADDRESSING_MODE(MODE) |

| #define | IS_SMBUS_ANALOG_FILTER(FILTER) |

| #define | IS_SMBUS_DIGITAL_FILTER(FILTER) ((FILTER) <= 0x0000000FU) |

| #define | IS_SMBUS_DUAL_ADDRESS(ADDRESS) |

| #define | IS_SMBUS_GENERAL_CALL(CALL) |

| #define | IS_SMBUS_NO_STRETCH(STRETCH) |

| #define | IS_SMBUS_OWN_ADDRESS1(ADDRESS1) ((ADDRESS1) <= 0x000003FFU) |

| #define | IS_SMBUS_OWN_ADDRESS2(ADDRESS2) ((ADDRESS2) <= (uint16_t)0x00FFU) |

| #define | IS_SMBUS_OWN_ADDRESS2_MASK(MASK) |

| #define | IS_SMBUS_PEC(PEC) |

| #define | IS_SMBUS_PERIPHERAL_MODE(MODE) |

| #define | IS_SMBUS_TRANSFER_MODE(MODE) |

| #define | IS_SMBUS_TRANSFER_OPTIONS_REQUEST(REQUEST) |

| #define | IS_SMBUS_TRANSFER_OTHER_OPTIONS_REQUEST(REQUEST) |

| #define | IS_SMBUS_TRANSFER_REQUEST(REQUEST) |

| #define | SMBUS_ADDRESSINGMODE_10BIT (0x00000002U) |

| #define | SMBUS_ADDRESSINGMODE_7BIT (0x00000001U) |

| #define | SMBUS_ANALOGFILTER_DISABLE I2C_CR1_ANFOFF |

| #define | SMBUS_ANALOGFILTER_ENABLE (0x00000000U) |

| #define | SMBUS_AUTOEND_MODE I2C_CR2_AUTOEND |

| #define | SMBUS_CHECK_FLAG(__ISR__, __FLAG__) ((((__ISR__) & ((__FLAG__) & SMBUS_FLAG_MASK)) == ((__FLAG__) & SMBUS_FLAG_MASK)) ? SET : RESET) |

| #define | SMBUS_CHECK_IT_SOURCE(__CR1__, __IT__) ((((__CR1__) & (__IT__)) == (__IT__)) ? SET : RESET) |

| #define | SMBUS_DUALADDRESS_DISABLE (0x00000000U) |

| #define | SMBUS_DUALADDRESS_ENABLE I2C_OAR2_OA2EN |

| #define | SMBUS_FIRST_AND_LAST_FRAME_NO_PEC SMBUS_AUTOEND_MODE |

| #define | SMBUS_FIRST_AND_LAST_FRAME_WITH_PEC ((uint32_t)(SMBUS_AUTOEND_MODE | SMBUS_SENDPEC_MODE)) |

| #define | SMBUS_FIRST_FRAME SMBUS_SOFTEND_MODE |

| #define | SMBUS_FLAG_ADDR I2C_ISR_ADDR |

| #define | SMBUS_FLAG_AF I2C_ISR_NACKF |

| #define | SMBUS_FLAG_ALERT I2C_ISR_ALERT |

| #define | SMBUS_FLAG_ARLO I2C_ISR_ARLO |

| #define | SMBUS_FLAG_BERR I2C_ISR_BERR |

| #define | SMBUS_FLAG_BUSY I2C_ISR_BUSY |

| #define | SMBUS_FLAG_DIR I2C_ISR_DIR |

| #define | SMBUS_FLAG_MASK (0x0001FFFFU) |

| Check whether the specified SMBUS flag is set or not. More... | |

| #define | SMBUS_FLAG_OVR I2C_ISR_OVR |

| #define | SMBUS_FLAG_PECERR I2C_ISR_PECERR |

| #define | SMBUS_FLAG_RXNE I2C_ISR_RXNE |

| #define | SMBUS_FLAG_STOPF I2C_ISR_STOPF |

| #define | SMBUS_FLAG_TC I2C_ISR_TC |

| #define | SMBUS_FLAG_TCR I2C_ISR_TCR |

| #define | SMBUS_FLAG_TIMEOUT I2C_ISR_TIMEOUT |

| #define | SMBUS_FLAG_TXE I2C_ISR_TXE |

| #define | SMBUS_FLAG_TXIS I2C_ISR_TXIS |

| #define | SMBUS_GENERALCALL_DISABLE (0x00000000U) |

| #define | SMBUS_GENERALCALL_ENABLE I2C_CR1_GCEN |

| #define | SMBUS_GENERATE_START(__ADDMODE__, __ADDRESS__) |

| #define | SMBUS_GENERATE_START_READ (uint32_t)(0x80000000U | I2C_CR2_START | I2C_CR2_RD_WRN) |

| #define | SMBUS_GENERATE_START_WRITE (uint32_t)(0x80000000U | I2C_CR2_START) |

| #define | SMBUS_GENERATE_STOP (uint32_t)(0x80000000U | I2C_CR2_STOP) |

| #define | SMBUS_GET_ADDR_MATCH(__HANDLE__) (((__HANDLE__)->Instance->ISR & I2C_ISR_ADDCODE) >> 17U) |

| #define | SMBUS_GET_ALERT_ENABLED(__HANDLE__) ((__HANDLE__)->Instance->CR1 & I2C_CR1_ALERTEN) |

| #define | SMBUS_GET_DIR(__HANDLE__) (((__HANDLE__)->Instance->ISR & I2C_ISR_DIR) >> 16U) |

| #define | SMBUS_GET_PEC_MODE(__HANDLE__) ((__HANDLE__)->Instance->CR2 & I2C_CR2_PECBYTE) |

| #define | SMBUS_GET_STOP_MODE(__HANDLE__) ((__HANDLE__)->Instance->CR2 & I2C_CR2_AUTOEND) |

| #define | SMBUS_IT_ADDR (SMBUS_IT_ADDRI | SMBUS_IT_STOPI | SMBUS_IT_NACKI) |

| #define | SMBUS_IT_ADDRI I2C_CR1_ADDRIE |

| #define | SMBUS_IT_ALERT (SMBUS_IT_ERRI) |

| #define | SMBUS_IT_ERRI I2C_CR1_ERRIE |

| #define | SMBUS_IT_NACKI I2C_CR1_NACKIE |

| #define | SMBUS_IT_RX (SMBUS_IT_ERRI | SMBUS_IT_TCI | SMBUS_IT_NACKI | SMBUS_IT_RXI) |

| #define | SMBUS_IT_RXI I2C_CR1_RXIE |

| #define | SMBUS_IT_STOPI I2C_CR1_STOPIE |

| #define | SMBUS_IT_TCI I2C_CR1_TCIE |

| #define | SMBUS_IT_TX (SMBUS_IT_ERRI | SMBUS_IT_TCI | SMBUS_IT_STOPI | SMBUS_IT_NACKI | SMBUS_IT_TXI) |

| #define | SMBUS_IT_TXI I2C_CR1_TXIE |

| #define | SMBUS_LAST_FRAME_NO_PEC SMBUS_AUTOEND_MODE |

| #define | SMBUS_LAST_FRAME_WITH_PEC ((uint32_t)(SMBUS_AUTOEND_MODE | SMBUS_SENDPEC_MODE)) |

| #define | SMBUS_NEXT_FRAME ((uint32_t)(SMBUS_RELOAD_MODE | SMBUS_SOFTEND_MODE)) |

| #define | SMBUS_NO_STARTSTOP (0x00000000U) |

| #define | SMBUS_NOSTRETCH_DISABLE (0x00000000U) |

| #define | SMBUS_NOSTRETCH_ENABLE I2C_CR1_NOSTRETCH |

| #define | SMBUS_OA2_MASK01 ((uint8_t)0x01U) |

| #define | SMBUS_OA2_MASK02 ((uint8_t)0x02U) |

| #define | SMBUS_OA2_MASK03 ((uint8_t)0x03U) |

| #define | SMBUS_OA2_MASK04 ((uint8_t)0x04U) |

| #define | SMBUS_OA2_MASK05 ((uint8_t)0x05U) |

| #define | SMBUS_OA2_MASK06 ((uint8_t)0x06U) |

| #define | SMBUS_OA2_MASK07 ((uint8_t)0x07U) |

| #define | SMBUS_OA2_NOMASK ((uint8_t)0x00U) |

| #define | SMBUS_OTHER_AND_LAST_FRAME_NO_PEC (0x00AA0000U) |

| #define | SMBUS_OTHER_AND_LAST_FRAME_WITH_PEC (0xAA000000U) |

| #define | SMBUS_OTHER_FRAME_NO_PEC (0x000000AAU) |

| #define | SMBUS_OTHER_FRAME_WITH_PEC (0x0000AA00U) |

| #define | SMBUS_PEC_DISABLE (0x00000000U) |

| #define | SMBUS_PEC_ENABLE I2C_CR1_PECEN |

| #define | SMBUS_PERIPHERAL_MODE_SMBUS_HOST I2C_CR1_SMBHEN |

| #define | SMBUS_PERIPHERAL_MODE_SMBUS_SLAVE (0x00000000U) |

| #define | SMBUS_PERIPHERAL_MODE_SMBUS_SLAVE_ARP I2C_CR1_SMBDEN |

| #define | SMBUS_RELOAD_MODE I2C_CR2_RELOAD |

| #define | SMBUS_RESET_CR1(__HANDLE__) ((__HANDLE__)->Instance->CR1 &= (uint32_t)~((uint32_t)(I2C_CR1_SMBHEN | I2C_CR1_SMBDEN | I2C_CR1_PECEN))) |

| #define | SMBUS_RESET_CR2(__HANDLE__) ((__HANDLE__)->Instance->CR2 &= (uint32_t)~((uint32_t)(I2C_CR2_SADD | I2C_CR2_HEAD10R | I2C_CR2_NBYTES | I2C_CR2_RELOAD | I2C_CR2_RD_WRN))) |

| #define | SMBUS_SENDPEC_MODE I2C_CR2_PECBYTE |

| #define | SMBUS_SOFTEND_MODE (0x00000000U) |

Typedefs | |

| typedef struct __SMBUS_HandleTypeDef | SMBUS_HandleTypeDef |

Detailed Description

Header file of SMBUS HAL module.

- Attention

© Copyright (c) 2017 STMicroelectronics. All rights reserved.

This software component is licensed by ST under BSD 3-Clause license, the "License"; You may not use this file except in compliance with the License. You may obtain a copy of the License at: opensource.org/licenses/BSD-3-Clause

Definition in file stm32f7xx_hal_smbus.h.