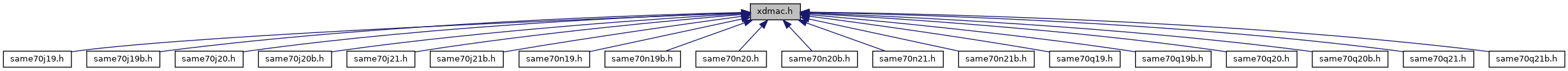

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Xdmac |

| struct | XdmacChid |

| XdmacChid hardware registers. More... | |

Macros | |

| #define | XDMAC_CBC_BLEN(value) ((XDMAC_CBC_BLEN_Msk & ((value) << XDMAC_CBC_BLEN_Pos))) |

| #define | XDMAC_CBC_BLEN_Msk (0xfffu << XDMAC_CBC_BLEN_Pos) |

| (XDMAC_CBC) Channel x Block Length More... | |

| #define | XDMAC_CBC_BLEN_Pos 0 |

| #define | XDMAC_CC_CSIZE(value) ((XDMAC_CC_CSIZE_Msk & ((value) << XDMAC_CC_CSIZE_Pos))) |

| #define | XDMAC_CC_CSIZE_CHK_1 (0x0u << 8) |

| (XDMAC_CC) 1 data transferred More... | |

| #define | XDMAC_CC_CSIZE_CHK_16 (0x4u << 8) |

| (XDMAC_CC) 16 data transferred More... | |

| #define | XDMAC_CC_CSIZE_CHK_2 (0x1u << 8) |

| (XDMAC_CC) 2 data transferred More... | |

| #define | XDMAC_CC_CSIZE_CHK_4 (0x2u << 8) |

| (XDMAC_CC) 4 data transferred More... | |

| #define | XDMAC_CC_CSIZE_CHK_8 (0x3u << 8) |

| (XDMAC_CC) 8 data transferred More... | |

| #define | XDMAC_CC_CSIZE_Msk (0x7u << XDMAC_CC_CSIZE_Pos) |

| (XDMAC_CC) Channel x Chunk Size More... | |

| #define | XDMAC_CC_CSIZE_Pos 8 |

| #define | XDMAC_CC_DAM(value) ((XDMAC_CC_DAM_Msk & ((value) << XDMAC_CC_DAM_Pos))) |

| #define | XDMAC_CC_DAM_FIXED_AM (0x0u << 18) |

| (XDMAC_CC) The address remains unchanged. More... | |

| #define | XDMAC_CC_DAM_INCREMENTED_AM (0x1u << 18) |

| (XDMAC_CC) The addressing mode is incremented (the increment size is set to the data size). More... | |

| #define | XDMAC_CC_DAM_Msk (0x3u << XDMAC_CC_DAM_Pos) |

| (XDMAC_CC) Channel x Destination Addressing Mode More... | |

| #define | XDMAC_CC_DAM_Pos 18 |

| #define | XDMAC_CC_DAM_UBS_AM (0x2u << 18) |

| (XDMAC_CC) The microblock stride is added at the microblock boundary. More... | |

| #define | XDMAC_CC_DAM_UBS_DS_AM (0x3u << 18) |

| (XDMAC_CC) The microblock stride is added at the microblock boundary, the data stride is added at the data boundary. More... | |

| #define | XDMAC_CC_DIF (0x1u << 14) |

| (XDMAC_CC) Channel x Destination Interface Identifier More... | |

| #define | XDMAC_CC_DIF_AHB_IF0 (0x0u << 14) |

| (XDMAC_CC) The data is written through the system bus interface 0 More... | |

| #define | XDMAC_CC_DIF_AHB_IF1 (0x1u << 14) |

| (XDMAC_CC) The data is written though the system bus interface 1 More... | |

| #define | XDMAC_CC_DSYNC (0x1u << 4) |

| (XDMAC_CC) Channel x Synchronization More... | |

| #define | XDMAC_CC_DSYNC_MEM2PER (0x1u << 4) |

| (XDMAC_CC) Memory to Peripheral transfer More... | |

| #define | XDMAC_CC_DSYNC_PER2MEM (0x0u << 4) |

| (XDMAC_CC) Peripheral to Memory transfer More... | |

| #define | XDMAC_CC_DWIDTH(value) ((XDMAC_CC_DWIDTH_Msk & ((value) << XDMAC_CC_DWIDTH_Pos))) |

| #define | XDMAC_CC_DWIDTH_BYTE (0x0u << 11) |

| (XDMAC_CC) The data size is set to 8 bits More... | |

| #define | XDMAC_CC_DWIDTH_HALFWORD (0x1u << 11) |

| (XDMAC_CC) The data size is set to 16 bits More... | |

| #define | XDMAC_CC_DWIDTH_Msk (0x3u << XDMAC_CC_DWIDTH_Pos) |

| (XDMAC_CC) Channel x Data Width More... | |

| #define | XDMAC_CC_DWIDTH_Pos 11 |

| #define | XDMAC_CC_DWIDTH_WORD (0x2u << 11) |

| (XDMAC_CC) The data size is set to 32 bits More... | |

| #define | XDMAC_CC_INITD (0x1u << 21) |

| (XDMAC_CC) Channel Initialization Terminated (this bit is read-only) More... | |

| #define | XDMAC_CC_INITD_IN_PROGRESS (0x0u << 21) |

| (XDMAC_CC) Channel initialization is in progress. More... | |

| #define | XDMAC_CC_INITD_TERMINATED (0x1u << 21) |

| (XDMAC_CC) Channel initialization is completed. More... | |

| #define | XDMAC_CC_MBSIZE(value) ((XDMAC_CC_MBSIZE_Msk & ((value) << XDMAC_CC_MBSIZE_Pos))) |

| #define | XDMAC_CC_MBSIZE_EIGHT (0x2u << 1) |

| (XDMAC_CC) The memory burst size is set to eight. More... | |

| #define | XDMAC_CC_MBSIZE_FOUR (0x1u << 1) |

| (XDMAC_CC) The memory burst size is set to four. More... | |

| #define | XDMAC_CC_MBSIZE_Msk (0x3u << XDMAC_CC_MBSIZE_Pos) |

| (XDMAC_CC) Channel x Memory Burst Size More... | |

| #define | XDMAC_CC_MBSIZE_Pos 1 |

| #define | XDMAC_CC_MBSIZE_SINGLE (0x0u << 1) |

| (XDMAC_CC) The memory burst size is set to one. More... | |

| #define | XDMAC_CC_MBSIZE_SIXTEEN (0x3u << 1) |

| (XDMAC_CC) The memory burst size is set to sixteen. More... | |

| #define | XDMAC_CC_MEMSET (0x1u << 7) |

| (XDMAC_CC) Channel x Fill Block of memory More... | |

| #define | XDMAC_CC_MEMSET_HW_MODE (0x1u << 7) |

| (XDMAC_CC) Sets the block of memory pointed by DA field to the specified value. This operation is performed on 8, 16 or 32 bits basis. More... | |

| #define | XDMAC_CC_MEMSET_NORMAL_MODE (0x0u << 7) |

| (XDMAC_CC) Memset is not activated More... | |

| #define | XDMAC_CC_PERID(value) ((XDMAC_CC_PERID_Msk & ((value) << XDMAC_CC_PERID_Pos))) |

| #define | XDMAC_CC_PERID_Msk (0x7fu << XDMAC_CC_PERID_Pos) |

| (XDMAC_CC) Channel x Peripheral Identifier More... | |

| #define | XDMAC_CC_PERID_Pos 24 |

| #define | XDMAC_CC_PROT (0x1u << 5) |

| (XDMAC_CC) Channel x Protection More... | |

| #define | XDMAC_CC_PROT_SEC (0x0u << 5) |

| (XDMAC_CC) Channel is secured More... | |

| #define | XDMAC_CC_PROT_UNSEC (0x1u << 5) |

| (XDMAC_CC) Channel is unsecured More... | |

| #define | XDMAC_CC_RDIP (0x1u << 22) |

| (XDMAC_CC) Read in Progress (this bit is read-only) More... | |

| #define | XDMAC_CC_RDIP_DONE (0x0u << 22) |

| (XDMAC_CC) No Active read transaction on the bus. More... | |

| #define | XDMAC_CC_RDIP_IN_PROGRESS (0x1u << 22) |

| (XDMAC_CC) A read transaction is in progress. More... | |

| #define | XDMAC_CC_SAM(value) ((XDMAC_CC_SAM_Msk & ((value) << XDMAC_CC_SAM_Pos))) |

| #define | XDMAC_CC_SAM_FIXED_AM (0x0u << 16) |

| (XDMAC_CC) The address remains unchanged. More... | |

| #define | XDMAC_CC_SAM_INCREMENTED_AM (0x1u << 16) |

| (XDMAC_CC) The addressing mode is incremented (the increment size is set to the data size). More... | |

| #define | XDMAC_CC_SAM_Msk (0x3u << XDMAC_CC_SAM_Pos) |

| (XDMAC_CC) Channel x Source Addressing Mode More... | |

| #define | XDMAC_CC_SAM_Pos 16 |

| #define | XDMAC_CC_SAM_UBS_AM (0x2u << 16) |

| (XDMAC_CC) The microblock stride is added at the microblock boundary. More... | |

| #define | XDMAC_CC_SAM_UBS_DS_AM (0x3u << 16) |

| (XDMAC_CC) The microblock stride is added at the microblock boundary, the data stride is added at the data boundary. More... | |

| #define | XDMAC_CC_SIF (0x1u << 13) |

| (XDMAC_CC) Channel x Source Interface Identifier More... | |

| #define | XDMAC_CC_SIF_AHB_IF0 (0x0u << 13) |

| (XDMAC_CC) The data is read through the system bus interface 0 More... | |

| #define | XDMAC_CC_SIF_AHB_IF1 (0x1u << 13) |

| (XDMAC_CC) The data is read through the system bus interface 1 More... | |

| #define | XDMAC_CC_SWREQ (0x1u << 6) |

| (XDMAC_CC) Channel x Software Request Trigger More... | |

| #define | XDMAC_CC_SWREQ_HWR_CONNECTED (0x0u << 6) |

| (XDMAC_CC) Hardware request line is connected to the peripheral request line. More... | |

| #define | XDMAC_CC_SWREQ_SWR_CONNECTED (0x1u << 6) |

| (XDMAC_CC) Software request is connected to the peripheral request line. More... | |

| #define | XDMAC_CC_TYPE (0x1u << 0) |

| (XDMAC_CC) Channel x Transfer Type More... | |

| #define | XDMAC_CC_TYPE_MEM_TRAN (0x0u << 0) |

| (XDMAC_CC) Self triggered mode (Memory to Memory Transfer). More... | |

| #define | XDMAC_CC_TYPE_PER_TRAN (0x1u << 0) |

| (XDMAC_CC) Synchronized mode (Peripheral to Memory or Memory to Peripheral Transfer). More... | |

| #define | XDMAC_CC_WRIP (0x1u << 23) |

| (XDMAC_CC) Write in Progress (this bit is read-only) More... | |

| #define | XDMAC_CC_WRIP_DONE (0x0u << 23) |

| (XDMAC_CC) No Active write transaction on the bus. More... | |

| #define | XDMAC_CC_WRIP_IN_PROGRESS (0x1u << 23) |

| (XDMAC_CC) A Write transaction is in progress. More... | |

| #define | XDMAC_CDA_DA(value) ((XDMAC_CDA_DA_Msk & ((value) << XDMAC_CDA_DA_Pos))) |

| #define | XDMAC_CDA_DA_Msk (0xffffffffu << XDMAC_CDA_DA_Pos) |

| (XDMAC_CDA) Channel x Destination Address More... | |

| #define | XDMAC_CDA_DA_Pos 0 |

| #define | XDMAC_CDS_MSP_DDS_MSP(value) ((XDMAC_CDS_MSP_DDS_MSP_Msk & ((value) << XDMAC_CDS_MSP_DDS_MSP_Pos))) |

| #define | XDMAC_CDS_MSP_DDS_MSP_Msk (0xffffu << XDMAC_CDS_MSP_DDS_MSP_Pos) |

| (XDMAC_CDS_MSP) Channel x Destination Data Stride or Memory Set Pattern More... | |

| #define | XDMAC_CDS_MSP_DDS_MSP_Pos 16 |

| #define | XDMAC_CDS_MSP_SDS_MSP(value) ((XDMAC_CDS_MSP_SDS_MSP_Msk & ((value) << XDMAC_CDS_MSP_SDS_MSP_Pos))) |

| #define | XDMAC_CDS_MSP_SDS_MSP_Msk (0xffffu << XDMAC_CDS_MSP_SDS_MSP_Pos) |

| (XDMAC_CDS_MSP) Channel x Source Data stride or Memory Set Pattern More... | |

| #define | XDMAC_CDS_MSP_SDS_MSP_Pos 0 |

| #define | XDMAC_CDUS_DUBS(value) ((XDMAC_CDUS_DUBS_Msk & ((value) << XDMAC_CDUS_DUBS_Pos))) |

| #define | XDMAC_CDUS_DUBS_Msk (0xffffffu << XDMAC_CDUS_DUBS_Pos) |

| (XDMAC_CDUS) Channel x Destination Microblock Stride More... | |

| #define | XDMAC_CDUS_DUBS_Pos 0 |

| #define | XDMAC_CID_BID (0x1u << 0) |

| (XDMAC_CID) End of Block Interrupt Disable Bit More... | |

| #define | XDMAC_CID_DID (0x1u << 2) |

| (XDMAC_CID) End of Disable Interrupt Disable Bit More... | |

| #define | XDMAC_CID_FID (0x1u << 3) |

| (XDMAC_CID) End of Flush Interrupt Disable Bit More... | |

| #define | XDMAC_CID_LID (0x1u << 1) |

| (XDMAC_CID) End of Linked List Interrupt Disable Bit More... | |

| #define | XDMAC_CID_RBEID (0x1u << 4) |

| (XDMAC_CID) Read Bus Error Interrupt Disable Bit More... | |

| #define | XDMAC_CID_ROID (0x1u << 6) |

| (XDMAC_CID) Request Overflow Error Interrupt Disable Bit More... | |

| #define | XDMAC_CID_WBEID (0x1u << 5) |

| (XDMAC_CID) Write Bus Error Interrupt Disable Bit More... | |

| #define | XDMAC_CIE_BIE (0x1u << 0) |

| (XDMAC_CIE) End of Block Interrupt Enable Bit More... | |

| #define | XDMAC_CIE_DIE (0x1u << 2) |

| (XDMAC_CIE) End of Disable Interrupt Enable Bit More... | |

| #define | XDMAC_CIE_FIE (0x1u << 3) |

| (XDMAC_CIE) End of Flush Interrupt Enable Bit More... | |

| #define | XDMAC_CIE_LIE (0x1u << 1) |

| (XDMAC_CIE) End of Linked List Interrupt Enable Bit More... | |

| #define | XDMAC_CIE_RBIE (0x1u << 4) |

| (XDMAC_CIE) Read Bus Error Interrupt Enable Bit More... | |

| #define | XDMAC_CIE_ROIE (0x1u << 6) |

| (XDMAC_CIE) Request Overflow Error Interrupt Enable Bit More... | |

| #define | XDMAC_CIE_WBIE (0x1u << 5) |

| (XDMAC_CIE) Write Bus Error Interrupt Enable Bit More... | |

| #define | XDMAC_CIM_BIM (0x1u << 0) |

| (XDMAC_CIM) End of Block Interrupt Mask Bit More... | |

| #define | XDMAC_CIM_DIM (0x1u << 2) |

| (XDMAC_CIM) End of Disable Interrupt Mask Bit More... | |

| #define | XDMAC_CIM_FIM (0x1u << 3) |

| (XDMAC_CIM) End of Flush Interrupt Mask Bit More... | |

| #define | XDMAC_CIM_LIM (0x1u << 1) |

| (XDMAC_CIM) End of Linked List Interrupt Mask Bit More... | |

| #define | XDMAC_CIM_RBEIM (0x1u << 4) |

| (XDMAC_CIM) Read Bus Error Interrupt Mask Bit More... | |

| #define | XDMAC_CIM_ROIM (0x1u << 6) |

| (XDMAC_CIM) Request Overflow Error Interrupt Mask Bit More... | |

| #define | XDMAC_CIM_WBEIM (0x1u << 5) |

| (XDMAC_CIM) Write Bus Error Interrupt Mask Bit More... | |

| #define | XDMAC_CIS_BIS (0x1u << 0) |

| (XDMAC_CIS) End of Block Interrupt Status Bit More... | |

| #define | XDMAC_CIS_DIS (0x1u << 2) |

| (XDMAC_CIS) End of Disable Interrupt Status Bit More... | |

| #define | XDMAC_CIS_FIS (0x1u << 3) |

| (XDMAC_CIS) End of Flush Interrupt Status Bit More... | |

| #define | XDMAC_CIS_LIS (0x1u << 1) |

| (XDMAC_CIS) End of Linked List Interrupt Status Bit More... | |

| #define | XDMAC_CIS_RBEIS (0x1u << 4) |

| (XDMAC_CIS) Read Bus Error Interrupt Status Bit More... | |

| #define | XDMAC_CIS_ROIS (0x1u << 6) |

| (XDMAC_CIS) Request Overflow Error Interrupt Status Bit More... | |

| #define | XDMAC_CIS_WBEIS (0x1u << 5) |

| (XDMAC_CIS) Write Bus Error Interrupt Status Bit More... | |

| #define | XDMAC_CNDA_NDA(value) (XDMAC_CNDA_NDA_Msk & (value)) |

| #define | XDMAC_CNDA_NDA_Msk (0x3fffffffu << XDMAC_CNDA_NDA_Pos) |

| (XDMAC_CNDA) Channel x Next Descriptor Address More... | |

| #define | XDMAC_CNDA_NDA_Pos 2 |

| #define | XDMAC_CNDA_NDAIF (0x1u << 0) |

| (XDMAC_CNDA) Channel x Next Descriptor Interface More... | |

| #define | XDMAC_CNDC_NDDUP (0x1u << 2) |

| (XDMAC_CNDC) Channel x Next Descriptor Destination Update More... | |

| #define | XDMAC_CNDC_NDDUP_DST_PARAMS_UNCHANGED (0x0u << 2) |

| (XDMAC_CNDC) Destination parameters remain unchanged. More... | |

| #define | XDMAC_CNDC_NDDUP_DST_PARAMS_UPDATED (0x1u << 2) |

| (XDMAC_CNDC) Destination parameters are updated when the descriptor is retrieved. More... | |

| #define | XDMAC_CNDC_NDE (0x1u << 0) |

| (XDMAC_CNDC) Channel x Next Descriptor Enable More... | |

| #define | XDMAC_CNDC_NDE_DSCR_FETCH_DIS (0x0u << 0) |

| (XDMAC_CNDC) Descriptor fetch is disabled More... | |

| #define | XDMAC_CNDC_NDE_DSCR_FETCH_EN (0x1u << 0) |

| (XDMAC_CNDC) Descriptor fetch is enabled More... | |

| #define | XDMAC_CNDC_NDSUP (0x1u << 1) |

| (XDMAC_CNDC) Channel x Next Descriptor Source Update More... | |

| #define | XDMAC_CNDC_NDSUP_SRC_PARAMS_UNCHANGED (0x0u << 1) |

| (XDMAC_CNDC) Source parameters remain unchanged. More... | |

| #define | XDMAC_CNDC_NDSUP_SRC_PARAMS_UPDATED (0x1u << 1) |

| (XDMAC_CNDC) Source parameters are updated when the descriptor is retrieved. More... | |

| #define | XDMAC_CNDC_NDVIEW(value) ((XDMAC_CNDC_NDVIEW_Msk & ((value) << XDMAC_CNDC_NDVIEW_Pos))) |

| #define | XDMAC_CNDC_NDVIEW_Msk (0x3u << XDMAC_CNDC_NDVIEW_Pos) |

| (XDMAC_CNDC) Channel x Next Descriptor View More... | |

| #define | XDMAC_CNDC_NDVIEW_NDV0 (0x0u << 3) |

| (XDMAC_CNDC) Next Descriptor View 0 More... | |

| #define | XDMAC_CNDC_NDVIEW_NDV1 (0x1u << 3) |

| (XDMAC_CNDC) Next Descriptor View 1 More... | |

| #define | XDMAC_CNDC_NDVIEW_NDV2 (0x2u << 3) |

| (XDMAC_CNDC) Next Descriptor View 2 More... | |

| #define | XDMAC_CNDC_NDVIEW_NDV3 (0x3u << 3) |

| (XDMAC_CNDC) Next Descriptor View 3 More... | |

| #define | XDMAC_CNDC_NDVIEW_Pos 3 |

| #define | XDMAC_CSA_SA(value) ((XDMAC_CSA_SA_Msk & ((value) << XDMAC_CSA_SA_Pos))) |

| #define | XDMAC_CSA_SA_Msk (0xffffffffu << XDMAC_CSA_SA_Pos) |

| (XDMAC_CSA) Channel x Source Address More... | |

| #define | XDMAC_CSA_SA_Pos 0 |

| #define | XDMAC_CSUS_SUBS(value) ((XDMAC_CSUS_SUBS_Msk & ((value) << XDMAC_CSUS_SUBS_Pos))) |

| #define | XDMAC_CSUS_SUBS_Msk (0xffffffu << XDMAC_CSUS_SUBS_Pos) |

| (XDMAC_CSUS) Channel x Source Microblock Stride More... | |

| #define | XDMAC_CSUS_SUBS_Pos 0 |

| #define | XDMAC_CUBC_UBLEN(value) ((XDMAC_CUBC_UBLEN_Msk & ((value) << XDMAC_CUBC_UBLEN_Pos))) |

| #define | XDMAC_CUBC_UBLEN_Msk (0xffffffu << XDMAC_CUBC_UBLEN_Pos) |

| (XDMAC_CUBC) Channel x Microblock Length More... | |

| #define | XDMAC_CUBC_UBLEN_Pos 0 |

| #define | XDMAC_GCFG_BXKBEN (0x1u << 8) |

| (XDMAC_GCFG) Boundary X Kilo byte Enable More... | |

| #define | XDMAC_GCFG_CGDISFIFO (0x1u << 2) |

| (XDMAC_GCFG) FIFO Clock Gating Disable More... | |

| #define | XDMAC_GCFG_CGDISIF (0x1u << 3) |

| (XDMAC_GCFG) Bus Interface Clock Gating Disable More... | |

| #define | XDMAC_GCFG_CGDISPIPE (0x1u << 1) |

| (XDMAC_GCFG) Pipeline Clock Gating Disable More... | |

| #define | XDMAC_GCFG_CGDISREG (0x1u << 0) |

| (XDMAC_GCFG) Configuration Registers Clock Gating Disable More... | |

| #define | XDMAC_GD_DI0 (0x1u << 0) |

| (XDMAC_GD) XDMAC Channel 0 Disable Bit More... | |

| #define | XDMAC_GD_DI1 (0x1u << 1) |

| (XDMAC_GD) XDMAC Channel 1 Disable Bit More... | |

| #define | XDMAC_GD_DI10 (0x1u << 10) |

| (XDMAC_GD) XDMAC Channel 10 Disable Bit More... | |

| #define | XDMAC_GD_DI11 (0x1u << 11) |

| (XDMAC_GD) XDMAC Channel 11 Disable Bit More... | |

| #define | XDMAC_GD_DI12 (0x1u << 12) |

| (XDMAC_GD) XDMAC Channel 12 Disable Bit More... | |

| #define | XDMAC_GD_DI13 (0x1u << 13) |

| (XDMAC_GD) XDMAC Channel 13 Disable Bit More... | |

| #define | XDMAC_GD_DI14 (0x1u << 14) |

| (XDMAC_GD) XDMAC Channel 14 Disable Bit More... | |

| #define | XDMAC_GD_DI15 (0x1u << 15) |

| (XDMAC_GD) XDMAC Channel 15 Disable Bit More... | |

| #define | XDMAC_GD_DI16 (0x1u << 16) |

| (XDMAC_GD) XDMAC Channel 16 Disable Bit More... | |

| #define | XDMAC_GD_DI17 (0x1u << 17) |

| (XDMAC_GD) XDMAC Channel 17 Disable Bit More... | |

| #define | XDMAC_GD_DI18 (0x1u << 18) |

| (XDMAC_GD) XDMAC Channel 18 Disable Bit More... | |

| #define | XDMAC_GD_DI19 (0x1u << 19) |

| (XDMAC_GD) XDMAC Channel 19 Disable Bit More... | |

| #define | XDMAC_GD_DI2 (0x1u << 2) |

| (XDMAC_GD) XDMAC Channel 2 Disable Bit More... | |

| #define | XDMAC_GD_DI20 (0x1u << 20) |

| (XDMAC_GD) XDMAC Channel 20 Disable Bit More... | |

| #define | XDMAC_GD_DI21 (0x1u << 21) |

| (XDMAC_GD) XDMAC Channel 21 Disable Bit More... | |

| #define | XDMAC_GD_DI22 (0x1u << 22) |

| (XDMAC_GD) XDMAC Channel 22 Disable Bit More... | |

| #define | XDMAC_GD_DI23 (0x1u << 23) |

| (XDMAC_GD) XDMAC Channel 23 Disable Bit More... | |

| #define | XDMAC_GD_DI3 (0x1u << 3) |

| (XDMAC_GD) XDMAC Channel 3 Disable Bit More... | |

| #define | XDMAC_GD_DI4 (0x1u << 4) |

| (XDMAC_GD) XDMAC Channel 4 Disable Bit More... | |

| #define | XDMAC_GD_DI5 (0x1u << 5) |

| (XDMAC_GD) XDMAC Channel 5 Disable Bit More... | |

| #define | XDMAC_GD_DI6 (0x1u << 6) |

| (XDMAC_GD) XDMAC Channel 6 Disable Bit More... | |

| #define | XDMAC_GD_DI7 (0x1u << 7) |

| (XDMAC_GD) XDMAC Channel 7 Disable Bit More... | |

| #define | XDMAC_GD_DI8 (0x1u << 8) |

| (XDMAC_GD) XDMAC Channel 8 Disable Bit More... | |

| #define | XDMAC_GD_DI9 (0x1u << 9) |

| (XDMAC_GD) XDMAC Channel 9 Disable Bit More... | |

| #define | XDMAC_GE_EN0 (0x1u << 0) |

| (XDMAC_GE) XDMAC Channel 0 Enable Bit More... | |

| #define | XDMAC_GE_EN1 (0x1u << 1) |

| (XDMAC_GE) XDMAC Channel 1 Enable Bit More... | |

| #define | XDMAC_GE_EN10 (0x1u << 10) |

| (XDMAC_GE) XDMAC Channel 10 Enable Bit More... | |

| #define | XDMAC_GE_EN11 (0x1u << 11) |

| (XDMAC_GE) XDMAC Channel 11 Enable Bit More... | |

| #define | XDMAC_GE_EN12 (0x1u << 12) |

| (XDMAC_GE) XDMAC Channel 12 Enable Bit More... | |

| #define | XDMAC_GE_EN13 (0x1u << 13) |

| (XDMAC_GE) XDMAC Channel 13 Enable Bit More... | |

| #define | XDMAC_GE_EN14 (0x1u << 14) |

| (XDMAC_GE) XDMAC Channel 14 Enable Bit More... | |

| #define | XDMAC_GE_EN15 (0x1u << 15) |

| (XDMAC_GE) XDMAC Channel 15 Enable Bit More... | |

| #define | XDMAC_GE_EN16 (0x1u << 16) |

| (XDMAC_GE) XDMAC Channel 16 Enable Bit More... | |

| #define | XDMAC_GE_EN17 (0x1u << 17) |

| (XDMAC_GE) XDMAC Channel 17 Enable Bit More... | |

| #define | XDMAC_GE_EN18 (0x1u << 18) |

| (XDMAC_GE) XDMAC Channel 18 Enable Bit More... | |

| #define | XDMAC_GE_EN19 (0x1u << 19) |

| (XDMAC_GE) XDMAC Channel 19 Enable Bit More... | |

| #define | XDMAC_GE_EN2 (0x1u << 2) |

| (XDMAC_GE) XDMAC Channel 2 Enable Bit More... | |

| #define | XDMAC_GE_EN20 (0x1u << 20) |

| (XDMAC_GE) XDMAC Channel 20 Enable Bit More... | |

| #define | XDMAC_GE_EN21 (0x1u << 21) |

| (XDMAC_GE) XDMAC Channel 21 Enable Bit More... | |

| #define | XDMAC_GE_EN22 (0x1u << 22) |

| (XDMAC_GE) XDMAC Channel 22 Enable Bit More... | |

| #define | XDMAC_GE_EN23 (0x1u << 23) |

| (XDMAC_GE) XDMAC Channel 23 Enable Bit More... | |

| #define | XDMAC_GE_EN3 (0x1u << 3) |

| (XDMAC_GE) XDMAC Channel 3 Enable Bit More... | |

| #define | XDMAC_GE_EN4 (0x1u << 4) |

| (XDMAC_GE) XDMAC Channel 4 Enable Bit More... | |

| #define | XDMAC_GE_EN5 (0x1u << 5) |

| (XDMAC_GE) XDMAC Channel 5 Enable Bit More... | |

| #define | XDMAC_GE_EN6 (0x1u << 6) |

| (XDMAC_GE) XDMAC Channel 6 Enable Bit More... | |

| #define | XDMAC_GE_EN7 (0x1u << 7) |

| (XDMAC_GE) XDMAC Channel 7 Enable Bit More... | |

| #define | XDMAC_GE_EN8 (0x1u << 8) |

| (XDMAC_GE) XDMAC Channel 8 Enable Bit More... | |

| #define | XDMAC_GE_EN9 (0x1u << 9) |

| (XDMAC_GE) XDMAC Channel 9 Enable Bit More... | |

| #define | XDMAC_GID_ID0 (0x1u << 0) |

| (XDMAC_GID) XDMAC Channel 0 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID1 (0x1u << 1) |

| (XDMAC_GID) XDMAC Channel 1 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID10 (0x1u << 10) |

| (XDMAC_GID) XDMAC Channel 10 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID11 (0x1u << 11) |

| (XDMAC_GID) XDMAC Channel 11 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID12 (0x1u << 12) |

| (XDMAC_GID) XDMAC Channel 12 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID13 (0x1u << 13) |

| (XDMAC_GID) XDMAC Channel 13 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID14 (0x1u << 14) |

| (XDMAC_GID) XDMAC Channel 14 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID15 (0x1u << 15) |

| (XDMAC_GID) XDMAC Channel 15 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID16 (0x1u << 16) |

| (XDMAC_GID) XDMAC Channel 16 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID17 (0x1u << 17) |

| (XDMAC_GID) XDMAC Channel 17 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID18 (0x1u << 18) |

| (XDMAC_GID) XDMAC Channel 18 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID19 (0x1u << 19) |

| (XDMAC_GID) XDMAC Channel 19 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID2 (0x1u << 2) |

| (XDMAC_GID) XDMAC Channel 2 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID20 (0x1u << 20) |

| (XDMAC_GID) XDMAC Channel 20 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID21 (0x1u << 21) |

| (XDMAC_GID) XDMAC Channel 21 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID22 (0x1u << 22) |

| (XDMAC_GID) XDMAC Channel 22 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID23 (0x1u << 23) |

| (XDMAC_GID) XDMAC Channel 23 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID3 (0x1u << 3) |

| (XDMAC_GID) XDMAC Channel 3 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID4 (0x1u << 4) |

| (XDMAC_GID) XDMAC Channel 4 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID5 (0x1u << 5) |

| (XDMAC_GID) XDMAC Channel 5 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID6 (0x1u << 6) |

| (XDMAC_GID) XDMAC Channel 6 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID7 (0x1u << 7) |

| (XDMAC_GID) XDMAC Channel 7 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID8 (0x1u << 8) |

| (XDMAC_GID) XDMAC Channel 8 Interrupt Disable Bit More... | |

| #define | XDMAC_GID_ID9 (0x1u << 9) |

| (XDMAC_GID) XDMAC Channel 9 Interrupt Disable Bit More... | |

| #define | XDMAC_GIE_IE0 (0x1u << 0) |

| (XDMAC_GIE) XDMAC Channel 0 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE1 (0x1u << 1) |

| (XDMAC_GIE) XDMAC Channel 1 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE10 (0x1u << 10) |

| (XDMAC_GIE) XDMAC Channel 10 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE11 (0x1u << 11) |

| (XDMAC_GIE) XDMAC Channel 11 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE12 (0x1u << 12) |

| (XDMAC_GIE) XDMAC Channel 12 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE13 (0x1u << 13) |

| (XDMAC_GIE) XDMAC Channel 13 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE14 (0x1u << 14) |

| (XDMAC_GIE) XDMAC Channel 14 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE15 (0x1u << 15) |

| (XDMAC_GIE) XDMAC Channel 15 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE16 (0x1u << 16) |

| (XDMAC_GIE) XDMAC Channel 16 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE17 (0x1u << 17) |

| (XDMAC_GIE) XDMAC Channel 17 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE18 (0x1u << 18) |

| (XDMAC_GIE) XDMAC Channel 18 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE19 (0x1u << 19) |

| (XDMAC_GIE) XDMAC Channel 19 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE2 (0x1u << 2) |

| (XDMAC_GIE) XDMAC Channel 2 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE20 (0x1u << 20) |

| (XDMAC_GIE) XDMAC Channel 20 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE21 (0x1u << 21) |

| (XDMAC_GIE) XDMAC Channel 21 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE22 (0x1u << 22) |

| (XDMAC_GIE) XDMAC Channel 22 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE23 (0x1u << 23) |

| (XDMAC_GIE) XDMAC Channel 23 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE3 (0x1u << 3) |

| (XDMAC_GIE) XDMAC Channel 3 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE4 (0x1u << 4) |

| (XDMAC_GIE) XDMAC Channel 4 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE5 (0x1u << 5) |

| (XDMAC_GIE) XDMAC Channel 5 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE6 (0x1u << 6) |

| (XDMAC_GIE) XDMAC Channel 6 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE7 (0x1u << 7) |

| (XDMAC_GIE) XDMAC Channel 7 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE8 (0x1u << 8) |

| (XDMAC_GIE) XDMAC Channel 8 Interrupt Enable Bit More... | |

| #define | XDMAC_GIE_IE9 (0x1u << 9) |

| (XDMAC_GIE) XDMAC Channel 9 Interrupt Enable Bit More... | |

| #define | XDMAC_GIM_IM0 (0x1u << 0) |

| (XDMAC_GIM) XDMAC Channel 0 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM1 (0x1u << 1) |

| (XDMAC_GIM) XDMAC Channel 1 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM10 (0x1u << 10) |

| (XDMAC_GIM) XDMAC Channel 10 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM11 (0x1u << 11) |

| (XDMAC_GIM) XDMAC Channel 11 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM12 (0x1u << 12) |

| (XDMAC_GIM) XDMAC Channel 12 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM13 (0x1u << 13) |

| (XDMAC_GIM) XDMAC Channel 13 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM14 (0x1u << 14) |

| (XDMAC_GIM) XDMAC Channel 14 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM15 (0x1u << 15) |

| (XDMAC_GIM) XDMAC Channel 15 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM16 (0x1u << 16) |

| (XDMAC_GIM) XDMAC Channel 16 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM17 (0x1u << 17) |

| (XDMAC_GIM) XDMAC Channel 17 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM18 (0x1u << 18) |

| (XDMAC_GIM) XDMAC Channel 18 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM19 (0x1u << 19) |

| (XDMAC_GIM) XDMAC Channel 19 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM2 (0x1u << 2) |

| (XDMAC_GIM) XDMAC Channel 2 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM20 (0x1u << 20) |

| (XDMAC_GIM) XDMAC Channel 20 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM21 (0x1u << 21) |

| (XDMAC_GIM) XDMAC Channel 21 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM22 (0x1u << 22) |

| (XDMAC_GIM) XDMAC Channel 22 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM23 (0x1u << 23) |

| (XDMAC_GIM) XDMAC Channel 23 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM3 (0x1u << 3) |

| (XDMAC_GIM) XDMAC Channel 3 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM4 (0x1u << 4) |

| (XDMAC_GIM) XDMAC Channel 4 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM5 (0x1u << 5) |

| (XDMAC_GIM) XDMAC Channel 5 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM6 (0x1u << 6) |

| (XDMAC_GIM) XDMAC Channel 6 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM7 (0x1u << 7) |

| (XDMAC_GIM) XDMAC Channel 7 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM8 (0x1u << 8) |

| (XDMAC_GIM) XDMAC Channel 8 Interrupt Mask Bit More... | |

| #define | XDMAC_GIM_IM9 (0x1u << 9) |

| (XDMAC_GIM) XDMAC Channel 9 Interrupt Mask Bit More... | |

| #define | XDMAC_GIS_IS0 (0x1u << 0) |

| (XDMAC_GIS) XDMAC Channel 0 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS1 (0x1u << 1) |

| (XDMAC_GIS) XDMAC Channel 1 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS10 (0x1u << 10) |

| (XDMAC_GIS) XDMAC Channel 10 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS11 (0x1u << 11) |

| (XDMAC_GIS) XDMAC Channel 11 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS12 (0x1u << 12) |

| (XDMAC_GIS) XDMAC Channel 12 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS13 (0x1u << 13) |

| (XDMAC_GIS) XDMAC Channel 13 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS14 (0x1u << 14) |

| (XDMAC_GIS) XDMAC Channel 14 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS15 (0x1u << 15) |

| (XDMAC_GIS) XDMAC Channel 15 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS16 (0x1u << 16) |

| (XDMAC_GIS) XDMAC Channel 16 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS17 (0x1u << 17) |

| (XDMAC_GIS) XDMAC Channel 17 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS18 (0x1u << 18) |

| (XDMAC_GIS) XDMAC Channel 18 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS19 (0x1u << 19) |

| (XDMAC_GIS) XDMAC Channel 19 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS2 (0x1u << 2) |

| (XDMAC_GIS) XDMAC Channel 2 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS20 (0x1u << 20) |

| (XDMAC_GIS) XDMAC Channel 20 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS21 (0x1u << 21) |

| (XDMAC_GIS) XDMAC Channel 21 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS22 (0x1u << 22) |

| (XDMAC_GIS) XDMAC Channel 22 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS23 (0x1u << 23) |

| (XDMAC_GIS) XDMAC Channel 23 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS3 (0x1u << 3) |

| (XDMAC_GIS) XDMAC Channel 3 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS4 (0x1u << 4) |

| (XDMAC_GIS) XDMAC Channel 4 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS5 (0x1u << 5) |

| (XDMAC_GIS) XDMAC Channel 5 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS6 (0x1u << 6) |

| (XDMAC_GIS) XDMAC Channel 6 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS7 (0x1u << 7) |

| (XDMAC_GIS) XDMAC Channel 7 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS8 (0x1u << 8) |

| (XDMAC_GIS) XDMAC Channel 8 Interrupt Status Bit More... | |

| #define | XDMAC_GIS_IS9 (0x1u << 9) |

| (XDMAC_GIS) XDMAC Channel 9 Interrupt Status Bit More... | |

| #define | XDMAC_GRS_RS0 (0x1u << 0) |

| (XDMAC_GRS) XDMAC Channel 0 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS1 (0x1u << 1) |

| (XDMAC_GRS) XDMAC Channel 1 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS10 (0x1u << 10) |

| (XDMAC_GRS) XDMAC Channel 10 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS11 (0x1u << 11) |

| (XDMAC_GRS) XDMAC Channel 11 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS12 (0x1u << 12) |

| (XDMAC_GRS) XDMAC Channel 12 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS13 (0x1u << 13) |

| (XDMAC_GRS) XDMAC Channel 13 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS14 (0x1u << 14) |

| (XDMAC_GRS) XDMAC Channel 14 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS15 (0x1u << 15) |

| (XDMAC_GRS) XDMAC Channel 15 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS16 (0x1u << 16) |

| (XDMAC_GRS) XDMAC Channel 16 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS17 (0x1u << 17) |

| (XDMAC_GRS) XDMAC Channel 17 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS18 (0x1u << 18) |

| (XDMAC_GRS) XDMAC Channel 18 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS19 (0x1u << 19) |

| (XDMAC_GRS) XDMAC Channel 19 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS2 (0x1u << 2) |

| (XDMAC_GRS) XDMAC Channel 2 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS20 (0x1u << 20) |

| (XDMAC_GRS) XDMAC Channel 20 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS21 (0x1u << 21) |

| (XDMAC_GRS) XDMAC Channel 21 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS22 (0x1u << 22) |

| (XDMAC_GRS) XDMAC Channel 22 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS23 (0x1u << 23) |

| (XDMAC_GRS) XDMAC Channel 23 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS3 (0x1u << 3) |

| (XDMAC_GRS) XDMAC Channel 3 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS4 (0x1u << 4) |

| (XDMAC_GRS) XDMAC Channel 4 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS5 (0x1u << 5) |

| (XDMAC_GRS) XDMAC Channel 5 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS6 (0x1u << 6) |

| (XDMAC_GRS) XDMAC Channel 6 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS7 (0x1u << 7) |

| (XDMAC_GRS) XDMAC Channel 7 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS8 (0x1u << 8) |

| (XDMAC_GRS) XDMAC Channel 8 Read Suspend Bit More... | |

| #define | XDMAC_GRS_RS9 (0x1u << 9) |

| (XDMAC_GRS) XDMAC Channel 9 Read Suspend Bit More... | |

| #define | XDMAC_GRWR_RWR0 (0x1u << 0) |

| (XDMAC_GRWR) XDMAC Channel 0 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR1 (0x1u << 1) |

| (XDMAC_GRWR) XDMAC Channel 1 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR10 (0x1u << 10) |

| (XDMAC_GRWR) XDMAC Channel 10 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR11 (0x1u << 11) |

| (XDMAC_GRWR) XDMAC Channel 11 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR12 (0x1u << 12) |

| (XDMAC_GRWR) XDMAC Channel 12 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR13 (0x1u << 13) |

| (XDMAC_GRWR) XDMAC Channel 13 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR14 (0x1u << 14) |

| (XDMAC_GRWR) XDMAC Channel 14 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR15 (0x1u << 15) |

| (XDMAC_GRWR) XDMAC Channel 15 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR16 (0x1u << 16) |

| (XDMAC_GRWR) XDMAC Channel 16 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR17 (0x1u << 17) |

| (XDMAC_GRWR) XDMAC Channel 17 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR18 (0x1u << 18) |

| (XDMAC_GRWR) XDMAC Channel 18 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR19 (0x1u << 19) |

| (XDMAC_GRWR) XDMAC Channel 19 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR2 (0x1u << 2) |

| (XDMAC_GRWR) XDMAC Channel 2 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR20 (0x1u << 20) |

| (XDMAC_GRWR) XDMAC Channel 20 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR21 (0x1u << 21) |

| (XDMAC_GRWR) XDMAC Channel 21 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR22 (0x1u << 22) |

| (XDMAC_GRWR) XDMAC Channel 22 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR23 (0x1u << 23) |

| (XDMAC_GRWR) XDMAC Channel 23 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR3 (0x1u << 3) |

| (XDMAC_GRWR) XDMAC Channel 3 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR4 (0x1u << 4) |

| (XDMAC_GRWR) XDMAC Channel 4 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR5 (0x1u << 5) |

| (XDMAC_GRWR) XDMAC Channel 5 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR6 (0x1u << 6) |

| (XDMAC_GRWR) XDMAC Channel 6 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR7 (0x1u << 7) |

| (XDMAC_GRWR) XDMAC Channel 7 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR8 (0x1u << 8) |

| (XDMAC_GRWR) XDMAC Channel 8 Read Write Resume Bit More... | |

| #define | XDMAC_GRWR_RWR9 (0x1u << 9) |

| (XDMAC_GRWR) XDMAC Channel 9 Read Write Resume Bit More... | |

| #define | XDMAC_GRWS_RWS0 (0x1u << 0) |

| (XDMAC_GRWS) XDMAC Channel 0 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS1 (0x1u << 1) |

| (XDMAC_GRWS) XDMAC Channel 1 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS10 (0x1u << 10) |

| (XDMAC_GRWS) XDMAC Channel 10 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS11 (0x1u << 11) |

| (XDMAC_GRWS) XDMAC Channel 11 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS12 (0x1u << 12) |

| (XDMAC_GRWS) XDMAC Channel 12 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS13 (0x1u << 13) |

| (XDMAC_GRWS) XDMAC Channel 13 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS14 (0x1u << 14) |

| (XDMAC_GRWS) XDMAC Channel 14 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS15 (0x1u << 15) |

| (XDMAC_GRWS) XDMAC Channel 15 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS16 (0x1u << 16) |

| (XDMAC_GRWS) XDMAC Channel 16 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS17 (0x1u << 17) |

| (XDMAC_GRWS) XDMAC Channel 17 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS18 (0x1u << 18) |

| (XDMAC_GRWS) XDMAC Channel 18 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS19 (0x1u << 19) |

| (XDMAC_GRWS) XDMAC Channel 19 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS2 (0x1u << 2) |

| (XDMAC_GRWS) XDMAC Channel 2 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS20 (0x1u << 20) |

| (XDMAC_GRWS) XDMAC Channel 20 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS21 (0x1u << 21) |

| (XDMAC_GRWS) XDMAC Channel 21 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS22 (0x1u << 22) |

| (XDMAC_GRWS) XDMAC Channel 22 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS23 (0x1u << 23) |

| (XDMAC_GRWS) XDMAC Channel 23 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS3 (0x1u << 3) |

| (XDMAC_GRWS) XDMAC Channel 3 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS4 (0x1u << 4) |

| (XDMAC_GRWS) XDMAC Channel 4 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS5 (0x1u << 5) |

| (XDMAC_GRWS) XDMAC Channel 5 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS6 (0x1u << 6) |

| (XDMAC_GRWS) XDMAC Channel 6 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS7 (0x1u << 7) |

| (XDMAC_GRWS) XDMAC Channel 7 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS8 (0x1u << 8) |

| (XDMAC_GRWS) XDMAC Channel 8 Read Write Suspend Bit More... | |

| #define | XDMAC_GRWS_RWS9 (0x1u << 9) |

| (XDMAC_GRWS) XDMAC Channel 9 Read Write Suspend Bit More... | |

| #define | XDMAC_GS_ST0 (0x1u << 0) |

| (XDMAC_GS) XDMAC Channel 0 Status Bit More... | |

| #define | XDMAC_GS_ST1 (0x1u << 1) |

| (XDMAC_GS) XDMAC Channel 1 Status Bit More... | |

| #define | XDMAC_GS_ST10 (0x1u << 10) |

| (XDMAC_GS) XDMAC Channel 10 Status Bit More... | |

| #define | XDMAC_GS_ST11 (0x1u << 11) |

| (XDMAC_GS) XDMAC Channel 11 Status Bit More... | |

| #define | XDMAC_GS_ST12 (0x1u << 12) |

| (XDMAC_GS) XDMAC Channel 12 Status Bit More... | |

| #define | XDMAC_GS_ST13 (0x1u << 13) |

| (XDMAC_GS) XDMAC Channel 13 Status Bit More... | |

| #define | XDMAC_GS_ST14 (0x1u << 14) |

| (XDMAC_GS) XDMAC Channel 14 Status Bit More... | |

| #define | XDMAC_GS_ST15 (0x1u << 15) |

| (XDMAC_GS) XDMAC Channel 15 Status Bit More... | |

| #define | XDMAC_GS_ST16 (0x1u << 16) |

| (XDMAC_GS) XDMAC Channel 16 Status Bit More... | |

| #define | XDMAC_GS_ST17 (0x1u << 17) |

| (XDMAC_GS) XDMAC Channel 17 Status Bit More... | |

| #define | XDMAC_GS_ST18 (0x1u << 18) |

| (XDMAC_GS) XDMAC Channel 18 Status Bit More... | |

| #define | XDMAC_GS_ST19 (0x1u << 19) |

| (XDMAC_GS) XDMAC Channel 19 Status Bit More... | |

| #define | XDMAC_GS_ST2 (0x1u << 2) |

| (XDMAC_GS) XDMAC Channel 2 Status Bit More... | |

| #define | XDMAC_GS_ST20 (0x1u << 20) |

| (XDMAC_GS) XDMAC Channel 20 Status Bit More... | |

| #define | XDMAC_GS_ST21 (0x1u << 21) |

| (XDMAC_GS) XDMAC Channel 21 Status Bit More... | |

| #define | XDMAC_GS_ST22 (0x1u << 22) |

| (XDMAC_GS) XDMAC Channel 22 Status Bit More... | |

| #define | XDMAC_GS_ST23 (0x1u << 23) |

| (XDMAC_GS) XDMAC Channel 23 Status Bit More... | |

| #define | XDMAC_GS_ST3 (0x1u << 3) |

| (XDMAC_GS) XDMAC Channel 3 Status Bit More... | |

| #define | XDMAC_GS_ST4 (0x1u << 4) |

| (XDMAC_GS) XDMAC Channel 4 Status Bit More... | |

| #define | XDMAC_GS_ST5 (0x1u << 5) |

| (XDMAC_GS) XDMAC Channel 5 Status Bit More... | |

| #define | XDMAC_GS_ST6 (0x1u << 6) |

| (XDMAC_GS) XDMAC Channel 6 Status Bit More... | |

| #define | XDMAC_GS_ST7 (0x1u << 7) |

| (XDMAC_GS) XDMAC Channel 7 Status Bit More... | |

| #define | XDMAC_GS_ST8 (0x1u << 8) |

| (XDMAC_GS) XDMAC Channel 8 Status Bit More... | |

| #define | XDMAC_GS_ST9 (0x1u << 9) |

| (XDMAC_GS) XDMAC Channel 9 Status Bit More... | |

| #define | XDMAC_GSWF_SWF0 (0x1u << 0) |

| (XDMAC_GSWF) XDMAC Channel 0 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF1 (0x1u << 1) |

| (XDMAC_GSWF) XDMAC Channel 1 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF10 (0x1u << 10) |

| (XDMAC_GSWF) XDMAC Channel 10 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF11 (0x1u << 11) |

| (XDMAC_GSWF) XDMAC Channel 11 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF12 (0x1u << 12) |

| (XDMAC_GSWF) XDMAC Channel 12 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF13 (0x1u << 13) |

| (XDMAC_GSWF) XDMAC Channel 13 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF14 (0x1u << 14) |

| (XDMAC_GSWF) XDMAC Channel 14 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF15 (0x1u << 15) |

| (XDMAC_GSWF) XDMAC Channel 15 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF16 (0x1u << 16) |

| (XDMAC_GSWF) XDMAC Channel 16 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF17 (0x1u << 17) |

| (XDMAC_GSWF) XDMAC Channel 17 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF18 (0x1u << 18) |

| (XDMAC_GSWF) XDMAC Channel 18 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF19 (0x1u << 19) |

| (XDMAC_GSWF) XDMAC Channel 19 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF2 (0x1u << 2) |

| (XDMAC_GSWF) XDMAC Channel 2 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF20 (0x1u << 20) |

| (XDMAC_GSWF) XDMAC Channel 20 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF21 (0x1u << 21) |

| (XDMAC_GSWF) XDMAC Channel 21 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF22 (0x1u << 22) |

| (XDMAC_GSWF) XDMAC Channel 22 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF23 (0x1u << 23) |

| (XDMAC_GSWF) XDMAC Channel 23 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF3 (0x1u << 3) |

| (XDMAC_GSWF) XDMAC Channel 3 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF4 (0x1u << 4) |

| (XDMAC_GSWF) XDMAC Channel 4 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF5 (0x1u << 5) |

| (XDMAC_GSWF) XDMAC Channel 5 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF6 (0x1u << 6) |

| (XDMAC_GSWF) XDMAC Channel 6 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF7 (0x1u << 7) |

| (XDMAC_GSWF) XDMAC Channel 7 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF8 (0x1u << 8) |

| (XDMAC_GSWF) XDMAC Channel 8 Software Flush Request Bit More... | |

| #define | XDMAC_GSWF_SWF9 (0x1u << 9) |

| (XDMAC_GSWF) XDMAC Channel 9 Software Flush Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ0 (0x1u << 0) |

| (XDMAC_GSWR) XDMAC Channel 0 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ1 (0x1u << 1) |

| (XDMAC_GSWR) XDMAC Channel 1 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ10 (0x1u << 10) |

| (XDMAC_GSWR) XDMAC Channel 10 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ11 (0x1u << 11) |

| (XDMAC_GSWR) XDMAC Channel 11 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ12 (0x1u << 12) |

| (XDMAC_GSWR) XDMAC Channel 12 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ13 (0x1u << 13) |

| (XDMAC_GSWR) XDMAC Channel 13 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ14 (0x1u << 14) |

| (XDMAC_GSWR) XDMAC Channel 14 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ15 (0x1u << 15) |

| (XDMAC_GSWR) XDMAC Channel 15 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ16 (0x1u << 16) |

| (XDMAC_GSWR) XDMAC Channel 16 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ17 (0x1u << 17) |

| (XDMAC_GSWR) XDMAC Channel 17 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ18 (0x1u << 18) |

| (XDMAC_GSWR) XDMAC Channel 18 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ19 (0x1u << 19) |

| (XDMAC_GSWR) XDMAC Channel 19 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ2 (0x1u << 2) |

| (XDMAC_GSWR) XDMAC Channel 2 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ20 (0x1u << 20) |

| (XDMAC_GSWR) XDMAC Channel 20 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ21 (0x1u << 21) |

| (XDMAC_GSWR) XDMAC Channel 21 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ22 (0x1u << 22) |

| (XDMAC_GSWR) XDMAC Channel 22 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ23 (0x1u << 23) |

| (XDMAC_GSWR) XDMAC Channel 23 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ3 (0x1u << 3) |

| (XDMAC_GSWR) XDMAC Channel 3 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ4 (0x1u << 4) |

| (XDMAC_GSWR) XDMAC Channel 4 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ5 (0x1u << 5) |

| (XDMAC_GSWR) XDMAC Channel 5 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ6 (0x1u << 6) |

| (XDMAC_GSWR) XDMAC Channel 6 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ7 (0x1u << 7) |

| (XDMAC_GSWR) XDMAC Channel 7 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ8 (0x1u << 8) |

| (XDMAC_GSWR) XDMAC Channel 8 Software Request Bit More... | |

| #define | XDMAC_GSWR_SWREQ9 (0x1u << 9) |

| (XDMAC_GSWR) XDMAC Channel 9 Software Request Bit More... | |

| #define | XDMAC_GSWS_SWRS0 (0x1u << 0) |

| (XDMAC_GSWS) XDMAC Channel 0 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS1 (0x1u << 1) |

| (XDMAC_GSWS) XDMAC Channel 1 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS10 (0x1u << 10) |

| (XDMAC_GSWS) XDMAC Channel 10 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS11 (0x1u << 11) |

| (XDMAC_GSWS) XDMAC Channel 11 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS12 (0x1u << 12) |

| (XDMAC_GSWS) XDMAC Channel 12 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS13 (0x1u << 13) |

| (XDMAC_GSWS) XDMAC Channel 13 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS14 (0x1u << 14) |

| (XDMAC_GSWS) XDMAC Channel 14 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS15 (0x1u << 15) |

| (XDMAC_GSWS) XDMAC Channel 15 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS16 (0x1u << 16) |

| (XDMAC_GSWS) XDMAC Channel 16 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS17 (0x1u << 17) |

| (XDMAC_GSWS) XDMAC Channel 17 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS18 (0x1u << 18) |

| (XDMAC_GSWS) XDMAC Channel 18 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS19 (0x1u << 19) |

| (XDMAC_GSWS) XDMAC Channel 19 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS2 (0x1u << 2) |

| (XDMAC_GSWS) XDMAC Channel 2 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS20 (0x1u << 20) |

| (XDMAC_GSWS) XDMAC Channel 20 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS21 (0x1u << 21) |

| (XDMAC_GSWS) XDMAC Channel 21 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS22 (0x1u << 22) |

| (XDMAC_GSWS) XDMAC Channel 22 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS23 (0x1u << 23) |

| (XDMAC_GSWS) XDMAC Channel 23 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS3 (0x1u << 3) |

| (XDMAC_GSWS) XDMAC Channel 3 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS4 (0x1u << 4) |

| (XDMAC_GSWS) XDMAC Channel 4 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS5 (0x1u << 5) |

| (XDMAC_GSWS) XDMAC Channel 5 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS6 (0x1u << 6) |

| (XDMAC_GSWS) XDMAC Channel 6 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS7 (0x1u << 7) |

| (XDMAC_GSWS) XDMAC Channel 7 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS8 (0x1u << 8) |

| (XDMAC_GSWS) XDMAC Channel 8 Software Request Status Bit More... | |

| #define | XDMAC_GSWS_SWRS9 (0x1u << 9) |

| (XDMAC_GSWS) XDMAC Channel 9 Software Request Status Bit More... | |

| #define | XDMAC_GTYPE_FIFO_SZ(value) ((XDMAC_GTYPE_FIFO_SZ_Msk & ((value) << XDMAC_GTYPE_FIFO_SZ_Pos))) |

| #define | XDMAC_GTYPE_FIFO_SZ_Msk (0x7ffu << XDMAC_GTYPE_FIFO_SZ_Pos) |

| (XDMAC_GTYPE) Number of Bytes More... | |

| #define | XDMAC_GTYPE_FIFO_SZ_Pos 5 |

| #define | XDMAC_GTYPE_NB_CH(value) ((XDMAC_GTYPE_NB_CH_Msk & ((value) << XDMAC_GTYPE_NB_CH_Pos))) |

| #define | XDMAC_GTYPE_NB_CH_Msk (0x1fu << XDMAC_GTYPE_NB_CH_Pos) |

| (XDMAC_GTYPE) Number of Channels Minus One More... | |

| #define | XDMAC_GTYPE_NB_CH_Pos 0 |

| #define | XDMAC_GTYPE_NB_REQ(value) ((XDMAC_GTYPE_NB_REQ_Msk & ((value) << XDMAC_GTYPE_NB_REQ_Pos))) |

| #define | XDMAC_GTYPE_NB_REQ_Msk (0x7fu << XDMAC_GTYPE_NB_REQ_Pos) |

| (XDMAC_GTYPE) Number of Peripheral Requests Minus One More... | |

| #define | XDMAC_GTYPE_NB_REQ_Pos 16 |

| #define | XDMAC_GWAC_PW0(value) ((XDMAC_GWAC_PW0_Msk & ((value) << XDMAC_GWAC_PW0_Pos))) |

| #define | XDMAC_GWAC_PW0_Msk (0xfu << XDMAC_GWAC_PW0_Pos) |

| (XDMAC_GWAC) Pool Weight 0 More... | |

| #define | XDMAC_GWAC_PW0_Pos 0 |

| #define | XDMAC_GWAC_PW1(value) ((XDMAC_GWAC_PW1_Msk & ((value) << XDMAC_GWAC_PW1_Pos))) |

| #define | XDMAC_GWAC_PW1_Msk (0xfu << XDMAC_GWAC_PW1_Pos) |

| (XDMAC_GWAC) Pool Weight 1 More... | |

| #define | XDMAC_GWAC_PW1_Pos 4 |

| #define | XDMAC_GWAC_PW2(value) ((XDMAC_GWAC_PW2_Msk & ((value) << XDMAC_GWAC_PW2_Pos))) |

| #define | XDMAC_GWAC_PW2_Msk (0xfu << XDMAC_GWAC_PW2_Pos) |

| (XDMAC_GWAC) Pool Weight 2 More... | |

| #define | XDMAC_GWAC_PW2_Pos 8 |

| #define | XDMAC_GWAC_PW3(value) ((XDMAC_GWAC_PW3_Msk & ((value) << XDMAC_GWAC_PW3_Pos))) |

| #define | XDMAC_GWAC_PW3_Msk (0xfu << XDMAC_GWAC_PW3_Pos) |

| (XDMAC_GWAC) Pool Weight 3 More... | |

| #define | XDMAC_GWAC_PW3_Pos 12 |

| #define | XDMAC_GWS_WS0 (0x1u << 0) |

| (XDMAC_GWS) XDMAC Channel 0 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS1 (0x1u << 1) |

| (XDMAC_GWS) XDMAC Channel 1 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS10 (0x1u << 10) |

| (XDMAC_GWS) XDMAC Channel 10 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS11 (0x1u << 11) |

| (XDMAC_GWS) XDMAC Channel 11 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS12 (0x1u << 12) |

| (XDMAC_GWS) XDMAC Channel 12 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS13 (0x1u << 13) |

| (XDMAC_GWS) XDMAC Channel 13 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS14 (0x1u << 14) |

| (XDMAC_GWS) XDMAC Channel 14 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS15 (0x1u << 15) |

| (XDMAC_GWS) XDMAC Channel 15 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS16 (0x1u << 16) |

| (XDMAC_GWS) XDMAC Channel 16 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS17 (0x1u << 17) |

| (XDMAC_GWS) XDMAC Channel 17 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS18 (0x1u << 18) |

| (XDMAC_GWS) XDMAC Channel 18 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS19 (0x1u << 19) |

| (XDMAC_GWS) XDMAC Channel 19 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS2 (0x1u << 2) |

| (XDMAC_GWS) XDMAC Channel 2 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS20 (0x1u << 20) |

| (XDMAC_GWS) XDMAC Channel 20 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS21 (0x1u << 21) |

| (XDMAC_GWS) XDMAC Channel 21 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS22 (0x1u << 22) |

| (XDMAC_GWS) XDMAC Channel 22 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS23 (0x1u << 23) |

| (XDMAC_GWS) XDMAC Channel 23 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS3 (0x1u << 3) |

| (XDMAC_GWS) XDMAC Channel 3 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS4 (0x1u << 4) |

| (XDMAC_GWS) XDMAC Channel 4 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS5 (0x1u << 5) |

| (XDMAC_GWS) XDMAC Channel 5 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS6 (0x1u << 6) |

| (XDMAC_GWS) XDMAC Channel 6 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS7 (0x1u << 7) |

| (XDMAC_GWS) XDMAC Channel 7 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS8 (0x1u << 8) |

| (XDMAC_GWS) XDMAC Channel 8 Write Suspend Bit More... | |

| #define | XDMAC_GWS_WS9 (0x1u << 9) |

| (XDMAC_GWS) XDMAC Channel 9 Write Suspend Bit More... | |

| #define | XDMAC_VERSION_MFN(value) ((XDMAC_VERSION_MFN_Msk & ((value) << XDMAC_VERSION_MFN_Pos))) |

| #define | XDMAC_VERSION_MFN_Msk (0x7u << XDMAC_VERSION_MFN_Pos) |

| (XDMAC_VERSION) Metal Fix Number More... | |

| #define | XDMAC_VERSION_MFN_Pos 16 |

| #define | XDMAC_VERSION_VERSION(value) ((XDMAC_VERSION_VERSION_Msk & ((value) << XDMAC_VERSION_VERSION_Pos))) |

| #define | XDMAC_VERSION_VERSION_Msk (0xfffu << XDMAC_VERSION_VERSION_Pos) |

| (XDMAC_VERSION) Version of the Hardware Module More... | |

| #define | XDMAC_VERSION_VERSION_Pos 0 |

| #define | XDMACCHID_NUMBER 24 |

| Xdmac hardware registers. More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file utils/cmsis/same70/include/component/xdmac.h.