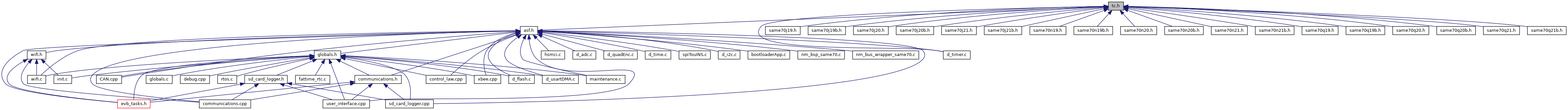

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Tc |

| struct | TcChannel |

| TcChannel hardware registers. More... | |

Macros | |

| #define | TC_BCR_SYNC (0x1u << 0) |

| (TC_BCR) Synchro Command More... | |

| #define | TC_BMR_EDGPHA (0x1u << 12) |

| (TC_BMR) Edge on PHA Count Mode More... | |

| #define | TC_BMR_IDXPHB (0x1u << 17) |

| (TC_BMR) Index Pin is PHB Pin More... | |

| #define | TC_BMR_INVA (0x1u << 13) |

| (TC_BMR) Inverted PHA More... | |

| #define | TC_BMR_INVB (0x1u << 14) |

| (TC_BMR) Inverted PHB More... | |

| #define | TC_BMR_INVIDX (0x1u << 15) |

| (TC_BMR) Inverted Index More... | |

| #define | TC_BMR_MAXFILT(value) ((TC_BMR_MAXFILT_Msk & ((value) << TC_BMR_MAXFILT_Pos))) |

| #define | TC_BMR_MAXFILT_Msk (0x3fu << TC_BMR_MAXFILT_Pos) |

| (TC_BMR) Maximum Filter More... | |

| #define | TC_BMR_MAXFILT_Pos 20 |

| #define | TC_BMR_POSEN (0x1u << 9) |

| (TC_BMR) Position Enabled More... | |

| #define | TC_BMR_QDEN (0x1u << 8) |

| (TC_BMR) Quadrature Decoder Enabled More... | |

| #define | TC_BMR_QDTRANS (0x1u << 11) |

| (TC_BMR) Quadrature Decoding Transparent More... | |

| #define | TC_BMR_SPEEDEN (0x1u << 10) |

| (TC_BMR) Speed Enabled More... | |

| #define | TC_BMR_SWAP (0x1u << 16) |

| (TC_BMR) Swap PHA and PHB More... | |

| #define | TC_BMR_TC0XC0S(value) ((TC_BMR_TC0XC0S_Msk & ((value) << TC_BMR_TC0XC0S_Pos))) |

| #define | TC_BMR_TC0XC0S_Msk (0x3u << TC_BMR_TC0XC0S_Pos) |

| (TC_BMR) External Clock Signal 0 Selection More... | |

| #define | TC_BMR_TC0XC0S_Pos 0 |

| #define | TC_BMR_TC0XC0S_TCLK0 (0x0u << 0) |

| (TC_BMR) Signal connected to XC0: TCLK0 More... | |

| #define | TC_BMR_TC0XC0S_TIOA1 (0x2u << 0) |

| (TC_BMR) Signal connected to XC0: TIOA1 More... | |

| #define | TC_BMR_TC0XC0S_TIOA2 (0x3u << 0) |

| (TC_BMR) Signal connected to XC0: TIOA2 More... | |

| #define | TC_BMR_TC1XC1S(value) ((TC_BMR_TC1XC1S_Msk & ((value) << TC_BMR_TC1XC1S_Pos))) |

| #define | TC_BMR_TC1XC1S_Msk (0x3u << TC_BMR_TC1XC1S_Pos) |

| (TC_BMR) External Clock Signal 1 Selection More... | |

| #define | TC_BMR_TC1XC1S_Pos 2 |

| #define | TC_BMR_TC1XC1S_TCLK1 (0x0u << 2) |

| (TC_BMR) Signal connected to XC1: TCLK1 More... | |

| #define | TC_BMR_TC1XC1S_TIOA0 (0x2u << 2) |

| (TC_BMR) Signal connected to XC1: TIOA0 More... | |

| #define | TC_BMR_TC1XC1S_TIOA2 (0x3u << 2) |

| (TC_BMR) Signal connected to XC1: TIOA2 More... | |

| #define | TC_BMR_TC2XC2S(value) ((TC_BMR_TC2XC2S_Msk & ((value) << TC_BMR_TC2XC2S_Pos))) |

| #define | TC_BMR_TC2XC2S_Msk (0x3u << TC_BMR_TC2XC2S_Pos) |

| (TC_BMR) External Clock Signal 2 Selection More... | |

| #define | TC_BMR_TC2XC2S_Pos 4 |

| #define | TC_BMR_TC2XC2S_TCLK2 (0x0u << 4) |

| (TC_BMR) Signal connected to XC2: TCLK2 More... | |

| #define | TC_BMR_TC2XC2S_TIOA0 (0x2u << 4) |

| (TC_BMR) Signal connected to XC2: TIOA0 More... | |

| #define | TC_BMR_TC2XC2S_TIOA1 (0x3u << 4) |

| (TC_BMR) Signal connected to XC2: TIOA1 More... | |

| #define | TC_CCR_CLKDIS (0x1u << 1) |

| (TC_CCR) Counter Clock Disable Command More... | |

| #define | TC_CCR_CLKEN (0x1u << 0) |

| (TC_CCR) Counter Clock Enable Command More... | |

| #define | TC_CCR_SWTRG (0x1u << 2) |

| (TC_CCR) Software Trigger Command More... | |

| #define | TC_CMR_ABETRG (0x1u << 10) |

| (TC_CMR) TIOA or TIOB External Trigger Selection More... | |

| #define | TC_CMR_ACPA(value) ((TC_CMR_ACPA_Msk & ((value) << TC_CMR_ACPA_Pos))) |

| #define | TC_CMR_ACPA_CLEAR (0x2u << 16) |

| (TC_CMR) Clear More... | |

| #define | TC_CMR_ACPA_Msk (0x3u << TC_CMR_ACPA_Pos) |

| (TC_CMR) RA Compare Effect on TIOA More... | |

| #define | TC_CMR_ACPA_NONE (0x0u << 16) |

| (TC_CMR) None More... | |

| #define | TC_CMR_ACPA_Pos 16 |

| #define | TC_CMR_ACPA_SET (0x1u << 16) |

| (TC_CMR) Set More... | |

| #define | TC_CMR_ACPA_TOGGLE (0x3u << 16) |

| (TC_CMR) Toggle More... | |

| #define | TC_CMR_ACPC(value) ((TC_CMR_ACPC_Msk & ((value) << TC_CMR_ACPC_Pos))) |

| #define | TC_CMR_ACPC_CLEAR (0x2u << 18) |

| (TC_CMR) Clear More... | |

| #define | TC_CMR_ACPC_Msk (0x3u << TC_CMR_ACPC_Pos) |

| (TC_CMR) RC Compare Effect on TIOA More... | |

| #define | TC_CMR_ACPC_NONE (0x0u << 18) |

| (TC_CMR) None More... | |

| #define | TC_CMR_ACPC_Pos 18 |

| #define | TC_CMR_ACPC_SET (0x1u << 18) |

| (TC_CMR) Set More... | |

| #define | TC_CMR_ACPC_TOGGLE (0x3u << 18) |

| (TC_CMR) Toggle More... | |

| #define | TC_CMR_AEEVT(value) ((TC_CMR_AEEVT_Msk & ((value) << TC_CMR_AEEVT_Pos))) |

| #define | TC_CMR_AEEVT_CLEAR (0x2u << 20) |

| (TC_CMR) Clear More... | |

| #define | TC_CMR_AEEVT_Msk (0x3u << TC_CMR_AEEVT_Pos) |

| (TC_CMR) External Event Effect on TIOA More... | |

| #define | TC_CMR_AEEVT_NONE (0x0u << 20) |

| (TC_CMR) None More... | |

| #define | TC_CMR_AEEVT_Pos 20 |

| #define | TC_CMR_AEEVT_SET (0x1u << 20) |

| (TC_CMR) Set More... | |

| #define | TC_CMR_AEEVT_TOGGLE (0x3u << 20) |

| (TC_CMR) Toggle More... | |

| #define | TC_CMR_ASWTRG(value) ((TC_CMR_ASWTRG_Msk & ((value) << TC_CMR_ASWTRG_Pos))) |

| #define | TC_CMR_ASWTRG_CLEAR (0x2u << 22) |

| (TC_CMR) Clear More... | |

| #define | TC_CMR_ASWTRG_Msk (0x3u << TC_CMR_ASWTRG_Pos) |

| (TC_CMR) Software Trigger Effect on TIOA More... | |

| #define | TC_CMR_ASWTRG_NONE (0x0u << 22) |

| (TC_CMR) None More... | |

| #define | TC_CMR_ASWTRG_Pos 22 |

| #define | TC_CMR_ASWTRG_SET (0x1u << 22) |

| (TC_CMR) Set More... | |

| #define | TC_CMR_ASWTRG_TOGGLE (0x3u << 22) |

| (TC_CMR) Toggle More... | |

| #define | TC_CMR_BCPB(value) ((TC_CMR_BCPB_Msk & ((value) << TC_CMR_BCPB_Pos))) |

| #define | TC_CMR_BCPB_CLEAR (0x2u << 24) |

| (TC_CMR) Clear More... | |

| #define | TC_CMR_BCPB_Msk (0x3u << TC_CMR_BCPB_Pos) |

| (TC_CMR) RB Compare Effect on TIOB More... | |

| #define | TC_CMR_BCPB_NONE (0x0u << 24) |

| (TC_CMR) None More... | |

| #define | TC_CMR_BCPB_Pos 24 |

| #define | TC_CMR_BCPB_SET (0x1u << 24) |

| (TC_CMR) Set More... | |

| #define | TC_CMR_BCPB_TOGGLE (0x3u << 24) |

| (TC_CMR) Toggle More... | |

| #define | TC_CMR_BCPC(value) ((TC_CMR_BCPC_Msk & ((value) << TC_CMR_BCPC_Pos))) |

| #define | TC_CMR_BCPC_CLEAR (0x2u << 26) |

| (TC_CMR) Clear More... | |

| #define | TC_CMR_BCPC_Msk (0x3u << TC_CMR_BCPC_Pos) |

| (TC_CMR) RC Compare Effect on TIOB More... | |

| #define | TC_CMR_BCPC_NONE (0x0u << 26) |

| (TC_CMR) None More... | |

| #define | TC_CMR_BCPC_Pos 26 |

| #define | TC_CMR_BCPC_SET (0x1u << 26) |

| (TC_CMR) Set More... | |

| #define | TC_CMR_BCPC_TOGGLE (0x3u << 26) |

| (TC_CMR) Toggle More... | |

| #define | TC_CMR_BEEVT(value) ((TC_CMR_BEEVT_Msk & ((value) << TC_CMR_BEEVT_Pos))) |

| #define | TC_CMR_BEEVT_CLEAR (0x2u << 28) |

| (TC_CMR) Clear More... | |

| #define | TC_CMR_BEEVT_Msk (0x3u << TC_CMR_BEEVT_Pos) |

| (TC_CMR) External Event Effect on TIOB More... | |

| #define | TC_CMR_BEEVT_NONE (0x0u << 28) |

| (TC_CMR) None More... | |

| #define | TC_CMR_BEEVT_Pos 28 |

| #define | TC_CMR_BEEVT_SET (0x1u << 28) |

| (TC_CMR) Set More... | |

| #define | TC_CMR_BEEVT_TOGGLE (0x3u << 28) |

| (TC_CMR) Toggle More... | |

| #define | TC_CMR_BSWTRG(value) ((TC_CMR_BSWTRG_Msk & ((value) << TC_CMR_BSWTRG_Pos))) |

| #define | TC_CMR_BSWTRG_CLEAR (0x2u << 30) |

| (TC_CMR) Clear More... | |

| #define | TC_CMR_BSWTRG_Msk (0x3u << TC_CMR_BSWTRG_Pos) |

| (TC_CMR) Software Trigger Effect on TIOB More... | |

| #define | TC_CMR_BSWTRG_NONE (0x0u << 30) |

| (TC_CMR) None More... | |

| #define | TC_CMR_BSWTRG_Pos 30 |

| #define | TC_CMR_BSWTRG_SET (0x1u << 30) |

| (TC_CMR) Set More... | |

| #define | TC_CMR_BSWTRG_TOGGLE (0x3u << 30) |

| (TC_CMR) Toggle More... | |

| #define | TC_CMR_BURST(value) ((TC_CMR_BURST_Msk & ((value) << TC_CMR_BURST_Pos))) |

| #define | TC_CMR_BURST_Msk (0x3u << TC_CMR_BURST_Pos) |

| (TC_CMR) Burst Signal Selection More... | |

| #define | TC_CMR_BURST_NONE (0x0u << 4) |

| (TC_CMR) The clock is not gated by an external signal. More... | |

| #define | TC_CMR_BURST_Pos 4 |

| #define | TC_CMR_BURST_XC0 (0x1u << 4) |

| (TC_CMR) XC0 is ANDed with the selected clock. More... | |

| #define | TC_CMR_BURST_XC1 (0x2u << 4) |

| (TC_CMR) XC1 is ANDed with the selected clock. More... | |

| #define | TC_CMR_BURST_XC2 (0x3u << 4) |

| (TC_CMR) XC2 is ANDed with the selected clock. More... | |

| #define | TC_CMR_CLKI (0x1u << 3) |

| (TC_CMR) Clock Invert More... | |

| #define | TC_CMR_CPCDIS (0x1u << 7) |

| (TC_CMR) Counter Clock Disable with RC Compare More... | |

| #define | TC_CMR_CPCSTOP (0x1u << 6) |

| (TC_CMR) Counter Clock Stopped with RC Compare More... | |

| #define | TC_CMR_CPCTRG (0x1u << 14) |

| (TC_CMR) RC Compare Trigger Enable More... | |

| #define | TC_CMR_EEVT(value) ((TC_CMR_EEVT_Msk & ((value) << TC_CMR_EEVT_Pos))) |

| #define | TC_CMR_EEVT_Msk (0x3u << TC_CMR_EEVT_Pos) |

| (TC_CMR) External Event Selection More... | |

| #define | TC_CMR_EEVT_Pos 10 |

| #define | TC_CMR_EEVT_TIOB (0x0u << 10) |

| (TC_CMR) TIOB More... | |

| #define | TC_CMR_EEVT_XC0 (0x1u << 10) |

| (TC_CMR) XC0 More... | |

| #define | TC_CMR_EEVT_XC1 (0x2u << 10) |

| (TC_CMR) XC1 More... | |

| #define | TC_CMR_EEVT_XC2 (0x3u << 10) |

| (TC_CMR) XC2 More... | |

| #define | TC_CMR_EEVTEDG(value) ((TC_CMR_EEVTEDG_Msk & ((value) << TC_CMR_EEVTEDG_Pos))) |

| #define | TC_CMR_EEVTEDG_EDGE (0x3u << 8) |

| (TC_CMR) Each edge More... | |

| #define | TC_CMR_EEVTEDG_FALLING (0x2u << 8) |

| (TC_CMR) Falling edge More... | |

| #define | TC_CMR_EEVTEDG_Msk (0x3u << TC_CMR_EEVTEDG_Pos) |

| (TC_CMR) External Event Edge Selection More... | |

| #define | TC_CMR_EEVTEDG_NONE (0x0u << 8) |

| (TC_CMR) None More... | |

| #define | TC_CMR_EEVTEDG_Pos 8 |

| #define | TC_CMR_EEVTEDG_RISING (0x1u << 8) |

| (TC_CMR) Rising edge More... | |

| #define | TC_CMR_ENETRG (0x1u << 12) |

| (TC_CMR) External Event Trigger Enable More... | |

| #define | TC_CMR_ETRGEDG(value) ((TC_CMR_ETRGEDG_Msk & ((value) << TC_CMR_ETRGEDG_Pos))) |

| #define | TC_CMR_ETRGEDG_EDGE (0x3u << 8) |

| (TC_CMR) Each edge More... | |

| #define | TC_CMR_ETRGEDG_FALLING (0x2u << 8) |

| (TC_CMR) Falling edge More... | |

| #define | TC_CMR_ETRGEDG_Msk (0x3u << TC_CMR_ETRGEDG_Pos) |

| (TC_CMR) External Trigger Edge Selection More... | |

| #define | TC_CMR_ETRGEDG_NONE (0x0u << 8) |

| (TC_CMR) The clock is not gated by an external signal. More... | |

| #define | TC_CMR_ETRGEDG_Pos 8 |

| #define | TC_CMR_ETRGEDG_RISING (0x1u << 8) |

| (TC_CMR) Rising edge More... | |

| #define | TC_CMR_LDBDIS (0x1u << 7) |

| (TC_CMR) Counter Clock Disable with RB Loading More... | |

| #define | TC_CMR_LDBSTOP (0x1u << 6) |

| (TC_CMR) Counter Clock Stopped with RB Loading More... | |

| #define | TC_CMR_LDRA(value) ((TC_CMR_LDRA_Msk & ((value) << TC_CMR_LDRA_Pos))) |

| #define | TC_CMR_LDRA_EDGE (0x3u << 16) |

| (TC_CMR) Each edge of TIOA More... | |

| #define | TC_CMR_LDRA_FALLING (0x2u << 16) |

| (TC_CMR) Falling edge of TIOA More... | |

| #define | TC_CMR_LDRA_Msk (0x3u << TC_CMR_LDRA_Pos) |

| (TC_CMR) RA Loading Edge Selection More... | |

| #define | TC_CMR_LDRA_NONE (0x0u << 16) |

| (TC_CMR) None More... | |

| #define | TC_CMR_LDRA_Pos 16 |

| #define | TC_CMR_LDRA_RISING (0x1u << 16) |

| (TC_CMR) Rising edge of TIOA More... | |

| #define | TC_CMR_LDRB(value) ((TC_CMR_LDRB_Msk & ((value) << TC_CMR_LDRB_Pos))) |

| #define | TC_CMR_LDRB_EDGE (0x3u << 18) |

| (TC_CMR) Each edge of TIOA More... | |

| #define | TC_CMR_LDRB_FALLING (0x2u << 18) |

| (TC_CMR) Falling edge of TIOA More... | |

| #define | TC_CMR_LDRB_Msk (0x3u << TC_CMR_LDRB_Pos) |

| (TC_CMR) RB Loading Edge Selection More... | |

| #define | TC_CMR_LDRB_NONE (0x0u << 18) |

| (TC_CMR) None More... | |

| #define | TC_CMR_LDRB_Pos 18 |

| #define | TC_CMR_LDRB_RISING (0x1u << 18) |

| (TC_CMR) Rising edge of TIOA More... | |

| #define | TC_CMR_SBSMPLR(value) ((TC_CMR_SBSMPLR_Msk & ((value) << TC_CMR_SBSMPLR_Pos))) |

| #define | TC_CMR_SBSMPLR_EIGHTH (0x3u << 20) |

| (TC_CMR) Load a Capture Register every 8 selected edges More... | |

| #define | TC_CMR_SBSMPLR_FOURTH (0x2u << 20) |

| (TC_CMR) Load a Capture Register every 4 selected edges More... | |

| #define | TC_CMR_SBSMPLR_HALF (0x1u << 20) |

| (TC_CMR) Load a Capture Register every 2 selected edges More... | |

| #define | TC_CMR_SBSMPLR_Msk (0x7u << TC_CMR_SBSMPLR_Pos) |

| (TC_CMR) Loading Edge Subsampling Ratio More... | |

| #define | TC_CMR_SBSMPLR_ONE (0x0u << 20) |

| (TC_CMR) Load a Capture Register each selected edge More... | |

| #define | TC_CMR_SBSMPLR_Pos 20 |

| #define | TC_CMR_SBSMPLR_SIXTEENTH (0x4u << 20) |

| (TC_CMR) Load a Capture Register every 16 selected edges More... | |

| #define | TC_CMR_TCCLKS(value) ((TC_CMR_TCCLKS_Msk & ((value) << TC_CMR_TCCLKS_Pos))) |

| #define | TC_CMR_TCCLKS_Msk (0x7u << TC_CMR_TCCLKS_Pos) |

| (TC_CMR) Clock Selection More... | |

| #define | TC_CMR_TCCLKS_Pos 0 |

| #define | TC_CMR_TCCLKS_TIMER_CLOCK1 (0x0u << 0) |

| (TC_CMR) Clock selected: internal PCK6 clock signal (from PMC) More... | |

| #define | TC_CMR_TCCLKS_TIMER_CLOCK2 (0x1u << 0) |

| (TC_CMR) Clock selected: internal MCK/8 clock signal (from PMC) More... | |

| #define | TC_CMR_TCCLKS_TIMER_CLOCK3 (0x2u << 0) |

| (TC_CMR) Clock selected: internal MCK/32 clock signal (from PMC) More... | |

| #define | TC_CMR_TCCLKS_TIMER_CLOCK4 (0x3u << 0) |

| (TC_CMR) Clock selected: internal MCK/128 clock signal (from PMC) More... | |

| #define | TC_CMR_TCCLKS_TIMER_CLOCK5 (0x4u << 0) |

| (TC_CMR) Clock selected: internal SLCK clock signal (from PMC) More... | |

| #define | TC_CMR_TCCLKS_XC0 (0x5u << 0) |

| (TC_CMR) Clock selected: XC0 More... | |

| #define | TC_CMR_TCCLKS_XC1 (0x6u << 0) |

| (TC_CMR) Clock selected: XC1 More... | |

| #define | TC_CMR_TCCLKS_XC2 (0x7u << 0) |

| (TC_CMR) Clock selected: XC2 More... | |

| #define | TC_CMR_WAVE (0x1u << 15) |

| (TC_CMR) Waveform Mode More... | |

| #define | TC_CMR_WAVSEL(value) ((TC_CMR_WAVSEL_Msk & ((value) << TC_CMR_WAVSEL_Pos))) |

| #define | TC_CMR_WAVSEL_Msk (0x3u << TC_CMR_WAVSEL_Pos) |

| (TC_CMR) Waveform Selection More... | |

| #define | TC_CMR_WAVSEL_Pos 13 |

| #define | TC_CMR_WAVSEL_UP (0x0u << 13) |

| (TC_CMR) UP mode without automatic trigger on RC Compare More... | |

| #define | TC_CMR_WAVSEL_UP_RC (0x2u << 13) |

| (TC_CMR) UP mode with automatic trigger on RC Compare More... | |

| #define | TC_CMR_WAVSEL_UPDOWN (0x1u << 13) |

| (TC_CMR) UPDOWN mode without automatic trigger on RC Compare More... | |

| #define | TC_CMR_WAVSEL_UPDOWN_RC (0x3u << 13) |

| (TC_CMR) UPDOWN mode with automatic trigger on RC Compare More... | |

| #define | TC_CV_CV_Msk (0xffffffffu << TC_CV_CV_Pos) |

| (TC_CV) Counter Value More... | |

| #define | TC_CV_CV_Pos 0 |

| #define | TC_EMR_NODIVCLK (0x1u << 8) |

| (TC_EMR) No Divided Clock More... | |

| #define | TC_EMR_TRIGSRCA(value) ((TC_EMR_TRIGSRCA_Msk & ((value) << TC_EMR_TRIGSRCA_Pos))) |

| #define | TC_EMR_TRIGSRCA_EXTERNAL_TIOAx (0x0u << 0) |

| (TC_EMR) The trigger/capture input A is driven by external pin TIOAx More... | |

| #define | TC_EMR_TRIGSRCA_Msk (0x3u << TC_EMR_TRIGSRCA_Pos) |

| (TC_EMR) Trigger Source for Input A More... | |

| #define | TC_EMR_TRIGSRCA_Pos 0 |

| #define | TC_EMR_TRIGSRCA_PWMx (0x1u << 0) |

| (TC_EMR) The trigger/capture input A is driven internally by PWMx More... | |

| #define | TC_EMR_TRIGSRCB(value) ((TC_EMR_TRIGSRCB_Msk & ((value) << TC_EMR_TRIGSRCB_Pos))) |

| #define | TC_EMR_TRIGSRCB_EXTERNAL_TIOBx (0x0u << 4) |

| (TC_EMR) The trigger/capture input B is driven by external pin TIOBx More... | |

| #define | TC_EMR_TRIGSRCB_Msk (0x3u << TC_EMR_TRIGSRCB_Pos) |

| (TC_EMR) Trigger Source for Input B More... | |

| #define | TC_EMR_TRIGSRCB_Pos 4 |

| #define | TC_EMR_TRIGSRCB_PWMx (0x1u << 4) |

| (TC_EMR) The trigger/capture input B is driven internally by PWMx More... | |

| #define | TC_FMR_ENCF0 (0x1u << 0) |

| (TC_FMR) Enable Compare Fault Channel 0 More... | |

| #define | TC_FMR_ENCF1 (0x1u << 1) |

| (TC_FMR) Enable Compare Fault Channel 1 More... | |

| #define | TC_IDR_COVFS (0x1u << 0) |

| (TC_IDR) Counter Overflow More... | |

| #define | TC_IDR_CPAS (0x1u << 2) |

| (TC_IDR) RA Compare More... | |

| #define | TC_IDR_CPBS (0x1u << 3) |

| (TC_IDR) RB Compare More... | |

| #define | TC_IDR_CPCS (0x1u << 4) |

| (TC_IDR) RC Compare More... | |

| #define | TC_IDR_ETRGS (0x1u << 7) |

| (TC_IDR) External Trigger More... | |

| #define | TC_IDR_LDRAS (0x1u << 5) |

| (TC_IDR) RA Loading More... | |

| #define | TC_IDR_LDRBS (0x1u << 6) |

| (TC_IDR) RB Loading More... | |

| #define | TC_IDR_LOVRS (0x1u << 1) |

| (TC_IDR) Load Overrun More... | |

| #define | TC_IER_COVFS (0x1u << 0) |

| (TC_IER) Counter Overflow More... | |

| #define | TC_IER_CPAS (0x1u << 2) |

| (TC_IER) RA Compare More... | |

| #define | TC_IER_CPBS (0x1u << 3) |

| (TC_IER) RB Compare More... | |

| #define | TC_IER_CPCS (0x1u << 4) |

| (TC_IER) RC Compare More... | |

| #define | TC_IER_ETRGS (0x1u << 7) |

| (TC_IER) External Trigger More... | |

| #define | TC_IER_LDRAS (0x1u << 5) |

| (TC_IER) RA Loading More... | |

| #define | TC_IER_LDRBS (0x1u << 6) |

| (TC_IER) RB Loading More... | |

| #define | TC_IER_LOVRS (0x1u << 1) |

| (TC_IER) Load Overrun More... | |

| #define | TC_IMR_COVFS (0x1u << 0) |

| (TC_IMR) Counter Overflow More... | |

| #define | TC_IMR_CPAS (0x1u << 2) |

| (TC_IMR) RA Compare More... | |

| #define | TC_IMR_CPBS (0x1u << 3) |

| (TC_IMR) RB Compare More... | |

| #define | TC_IMR_CPCS (0x1u << 4) |

| (TC_IMR) RC Compare More... | |

| #define | TC_IMR_ETRGS (0x1u << 7) |

| (TC_IMR) External Trigger More... | |

| #define | TC_IMR_LDRAS (0x1u << 5) |

| (TC_IMR) RA Loading More... | |

| #define | TC_IMR_LDRBS (0x1u << 6) |

| (TC_IMR) RB Loading More... | |

| #define | TC_IMR_LOVRS (0x1u << 1) |

| (TC_IMR) Load Overrun More... | |

| #define | TC_QIDR_DIRCHG (0x1u << 1) |

| (TC_QIDR) Direction Change More... | |

| #define | TC_QIDR_IDX (0x1u << 0) |

| (TC_QIDR) Index More... | |

| #define | TC_QIDR_QERR (0x1u << 2) |

| (TC_QIDR) Quadrature Error More... | |

| #define | TC_QIER_DIRCHG (0x1u << 1) |

| (TC_QIER) Direction Change More... | |

| #define | TC_QIER_IDX (0x1u << 0) |

| (TC_QIER) Index More... | |

| #define | TC_QIER_QERR (0x1u << 2) |

| (TC_QIER) Quadrature Error More... | |

| #define | TC_QIMR_DIRCHG (0x1u << 1) |

| (TC_QIMR) Direction Change More... | |

| #define | TC_QIMR_IDX (0x1u << 0) |

| (TC_QIMR) Index More... | |

| #define | TC_QIMR_QERR (0x1u << 2) |

| (TC_QIMR) Quadrature Error More... | |

| #define | TC_QISR_DIR (0x1u << 8) |

| (TC_QISR) Direction More... | |

| #define | TC_QISR_DIRCHG (0x1u << 1) |

| (TC_QISR) Direction Change More... | |

| #define | TC_QISR_IDX (0x1u << 0) |

| (TC_QISR) Index More... | |

| #define | TC_QISR_QERR (0x1u << 2) |

| (TC_QISR) Quadrature Error More... | |

| #define | TC_RA_RA(value) ((TC_RA_RA_Msk & ((value) << TC_RA_RA_Pos))) |

| #define | TC_RA_RA_Msk (0xffffffffu << TC_RA_RA_Pos) |

| (TC_RA) Register A More... | |

| #define | TC_RA_RA_Pos 0 |

| #define | TC_RAB_RAB_Msk (0xffffffffu << TC_RAB_RAB_Pos) |

| (TC_RAB) Register A or Register B More... | |

| #define | TC_RAB_RAB_Pos 0 |

| #define | TC_RB_RB(value) ((TC_RB_RB_Msk & ((value) << TC_RB_RB_Pos))) |

| #define | TC_RB_RB_Msk (0xffffffffu << TC_RB_RB_Pos) |

| (TC_RB) Register B More... | |

| #define | TC_RB_RB_Pos 0 |

| #define | TC_RC_RC(value) ((TC_RC_RC_Msk & ((value) << TC_RC_RC_Pos))) |

| #define | TC_RC_RC_Msk (0xffffffffu << TC_RC_RC_Pos) |

| (TC_RC) Register C More... | |

| #define | TC_RC_RC_Pos 0 |

| #define | TC_SMMR_DOWN (0x1u << 1) |

| (TC_SMMR) Down Count More... | |

| #define | TC_SMMR_GCEN (0x1u << 0) |

| (TC_SMMR) Gray Count Enable More... | |

| #define | TC_SR_CLKSTA (0x1u << 16) |

| (TC_SR) Clock Enabling Status More... | |

| #define | TC_SR_COVFS (0x1u << 0) |

| (TC_SR) Counter Overflow Status (cleared on read) More... | |

| #define | TC_SR_CPAS (0x1u << 2) |

| (TC_SR) RA Compare Status (cleared on read) More... | |

| #define | TC_SR_CPBS (0x1u << 3) |

| (TC_SR) RB Compare Status (cleared on read) More... | |

| #define | TC_SR_CPCS (0x1u << 4) |

| (TC_SR) RC Compare Status (cleared on read) More... | |

| #define | TC_SR_ETRGS (0x1u << 7) |

| (TC_SR) External Trigger Status (cleared on read) More... | |

| #define | TC_SR_LDRAS (0x1u << 5) |

| (TC_SR) RA Loading Status (cleared on read) More... | |

| #define | TC_SR_LDRBS (0x1u << 6) |

| (TC_SR) RB Loading Status (cleared on read) More... | |

| #define | TC_SR_LOVRS (0x1u << 1) |

| (TC_SR) Load Overrun Status (cleared on read) More... | |

| #define | TC_SR_MTIOA (0x1u << 17) |

| (TC_SR) TIOA Mirror More... | |

| #define | TC_SR_MTIOB (0x1u << 18) |

| (TC_SR) TIOB Mirror More... | |

| #define | TC_VER_MFN_Msk (0x7u << TC_VER_MFN_Pos) |

| (TC_VER) Metal Fix Number More... | |

| #define | TC_VER_MFN_Pos 16 |

| #define | TC_VER_VERSION_Msk (0xfffu << TC_VER_VERSION_Pos) |

| (TC_VER) Version of the Hardware Module More... | |

| #define | TC_VER_VERSION_Pos 0 |

| #define | TC_WPMR_WPEN (0x1u << 0) |

| (TC_WPMR) Write Protection Enable More... | |

| #define | TC_WPMR_WPKEY(value) ((TC_WPMR_WPKEY_Msk & ((value) << TC_WPMR_WPKEY_Pos))) |

| #define | TC_WPMR_WPKEY_Msk (0xffffffu << TC_WPMR_WPKEY_Pos) |

| (TC_WPMR) Write Protection Key More... | |

| #define | TC_WPMR_WPKEY_PASSWD (0x54494Du << 8) |

| (TC_WPMR) Writing any other value in this field aborts the write operation of the WPEN bit.Always reads as 0. More... | |

| #define | TC_WPMR_WPKEY_Pos 8 |

| #define | TCCHANNEL_NUMBER 3 |

| Tc hardware registers. More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file utils/cmsis/same70/include/component/tc.h.