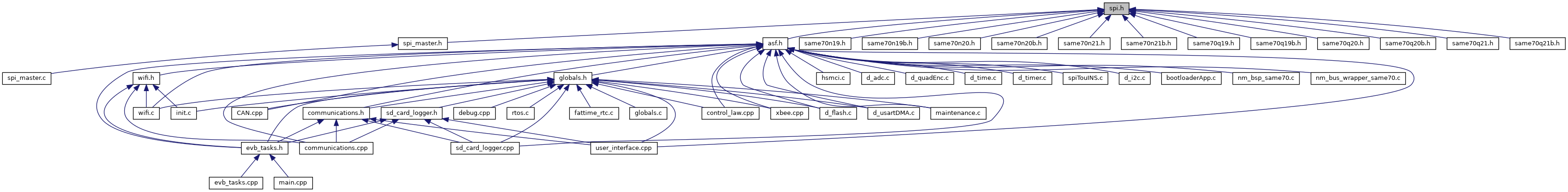

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Spi |

| Spi hardware registers. More... | |

Macros | |

| #define | SPI_CR_FIFODIS (0x1u << 31) |

| (SPI_CR) FIFO Disable More... | |

| #define | SPI_CR_FIFOEN (0x1u << 30) |

| (SPI_CR) FIFO Enable More... | |

| #define | SPI_CR_LASTXFER (0x1u << 24) |

| (SPI_CR) Last Transfer More... | |

| #define | SPI_CR_REQCLR (0x1u << 12) |

| (SPI_CR) Request to Clear the Comparison Trigger More... | |

| #define | SPI_CR_RXFCLR (0x1u << 17) |

| (SPI_CR) Receive FIFO Clear More... | |

| #define | SPI_CR_SPIDIS (0x1u << 1) |

| (SPI_CR) SPI Disable More... | |

| #define | SPI_CR_SPIEN (0x1u << 0) |

| (SPI_CR) SPI Enable More... | |

| #define | SPI_CR_SWRST (0x1u << 7) |

| (SPI_CR) SPI Software Reset More... | |

| #define | SPI_CR_TXFCLR (0x1u << 16) |

| (SPI_CR) Transmit FIFO Clear More... | |

| #define | SPI_CSR_BITS(value) ((SPI_CSR_BITS_Msk & ((value) << SPI_CSR_BITS_Pos))) |

| #define | SPI_CSR_BITS_10_BIT (0x2u << 4) |

| (SPI_CSR[4]) 10 bits for transfer More... | |

| #define | SPI_CSR_BITS_11_BIT (0x3u << 4) |

| (SPI_CSR[4]) 11 bits for transfer More... | |

| #define | SPI_CSR_BITS_12_BIT (0x4u << 4) |

| (SPI_CSR[4]) 12 bits for transfer More... | |

| #define | SPI_CSR_BITS_13_BIT (0x5u << 4) |

| (SPI_CSR[4]) 13 bits for transfer More... | |

| #define | SPI_CSR_BITS_14_BIT (0x6u << 4) |

| (SPI_CSR[4]) 14 bits for transfer More... | |

| #define | SPI_CSR_BITS_15_BIT (0x7u << 4) |

| (SPI_CSR[4]) 15 bits for transfer More... | |

| #define | SPI_CSR_BITS_16_BIT (0x8u << 4) |

| (SPI_CSR[4]) 16 bits for transfer More... | |

| #define | SPI_CSR_BITS_8_BIT (0x0u << 4) |

| (SPI_CSR[4]) 8 bits for transfer More... | |

| #define | SPI_CSR_BITS_9_BIT (0x1u << 4) |

| (SPI_CSR[4]) 9 bits for transfer More... | |

| #define | SPI_CSR_BITS_Msk (0xfu << SPI_CSR_BITS_Pos) |

| (SPI_CSR[4]) Bits Per Transfer More... | |

| #define | SPI_CSR_BITS_Pos 4 |

| #define | SPI_CSR_CPOL (0x1u << 0) |

| (SPI_CSR[4]) Clock Polarity More... | |

| #define | SPI_CSR_CSAAT (0x1u << 3) |

| (SPI_CSR[4]) Chip Select Active After Transfer More... | |

| #define | SPI_CSR_CSNAAT (0x1u << 2) |

| (SPI_CSR[4]) Chip Select Not Active After Transfer (Ignored if CSAAT = 1) More... | |

| #define | SPI_CSR_DLYBCT(value) ((SPI_CSR_DLYBCT_Msk & ((value) << SPI_CSR_DLYBCT_Pos))) |

| #define | SPI_CSR_DLYBCT_Msk (0xffu << SPI_CSR_DLYBCT_Pos) |

| (SPI_CSR[4]) Delay Between Consecutive Transfers More... | |

| #define | SPI_CSR_DLYBCT_Pos 24 |

| #define | SPI_CSR_DLYBS(value) ((SPI_CSR_DLYBS_Msk & ((value) << SPI_CSR_DLYBS_Pos))) |

| #define | SPI_CSR_DLYBS_Msk (0xffu << SPI_CSR_DLYBS_Pos) |

| (SPI_CSR[4]) Delay Before SPCK More... | |

| #define | SPI_CSR_DLYBS_Pos 16 |

| #define | SPI_CSR_NCPHA (0x1u << 1) |

| (SPI_CSR[4]) Clock Phase More... | |

| #define | SPI_CSR_SCBR(value) ((SPI_CSR_SCBR_Msk & ((value) << SPI_CSR_SCBR_Pos))) |

| #define | SPI_CSR_SCBR_Msk (0xffu << SPI_CSR_SCBR_Pos) |

| (SPI_CSR[4]) Serial Clock Bit Rate More... | |

| #define | SPI_CSR_SCBR_Pos 8 |

| #define | SPI_IDR_MODF (0x1u << 2) |

| (SPI_IDR) Mode Fault Error Interrupt Disable More... | |

| #define | SPI_IDR_NSSR (0x1u << 8) |

| (SPI_IDR) NSS Rising Interrupt Disable More... | |

| #define | SPI_IDR_OVRES (0x1u << 3) |

| (SPI_IDR) Overrun Error Interrupt Disable More... | |

| #define | SPI_IDR_RDRF (0x1u << 0) |

| (SPI_IDR) Receive Data Register Full Interrupt Disable More... | |

| #define | SPI_IDR_TDRE (0x1u << 1) |

| (SPI_IDR) SPI Transmit Data Register Empty Interrupt Disable More... | |

| #define | SPI_IDR_TXEMPTY (0x1u << 9) |

| (SPI_IDR) Transmission Registers Empty Disable More... | |

| #define | SPI_IDR_UNDES (0x1u << 10) |

| (SPI_IDR) Underrun Error Interrupt Disable More... | |

| #define | SPI_IER_MODF (0x1u << 2) |

| (SPI_IER) Mode Fault Error Interrupt Enable More... | |

| #define | SPI_IER_NSSR (0x1u << 8) |

| (SPI_IER) NSS Rising Interrupt Enable More... | |

| #define | SPI_IER_OVRES (0x1u << 3) |

| (SPI_IER) Overrun Error Interrupt Enable More... | |

| #define | SPI_IER_RDRF (0x1u << 0) |

| (SPI_IER) Receive Data Register Full Interrupt Enable More... | |

| #define | SPI_IER_TDRE (0x1u << 1) |

| (SPI_IER) SPI Transmit Data Register Empty Interrupt Enable More... | |

| #define | SPI_IER_TXEMPTY (0x1u << 9) |

| (SPI_IER) Transmission Registers Empty Enable More... | |

| #define | SPI_IER_UNDES (0x1u << 10) |

| (SPI_IER) Underrun Error Interrupt Enable More... | |

| #define | SPI_IMR_MODF (0x1u << 2) |

| (SPI_IMR) Mode Fault Error Interrupt Mask More... | |

| #define | SPI_IMR_NSSR (0x1u << 8) |

| (SPI_IMR) NSS Rising Interrupt Mask More... | |

| #define | SPI_IMR_OVRES (0x1u << 3) |

| (SPI_IMR) Overrun Error Interrupt Mask More... | |

| #define | SPI_IMR_RDRF (0x1u << 0) |

| (SPI_IMR) Receive Data Register Full Interrupt Mask More... | |

| #define | SPI_IMR_TDRE (0x1u << 1) |

| (SPI_IMR) SPI Transmit Data Register Empty Interrupt Mask More... | |

| #define | SPI_IMR_TXEMPTY (0x1u << 9) |

| (SPI_IMR) Transmission Registers Empty Mask More... | |

| #define | SPI_IMR_UNDES (0x1u << 10) |

| (SPI_IMR) Underrun Error Interrupt Mask More... | |

| #define | SPI_MR_DLYBCS(value) ((SPI_MR_DLYBCS_Msk & ((value) << SPI_MR_DLYBCS_Pos))) |

| #define | SPI_MR_DLYBCS_Msk (0xffu << SPI_MR_DLYBCS_Pos) |

| (SPI_MR) Delay Between Chip Selects More... | |

| #define | SPI_MR_DLYBCS_Pos 24 |

| #define | SPI_MR_LLB (0x1u << 7) |

| (SPI_MR) Local Loopback Enable More... | |

| #define | SPI_MR_MODFDIS (0x1u << 4) |

| (SPI_MR) Mode Fault Detection More... | |

| #define | SPI_MR_MSTR (0x1u << 0) |

| (SPI_MR) Master/Slave Mode More... | |

| #define | SPI_MR_PCS(value) ((SPI_MR_PCS_Msk & ((value) << SPI_MR_PCS_Pos))) |

| #define | SPI_MR_PCS_Msk (0xfu << SPI_MR_PCS_Pos) |

| (SPI_MR) Peripheral Chip Select More... | |

| #define | SPI_MR_PCS_Pos 16 |

| #define | SPI_MR_PCSDEC (0x1u << 2) |

| (SPI_MR) Chip Select Decode More... | |

| #define | SPI_MR_PS (0x1u << 1) |

| (SPI_MR) Peripheral Select More... | |

| #define | SPI_MR_WDRBT (0x1u << 5) |

| (SPI_MR) Wait Data Read Before Transfer More... | |

| #define | SPI_RDR_PCS_Msk (0xfu << SPI_RDR_PCS_Pos) |

| (SPI_RDR) Peripheral Chip Select More... | |

| #define | SPI_RDR_PCS_Pos 16 |

| #define | SPI_RDR_RD_Msk (0xffffu << SPI_RDR_RD_Pos) |

| (SPI_RDR) Receive Data More... | |

| #define | SPI_RDR_RD_Pos 0 |

| #define | SPI_SR_MODF (0x1u << 2) |

| (SPI_SR) Mode Fault Error (cleared on read) More... | |

| #define | SPI_SR_NSSR (0x1u << 8) |

| (SPI_SR) NSS Rising (cleared on read) More... | |

| #define | SPI_SR_OVRES (0x1u << 3) |

| (SPI_SR) Overrun Error Status (cleared on read) More... | |

| #define | SPI_SR_RDRF (0x1u << 0) |

| (SPI_SR) Receive Data Register Full (cleared by reading SPI_RDR) More... | |

| #define | SPI_SR_SPIENS (0x1u << 16) |

| (SPI_SR) SPI Enable Status More... | |

| #define | SPI_SR_TDRE (0x1u << 1) |

| (SPI_SR) Transmit Data Register Empty (cleared by writing SPI_TDR) More... | |

| #define | SPI_SR_TXEMPTY (0x1u << 9) |

| (SPI_SR) Transmission Registers Empty (cleared by writing SPI_TDR) More... | |

| #define | SPI_SR_UNDES (0x1u << 10) |

| (SPI_SR) Underrun Error Status (Slave mode only) (cleared on read) More... | |

| #define | SPI_TDR_LASTXFER (0x1u << 24) |

| (SPI_TDR) Last Transfer More... | |

| #define | SPI_TDR_PCS(value) ((SPI_TDR_PCS_Msk & ((value) << SPI_TDR_PCS_Pos))) |

| #define | SPI_TDR_PCS_Msk (0xfu << SPI_TDR_PCS_Pos) |

| (SPI_TDR) Peripheral Chip Select More... | |

| #define | SPI_TDR_PCS_Pos 16 |

| #define | SPI_TDR_TD(value) ((SPI_TDR_TD_Msk & ((value) << SPI_TDR_TD_Pos))) |

| #define | SPI_TDR_TD_Msk (0xffffu << SPI_TDR_TD_Pos) |

| (SPI_TDR) Transmit Data More... | |

| #define | SPI_TDR_TD_Pos 0 |

| #define | SPI_VERSION_MFN_Msk (0x7u << SPI_VERSION_MFN_Pos) |

| (SPI_VERSION) Metal Fix Number More... | |

| #define | SPI_VERSION_MFN_Pos 16 |

| #define | SPI_VERSION_VERSION_Msk (0xfffu << SPI_VERSION_VERSION_Pos) |

| (SPI_VERSION) Version of the Hardware Module More... | |

| #define | SPI_VERSION_VERSION_Pos 0 |

| #define | SPI_WPMR_WPEN (0x1u << 0) |

| (SPI_WPMR) Write Protection Enable More... | |

| #define | SPI_WPMR_WPKEY(value) ((SPI_WPMR_WPKEY_Msk & ((value) << SPI_WPMR_WPKEY_Pos))) |

| #define | SPI_WPMR_WPKEY_Msk (0xffffffu << SPI_WPMR_WPKEY_Pos) |

| (SPI_WPMR) Write Protection Key More... | |

| #define | SPI_WPMR_WPKEY_PASSWD (0x535049u << 8) |

| (SPI_WPMR) Writing any other value in this field aborts the write operation of the WPEN bit.Always reads as 0. More... | |

| #define | SPI_WPMR_WPKEY_Pos 8 |

| #define | SPI_WPSR_WPVS (0x1u << 0) |

| (SPI_WPSR) Write Protection Violation Status More... | |

| #define | SPI_WPSR_WPVSRC_Msk (0xffu << SPI_WPSR_WPVSRC_Pos) |

| (SPI_WPSR) Write Protection Violation Source More... | |

| #define | SPI_WPSR_WPVSRC_Pos 8 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file utils/cmsis/same70/include/component/spi.h.