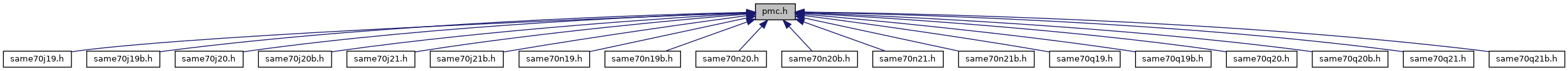

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Pmc |

| Pmc hardware registers. More... | |

Macros | |

| #define | CKGR_MCFR_CCSS (0x1u << 24) |

| (CKGR_MCFR) Counter Clock Source Selection More... | |

| #define | CKGR_MCFR_MAINF(value) ((CKGR_MCFR_MAINF_Msk & ((value) << CKGR_MCFR_MAINF_Pos))) |

| #define | CKGR_MCFR_MAINF_Msk (0xffffu << CKGR_MCFR_MAINF_Pos) |

| (CKGR_MCFR) Main Clock Frequency More... | |

| #define | CKGR_MCFR_MAINF_Pos 0 |

| #define | CKGR_MCFR_MAINFRDY (0x1u << 16) |

| (CKGR_MCFR) Main Clock Frequency Measure Ready More... | |

| #define | CKGR_MCFR_RCMEAS (0x1u << 20) |

| (CKGR_MCFR) RC Oscillator Frequency Measure (write-only) More... | |

| #define | CKGR_MOR_CFDEN (0x1u << 25) |

| (CKGR_MOR) Clock Failure Detector Enable More... | |

| #define | CKGR_MOR_KEY(value) ((CKGR_MOR_KEY_Msk & ((value) << CKGR_MOR_KEY_Pos))) |

| #define | CKGR_MOR_KEY_Msk (0xffu << CKGR_MOR_KEY_Pos) |

| (CKGR_MOR) Write Access Password More... | |

| #define | CKGR_MOR_KEY_PASSWD (0x37u << 16) |

| (CKGR_MOR) Writing any other value in this field aborts the write operation.Always reads as 0. More... | |

| #define | CKGR_MOR_KEY_Pos 16 |

| #define | CKGR_MOR_MOSCRCEN (0x1u << 3) |

| (CKGR_MOR) Main On-Chip RC Oscillator Enable More... | |

| #define | CKGR_MOR_MOSCRCF(value) ((CKGR_MOR_MOSCRCF_Msk & ((value) << CKGR_MOR_MOSCRCF_Pos))) |

| #define | CKGR_MOR_MOSCRCF_12_MHz (0x2u << 4) |

| (CKGR_MOR) Fast RC oscillator frequency is at 12 MHz More... | |

| #define | CKGR_MOR_MOSCRCF_4_MHz (0x0u << 4) |

| (CKGR_MOR) Fast RC oscillator frequency is at 4 MHz (default) More... | |

| #define | CKGR_MOR_MOSCRCF_8_MHz (0x1u << 4) |

| (CKGR_MOR) Fast RC oscillator frequency is at 8 MHz More... | |

| #define | CKGR_MOR_MOSCRCF_Msk (0x7u << CKGR_MOR_MOSCRCF_Pos) |

| (CKGR_MOR) Main On-Chip RC Oscillator Frequency Selection More... | |

| #define | CKGR_MOR_MOSCRCF_Pos 4 |

| #define | CKGR_MOR_MOSCSEL (0x1u << 24) |

| (CKGR_MOR) Main Oscillator Selection More... | |

| #define | CKGR_MOR_MOSCXTBY (0x1u << 1) |

| (CKGR_MOR) Main Crystal Oscillator Bypass More... | |

| #define | CKGR_MOR_MOSCXTEN (0x1u << 0) |

| (CKGR_MOR) Main Crystal Oscillator Enable More... | |

| #define | CKGR_MOR_MOSCXTST(value) ((CKGR_MOR_MOSCXTST_Msk & ((value) << CKGR_MOR_MOSCXTST_Pos))) |

| #define | CKGR_MOR_MOSCXTST_Msk (0xffu << CKGR_MOR_MOSCXTST_Pos) |

| (CKGR_MOR) Main Crystal Oscillator Start-up Time More... | |

| #define | CKGR_MOR_MOSCXTST_Pos 8 |

| #define | CKGR_MOR_WAITMODE (0x1u << 2) |

| (CKGR_MOR) Wait Mode Command (Write-only) More... | |

| #define | CKGR_MOR_XT32KFME (0x1u << 26) |

| (CKGR_MOR) Slow Crystal Oscillator Frequency Monitoring Enable More... | |

| #define | CKGR_PLLAR_DIVA(value) ((CKGR_PLLAR_DIVA_Msk & ((value) << CKGR_PLLAR_DIVA_Pos))) |

| #define | CKGR_PLLAR_DIVA_0 (0x0u << 0) |

| (CKGR_PLLAR) Divider output is 0 and PLLA is disabled. More... | |

| #define | CKGR_PLLAR_DIVA_BYPASS (0x1u << 0) |

| (CKGR_PLLAR) Divider is bypassed (divide by 1) and PLLA is enabled. More... | |

| #define | CKGR_PLLAR_DIVA_Msk (0xffu << CKGR_PLLAR_DIVA_Pos) |

| (CKGR_PLLAR) PLLA Front End Divider More... | |

| #define | CKGR_PLLAR_DIVA_Pos 0 |

| #define | CKGR_PLLAR_MULA(value) ((CKGR_PLLAR_MULA_Msk & ((value) << CKGR_PLLAR_MULA_Pos))) |

| #define | CKGR_PLLAR_MULA_Msk (0x7ffu << CKGR_PLLAR_MULA_Pos) |

| (CKGR_PLLAR) PLLA Multiplier More... | |

| #define | CKGR_PLLAR_MULA_Pos 16 |

| #define | CKGR_PLLAR_ONE (0x1u << 29) |

| (CKGR_PLLAR) Must Be Set to 1 More... | |

| #define | CKGR_PLLAR_PLLACOUNT(value) ((CKGR_PLLAR_PLLACOUNT_Msk & ((value) << CKGR_PLLAR_PLLACOUNT_Pos))) |

| #define | CKGR_PLLAR_PLLACOUNT_Msk (0x3fu << CKGR_PLLAR_PLLACOUNT_Pos) |

| (CKGR_PLLAR) PLLA Counter More... | |

| #define | CKGR_PLLAR_PLLACOUNT_Pos 8 |

| #define | CKGR_UCKR_UPLLCOUNT(value) ((CKGR_UCKR_UPLLCOUNT_Msk & ((value) << CKGR_UCKR_UPLLCOUNT_Pos))) |

| #define | CKGR_UCKR_UPLLCOUNT_Msk (0xfu << CKGR_UCKR_UPLLCOUNT_Pos) |

| (CKGR_UCKR) UTMI PLL Start-up Time More... | |

| #define | CKGR_UCKR_UPLLCOUNT_Pos 20 |

| #define | CKGR_UCKR_UPLLEN (0x1u << 16) |

| (CKGR_UCKR) UTMI PLL Enable More... | |

| #define | PMC_APLLACR_BIAS(value) ((PMC_APLLACR_BIAS_Msk & ((value) << PMC_APLLACR_BIAS_Pos))) |

| #define | PMC_APLLACR_BIAS_Msk (0x3u << PMC_APLLACR_BIAS_Pos) |

| (PMC_APLLACR) Bias Voltage Selection More... | |

| #define | PMC_APLLACR_BIAS_Pos 8 |

| #define | PMC_APLLACR_DCOFLTSEL(value) ((PMC_APLLACR_DCOFLTSEL_Msk & ((value) << PMC_APLLACR_DCOFLTSEL_Pos))) |

| #define | PMC_APLLACR_DCOFLTSEL_Msk (0xfu << PMC_APLLACR_DCOFLTSEL_Pos) |

| (PMC_APLLACR) DCO Filter Selection More... | |

| #define | PMC_APLLACR_DCOFLTSEL_Pos 0 |

| #define | PMC_APLLACR_FLTSEL(value) ((PMC_APLLACR_FLTSEL_Msk & ((value) << PMC_APLLACR_FLTSEL_Pos))) |

| #define | PMC_APLLACR_FLTSEL_Msk (0xfu << PMC_APLLACR_FLTSEL_Pos) |

| (PMC_APLLACR) PLL Filter Selection More... | |

| #define | PMC_APLLACR_FLTSEL_Pos 4 |

| #define | PMC_FOCR_FOCLR (0x1u << 0) |

| (PMC_FOCR) Fault Output Clear More... | |

| #define | PMC_FSMR_FFLPM (0x1u << 23) |

| (PMC_FSMR) Force Flash Low-power Mode More... | |

| #define | PMC_FSMR_FLPM(value) ((PMC_FSMR_FLPM_Msk & ((value) << PMC_FSMR_FLPM_Pos))) |

| #define | PMC_FSMR_FLPM_FLASH_DEEP_POWERDOWN (0x1u << 21) |

| (PMC_FSMR) Flash is in Deep-power-down mode when system enters Wait Mode More... | |

| #define | PMC_FSMR_FLPM_FLASH_IDLE (0x2u << 21) |

| (PMC_FSMR) Idle mode More... | |

| #define | PMC_FSMR_FLPM_FLASH_STANDBY (0x0u << 21) |

| (PMC_FSMR) Flash is in Standby Mode when system enters Wait Mode More... | |

| #define | PMC_FSMR_FLPM_Msk (0x3u << PMC_FSMR_FLPM_Pos) |

| (PMC_FSMR) Flash Low-power Mode More... | |

| #define | PMC_FSMR_FLPM_Pos 21 |

| #define | PMC_FSMR_FSTT0 (0x1u << 0) |

| (PMC_FSMR) Fast Startup Input Enable 0 More... | |

| #define | PMC_FSMR_FSTT1 (0x1u << 1) |

| (PMC_FSMR) Fast Startup Input Enable 1 More... | |

| #define | PMC_FSMR_FSTT10 (0x1u << 10) |

| (PMC_FSMR) Fast Startup Input Enable 10 More... | |

| #define | PMC_FSMR_FSTT11 (0x1u << 11) |

| (PMC_FSMR) Fast Startup Input Enable 11 More... | |

| #define | PMC_FSMR_FSTT12 (0x1u << 12) |

| (PMC_FSMR) Fast Startup Input Enable 12 More... | |

| #define | PMC_FSMR_FSTT13 (0x1u << 13) |

| (PMC_FSMR) Fast Startup Input Enable 13 More... | |

| #define | PMC_FSMR_FSTT14 (0x1u << 14) |

| (PMC_FSMR) Fast Startup Input Enable 14 More... | |

| #define | PMC_FSMR_FSTT15 (0x1u << 15) |

| (PMC_FSMR) Fast Startup Input Enable 15 More... | |

| #define | PMC_FSMR_FSTT2 (0x1u << 2) |

| (PMC_FSMR) Fast Startup Input Enable 2 More... | |

| #define | PMC_FSMR_FSTT3 (0x1u << 3) |

| (PMC_FSMR) Fast Startup Input Enable 3 More... | |

| #define | PMC_FSMR_FSTT4 (0x1u << 4) |

| (PMC_FSMR) Fast Startup Input Enable 4 More... | |

| #define | PMC_FSMR_FSTT5 (0x1u << 5) |

| (PMC_FSMR) Fast Startup Input Enable 5 More... | |

| #define | PMC_FSMR_FSTT6 (0x1u << 6) |

| (PMC_FSMR) Fast Startup Input Enable 6 More... | |

| #define | PMC_FSMR_FSTT7 (0x1u << 7) |

| (PMC_FSMR) Fast Startup Input Enable 7 More... | |

| #define | PMC_FSMR_FSTT8 (0x1u << 8) |

| (PMC_FSMR) Fast Startup Input Enable 8 More... | |

| #define | PMC_FSMR_FSTT9 (0x1u << 9) |

| (PMC_FSMR) Fast Startup Input Enable 9 More... | |

| #define | PMC_FSMR_LPM (0x1u << 20) |

| (PMC_FSMR) Low-power Mode More... | |

| #define | PMC_FSMR_RTCAL (0x1u << 17) |

| (PMC_FSMR) RTC Alarm Enable More... | |

| #define | PMC_FSMR_RTTAL (0x1u << 16) |

| (PMC_FSMR) RTT Alarm Enable More... | |

| #define | PMC_FSMR_USBAL (0x1u << 18) |

| (PMC_FSMR) USB Alarm Enable More... | |

| #define | PMC_FSPR_FSTP0 (0x1u << 0) |

| (PMC_FSPR) Fast Startup Input Polarity 0 More... | |

| #define | PMC_FSPR_FSTP1 (0x1u << 1) |

| (PMC_FSPR) Fast Startup Input Polarity 1 More... | |

| #define | PMC_FSPR_FSTP10 (0x1u << 10) |

| (PMC_FSPR) Fast Startup Input Polarity 10 More... | |

| #define | PMC_FSPR_FSTP11 (0x1u << 11) |

| (PMC_FSPR) Fast Startup Input Polarity 11 More... | |

| #define | PMC_FSPR_FSTP12 (0x1u << 12) |

| (PMC_FSPR) Fast Startup Input Polarity 12 More... | |

| #define | PMC_FSPR_FSTP13 (0x1u << 13) |

| (PMC_FSPR) Fast Startup Input Polarity 13 More... | |

| #define | PMC_FSPR_FSTP14 (0x1u << 14) |

| (PMC_FSPR) Fast Startup Input Polarity 14 More... | |

| #define | PMC_FSPR_FSTP15 (0x1u << 15) |

| (PMC_FSPR) Fast Startup Input Polarity 15 More... | |

| #define | PMC_FSPR_FSTP2 (0x1u << 2) |

| (PMC_FSPR) Fast Startup Input Polarity 2 More... | |

| #define | PMC_FSPR_FSTP3 (0x1u << 3) |

| (PMC_FSPR) Fast Startup Input Polarity 3 More... | |

| #define | PMC_FSPR_FSTP4 (0x1u << 4) |

| (PMC_FSPR) Fast Startup Input Polarity 4 More... | |

| #define | PMC_FSPR_FSTP5 (0x1u << 5) |

| (PMC_FSPR) Fast Startup Input Polarity 5 More... | |

| #define | PMC_FSPR_FSTP6 (0x1u << 6) |

| (PMC_FSPR) Fast Startup Input Polarity 6 More... | |

| #define | PMC_FSPR_FSTP7 (0x1u << 7) |

| (PMC_FSPR) Fast Startup Input Polarity 7 More... | |

| #define | PMC_FSPR_FSTP8 (0x1u << 8) |

| (PMC_FSPR) Fast Startup Input Polarity 8 More... | |

| #define | PMC_FSPR_FSTP9 (0x1u << 9) |

| (PMC_FSPR) Fast Startup Input Polarity 9 More... | |

| #define | PMC_IDR_CFDEV (0x1u << 18) |

| (PMC_IDR) Clock Failure Detector Event Interrupt Disable More... | |

| #define | PMC_IDR_LOCKA (0x1u << 1) |

| (PMC_IDR) PLLA Lock Interrupt Disable More... | |

| #define | PMC_IDR_LOCKU (0x1u << 6) |

| (PMC_IDR) UTMI PLL Lock Interrupt Disable More... | |

| #define | PMC_IDR_MCKRDY (0x1u << 3) |

| (PMC_IDR) Master Clock Ready Interrupt Disable More... | |

| #define | PMC_IDR_MOSCRCS (0x1u << 17) |

| (PMC_IDR) Main On-Chip RC Status Interrupt Disable More... | |

| #define | PMC_IDR_MOSCSELS (0x1u << 16) |

| (PMC_IDR) Main Oscillator Selection Status Interrupt Disable More... | |

| #define | PMC_IDR_MOSCXTS (0x1u << 0) |

| (PMC_IDR) Main Crystal Oscillator Status Interrupt Disable More... | |

| #define | PMC_IDR_PCKRDY0 (0x1u << 8) |

| (PMC_IDR) Programmable Clock Ready 0 Interrupt Disable More... | |

| #define | PMC_IDR_PCKRDY1 (0x1u << 9) |

| (PMC_IDR) Programmable Clock Ready 1 Interrupt Disable More... | |

| #define | PMC_IDR_PCKRDY2 (0x1u << 10) |

| (PMC_IDR) Programmable Clock Ready 2 Interrupt Disable More... | |

| #define | PMC_IDR_PCKRDY3 (0x1u << 11) |

| (PMC_IDR) Programmable Clock Ready 3 Interrupt Disable More... | |

| #define | PMC_IDR_PCKRDY4 (0x1u << 12) |

| (PMC_IDR) Programmable Clock Ready 4 Interrupt Disable More... | |

| #define | PMC_IDR_PCKRDY5 (0x1u << 13) |

| (PMC_IDR) Programmable Clock Ready 5 Interrupt Disable More... | |

| #define | PMC_IDR_PCKRDY6 (0x1u << 14) |

| (PMC_IDR) Programmable Clock Ready 6 Interrupt Disable More... | |

| #define | PMC_IDR_XT32KERR (0x1u << 21) |

| (PMC_IDR) Slow Crystal Oscillator Error Interrupt Disable More... | |

| #define | PMC_IER_CFDEV (0x1u << 18) |

| (PMC_IER) Clock Failure Detector Event Interrupt Enable More... | |

| #define | PMC_IER_LOCKA (0x1u << 1) |

| (PMC_IER) PLLA Lock Interrupt Enable More... | |

| #define | PMC_IER_LOCKU (0x1u << 6) |

| (PMC_IER) UTMI PLL Lock Interrupt Enable More... | |

| #define | PMC_IER_MCKRDY (0x1u << 3) |

| (PMC_IER) Master Clock Ready Interrupt Enable More... | |

| #define | PMC_IER_MOSCRCS (0x1u << 17) |

| (PMC_IER) Main On-Chip RC Status Interrupt Enable More... | |

| #define | PMC_IER_MOSCSELS (0x1u << 16) |

| (PMC_IER) Main Oscillator Selection Status Interrupt Enable More... | |

| #define | PMC_IER_MOSCXTS (0x1u << 0) |

| (PMC_IER) Main Crystal Oscillator Status Interrupt Enable More... | |

| #define | PMC_IER_PCKRDY0 (0x1u << 8) |

| (PMC_IER) Programmable Clock Ready 0 Interrupt Enable More... | |

| #define | PMC_IER_PCKRDY1 (0x1u << 9) |

| (PMC_IER) Programmable Clock Ready 1 Interrupt Enable More... | |

| #define | PMC_IER_PCKRDY2 (0x1u << 10) |

| (PMC_IER) Programmable Clock Ready 2 Interrupt Enable More... | |

| #define | PMC_IER_PCKRDY3 (0x1u << 11) |

| (PMC_IER) Programmable Clock Ready 3 Interrupt Enable More... | |

| #define | PMC_IER_PCKRDY4 (0x1u << 12) |

| (PMC_IER) Programmable Clock Ready 4 Interrupt Enable More... | |

| #define | PMC_IER_PCKRDY5 (0x1u << 13) |

| (PMC_IER) Programmable Clock Ready 5 Interrupt Enable More... | |

| #define | PMC_IER_PCKRDY6 (0x1u << 14) |

| (PMC_IER) Programmable Clock Ready 6 Interrupt Enable More... | |

| #define | PMC_IER_XT32KERR (0x1u << 21) |

| (PMC_IER) Slow Crystal Oscillator Error Interrupt Enable More... | |

| #define | PMC_IMR_CFDEV (0x1u << 18) |

| (PMC_IMR) Clock Failure Detector Event Interrupt Mask More... | |

| #define | PMC_IMR_LOCKA (0x1u << 1) |

| (PMC_IMR) PLLA Lock Interrupt Mask More... | |

| #define | PMC_IMR_LOCKU (0x1u << 6) |

| (PMC_IMR) UTMI PLL Lock Interrupt Mask More... | |

| #define | PMC_IMR_MCKRDY (0x1u << 3) |

| (PMC_IMR) Master Clock Ready Interrupt Mask More... | |

| #define | PMC_IMR_MOSCRCS (0x1u << 17) |

| (PMC_IMR) Main On-Chip RC Status Interrupt Mask More... | |

| #define | PMC_IMR_MOSCSELS (0x1u << 16) |

| (PMC_IMR) Main Oscillator Selection Status Interrupt Mask More... | |

| #define | PMC_IMR_MOSCXTS (0x1u << 0) |

| (PMC_IMR) Main Crystal Oscillator Status Interrupt Mask More... | |

| #define | PMC_IMR_PCKRDY0 (0x1u << 8) |

| (PMC_IMR) Programmable Clock Ready 0 Interrupt Mask More... | |

| #define | PMC_IMR_PCKRDY1 (0x1u << 9) |

| (PMC_IMR) Programmable Clock Ready 1 Interrupt Mask More... | |

| #define | PMC_IMR_PCKRDY2 (0x1u << 10) |

| (PMC_IMR) Programmable Clock Ready 2 Interrupt Mask More... | |

| #define | PMC_IMR_PCKRDY3 (0x1u << 11) |

| (PMC_IMR) Programmable Clock Ready 3 Interrupt Mask More... | |

| #define | PMC_IMR_PCKRDY4 (0x1u << 12) |

| (PMC_IMR) Programmable Clock Ready 4 Interrupt Mask More... | |

| #define | PMC_IMR_PCKRDY5 (0x1u << 13) |

| (PMC_IMR) Programmable Clock Ready 5 Interrupt Mask More... | |

| #define | PMC_IMR_PCKRDY6 (0x1u << 14) |

| (PMC_IMR) Programmable Clock Ready 6 Interrupt Mask More... | |

| #define | PMC_IMR_XT32KERR (0x1u << 21) |

| (PMC_IMR) Slow Crystal Oscillator Error Interrupt Mask More... | |

| #define | PMC_MCKR_CSS(value) ((PMC_MCKR_CSS_Msk & ((value) << PMC_MCKR_CSS_Pos))) |

| #define | PMC_MCKR_CSS_MAIN_CLK (0x1u << 0) |

| (PMC_MCKR) Main Clock is selected More... | |

| #define | PMC_MCKR_CSS_Msk (0x3u << PMC_MCKR_CSS_Pos) |

| (PMC_MCKR) Master Clock Source Selection More... | |

| #define | PMC_MCKR_CSS_PLLA_CLK (0x2u << 0) |

| (PMC_MCKR) PLLA Clock is selected More... | |

| #define | PMC_MCKR_CSS_Pos 0 |

| #define | PMC_MCKR_CSS_SLOW_CLK (0x0u << 0) |

| (PMC_MCKR) Slow Clock is selected More... | |

| #define | PMC_MCKR_CSS_UPLL_CLK (0x3u << 0) |

| (PMC_MCKR) Divided UPLL Clock is selected More... | |

| #define | PMC_MCKR_MDIV(value) ((PMC_MCKR_MDIV_Msk & ((value) << PMC_MCKR_MDIV_Pos))) |

| #define | PMC_MCKR_MDIV_EQ_PCK (0x0u << 8) |

| (PMC_MCKR) Master Clock is Prescaler Output Clock divided by 1. More... | |

| #define | PMC_MCKR_MDIV_Msk (0x3u << PMC_MCKR_MDIV_Pos) |

| (PMC_MCKR) Master Clock Division More... | |

| #define | PMC_MCKR_MDIV_PCK_DIV2 (0x1u << 8) |

| (PMC_MCKR) Master Clock is Prescaler Output Clock divided by 2. More... | |

| #define | PMC_MCKR_MDIV_PCK_DIV3 (0x3u << 8) |

| (PMC_MCKR) Master Clock is Prescaler Output Clock divided by 3. More... | |

| #define | PMC_MCKR_MDIV_PCK_DIV4 (0x2u << 8) |

| (PMC_MCKR) Master Clock is Prescaler Output Clock divided by 4. More... | |

| #define | PMC_MCKR_MDIV_Pos 8 |

| #define | PMC_MCKR_PRES(value) ((PMC_MCKR_PRES_Msk & ((value) << PMC_MCKR_PRES_Pos))) |

| #define | PMC_MCKR_PRES_CLK_1 (0x0u << 4) |

| (PMC_MCKR) Selected clock More... | |

| #define | PMC_MCKR_PRES_CLK_16 (0x4u << 4) |

| (PMC_MCKR) Selected clock divided by 16 More... | |

| #define | PMC_MCKR_PRES_CLK_2 (0x1u << 4) |

| (PMC_MCKR) Selected clock divided by 2 More... | |

| #define | PMC_MCKR_PRES_CLK_3 (0x7u << 4) |

| (PMC_MCKR) Selected clock divided by 3 More... | |

| #define | PMC_MCKR_PRES_CLK_32 (0x5u << 4) |

| (PMC_MCKR) Selected clock divided by 32 More... | |

| #define | PMC_MCKR_PRES_CLK_4 (0x2u << 4) |

| (PMC_MCKR) Selected clock divided by 4 More... | |

| #define | PMC_MCKR_PRES_CLK_64 (0x6u << 4) |

| (PMC_MCKR) Selected clock divided by 64 More... | |

| #define | PMC_MCKR_PRES_CLK_8 (0x3u << 4) |

| (PMC_MCKR) Selected clock divided by 8 More... | |

| #define | PMC_MCKR_PRES_Msk (0x7u << PMC_MCKR_PRES_Pos) |

| (PMC_MCKR) Processor Clock Prescaler More... | |

| #define | PMC_MCKR_PRES_Pos 4 |

| #define | PMC_MCKR_UPLLDIV2 (0x1u << 13) |

| (PMC_MCKR) UPLL Divisor by 2 More... | |

| #define | PMC_OCR_CAL12(value) ((PMC_OCR_CAL12_Msk & ((value) << PMC_OCR_CAL12_Pos))) |

| #define | PMC_OCR_CAL12_Msk (0x7fu << PMC_OCR_CAL12_Pos) |

| (PMC_OCR) RC Oscillator Calibration bits for 12 MHz More... | |

| #define | PMC_OCR_CAL12_Pos 16 |

| #define | PMC_OCR_CAL4(value) ((PMC_OCR_CAL4_Msk & ((value) << PMC_OCR_CAL4_Pos))) |

| #define | PMC_OCR_CAL4_Msk (0x7fu << PMC_OCR_CAL4_Pos) |

| (PMC_OCR) RC Oscillator Calibration bits for 4 MHz More... | |

| #define | PMC_OCR_CAL4_Pos 0 |

| #define | PMC_OCR_CAL8(value) ((PMC_OCR_CAL8_Msk & ((value) << PMC_OCR_CAL8_Pos))) |

| #define | PMC_OCR_CAL8_Msk (0x7fu << PMC_OCR_CAL8_Pos) |

| (PMC_OCR) RC Oscillator Calibration bits for 8 MHz More... | |

| #define | PMC_OCR_CAL8_Pos 8 |

| #define | PMC_OCR_SEL12 (0x1u << 23) |

| (PMC_OCR) Selection of RC Oscillator Calibration bits for 12 MHz More... | |

| #define | PMC_OCR_SEL4 (0x1u << 7) |

| (PMC_OCR) Selection of RC Oscillator Calibration bits for 4 MHz More... | |

| #define | PMC_OCR_SEL8 (0x1u << 15) |

| (PMC_OCR) Selection of RC Oscillator Calibration bits for 8 MHz More... | |

| #define | PMC_PCDR0_PID10 (0x1u << 10) |

| (PMC_PCDR0) Peripheral Clock 10 Disable More... | |

| #define | PMC_PCDR0_PID11 (0x1u << 11) |

| (PMC_PCDR0) Peripheral Clock 11 Disable More... | |

| #define | PMC_PCDR0_PID12 (0x1u << 12) |

| (PMC_PCDR0) Peripheral Clock 12 Disable More... | |

| #define | PMC_PCDR0_PID13 (0x1u << 13) |

| (PMC_PCDR0) Peripheral Clock 13 Disable More... | |

| #define | PMC_PCDR0_PID14 (0x1u << 14) |

| (PMC_PCDR0) Peripheral Clock 14 Disable More... | |

| #define | PMC_PCDR0_PID15 (0x1u << 15) |

| (PMC_PCDR0) Peripheral Clock 15 Disable More... | |

| #define | PMC_PCDR0_PID16 (0x1u << 16) |

| (PMC_PCDR0) Peripheral Clock 16 Disable More... | |

| #define | PMC_PCDR0_PID17 (0x1u << 17) |

| (PMC_PCDR0) Peripheral Clock 17 Disable More... | |

| #define | PMC_PCDR0_PID18 (0x1u << 18) |

| (PMC_PCDR0) Peripheral Clock 18 Disable More... | |

| #define | PMC_PCDR0_PID19 (0x1u << 19) |

| (PMC_PCDR0) Peripheral Clock 19 Disable More... | |

| #define | PMC_PCDR0_PID20 (0x1u << 20) |

| (PMC_PCDR0) Peripheral Clock 20 Disable More... | |

| #define | PMC_PCDR0_PID21 (0x1u << 21) |

| (PMC_PCDR0) Peripheral Clock 21 Disable More... | |

| #define | PMC_PCDR0_PID22 (0x1u << 22) |

| (PMC_PCDR0) Peripheral Clock 22 Disable More... | |

| #define | PMC_PCDR0_PID23 (0x1u << 23) |

| (PMC_PCDR0) Peripheral Clock 23 Disable More... | |

| #define | PMC_PCDR0_PID24 (0x1u << 24) |

| (PMC_PCDR0) Peripheral Clock 24 Disable More... | |

| #define | PMC_PCDR0_PID25 (0x1u << 25) |

| (PMC_PCDR0) Peripheral Clock 25 Disable More... | |

| #define | PMC_PCDR0_PID26 (0x1u << 26) |

| (PMC_PCDR0) Peripheral Clock 26 Disable More... | |

| #define | PMC_PCDR0_PID27 (0x1u << 27) |

| (PMC_PCDR0) Peripheral Clock 27 Disable More... | |

| #define | PMC_PCDR0_PID28 (0x1u << 28) |

| (PMC_PCDR0) Peripheral Clock 28 Disable More... | |

| #define | PMC_PCDR0_PID29 (0x1u << 29) |

| (PMC_PCDR0) Peripheral Clock 29 Disable More... | |

| #define | PMC_PCDR0_PID30 (0x1u << 30) |

| (PMC_PCDR0) Peripheral Clock 30 Disable More... | |

| #define | PMC_PCDR0_PID31 (0x1u << 31) |

| (PMC_PCDR0) Peripheral Clock 31 Disable More... | |

| #define | PMC_PCDR0_PID7 (0x1u << 7) |

| (PMC_PCDR0) Peripheral Clock 7 Disable More... | |

| #define | PMC_PCDR0_PID8 (0x1u << 8) |

| (PMC_PCDR0) Peripheral Clock 8 Disable More... | |

| #define | PMC_PCDR0_PID9 (0x1u << 9) |

| (PMC_PCDR0) Peripheral Clock 9 Disable More... | |

| #define | PMC_PCDR1_PID32 (0x1u << 0) |

| (PMC_PCDR1) Peripheral Clock 32 Disable More... | |

| #define | PMC_PCDR1_PID33 (0x1u << 1) |

| (PMC_PCDR1) Peripheral Clock 33 Disable More... | |

| #define | PMC_PCDR1_PID34 (0x1u << 2) |

| (PMC_PCDR1) Peripheral Clock 34 Disable More... | |

| #define | PMC_PCDR1_PID35 (0x1u << 3) |

| (PMC_PCDR1) Peripheral Clock 35 Disable More... | |

| #define | PMC_PCDR1_PID37 (0x1u << 5) |

| (PMC_PCDR1) Peripheral Clock 37 Disable More... | |

| #define | PMC_PCDR1_PID39 (0x1u << 7) |

| (PMC_PCDR1) Peripheral Clock 39 Disable More... | |

| #define | PMC_PCDR1_PID40 (0x1u << 8) |

| (PMC_PCDR1) Peripheral Clock 40 Disable More... | |

| #define | PMC_PCDR1_PID41 (0x1u << 9) |

| (PMC_PCDR1) Peripheral Clock 41 Disable More... | |

| #define | PMC_PCDR1_PID42 (0x1u << 10) |

| (PMC_PCDR1) Peripheral Clock 42 Disable More... | |

| #define | PMC_PCDR1_PID43 (0x1u << 11) |

| (PMC_PCDR1) Peripheral Clock 43 Disable More... | |

| #define | PMC_PCDR1_PID44 (0x1u << 12) |

| (PMC_PCDR1) Peripheral Clock 44 Disable More... | |

| #define | PMC_PCDR1_PID45 (0x1u << 13) |

| (PMC_PCDR1) Peripheral Clock 45 Disable More... | |

| #define | PMC_PCDR1_PID46 (0x1u << 14) |

| (PMC_PCDR1) Peripheral Clock 46 Disable More... | |

| #define | PMC_PCDR1_PID47 (0x1u << 15) |

| (PMC_PCDR1) Peripheral Clock 47 Disable More... | |

| #define | PMC_PCDR1_PID48 (0x1u << 16) |

| (PMC_PCDR1) Peripheral Clock 48 Disable More... | |

| #define | PMC_PCDR1_PID49 (0x1u << 17) |

| (PMC_PCDR1) Peripheral Clock 49 Disable More... | |

| #define | PMC_PCDR1_PID50 (0x1u << 18) |

| (PMC_PCDR1) Peripheral Clock 50 Disable More... | |

| #define | PMC_PCDR1_PID51 (0x1u << 19) |

| (PMC_PCDR1) Peripheral Clock 51 Disable More... | |

| #define | PMC_PCDR1_PID52 (0x1u << 20) |

| (PMC_PCDR1) Peripheral Clock 52 Disable More... | |

| #define | PMC_PCDR1_PID53 (0x1u << 21) |

| (PMC_PCDR1) Peripheral Clock 53 Disable More... | |

| #define | PMC_PCDR1_PID56 (0x1u << 24) |

| (PMC_PCDR1) Peripheral Clock 56 Disable More... | |

| #define | PMC_PCDR1_PID57 (0x1u << 25) |

| (PMC_PCDR1) Peripheral Clock 57 Disable More... | |

| #define | PMC_PCDR1_PID58 (0x1u << 26) |

| (PMC_PCDR1) Peripheral Clock 58 Disable More... | |

| #define | PMC_PCDR1_PID59 (0x1u << 27) |

| (PMC_PCDR1) Peripheral Clock 59 Disable More... | |

| #define | PMC_PCDR1_PID60 (0x1u << 28) |

| (PMC_PCDR1) Peripheral Clock 60 Disable More... | |

| #define | PMC_PCER0_PID10 (0x1u << 10) |

| (PMC_PCER0) Peripheral Clock 10 Enable More... | |

| #define | PMC_PCER0_PID11 (0x1u << 11) |

| (PMC_PCER0) Peripheral Clock 11 Enable More... | |

| #define | PMC_PCER0_PID12 (0x1u << 12) |

| (PMC_PCER0) Peripheral Clock 12 Enable More... | |

| #define | PMC_PCER0_PID13 (0x1u << 13) |

| (PMC_PCER0) Peripheral Clock 13 Enable More... | |

| #define | PMC_PCER0_PID14 (0x1u << 14) |

| (PMC_PCER0) Peripheral Clock 14 Enable More... | |

| #define | PMC_PCER0_PID15 (0x1u << 15) |

| (PMC_PCER0) Peripheral Clock 15 Enable More... | |

| #define | PMC_PCER0_PID16 (0x1u << 16) |

| (PMC_PCER0) Peripheral Clock 16 Enable More... | |

| #define | PMC_PCER0_PID17 (0x1u << 17) |

| (PMC_PCER0) Peripheral Clock 17 Enable More... | |

| #define | PMC_PCER0_PID18 (0x1u << 18) |

| (PMC_PCER0) Peripheral Clock 18 Enable More... | |

| #define | PMC_PCER0_PID19 (0x1u << 19) |

| (PMC_PCER0) Peripheral Clock 19 Enable More... | |

| #define | PMC_PCER0_PID20 (0x1u << 20) |

| (PMC_PCER0) Peripheral Clock 20 Enable More... | |

| #define | PMC_PCER0_PID21 (0x1u << 21) |

| (PMC_PCER0) Peripheral Clock 21 Enable More... | |

| #define | PMC_PCER0_PID22 (0x1u << 22) |

| (PMC_PCER0) Peripheral Clock 22 Enable More... | |

| #define | PMC_PCER0_PID23 (0x1u << 23) |

| (PMC_PCER0) Peripheral Clock 23 Enable More... | |

| #define | PMC_PCER0_PID24 (0x1u << 24) |

| (PMC_PCER0) Peripheral Clock 24 Enable More... | |

| #define | PMC_PCER0_PID25 (0x1u << 25) |

| (PMC_PCER0) Peripheral Clock 25 Enable More... | |

| #define | PMC_PCER0_PID26 (0x1u << 26) |

| (PMC_PCER0) Peripheral Clock 26 Enable More... | |

| #define | PMC_PCER0_PID27 (0x1u << 27) |

| (PMC_PCER0) Peripheral Clock 27 Enable More... | |

| #define | PMC_PCER0_PID28 (0x1u << 28) |

| (PMC_PCER0) Peripheral Clock 28 Enable More... | |

| #define | PMC_PCER0_PID29 (0x1u << 29) |

| (PMC_PCER0) Peripheral Clock 29 Enable More... | |

| #define | PMC_PCER0_PID30 (0x1u << 30) |

| (PMC_PCER0) Peripheral Clock 30 Enable More... | |

| #define | PMC_PCER0_PID31 (0x1u << 31) |

| (PMC_PCER0) Peripheral Clock 31 Enable More... | |

| #define | PMC_PCER0_PID7 (0x1u << 7) |

| (PMC_PCER0) Peripheral Clock 7 Enable More... | |

| #define | PMC_PCER0_PID8 (0x1u << 8) |

| (PMC_PCER0) Peripheral Clock 8 Enable More... | |

| #define | PMC_PCER0_PID9 (0x1u << 9) |

| (PMC_PCER0) Peripheral Clock 9 Enable More... | |

| #define | PMC_PCER1_PID32 (0x1u << 0) |

| (PMC_PCER1) Peripheral Clock 32 Enable More... | |

| #define | PMC_PCER1_PID33 (0x1u << 1) |

| (PMC_PCER1) Peripheral Clock 33 Enable More... | |

| #define | PMC_PCER1_PID34 (0x1u << 2) |

| (PMC_PCER1) Peripheral Clock 34 Enable More... | |

| #define | PMC_PCER1_PID35 (0x1u << 3) |

| (PMC_PCER1) Peripheral Clock 35 Enable More... | |

| #define | PMC_PCER1_PID37 (0x1u << 5) |

| (PMC_PCER1) Peripheral Clock 37 Enable More... | |

| #define | PMC_PCER1_PID39 (0x1u << 7) |

| (PMC_PCER1) Peripheral Clock 39 Enable More... | |

| #define | PMC_PCER1_PID40 (0x1u << 8) |

| (PMC_PCER1) Peripheral Clock 40 Enable More... | |

| #define | PMC_PCER1_PID41 (0x1u << 9) |

| (PMC_PCER1) Peripheral Clock 41 Enable More... | |

| #define | PMC_PCER1_PID42 (0x1u << 10) |

| (PMC_PCER1) Peripheral Clock 42 Enable More... | |

| #define | PMC_PCER1_PID43 (0x1u << 11) |

| (PMC_PCER1) Peripheral Clock 43 Enable More... | |

| #define | PMC_PCER1_PID44 (0x1u << 12) |

| (PMC_PCER1) Peripheral Clock 44 Enable More... | |

| #define | PMC_PCER1_PID45 (0x1u << 13) |

| (PMC_PCER1) Peripheral Clock 45 Enable More... | |

| #define | PMC_PCER1_PID46 (0x1u << 14) |

| (PMC_PCER1) Peripheral Clock 46 Enable More... | |

| #define | PMC_PCER1_PID47 (0x1u << 15) |

| (PMC_PCER1) Peripheral Clock 47 Enable More... | |

| #define | PMC_PCER1_PID48 (0x1u << 16) |

| (PMC_PCER1) Peripheral Clock 48 Enable More... | |

| #define | PMC_PCER1_PID49 (0x1u << 17) |

| (PMC_PCER1) Peripheral Clock 49 Enable More... | |

| #define | PMC_PCER1_PID50 (0x1u << 18) |

| (PMC_PCER1) Peripheral Clock 50 Enable More... | |

| #define | PMC_PCER1_PID51 (0x1u << 19) |

| (PMC_PCER1) Peripheral Clock 51 Enable More... | |

| #define | PMC_PCER1_PID52 (0x1u << 20) |

| (PMC_PCER1) Peripheral Clock 52 Enable More... | |

| #define | PMC_PCER1_PID53 (0x1u << 21) |

| (PMC_PCER1) Peripheral Clock 53 Enable More... | |

| #define | PMC_PCER1_PID56 (0x1u << 24) |

| (PMC_PCER1) Peripheral Clock 56 Enable More... | |

| #define | PMC_PCER1_PID57 (0x1u << 25) |

| (PMC_PCER1) Peripheral Clock 57 Enable More... | |

| #define | PMC_PCER1_PID58 (0x1u << 26) |

| (PMC_PCER1) Peripheral Clock 58 Enable More... | |

| #define | PMC_PCER1_PID59 (0x1u << 27) |

| (PMC_PCER1) Peripheral Clock 59 Enable More... | |

| #define | PMC_PCER1_PID60 (0x1u << 28) |

| (PMC_PCER1) Peripheral Clock 60 Enable More... | |

| #define | PMC_PCK_CSS(value) ((PMC_PCK_CSS_Msk & ((value) << PMC_PCK_CSS_Pos))) |

| #define | PMC_PCK_CSS_MAIN_CLK (0x1u << 0) |

| (PMC_PCK[8]) Main Clock is selected More... | |

| #define | PMC_PCK_CSS_MCK (0x4u << 0) |

| (PMC_PCK[8]) Master Clock is selected More... | |

| #define | PMC_PCK_CSS_Msk (0x7u << PMC_PCK_CSS_Pos) |

| (PMC_PCK[8]) Programmable Clock Source Selection More... | |

| #define | PMC_PCK_CSS_PLLA_CLK (0x2u << 0) |

| (PMC_PCK[8]) PLLA Clock is selected More... | |

| #define | PMC_PCK_CSS_Pos 0 |

| #define | PMC_PCK_CSS_SLOW_CLK (0x0u << 0) |

| (PMC_PCK[8]) Slow Clock is selected More... | |

| #define | PMC_PCK_CSS_UPLL_CLK (0x3u << 0) |

| (PMC_PCK[8]) Divided UPLL Clock is selected More... | |

| #define | PMC_PCK_PRES(value) ((PMC_PCK_PRES_Msk & ((value) << PMC_PCK_PRES_Pos))) |

| #define | PMC_PCK_PRES_Msk (0xffu << PMC_PCK_PRES_Pos) |

| (PMC_PCK[8]) Programmable Clock Prescaler More... | |

| #define | PMC_PCK_PRES_Pos 4 |

| #define | PMC_PCR_CMD (0x1u << 12) |

| (PMC_PCR) Command More... | |

| #define | PMC_PCR_DIV(value) ((PMC_PCR_DIV_Msk & ((value) << PMC_PCR_DIV_Pos))) |

| #define | PMC_PCR_DIV_Msk (0x3u << PMC_PCR_DIV_Pos) |

| (PMC_PCR) Divisor Value More... | |

| #define | PMC_PCR_DIV_PERIPH_DIV2_MCK (0x1u << 16) |

| (PMC_PCR) Peripheral clock is MCK/2 More... | |

| #define | PMC_PCR_DIV_PERIPH_DIV4_MCK (0x2u << 16) |

| (PMC_PCR) Peripheral clock is MCK/4 More... | |

| #define | PMC_PCR_DIV_PERIPH_DIV8_MCK (0x3u << 16) |

| (PMC_PCR) Peripheral clock is MCK/8 More... | |

| #define | PMC_PCR_DIV_PERIPH_DIV_MCK (0x0u << 16) |

| (PMC_PCR) Peripheral clock is MCK More... | |

| #define | PMC_PCR_DIV_Pos 16 |

| #define | PMC_PCR_EN (0x1u << 28) |

| (PMC_PCR) Enable More... | |

| #define | PMC_PCR_GCLKCSS(value) ((PMC_PCR_GCLKCSS_Msk & ((value) << PMC_PCR_GCLKCSS_Pos))) |

| #define | PMC_PCR_GCLKCSS_MAIN_CLK (0x1u << 8) |

| (PMC_PCR) Main clock is selected More... | |

| #define | PMC_PCR_GCLKCSS_MCK_CLK (0x4u << 8) |

| (PMC_PCR) Master Clock is selected More... | |

| #define | PMC_PCR_GCLKCSS_Msk (0x7u << PMC_PCR_GCLKCSS_Pos) |

| (PMC_PCR) Generic Clock Source Selection More... | |

| #define | PMC_PCR_GCLKCSS_PLLA_CLK (0x2u << 8) |

| (PMC_PCR) PLLACK is selected More... | |

| #define | PMC_PCR_GCLKCSS_Pos 8 |

| #define | PMC_PCR_GCLKCSS_SLOW_CLK (0x0u << 8) |

| (PMC_PCR) Slow clock is selected More... | |

| #define | PMC_PCR_GCLKCSS_UPLL_CLK (0x3u << 8) |

| (PMC_PCR) UPLL Clock is selected More... | |

| #define | PMC_PCR_GCLKDIV(value) ((PMC_PCR_GCLKDIV_Msk & ((value) << PMC_PCR_GCLKDIV_Pos))) |

| #define | PMC_PCR_GCLKDIV_Msk (0xffu << PMC_PCR_GCLKDIV_Pos) |

| (PMC_PCR) Generic Clock Division Ratio More... | |

| #define | PMC_PCR_GCLKDIV_Pos 20 |

| #define | PMC_PCR_GCLKEN (0x1u << 29) |

| (PMC_PCR) Generic Clock Enable More... | |

| #define | PMC_PCR_PID(value) ((PMC_PCR_PID_Msk & ((value) << PMC_PCR_PID_Pos))) |

| #define | PMC_PCR_PID_Msk (0x7fu << PMC_PCR_PID_Pos) |

| (PMC_PCR) Peripheral ID More... | |

| #define | PMC_PCR_PID_Pos 0 |

| #define | PMC_PCSR0_PID10 (0x1u << 10) |

| (PMC_PCSR0) Peripheral Clock 10 Status More... | |

| #define | PMC_PCSR0_PID11 (0x1u << 11) |

| (PMC_PCSR0) Peripheral Clock 11 Status More... | |

| #define | PMC_PCSR0_PID12 (0x1u << 12) |

| (PMC_PCSR0) Peripheral Clock 12 Status More... | |

| #define | PMC_PCSR0_PID13 (0x1u << 13) |

| (PMC_PCSR0) Peripheral Clock 13 Status More... | |

| #define | PMC_PCSR0_PID14 (0x1u << 14) |

| (PMC_PCSR0) Peripheral Clock 14 Status More... | |

| #define | PMC_PCSR0_PID15 (0x1u << 15) |

| (PMC_PCSR0) Peripheral Clock 15 Status More... | |

| #define | PMC_PCSR0_PID16 (0x1u << 16) |

| (PMC_PCSR0) Peripheral Clock 16 Status More... | |

| #define | PMC_PCSR0_PID17 (0x1u << 17) |

| (PMC_PCSR0) Peripheral Clock 17 Status More... | |

| #define | PMC_PCSR0_PID18 (0x1u << 18) |

| (PMC_PCSR0) Peripheral Clock 18 Status More... | |

| #define | PMC_PCSR0_PID19 (0x1u << 19) |

| (PMC_PCSR0) Peripheral Clock 19 Status More... | |

| #define | PMC_PCSR0_PID20 (0x1u << 20) |

| (PMC_PCSR0) Peripheral Clock 20 Status More... | |

| #define | PMC_PCSR0_PID21 (0x1u << 21) |

| (PMC_PCSR0) Peripheral Clock 21 Status More... | |

| #define | PMC_PCSR0_PID22 (0x1u << 22) |

| (PMC_PCSR0) Peripheral Clock 22 Status More... | |

| #define | PMC_PCSR0_PID23 (0x1u << 23) |

| (PMC_PCSR0) Peripheral Clock 23 Status More... | |

| #define | PMC_PCSR0_PID24 (0x1u << 24) |

| (PMC_PCSR0) Peripheral Clock 24 Status More... | |

| #define | PMC_PCSR0_PID25 (0x1u << 25) |

| (PMC_PCSR0) Peripheral Clock 25 Status More... | |

| #define | PMC_PCSR0_PID26 (0x1u << 26) |

| (PMC_PCSR0) Peripheral Clock 26 Status More... | |

| #define | PMC_PCSR0_PID27 (0x1u << 27) |

| (PMC_PCSR0) Peripheral Clock 27 Status More... | |

| #define | PMC_PCSR0_PID28 (0x1u << 28) |

| (PMC_PCSR0) Peripheral Clock 28 Status More... | |

| #define | PMC_PCSR0_PID29 (0x1u << 29) |

| (PMC_PCSR0) Peripheral Clock 29 Status More... | |

| #define | PMC_PCSR0_PID30 (0x1u << 30) |

| (PMC_PCSR0) Peripheral Clock 30 Status More... | |

| #define | PMC_PCSR0_PID31 (0x1u << 31) |

| (PMC_PCSR0) Peripheral Clock 31 Status More... | |

| #define | PMC_PCSR0_PID7 (0x1u << 7) |

| (PMC_PCSR0) Peripheral Clock 7 Status More... | |

| #define | PMC_PCSR0_PID8 (0x1u << 8) |

| (PMC_PCSR0) Peripheral Clock 8 Status More... | |

| #define | PMC_PCSR0_PID9 (0x1u << 9) |

| (PMC_PCSR0) Peripheral Clock 9 Status More... | |

| #define | PMC_PCSR1_PID32 (0x1u << 0) |

| (PMC_PCSR1) Peripheral Clock 32 Status More... | |

| #define | PMC_PCSR1_PID33 (0x1u << 1) |

| (PMC_PCSR1) Peripheral Clock 33 Status More... | |

| #define | PMC_PCSR1_PID34 (0x1u << 2) |

| (PMC_PCSR1) Peripheral Clock 34 Status More... | |

| #define | PMC_PCSR1_PID35 (0x1u << 3) |

| (PMC_PCSR1) Peripheral Clock 35 Status More... | |

| #define | PMC_PCSR1_PID37 (0x1u << 5) |

| (PMC_PCSR1) Peripheral Clock 37 Status More... | |

| #define | PMC_PCSR1_PID39 (0x1u << 7) |

| (PMC_PCSR1) Peripheral Clock 39 Status More... | |

| #define | PMC_PCSR1_PID40 (0x1u << 8) |

| (PMC_PCSR1) Peripheral Clock 40 Status More... | |

| #define | PMC_PCSR1_PID41 (0x1u << 9) |

| (PMC_PCSR1) Peripheral Clock 41 Status More... | |

| #define | PMC_PCSR1_PID42 (0x1u << 10) |

| (PMC_PCSR1) Peripheral Clock 42 Status More... | |

| #define | PMC_PCSR1_PID43 (0x1u << 11) |

| (PMC_PCSR1) Peripheral Clock 43 Status More... | |

| #define | PMC_PCSR1_PID44 (0x1u << 12) |

| (PMC_PCSR1) Peripheral Clock 44 Status More... | |

| #define | PMC_PCSR1_PID45 (0x1u << 13) |

| (PMC_PCSR1) Peripheral Clock 45 Status More... | |

| #define | PMC_PCSR1_PID46 (0x1u << 14) |

| (PMC_PCSR1) Peripheral Clock 46 Status More... | |

| #define | PMC_PCSR1_PID47 (0x1u << 15) |

| (PMC_PCSR1) Peripheral Clock 47 Status More... | |

| #define | PMC_PCSR1_PID48 (0x1u << 16) |

| (PMC_PCSR1) Peripheral Clock 48 Status More... | |

| #define | PMC_PCSR1_PID49 (0x1u << 17) |

| (PMC_PCSR1) Peripheral Clock 49 Status More... | |

| #define | PMC_PCSR1_PID50 (0x1u << 18) |

| (PMC_PCSR1) Peripheral Clock 50 Status More... | |

| #define | PMC_PCSR1_PID51 (0x1u << 19) |

| (PMC_PCSR1) Peripheral Clock 51 Status More... | |

| #define | PMC_PCSR1_PID52 (0x1u << 20) |

| (PMC_PCSR1) Peripheral Clock 52 Status More... | |

| #define | PMC_PCSR1_PID53 (0x1u << 21) |

| (PMC_PCSR1) Peripheral Clock 53 Status More... | |

| #define | PMC_PCSR1_PID56 (0x1u << 24) |

| (PMC_PCSR1) Peripheral Clock 56 Status More... | |

| #define | PMC_PCSR1_PID57 (0x1u << 25) |

| (PMC_PCSR1) Peripheral Clock 57 Status More... | |

| #define | PMC_PCSR1_PID58 (0x1u << 26) |

| (PMC_PCSR1) Peripheral Clock 58 Status More... | |

| #define | PMC_PCSR1_PID59 (0x1u << 27) |

| (PMC_PCSR1) Peripheral Clock 59 Status More... | |

| #define | PMC_PCSR1_PID60 (0x1u << 28) |

| (PMC_PCSR1) Peripheral Clock 60 Status More... | |

| #define | PMC_PMMR_PLLA_MMAX(value) ((PMC_PMMR_PLLA_MMAX_Msk & ((value) << PMC_PMMR_PLLA_MMAX_Pos))) |

| #define | PMC_PMMR_PLLA_MMAX_Msk (0x7ffu << PMC_PMMR_PLLA_MMAX_Pos) |

| (PMC_PMMR) PLLA Maximum Allowed Multiplier Value More... | |

| #define | PMC_PMMR_PLLA_MMAX_Pos 0 |

| #define | PMC_SCDR_PCK0 (0x1u << 8) |

| (PMC_SCDR) Programmable Clock 0 Output Disable More... | |

| #define | PMC_SCDR_PCK1 (0x1u << 9) |

| (PMC_SCDR) Programmable Clock 1 Output Disable More... | |

| #define | PMC_SCDR_PCK2 (0x1u << 10) |

| (PMC_SCDR) Programmable Clock 2 Output Disable More... | |

| #define | PMC_SCDR_PCK3 (0x1u << 11) |

| (PMC_SCDR) Programmable Clock 3 Output Disable More... | |

| #define | PMC_SCDR_PCK4 (0x1u << 12) |

| (PMC_SCDR) Programmable Clock 4 Output Disable More... | |

| #define | PMC_SCDR_PCK5 (0x1u << 13) |

| (PMC_SCDR) Programmable Clock 5 Output Disable More... | |

| #define | PMC_SCDR_PCK6 (0x1u << 14) |

| (PMC_SCDR) Programmable Clock 6 Output Disable More... | |

| #define | PMC_SCDR_USBCLK (0x1u << 5) |

| (PMC_SCDR) Disable USB FS Clock More... | |

| #define | PMC_SCER_PCK0 (0x1u << 8) |

| (PMC_SCER) Programmable Clock 0 Output Enable More... | |

| #define | PMC_SCER_PCK1 (0x1u << 9) |

| (PMC_SCER) Programmable Clock 1 Output Enable More... | |

| #define | PMC_SCER_PCK2 (0x1u << 10) |

| (PMC_SCER) Programmable Clock 2 Output Enable More... | |

| #define | PMC_SCER_PCK3 (0x1u << 11) |

| (PMC_SCER) Programmable Clock 3 Output Enable More... | |

| #define | PMC_SCER_PCK4 (0x1u << 12) |

| (PMC_SCER) Programmable Clock 4 Output Enable More... | |

| #define | PMC_SCER_PCK5 (0x1u << 13) |

| (PMC_SCER) Programmable Clock 5 Output Enable More... | |

| #define | PMC_SCER_PCK6 (0x1u << 14) |

| (PMC_SCER) Programmable Clock 6 Output Enable More... | |

| #define | PMC_SCER_USBCLK (0x1u << 5) |

| (PMC_SCER) Enable USB FS Clock More... | |

| #define | PMC_SCSR_HCLKS (0x1u << 0) |

| (PMC_SCSR) Processor Clock Status More... | |

| #define | PMC_SCSR_PCK0 (0x1u << 8) |

| (PMC_SCSR) Programmable Clock 0 Output Status More... | |

| #define | PMC_SCSR_PCK1 (0x1u << 9) |

| (PMC_SCSR) Programmable Clock 1 Output Status More... | |

| #define | PMC_SCSR_PCK2 (0x1u << 10) |

| (PMC_SCSR) Programmable Clock 2 Output Status More... | |

| #define | PMC_SCSR_PCK3 (0x1u << 11) |

| (PMC_SCSR) Programmable Clock 3 Output Status More... | |

| #define | PMC_SCSR_PCK4 (0x1u << 12) |

| (PMC_SCSR) Programmable Clock 4 Output Status More... | |

| #define | PMC_SCSR_PCK5 (0x1u << 13) |

| (PMC_SCSR) Programmable Clock 5 Output Status More... | |

| #define | PMC_SCSR_PCK6 (0x1u << 14) |

| (PMC_SCSR) Programmable Clock 6 Output Status More... | |

| #define | PMC_SCSR_USBCLK (0x1u << 5) |

| (PMC_SCSR) USB FS Clock Status More... | |

| #define | PMC_SLPWK_AIPR_AIP (0x1u << 0) |

| (PMC_SLPWK_AIPR) Activity In Progress More... | |

| #define | PMC_SLPWK_ASR0_PID10 (0x1u << 10) |

| (PMC_SLPWK_ASR0) Peripheral 10 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID11 (0x1u << 11) |

| (PMC_SLPWK_ASR0) Peripheral 11 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID12 (0x1u << 12) |

| (PMC_SLPWK_ASR0) Peripheral 12 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID13 (0x1u << 13) |

| (PMC_SLPWK_ASR0) Peripheral 13 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID14 (0x1u << 14) |

| (PMC_SLPWK_ASR0) Peripheral 14 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID15 (0x1u << 15) |

| (PMC_SLPWK_ASR0) Peripheral 15 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID16 (0x1u << 16) |

| (PMC_SLPWK_ASR0) Peripheral 16 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID17 (0x1u << 17) |

| (PMC_SLPWK_ASR0) Peripheral 17 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID18 (0x1u << 18) |

| (PMC_SLPWK_ASR0) Peripheral 18 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID19 (0x1u << 19) |

| (PMC_SLPWK_ASR0) Peripheral 19 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID20 (0x1u << 20) |

| (PMC_SLPWK_ASR0) Peripheral 20 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID21 (0x1u << 21) |

| (PMC_SLPWK_ASR0) Peripheral 21 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID22 (0x1u << 22) |

| (PMC_SLPWK_ASR0) Peripheral 22 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID23 (0x1u << 23) |

| (PMC_SLPWK_ASR0) Peripheral 23 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID24 (0x1u << 24) |

| (PMC_SLPWK_ASR0) Peripheral 24 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID25 (0x1u << 25) |

| (PMC_SLPWK_ASR0) Peripheral 25 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID26 (0x1u << 26) |

| (PMC_SLPWK_ASR0) Peripheral 26 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID27 (0x1u << 27) |

| (PMC_SLPWK_ASR0) Peripheral 27 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID28 (0x1u << 28) |

| (PMC_SLPWK_ASR0) Peripheral 28 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID29 (0x1u << 29) |

| (PMC_SLPWK_ASR0) Peripheral 29 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID30 (0x1u << 30) |

| (PMC_SLPWK_ASR0) Peripheral 30 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID31 (0x1u << 31) |

| (PMC_SLPWK_ASR0) Peripheral 31 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID7 (0x1u << 7) |

| (PMC_SLPWK_ASR0) Peripheral 7 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID8 (0x1u << 8) |

| (PMC_SLPWK_ASR0) Peripheral 8 Activity Status More... | |

| #define | PMC_SLPWK_ASR0_PID9 (0x1u << 9) |

| (PMC_SLPWK_ASR0) Peripheral 9 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID32 (0x1u << 0) |

| (PMC_SLPWK_ASR1) Peripheral 32 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID33 (0x1u << 1) |

| (PMC_SLPWK_ASR1) Peripheral 33 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID34 (0x1u << 2) |

| (PMC_SLPWK_ASR1) Peripheral 34 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID35 (0x1u << 3) |

| (PMC_SLPWK_ASR1) Peripheral 35 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID37 (0x1u << 5) |

| (PMC_SLPWK_ASR1) Peripheral 37 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID39 (0x1u << 7) |

| (PMC_SLPWK_ASR1) Peripheral 39 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID40 (0x1u << 8) |

| (PMC_SLPWK_ASR1) Peripheral 40 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID41 (0x1u << 9) |

| (PMC_SLPWK_ASR1) Peripheral 41 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID42 (0x1u << 10) |

| (PMC_SLPWK_ASR1) Peripheral 42 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID43 (0x1u << 11) |

| (PMC_SLPWK_ASR1) Peripheral 43 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID44 (0x1u << 12) |

| (PMC_SLPWK_ASR1) Peripheral 44 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID45 (0x1u << 13) |

| (PMC_SLPWK_ASR1) Peripheral 45 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID46 (0x1u << 14) |

| (PMC_SLPWK_ASR1) Peripheral 46 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID47 (0x1u << 15) |

| (PMC_SLPWK_ASR1) Peripheral 47 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID48 (0x1u << 16) |

| (PMC_SLPWK_ASR1) Peripheral 48 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID49 (0x1u << 17) |

| (PMC_SLPWK_ASR1) Peripheral 49 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID50 (0x1u << 18) |

| (PMC_SLPWK_ASR1) Peripheral 50 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID51 (0x1u << 19) |

| (PMC_SLPWK_ASR1) Peripheral 51 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID52 (0x1u << 20) |

| (PMC_SLPWK_ASR1) Peripheral 52 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID53 (0x1u << 21) |

| (PMC_SLPWK_ASR1) Peripheral 53 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID56 (0x1u << 24) |

| (PMC_SLPWK_ASR1) Peripheral 56 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID57 (0x1u << 25) |

| (PMC_SLPWK_ASR1) Peripheral 57 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID58 (0x1u << 26) |

| (PMC_SLPWK_ASR1) Peripheral 58 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID59 (0x1u << 27) |

| (PMC_SLPWK_ASR1) Peripheral 59 Activity Status More... | |

| #define | PMC_SLPWK_ASR1_PID60 (0x1u << 28) |

| (PMC_SLPWK_ASR1) Peripheral 60 Activity Status More... | |

| #define | PMC_SLPWK_DR0_PID10 (0x1u << 10) |

| (PMC_SLPWK_DR0) Peripheral 10 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID11 (0x1u << 11) |

| (PMC_SLPWK_DR0) Peripheral 11 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID12 (0x1u << 12) |

| (PMC_SLPWK_DR0) Peripheral 12 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID13 (0x1u << 13) |

| (PMC_SLPWK_DR0) Peripheral 13 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID14 (0x1u << 14) |

| (PMC_SLPWK_DR0) Peripheral 14 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID15 (0x1u << 15) |

| (PMC_SLPWK_DR0) Peripheral 15 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID16 (0x1u << 16) |

| (PMC_SLPWK_DR0) Peripheral 16 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID17 (0x1u << 17) |

| (PMC_SLPWK_DR0) Peripheral 17 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID18 (0x1u << 18) |

| (PMC_SLPWK_DR0) Peripheral 18 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID19 (0x1u << 19) |

| (PMC_SLPWK_DR0) Peripheral 19 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID20 (0x1u << 20) |

| (PMC_SLPWK_DR0) Peripheral 20 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID21 (0x1u << 21) |

| (PMC_SLPWK_DR0) Peripheral 21 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID22 (0x1u << 22) |

| (PMC_SLPWK_DR0) Peripheral 22 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID23 (0x1u << 23) |

| (PMC_SLPWK_DR0) Peripheral 23 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID24 (0x1u << 24) |

| (PMC_SLPWK_DR0) Peripheral 24 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID25 (0x1u << 25) |

| (PMC_SLPWK_DR0) Peripheral 25 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID26 (0x1u << 26) |

| (PMC_SLPWK_DR0) Peripheral 26 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID27 (0x1u << 27) |

| (PMC_SLPWK_DR0) Peripheral 27 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID28 (0x1u << 28) |

| (PMC_SLPWK_DR0) Peripheral 28 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID29 (0x1u << 29) |

| (PMC_SLPWK_DR0) Peripheral 29 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID30 (0x1u << 30) |

| (PMC_SLPWK_DR0) Peripheral 30 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID31 (0x1u << 31) |

| (PMC_SLPWK_DR0) Peripheral 31 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID7 (0x1u << 7) |

| (PMC_SLPWK_DR0) Peripheral 7 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID8 (0x1u << 8) |

| (PMC_SLPWK_DR0) Peripheral 8 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR0_PID9 (0x1u << 9) |

| (PMC_SLPWK_DR0) Peripheral 9 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID32 (0x1u << 0) |

| (PMC_SLPWK_DR1) Peripheral 32 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID33 (0x1u << 1) |

| (PMC_SLPWK_DR1) Peripheral 33 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID34 (0x1u << 2) |

| (PMC_SLPWK_DR1) Peripheral 34 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID35 (0x1u << 3) |

| (PMC_SLPWK_DR1) Peripheral 35 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID37 (0x1u << 5) |

| (PMC_SLPWK_DR1) Peripheral 37 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID39 (0x1u << 7) |

| (PMC_SLPWK_DR1) Peripheral 39 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID40 (0x1u << 8) |

| (PMC_SLPWK_DR1) Peripheral 40 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID41 (0x1u << 9) |

| (PMC_SLPWK_DR1) Peripheral 41 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID42 (0x1u << 10) |

| (PMC_SLPWK_DR1) Peripheral 42 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID43 (0x1u << 11) |

| (PMC_SLPWK_DR1) Peripheral 43 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID44 (0x1u << 12) |

| (PMC_SLPWK_DR1) Peripheral 44 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID45 (0x1u << 13) |

| (PMC_SLPWK_DR1) Peripheral 45 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID46 (0x1u << 14) |

| (PMC_SLPWK_DR1) Peripheral 46 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID47 (0x1u << 15) |

| (PMC_SLPWK_DR1) Peripheral 47 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID48 (0x1u << 16) |

| (PMC_SLPWK_DR1) Peripheral 48 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID49 (0x1u << 17) |

| (PMC_SLPWK_DR1) Peripheral 49 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID50 (0x1u << 18) |

| (PMC_SLPWK_DR1) Peripheral 50 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID51 (0x1u << 19) |

| (PMC_SLPWK_DR1) Peripheral 51 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID52 (0x1u << 20) |

| (PMC_SLPWK_DR1) Peripheral 52 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID53 (0x1u << 21) |

| (PMC_SLPWK_DR1) Peripheral 53 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID56 (0x1u << 24) |

| (PMC_SLPWK_DR1) Peripheral 56 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID57 (0x1u << 25) |

| (PMC_SLPWK_DR1) Peripheral 57 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID58 (0x1u << 26) |

| (PMC_SLPWK_DR1) Peripheral 58 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID59 (0x1u << 27) |

| (PMC_SLPWK_DR1) Peripheral 59 SleepWalking Disable More... | |

| #define | PMC_SLPWK_DR1_PID60 (0x1u << 28) |

| (PMC_SLPWK_DR1) Peripheral 60 SleepWalking Disable More... | |

| #define | PMC_SLPWK_ER0_PID10 (0x1u << 10) |

| (PMC_SLPWK_ER0) Peripheral 10 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID11 (0x1u << 11) |

| (PMC_SLPWK_ER0) Peripheral 11 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID12 (0x1u << 12) |

| (PMC_SLPWK_ER0) Peripheral 12 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID13 (0x1u << 13) |

| (PMC_SLPWK_ER0) Peripheral 13 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID14 (0x1u << 14) |

| (PMC_SLPWK_ER0) Peripheral 14 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID15 (0x1u << 15) |

| (PMC_SLPWK_ER0) Peripheral 15 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID16 (0x1u << 16) |

| (PMC_SLPWK_ER0) Peripheral 16 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID17 (0x1u << 17) |

| (PMC_SLPWK_ER0) Peripheral 17 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID18 (0x1u << 18) |

| (PMC_SLPWK_ER0) Peripheral 18 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID19 (0x1u << 19) |

| (PMC_SLPWK_ER0) Peripheral 19 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID20 (0x1u << 20) |

| (PMC_SLPWK_ER0) Peripheral 20 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID21 (0x1u << 21) |

| (PMC_SLPWK_ER0) Peripheral 21 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID22 (0x1u << 22) |

| (PMC_SLPWK_ER0) Peripheral 22 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID23 (0x1u << 23) |

| (PMC_SLPWK_ER0) Peripheral 23 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID24 (0x1u << 24) |

| (PMC_SLPWK_ER0) Peripheral 24 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID25 (0x1u << 25) |

| (PMC_SLPWK_ER0) Peripheral 25 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID26 (0x1u << 26) |

| (PMC_SLPWK_ER0) Peripheral 26 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID27 (0x1u << 27) |

| (PMC_SLPWK_ER0) Peripheral 27 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID28 (0x1u << 28) |

| (PMC_SLPWK_ER0) Peripheral 28 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID29 (0x1u << 29) |

| (PMC_SLPWK_ER0) Peripheral 29 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID30 (0x1u << 30) |

| (PMC_SLPWK_ER0) Peripheral 30 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID31 (0x1u << 31) |

| (PMC_SLPWK_ER0) Peripheral 31 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID7 (0x1u << 7) |

| (PMC_SLPWK_ER0) Peripheral 7 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID8 (0x1u << 8) |

| (PMC_SLPWK_ER0) Peripheral 8 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER0_PID9 (0x1u << 9) |

| (PMC_SLPWK_ER0) Peripheral 9 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID32 (0x1u << 0) |

| (PMC_SLPWK_ER1) Peripheral 32 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID33 (0x1u << 1) |

| (PMC_SLPWK_ER1) Peripheral 33 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID34 (0x1u << 2) |

| (PMC_SLPWK_ER1) Peripheral 34 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID35 (0x1u << 3) |

| (PMC_SLPWK_ER1) Peripheral 35 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID37 (0x1u << 5) |

| (PMC_SLPWK_ER1) Peripheral 37 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID39 (0x1u << 7) |

| (PMC_SLPWK_ER1) Peripheral 39 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID40 (0x1u << 8) |

| (PMC_SLPWK_ER1) Peripheral 40 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID41 (0x1u << 9) |

| (PMC_SLPWK_ER1) Peripheral 41 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID42 (0x1u << 10) |

| (PMC_SLPWK_ER1) Peripheral 42 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID43 (0x1u << 11) |

| (PMC_SLPWK_ER1) Peripheral 43 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID44 (0x1u << 12) |

| (PMC_SLPWK_ER1) Peripheral 44 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID45 (0x1u << 13) |

| (PMC_SLPWK_ER1) Peripheral 45 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID46 (0x1u << 14) |

| (PMC_SLPWK_ER1) Peripheral 46 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID47 (0x1u << 15) |

| (PMC_SLPWK_ER1) Peripheral 47 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID48 (0x1u << 16) |

| (PMC_SLPWK_ER1) Peripheral 48 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID49 (0x1u << 17) |

| (PMC_SLPWK_ER1) Peripheral 49 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID50 (0x1u << 18) |

| (PMC_SLPWK_ER1) Peripheral 50 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID51 (0x1u << 19) |

| (PMC_SLPWK_ER1) Peripheral 51 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID52 (0x1u << 20) |

| (PMC_SLPWK_ER1) Peripheral 52 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID53 (0x1u << 21) |

| (PMC_SLPWK_ER1) Peripheral 53 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID56 (0x1u << 24) |

| (PMC_SLPWK_ER1) Peripheral 56 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID57 (0x1u << 25) |

| (PMC_SLPWK_ER1) Peripheral 57 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID58 (0x1u << 26) |

| (PMC_SLPWK_ER1) Peripheral 58 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID59 (0x1u << 27) |

| (PMC_SLPWK_ER1) Peripheral 59 SleepWalking Enable More... | |

| #define | PMC_SLPWK_ER1_PID60 (0x1u << 28) |

| (PMC_SLPWK_ER1) Peripheral 60 SleepWalking Enable More... | |

| #define | PMC_SLPWK_SR0_PID10 (0x1u << 10) |

| (PMC_SLPWK_SR0) Peripheral 10 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID11 (0x1u << 11) |

| (PMC_SLPWK_SR0) Peripheral 11 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID12 (0x1u << 12) |

| (PMC_SLPWK_SR0) Peripheral 12 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID13 (0x1u << 13) |

| (PMC_SLPWK_SR0) Peripheral 13 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID14 (0x1u << 14) |

| (PMC_SLPWK_SR0) Peripheral 14 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID15 (0x1u << 15) |

| (PMC_SLPWK_SR0) Peripheral 15 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID16 (0x1u << 16) |

| (PMC_SLPWK_SR0) Peripheral 16 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID17 (0x1u << 17) |

| (PMC_SLPWK_SR0) Peripheral 17 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID18 (0x1u << 18) |

| (PMC_SLPWK_SR0) Peripheral 18 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID19 (0x1u << 19) |

| (PMC_SLPWK_SR0) Peripheral 19 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID20 (0x1u << 20) |

| (PMC_SLPWK_SR0) Peripheral 20 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID21 (0x1u << 21) |

| (PMC_SLPWK_SR0) Peripheral 21 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID22 (0x1u << 22) |

| (PMC_SLPWK_SR0) Peripheral 22 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID23 (0x1u << 23) |

| (PMC_SLPWK_SR0) Peripheral 23 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID24 (0x1u << 24) |

| (PMC_SLPWK_SR0) Peripheral 24 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID25 (0x1u << 25) |

| (PMC_SLPWK_SR0) Peripheral 25 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID26 (0x1u << 26) |

| (PMC_SLPWK_SR0) Peripheral 26 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID27 (0x1u << 27) |

| (PMC_SLPWK_SR0) Peripheral 27 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID28 (0x1u << 28) |

| (PMC_SLPWK_SR0) Peripheral 28 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID29 (0x1u << 29) |

| (PMC_SLPWK_SR0) Peripheral 29 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID30 (0x1u << 30) |

| (PMC_SLPWK_SR0) Peripheral 30 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID31 (0x1u << 31) |

| (PMC_SLPWK_SR0) Peripheral 31 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID7 (0x1u << 7) |

| (PMC_SLPWK_SR0) Peripheral 7 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID8 (0x1u << 8) |

| (PMC_SLPWK_SR0) Peripheral 8 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR0_PID9 (0x1u << 9) |

| (PMC_SLPWK_SR0) Peripheral 9 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID32 (0x1u << 0) |

| (PMC_SLPWK_SR1) Peripheral 32 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID33 (0x1u << 1) |

| (PMC_SLPWK_SR1) Peripheral 33 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID34 (0x1u << 2) |

| (PMC_SLPWK_SR1) Peripheral 34 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID35 (0x1u << 3) |

| (PMC_SLPWK_SR1) Peripheral 35 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID37 (0x1u << 5) |

| (PMC_SLPWK_SR1) Peripheral 37 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID39 (0x1u << 7) |

| (PMC_SLPWK_SR1) Peripheral 39 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID40 (0x1u << 8) |

| (PMC_SLPWK_SR1) Peripheral 40 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID41 (0x1u << 9) |

| (PMC_SLPWK_SR1) Peripheral 41 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID42 (0x1u << 10) |

| (PMC_SLPWK_SR1) Peripheral 42 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID43 (0x1u << 11) |

| (PMC_SLPWK_SR1) Peripheral 43 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID44 (0x1u << 12) |

| (PMC_SLPWK_SR1) Peripheral 44 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID45 (0x1u << 13) |

| (PMC_SLPWK_SR1) Peripheral 45 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID46 (0x1u << 14) |

| (PMC_SLPWK_SR1) Peripheral 46 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID47 (0x1u << 15) |

| (PMC_SLPWK_SR1) Peripheral 47 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID48 (0x1u << 16) |

| (PMC_SLPWK_SR1) Peripheral 48 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID49 (0x1u << 17) |

| (PMC_SLPWK_SR1) Peripheral 49 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID50 (0x1u << 18) |

| (PMC_SLPWK_SR1) Peripheral 50 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID51 (0x1u << 19) |

| (PMC_SLPWK_SR1) Peripheral 51 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID52 (0x1u << 20) |

| (PMC_SLPWK_SR1) Peripheral 52 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID53 (0x1u << 21) |

| (PMC_SLPWK_SR1) Peripheral 53 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID56 (0x1u << 24) |

| (PMC_SLPWK_SR1) Peripheral 56 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID57 (0x1u << 25) |

| (PMC_SLPWK_SR1) Peripheral 57 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID58 (0x1u << 26) |

| (PMC_SLPWK_SR1) Peripheral 58 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID59 (0x1u << 27) |

| (PMC_SLPWK_SR1) Peripheral 59 SleepWalking Status More... | |

| #define | PMC_SLPWK_SR1_PID60 (0x1u << 28) |

| (PMC_SLPWK_SR1) Peripheral 60 SleepWalking Status More... | |

| #define | PMC_SR_CFDEV (0x1u << 18) |

| (PMC_SR) Clock Failure Detector Event More... | |

| #define | PMC_SR_CFDS (0x1u << 19) |

| (PMC_SR) Clock Failure Detector Status More... | |

| #define | PMC_SR_FOS (0x1u << 20) |

| (PMC_SR) Clock Failure Detector Fault Output Status More... | |

| #define | PMC_SR_LOCKA (0x1u << 1) |

| (PMC_SR) PLLA Lock Status More... | |

| #define | PMC_SR_LOCKU (0x1u << 6) |

| (PMC_SR) UTMI PLL Lock Status More... | |

| #define | PMC_SR_MCKRDY (0x1u << 3) |

| (PMC_SR) Master Clock Status More... | |

| #define | PMC_SR_MOSCRCS (0x1u << 17) |

| (PMC_SR) Main On-Chip RC Oscillator Status More... | |

| #define | PMC_SR_MOSCSELS (0x1u << 16) |

| (PMC_SR) Main Oscillator Selection Status More... | |

| #define | PMC_SR_MOSCXTS (0x1u << 0) |

| (PMC_SR) Main Crystal Oscillator Status More... | |

| #define | PMC_SR_OSCSELS (0x1u << 7) |

| (PMC_SR) Slow Clock Oscillator Selection More... | |

| #define | PMC_SR_PCKRDY0 (0x1u << 8) |

| (PMC_SR) Programmable Clock Ready Status More... | |

| #define | PMC_SR_PCKRDY1 (0x1u << 9) |

| (PMC_SR) Programmable Clock Ready Status More... | |

| #define | PMC_SR_PCKRDY2 (0x1u << 10) |

| (PMC_SR) Programmable Clock Ready Status More... | |

| #define | PMC_SR_PCKRDY3 (0x1u << 11) |

| (PMC_SR) Programmable Clock Ready Status More... | |

| #define | PMC_SR_PCKRDY4 (0x1u << 12) |

| (PMC_SR) Programmable Clock Ready Status More... | |

| #define | PMC_SR_PCKRDY5 (0x1u << 13) |

| (PMC_SR) Programmable Clock Ready Status More... | |

| #define | PMC_SR_PCKRDY6 (0x1u << 14) |

| (PMC_SR) Programmable Clock Ready Status More... | |

| #define | PMC_SR_XT32KERR (0x1u << 21) |

| (PMC_SR) Slow Crystal Oscillator Error More... | |

| #define | PMC_USB_USBDIV(value) ((PMC_USB_USBDIV_Msk & ((value) << PMC_USB_USBDIV_Pos))) |

| #define | PMC_USB_USBDIV_Msk (0xfu << PMC_USB_USBDIV_Pos) |

| (PMC_USB) Divider for USB Clock More... | |

| #define | PMC_USB_USBDIV_Pos 8 |

| #define | PMC_USB_USBS (0x1u << 0) |

| (PMC_USB) USB Input Clock Selection More... | |

| #define | PMC_VERSION_MFN_Msk (0x7u << PMC_VERSION_MFN_Pos) |

| (PMC_VERSION) Metal Fix Number More... | |

| #define | PMC_VERSION_MFN_Pos 16 |

| #define | PMC_VERSION_VERSION_Msk (0xfffu << PMC_VERSION_VERSION_Pos) |

| (PMC_VERSION) Version of the Hardware Module More... | |

| #define | PMC_VERSION_VERSION_Pos 0 |

| #define | PMC_WMST_KEY(value) ((PMC_WMST_KEY_Msk & ((value) << PMC_WMST_KEY_Pos))) |

| #define | PMC_WMST_KEY_Msk (0xffu << PMC_WMST_KEY_Pos) |

| (PMC_WMST) Write Access Password More... | |

| #define | PMC_WMST_KEY_PASSWD (0x5Au << 24) |

| (PMC_WMST) Writing any other value in this field aborts the write operation.Always reads as 0. More... | |

| #define | PMC_WMST_KEY_Pos 24 |

| #define | PMC_WMST_WMST(value) ((PMC_WMST_WMST_Msk & ((value) << PMC_WMST_WMST_Pos))) |

| #define | PMC_WMST_WMST_Msk (0xffu << PMC_WMST_WMST_Pos) |

| (PMC_WMST) Wait Mode Startup Time More... | |

| #define | PMC_WMST_WMST_Pos 0 |

| #define | PMC_WPMR_WPEN (0x1u << 0) |

| (PMC_WPMR) Write Protection Enable More... | |

| #define | PMC_WPMR_WPKEY(value) ((PMC_WPMR_WPKEY_Msk & ((value) << PMC_WPMR_WPKEY_Pos))) |

| #define | PMC_WPMR_WPKEY_Msk (0xffffffu << PMC_WPMR_WPKEY_Pos) |

| (PMC_WPMR) Write Protection Key More... | |

| #define | PMC_WPMR_WPKEY_PASSWD (0x504D43u << 8) |

| (PMC_WPMR) Writing any other value in this field aborts the write operation of the WPEN bit. Always reads as 0. More... | |

| #define | PMC_WPMR_WPKEY_Pos 8 |

| #define | PMC_WPSR_WPVS (0x1u << 0) |

| (PMC_WPSR) Write Protection Violation Status More... | |

| #define | PMC_WPSR_WPVSRC_Msk (0xffffu << PMC_WPSR_WPVSRC_Pos) |

| (PMC_WPSR) Write Protection Violation Source More... | |

| #define | PMC_WPSR_WPVSRC_Pos 8 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file utils/cmsis/same70/include/component/pmc.h.