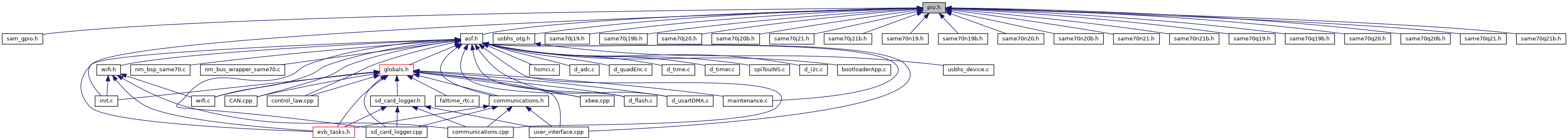

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Pio |

| Pio hardware registers. More... | |

Macros | |

| #define | PIO_ABCDSR_P0 (0x1u << 0) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P1 (0x1u << 1) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P10 (0x1u << 10) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P11 (0x1u << 11) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P12 (0x1u << 12) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P13 (0x1u << 13) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P14 (0x1u << 14) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P15 (0x1u << 15) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P16 (0x1u << 16) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P17 (0x1u << 17) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P18 (0x1u << 18) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P19 (0x1u << 19) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P2 (0x1u << 2) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P20 (0x1u << 20) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P21 (0x1u << 21) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P22 (0x1u << 22) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P23 (0x1u << 23) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P24 (0x1u << 24) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P25 (0x1u << 25) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P26 (0x1u << 26) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P27 (0x1u << 27) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P28 (0x1u << 28) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P29 (0x1u << 29) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P3 (0x1u << 3) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P30 (0x1u << 30) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P31 (0x1u << 31) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P4 (0x1u << 4) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P5 (0x1u << 5) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P6 (0x1u << 6) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P7 (0x1u << 7) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P8 (0x1u << 8) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_ABCDSR_P9 (0x1u << 9) |

| (PIO_ABCDSR[2]) Peripheral Select More... | |

| #define | PIO_AIMDR_P0 (0x1u << 0) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P1 (0x1u << 1) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P10 (0x1u << 10) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P11 (0x1u << 11) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P12 (0x1u << 12) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P13 (0x1u << 13) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P14 (0x1u << 14) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P15 (0x1u << 15) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P16 (0x1u << 16) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P17 (0x1u << 17) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P18 (0x1u << 18) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P19 (0x1u << 19) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P2 (0x1u << 2) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P20 (0x1u << 20) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P21 (0x1u << 21) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P22 (0x1u << 22) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P23 (0x1u << 23) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P24 (0x1u << 24) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P25 (0x1u << 25) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P26 (0x1u << 26) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P27 (0x1u << 27) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P28 (0x1u << 28) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P29 (0x1u << 29) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P3 (0x1u << 3) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P30 (0x1u << 30) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P31 (0x1u << 31) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P4 (0x1u << 4) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P5 (0x1u << 5) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P6 (0x1u << 6) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P7 (0x1u << 7) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P8 (0x1u << 8) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMDR_P9 (0x1u << 9) |

| (PIO_AIMDR) Additional Interrupt Modes Disable More... | |

| #define | PIO_AIMER_P0 (0x1u << 0) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P1 (0x1u << 1) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P10 (0x1u << 10) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P11 (0x1u << 11) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P12 (0x1u << 12) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P13 (0x1u << 13) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P14 (0x1u << 14) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P15 (0x1u << 15) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P16 (0x1u << 16) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P17 (0x1u << 17) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P18 (0x1u << 18) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P19 (0x1u << 19) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P2 (0x1u << 2) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P20 (0x1u << 20) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P21 (0x1u << 21) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P22 (0x1u << 22) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P23 (0x1u << 23) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P24 (0x1u << 24) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P25 (0x1u << 25) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P26 (0x1u << 26) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P27 (0x1u << 27) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P28 (0x1u << 28) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P29 (0x1u << 29) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P3 (0x1u << 3) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P30 (0x1u << 30) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P31 (0x1u << 31) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P4 (0x1u << 4) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P5 (0x1u << 5) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P6 (0x1u << 6) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P7 (0x1u << 7) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P8 (0x1u << 8) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMER_P9 (0x1u << 9) |

| (PIO_AIMER) Additional Interrupt Modes Enable More... | |

| #define | PIO_AIMMR_P0 (0x1u << 0) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P1 (0x1u << 1) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P10 (0x1u << 10) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P11 (0x1u << 11) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P12 (0x1u << 12) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P13 (0x1u << 13) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P14 (0x1u << 14) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P15 (0x1u << 15) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P16 (0x1u << 16) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P17 (0x1u << 17) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P18 (0x1u << 18) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P19 (0x1u << 19) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P2 (0x1u << 2) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P20 (0x1u << 20) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P21 (0x1u << 21) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P22 (0x1u << 22) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P23 (0x1u << 23) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P24 (0x1u << 24) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P25 (0x1u << 25) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P26 (0x1u << 26) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P27 (0x1u << 27) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P28 (0x1u << 28) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P29 (0x1u << 29) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P3 (0x1u << 3) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P30 (0x1u << 30) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P31 (0x1u << 31) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P4 (0x1u << 4) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P5 (0x1u << 5) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P6 (0x1u << 6) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P7 (0x1u << 7) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P8 (0x1u << 8) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_AIMMR_P9 (0x1u << 9) |

| (PIO_AIMMR) IO Line Index More... | |

| #define | PIO_CODR_P0 (0x1u << 0) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P1 (0x1u << 1) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P10 (0x1u << 10) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P11 (0x1u << 11) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P12 (0x1u << 12) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P13 (0x1u << 13) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P14 (0x1u << 14) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P15 (0x1u << 15) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P16 (0x1u << 16) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P17 (0x1u << 17) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P18 (0x1u << 18) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P19 (0x1u << 19) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P2 (0x1u << 2) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P20 (0x1u << 20) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P21 (0x1u << 21) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P22 (0x1u << 22) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P23 (0x1u << 23) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P24 (0x1u << 24) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P25 (0x1u << 25) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P26 (0x1u << 26) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P27 (0x1u << 27) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P28 (0x1u << 28) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P29 (0x1u << 29) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P3 (0x1u << 3) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P30 (0x1u << 30) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P31 (0x1u << 31) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P4 (0x1u << 4) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P5 (0x1u << 5) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P6 (0x1u << 6) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P7 (0x1u << 7) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P8 (0x1u << 8) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_CODR_P9 (0x1u << 9) |

| (PIO_CODR) Clear Output Data More... | |

| #define | PIO_DRIVER_LINE0 (0x1u << 0) |

| (PIO_DRIVER) Drive of PIO Line 0 More... | |

| #define | PIO_DRIVER_LINE0_HIGH_DRIVE (0x1u << 0) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE0_LOW_DRIVE (0x0u << 0) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE1 (0x1u << 1) |

| (PIO_DRIVER) Drive of PIO Line 1 More... | |

| #define | PIO_DRIVER_LINE10 (0x1u << 10) |

| (PIO_DRIVER) Drive of PIO Line 10 More... | |

| #define | PIO_DRIVER_LINE10_HIGH_DRIVE (0x1u << 10) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE10_LOW_DRIVE (0x0u << 10) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE11 (0x1u << 11) |

| (PIO_DRIVER) Drive of PIO Line 11 More... | |

| #define | PIO_DRIVER_LINE11_HIGH_DRIVE (0x1u << 11) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE11_LOW_DRIVE (0x0u << 11) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE12 (0x1u << 12) |

| (PIO_DRIVER) Drive of PIO Line 12 More... | |

| #define | PIO_DRIVER_LINE12_HIGH_DRIVE (0x1u << 12) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE12_LOW_DRIVE (0x0u << 12) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE13 (0x1u << 13) |

| (PIO_DRIVER) Drive of PIO Line 13 More... | |

| #define | PIO_DRIVER_LINE13_HIGH_DRIVE (0x1u << 13) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE13_LOW_DRIVE (0x0u << 13) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE14 (0x1u << 14) |

| (PIO_DRIVER) Drive of PIO Line 14 More... | |

| #define | PIO_DRIVER_LINE14_HIGH_DRIVE (0x1u << 14) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE14_LOW_DRIVE (0x0u << 14) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE15 (0x1u << 15) |

| (PIO_DRIVER) Drive of PIO Line 15 More... | |

| #define | PIO_DRIVER_LINE15_HIGH_DRIVE (0x1u << 15) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE15_LOW_DRIVE (0x0u << 15) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE16 (0x1u << 16) |

| (PIO_DRIVER) Drive of PIO Line 16 More... | |

| #define | PIO_DRIVER_LINE16_HIGH_DRIVE (0x1u << 16) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE16_LOW_DRIVE (0x0u << 16) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE17 (0x1u << 17) |

| (PIO_DRIVER) Drive of PIO Line 17 More... | |

| #define | PIO_DRIVER_LINE17_HIGH_DRIVE (0x1u << 17) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE17_LOW_DRIVE (0x0u << 17) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE18 (0x1u << 18) |

| (PIO_DRIVER) Drive of PIO Line 18 More... | |

| #define | PIO_DRIVER_LINE18_HIGH_DRIVE (0x1u << 18) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE18_LOW_DRIVE (0x0u << 18) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE19 (0x1u << 19) |

| (PIO_DRIVER) Drive of PIO Line 19 More... | |

| #define | PIO_DRIVER_LINE19_HIGH_DRIVE (0x1u << 19) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE19_LOW_DRIVE (0x0u << 19) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE1_HIGH_DRIVE (0x1u << 1) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE1_LOW_DRIVE (0x0u << 1) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE2 (0x1u << 2) |

| (PIO_DRIVER) Drive of PIO Line 2 More... | |

| #define | PIO_DRIVER_LINE20 (0x1u << 20) |

| (PIO_DRIVER) Drive of PIO Line 20 More... | |

| #define | PIO_DRIVER_LINE20_HIGH_DRIVE (0x1u << 20) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE20_LOW_DRIVE (0x0u << 20) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE21 (0x1u << 21) |

| (PIO_DRIVER) Drive of PIO Line 21 More... | |

| #define | PIO_DRIVER_LINE21_HIGH_DRIVE (0x1u << 21) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE21_LOW_DRIVE (0x0u << 21) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE22 (0x1u << 22) |

| (PIO_DRIVER) Drive of PIO Line 22 More... | |

| #define | PIO_DRIVER_LINE22_HIGH_DRIVE (0x1u << 22) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE22_LOW_DRIVE (0x0u << 22) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE23 (0x1u << 23) |

| (PIO_DRIVER) Drive of PIO Line 23 More... | |

| #define | PIO_DRIVER_LINE23_HIGH_DRIVE (0x1u << 23) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE23_LOW_DRIVE (0x0u << 23) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE24 (0x1u << 24) |

| (PIO_DRIVER) Drive of PIO Line 24 More... | |

| #define | PIO_DRIVER_LINE24_HIGH_DRIVE (0x1u << 24) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE24_LOW_DRIVE (0x0u << 24) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE25 (0x1u << 25) |

| (PIO_DRIVER) Drive of PIO Line 25 More... | |

| #define | PIO_DRIVER_LINE25_HIGH_DRIVE (0x1u << 25) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE25_LOW_DRIVE (0x0u << 25) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE26 (0x1u << 26) |

| (PIO_DRIVER) Drive of PIO Line 26 More... | |

| #define | PIO_DRIVER_LINE26_HIGH_DRIVE (0x1u << 26) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE26_LOW_DRIVE (0x0u << 26) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE27 (0x1u << 27) |

| (PIO_DRIVER) Drive of PIO Line 27 More... | |

| #define | PIO_DRIVER_LINE27_HIGH_DRIVE (0x1u << 27) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE27_LOW_DRIVE (0x0u << 27) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE28 (0x1u << 28) |

| (PIO_DRIVER) Drive of PIO Line 28 More... | |

| #define | PIO_DRIVER_LINE28_HIGH_DRIVE (0x1u << 28) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE28_LOW_DRIVE (0x0u << 28) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE29 (0x1u << 29) |

| (PIO_DRIVER) Drive of PIO Line 29 More... | |

| #define | PIO_DRIVER_LINE29_HIGH_DRIVE (0x1u << 29) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE29_LOW_DRIVE (0x0u << 29) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE2_HIGH_DRIVE (0x1u << 2) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE2_LOW_DRIVE (0x0u << 2) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE3 (0x1u << 3) |

| (PIO_DRIVER) Drive of PIO Line 3 More... | |

| #define | PIO_DRIVER_LINE30 (0x1u << 30) |

| (PIO_DRIVER) Drive of PIO Line 30 More... | |

| #define | PIO_DRIVER_LINE30_HIGH_DRIVE (0x1u << 30) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE30_LOW_DRIVE (0x0u << 30) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE31 (0x1u << 31) |

| (PIO_DRIVER) Drive of PIO Line 31 More... | |

| #define | PIO_DRIVER_LINE31_HIGH_DRIVE (0x1u << 31) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE31_LOW_DRIVE (0x0u << 31) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE3_HIGH_DRIVE (0x1u << 3) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE3_LOW_DRIVE (0x0u << 3) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE4 (0x1u << 4) |

| (PIO_DRIVER) Drive of PIO Line 4 More... | |

| #define | PIO_DRIVER_LINE4_HIGH_DRIVE (0x1u << 4) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE4_LOW_DRIVE (0x0u << 4) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE5 (0x1u << 5) |

| (PIO_DRIVER) Drive of PIO Line 5 More... | |

| #define | PIO_DRIVER_LINE5_HIGH_DRIVE (0x1u << 5) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE5_LOW_DRIVE (0x0u << 5) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE6 (0x1u << 6) |

| (PIO_DRIVER) Drive of PIO Line 6 More... | |

| #define | PIO_DRIVER_LINE6_HIGH_DRIVE (0x1u << 6) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE6_LOW_DRIVE (0x0u << 6) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE7 (0x1u << 7) |

| (PIO_DRIVER) Drive of PIO Line 7 More... | |

| #define | PIO_DRIVER_LINE7_HIGH_DRIVE (0x1u << 7) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE7_LOW_DRIVE (0x0u << 7) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE8 (0x1u << 8) |

| (PIO_DRIVER) Drive of PIO Line 8 More... | |

| #define | PIO_DRIVER_LINE8_HIGH_DRIVE (0x1u << 8) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE8_LOW_DRIVE (0x0u << 8) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_DRIVER_LINE9 (0x1u << 9) |

| (PIO_DRIVER) Drive of PIO Line 9 More... | |

| #define | PIO_DRIVER_LINE9_HIGH_DRIVE (0x1u << 9) |

| (PIO_DRIVER) Highest drive More... | |

| #define | PIO_DRIVER_LINE9_LOW_DRIVE (0x0u << 9) |

| (PIO_DRIVER) Lowest drive More... | |

| #define | PIO_ELSR_P0 (0x1u << 0) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P1 (0x1u << 1) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P10 (0x1u << 10) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P11 (0x1u << 11) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P12 (0x1u << 12) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P13 (0x1u << 13) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P14 (0x1u << 14) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P15 (0x1u << 15) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P16 (0x1u << 16) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P17 (0x1u << 17) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P18 (0x1u << 18) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P19 (0x1u << 19) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P2 (0x1u << 2) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P20 (0x1u << 20) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P21 (0x1u << 21) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P22 (0x1u << 22) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P23 (0x1u << 23) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P24 (0x1u << 24) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P25 (0x1u << 25) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P26 (0x1u << 26) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P27 (0x1u << 27) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P28 (0x1u << 28) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P29 (0x1u << 29) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P3 (0x1u << 3) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P30 (0x1u << 30) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P31 (0x1u << 31) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P4 (0x1u << 4) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P5 (0x1u << 5) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P6 (0x1u << 6) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P7 (0x1u << 7) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P8 (0x1u << 8) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ELSR_P9 (0x1u << 9) |

| (PIO_ELSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_ESR_P0 (0x1u << 0) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P1 (0x1u << 1) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P10 (0x1u << 10) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P11 (0x1u << 11) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P12 (0x1u << 12) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P13 (0x1u << 13) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P14 (0x1u << 14) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P15 (0x1u << 15) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P16 (0x1u << 16) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P17 (0x1u << 17) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P18 (0x1u << 18) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P19 (0x1u << 19) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P2 (0x1u << 2) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P20 (0x1u << 20) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P21 (0x1u << 21) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P22 (0x1u << 22) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P23 (0x1u << 23) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P24 (0x1u << 24) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P25 (0x1u << 25) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P26 (0x1u << 26) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P27 (0x1u << 27) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P28 (0x1u << 28) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P29 (0x1u << 29) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P3 (0x1u << 3) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P30 (0x1u << 30) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P31 (0x1u << 31) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P4 (0x1u << 4) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P5 (0x1u << 5) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P6 (0x1u << 6) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P7 (0x1u << 7) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P8 (0x1u << 8) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_ESR_P9 (0x1u << 9) |

| (PIO_ESR) Edge Interrupt Selection More... | |

| #define | PIO_FELLSR_P0 (0x1u << 0) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P1 (0x1u << 1) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P10 (0x1u << 10) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P11 (0x1u << 11) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P12 (0x1u << 12) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P13 (0x1u << 13) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P14 (0x1u << 14) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P15 (0x1u << 15) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P16 (0x1u << 16) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P17 (0x1u << 17) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P18 (0x1u << 18) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P19 (0x1u << 19) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P2 (0x1u << 2) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P20 (0x1u << 20) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P21 (0x1u << 21) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P22 (0x1u << 22) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P23 (0x1u << 23) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P24 (0x1u << 24) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P25 (0x1u << 25) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P26 (0x1u << 26) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P27 (0x1u << 27) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P28 (0x1u << 28) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P29 (0x1u << 29) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P3 (0x1u << 3) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P30 (0x1u << 30) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P31 (0x1u << 31) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P4 (0x1u << 4) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P5 (0x1u << 5) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P6 (0x1u << 6) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P7 (0x1u << 7) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P8 (0x1u << 8) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FELLSR_P9 (0x1u << 9) |

| (PIO_FELLSR) Falling Edge/Low-Level Interrupt Selection More... | |

| #define | PIO_FRLHSR_P0 (0x1u << 0) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P1 (0x1u << 1) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P10 (0x1u << 10) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P11 (0x1u << 11) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P12 (0x1u << 12) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P13 (0x1u << 13) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P14 (0x1u << 14) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P15 (0x1u << 15) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P16 (0x1u << 16) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P17 (0x1u << 17) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P18 (0x1u << 18) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P19 (0x1u << 19) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P2 (0x1u << 2) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P20 (0x1u << 20) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P21 (0x1u << 21) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P22 (0x1u << 22) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P23 (0x1u << 23) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P24 (0x1u << 24) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P25 (0x1u << 25) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P26 (0x1u << 26) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P27 (0x1u << 27) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P28 (0x1u << 28) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P29 (0x1u << 29) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P3 (0x1u << 3) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P30 (0x1u << 30) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P31 (0x1u << 31) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P4 (0x1u << 4) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P5 (0x1u << 5) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P6 (0x1u << 6) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P7 (0x1u << 7) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P8 (0x1u << 8) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_FRLHSR_P9 (0x1u << 9) |

| (PIO_FRLHSR) Edge/Level Interrupt Source Selection More... | |

| #define | PIO_IDR_P0 (0x1u << 0) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P1 (0x1u << 1) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P10 (0x1u << 10) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P11 (0x1u << 11) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P12 (0x1u << 12) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P13 (0x1u << 13) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P14 (0x1u << 14) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P15 (0x1u << 15) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P16 (0x1u << 16) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P17 (0x1u << 17) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P18 (0x1u << 18) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P19 (0x1u << 19) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P2 (0x1u << 2) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P20 (0x1u << 20) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P21 (0x1u << 21) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P22 (0x1u << 22) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P23 (0x1u << 23) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P24 (0x1u << 24) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P25 (0x1u << 25) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P26 (0x1u << 26) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P27 (0x1u << 27) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P28 (0x1u << 28) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P29 (0x1u << 29) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P3 (0x1u << 3) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P30 (0x1u << 30) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P31 (0x1u << 31) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P4 (0x1u << 4) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P5 (0x1u << 5) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P6 (0x1u << 6) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P7 (0x1u << 7) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P8 (0x1u << 8) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IDR_P9 (0x1u << 9) |

| (PIO_IDR) Input Change Interrupt Disable More... | |

| #define | PIO_IER_P0 (0x1u << 0) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P1 (0x1u << 1) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P10 (0x1u << 10) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P11 (0x1u << 11) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P12 (0x1u << 12) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P13 (0x1u << 13) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P14 (0x1u << 14) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P15 (0x1u << 15) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P16 (0x1u << 16) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P17 (0x1u << 17) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P18 (0x1u << 18) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P19 (0x1u << 19) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P2 (0x1u << 2) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P20 (0x1u << 20) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P21 (0x1u << 21) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P22 (0x1u << 22) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P23 (0x1u << 23) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P24 (0x1u << 24) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P25 (0x1u << 25) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P26 (0x1u << 26) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P27 (0x1u << 27) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P28 (0x1u << 28) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P29 (0x1u << 29) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P3 (0x1u << 3) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P30 (0x1u << 30) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P31 (0x1u << 31) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P4 (0x1u << 4) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P5 (0x1u << 5) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P6 (0x1u << 6) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P7 (0x1u << 7) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P8 (0x1u << 8) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IER_P9 (0x1u << 9) |

| (PIO_IER) Input Change Interrupt Enable More... | |

| #define | PIO_IFDR_P0 (0x1u << 0) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P1 (0x1u << 1) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P10 (0x1u << 10) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P11 (0x1u << 11) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P12 (0x1u << 12) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P13 (0x1u << 13) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P14 (0x1u << 14) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P15 (0x1u << 15) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P16 (0x1u << 16) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P17 (0x1u << 17) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P18 (0x1u << 18) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P19 (0x1u << 19) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P2 (0x1u << 2) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P20 (0x1u << 20) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P21 (0x1u << 21) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P22 (0x1u << 22) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P23 (0x1u << 23) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P24 (0x1u << 24) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P25 (0x1u << 25) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P26 (0x1u << 26) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P27 (0x1u << 27) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P28 (0x1u << 28) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P29 (0x1u << 29) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P3 (0x1u << 3) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P30 (0x1u << 30) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P31 (0x1u << 31) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P4 (0x1u << 4) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P5 (0x1u << 5) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P6 (0x1u << 6) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P7 (0x1u << 7) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P8 (0x1u << 8) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFDR_P9 (0x1u << 9) |

| (PIO_IFDR) Input Filter Disable More... | |

| #define | PIO_IFER_P0 (0x1u << 0) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P1 (0x1u << 1) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P10 (0x1u << 10) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P11 (0x1u << 11) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P12 (0x1u << 12) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P13 (0x1u << 13) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P14 (0x1u << 14) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P15 (0x1u << 15) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P16 (0x1u << 16) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P17 (0x1u << 17) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P18 (0x1u << 18) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P19 (0x1u << 19) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P2 (0x1u << 2) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P20 (0x1u << 20) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P21 (0x1u << 21) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P22 (0x1u << 22) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P23 (0x1u << 23) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P24 (0x1u << 24) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P25 (0x1u << 25) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P26 (0x1u << 26) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P27 (0x1u << 27) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P28 (0x1u << 28) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P29 (0x1u << 29) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P3 (0x1u << 3) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P30 (0x1u << 30) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P31 (0x1u << 31) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P4 (0x1u << 4) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P5 (0x1u << 5) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P6 (0x1u << 6) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P7 (0x1u << 7) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P8 (0x1u << 8) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFER_P9 (0x1u << 9) |

| (PIO_IFER) Input Filter Enable More... | |

| #define | PIO_IFSCDR_P0 (0x1u << 0) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P1 (0x1u << 1) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P10 (0x1u << 10) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P11 (0x1u << 11) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P12 (0x1u << 12) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P13 (0x1u << 13) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P14 (0x1u << 14) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P15 (0x1u << 15) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P16 (0x1u << 16) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P17 (0x1u << 17) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P18 (0x1u << 18) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P19 (0x1u << 19) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P2 (0x1u << 2) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P20 (0x1u << 20) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P21 (0x1u << 21) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P22 (0x1u << 22) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P23 (0x1u << 23) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P24 (0x1u << 24) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P25 (0x1u << 25) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P26 (0x1u << 26) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P27 (0x1u << 27) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P28 (0x1u << 28) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P29 (0x1u << 29) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P3 (0x1u << 3) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P30 (0x1u << 30) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P31 (0x1u << 31) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P4 (0x1u << 4) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P5 (0x1u << 5) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P6 (0x1u << 6) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P7 (0x1u << 7) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P8 (0x1u << 8) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCDR_P9 (0x1u << 9) |

| (PIO_IFSCDR) Peripheral Clock Glitch Filtering Select More... | |

| #define | PIO_IFSCER_P0 (0x1u << 0) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P1 (0x1u << 1) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P10 (0x1u << 10) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P11 (0x1u << 11) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P12 (0x1u << 12) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P13 (0x1u << 13) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P14 (0x1u << 14) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P15 (0x1u << 15) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P16 (0x1u << 16) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P17 (0x1u << 17) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P18 (0x1u << 18) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P19 (0x1u << 19) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P2 (0x1u << 2) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P20 (0x1u << 20) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P21 (0x1u << 21) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P22 (0x1u << 22) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P23 (0x1u << 23) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P24 (0x1u << 24) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P25 (0x1u << 25) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P26 (0x1u << 26) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P27 (0x1u << 27) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P28 (0x1u << 28) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P29 (0x1u << 29) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P3 (0x1u << 3) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P30 (0x1u << 30) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P31 (0x1u << 31) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P4 (0x1u << 4) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P5 (0x1u << 5) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P6 (0x1u << 6) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P7 (0x1u << 7) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P8 (0x1u << 8) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCER_P9 (0x1u << 9) |

| (PIO_IFSCER) Slow Clock Debouncing Filtering Select More... | |

| #define | PIO_IFSCSR_P0 (0x1u << 0) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P1 (0x1u << 1) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P10 (0x1u << 10) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P11 (0x1u << 11) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P12 (0x1u << 12) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P13 (0x1u << 13) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P14 (0x1u << 14) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P15 (0x1u << 15) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P16 (0x1u << 16) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P17 (0x1u << 17) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P18 (0x1u << 18) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P19 (0x1u << 19) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P2 (0x1u << 2) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P20 (0x1u << 20) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P21 (0x1u << 21) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P22 (0x1u << 22) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P23 (0x1u << 23) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P24 (0x1u << 24) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P25 (0x1u << 25) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P26 (0x1u << 26) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P27 (0x1u << 27) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P28 (0x1u << 28) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P29 (0x1u << 29) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P3 (0x1u << 3) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P30 (0x1u << 30) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P31 (0x1u << 31) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P4 (0x1u << 4) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P5 (0x1u << 5) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P6 (0x1u << 6) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P7 (0x1u << 7) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P8 (0x1u << 8) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSCSR_P9 (0x1u << 9) |

| (PIO_IFSCSR) Glitch or Debouncing Filter Selection Status More... | |

| #define | PIO_IFSR_P0 (0x1u << 0) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P1 (0x1u << 1) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P10 (0x1u << 10) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P11 (0x1u << 11) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P12 (0x1u << 12) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P13 (0x1u << 13) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P14 (0x1u << 14) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P15 (0x1u << 15) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P16 (0x1u << 16) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P17 (0x1u << 17) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P18 (0x1u << 18) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P19 (0x1u << 19) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P2 (0x1u << 2) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P20 (0x1u << 20) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P21 (0x1u << 21) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P22 (0x1u << 22) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P23 (0x1u << 23) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P24 (0x1u << 24) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P25 (0x1u << 25) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P26 (0x1u << 26) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P27 (0x1u << 27) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P28 (0x1u << 28) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P29 (0x1u << 29) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P3 (0x1u << 3) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P30 (0x1u << 30) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P31 (0x1u << 31) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P4 (0x1u << 4) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P5 (0x1u << 5) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P6 (0x1u << 6) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P7 (0x1u << 7) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P8 (0x1u << 8) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IFSR_P9 (0x1u << 9) |

| (PIO_IFSR) Input Filter Status More... | |

| #define | PIO_IMR_P0 (0x1u << 0) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P1 (0x1u << 1) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P10 (0x1u << 10) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P11 (0x1u << 11) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P12 (0x1u << 12) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P13 (0x1u << 13) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P14 (0x1u << 14) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P15 (0x1u << 15) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P16 (0x1u << 16) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P17 (0x1u << 17) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P18 (0x1u << 18) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P19 (0x1u << 19) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P2 (0x1u << 2) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P20 (0x1u << 20) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P21 (0x1u << 21) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P22 (0x1u << 22) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P23 (0x1u << 23) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P24 (0x1u << 24) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P25 (0x1u << 25) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P26 (0x1u << 26) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P27 (0x1u << 27) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P28 (0x1u << 28) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P29 (0x1u << 29) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P3 (0x1u << 3) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P30 (0x1u << 30) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P31 (0x1u << 31) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P4 (0x1u << 4) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P5 (0x1u << 5) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P6 (0x1u << 6) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P7 (0x1u << 7) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P8 (0x1u << 8) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_IMR_P9 (0x1u << 9) |

| (PIO_IMR) Input Change Interrupt Mask More... | |

| #define | PIO_ISR_P0 (0x1u << 0) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P1 (0x1u << 1) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P10 (0x1u << 10) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P11 (0x1u << 11) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P12 (0x1u << 12) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P13 (0x1u << 13) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P14 (0x1u << 14) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P15 (0x1u << 15) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P16 (0x1u << 16) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P17 (0x1u << 17) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P18 (0x1u << 18) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P19 (0x1u << 19) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P2 (0x1u << 2) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P20 (0x1u << 20) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P21 (0x1u << 21) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P22 (0x1u << 22) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P23 (0x1u << 23) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P24 (0x1u << 24) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P25 (0x1u << 25) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P26 (0x1u << 26) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P27 (0x1u << 27) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P28 (0x1u << 28) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P29 (0x1u << 29) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P3 (0x1u << 3) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P30 (0x1u << 30) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P31 (0x1u << 31) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P4 (0x1u << 4) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P5 (0x1u << 5) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P6 (0x1u << 6) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P7 (0x1u << 7) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P8 (0x1u << 8) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_ISR_P9 (0x1u << 9) |

| (PIO_ISR) Input Change Interrupt Status More... | |

| #define | PIO_LOCKSR_P0 (0x1u << 0) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P1 (0x1u << 1) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P10 (0x1u << 10) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P11 (0x1u << 11) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P12 (0x1u << 12) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P13 (0x1u << 13) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P14 (0x1u << 14) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P15 (0x1u << 15) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P16 (0x1u << 16) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P17 (0x1u << 17) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P18 (0x1u << 18) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P19 (0x1u << 19) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P2 (0x1u << 2) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P20 (0x1u << 20) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P21 (0x1u << 21) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P22 (0x1u << 22) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P23 (0x1u << 23) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P24 (0x1u << 24) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P25 (0x1u << 25) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P26 (0x1u << 26) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P27 (0x1u << 27) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P28 (0x1u << 28) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P29 (0x1u << 29) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P3 (0x1u << 3) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P30 (0x1u << 30) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P31 (0x1u << 31) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P4 (0x1u << 4) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P5 (0x1u << 5) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P6 (0x1u << 6) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P7 (0x1u << 7) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P8 (0x1u << 8) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LOCKSR_P9 (0x1u << 9) |

| (PIO_LOCKSR) Lock Status More... | |

| #define | PIO_LSR_P0 (0x1u << 0) |

| (PIO_LSR) Level Interrupt Selection More... | |

| #define | PIO_LSR_P1 (0x1u << 1) |

| (PIO_LSR) Level Interrupt Selection More... | |

| #define | PIO_LSR_P10 (0x1u << 10) |

| (PIO_LSR) Level Interrupt Selection More... | |

| #define | PIO_LSR_P11 (0x1u << 11) |

| (PIO_LSR) Level Interrupt Selection More... | |

| #define | PIO_LSR_P12 (0x1u << 12) |

| (PIO_LSR) Level Interrupt Selection More... | |

| #define | PIO_LSR_P13 (0x1u << 13) |

| (PIO_LSR) Level Interrupt Selection More... | |

| #define | PIO_LSR_P14 (0x1u << 14) |

| (PIO_LSR) Level Interrupt Selection More... | |

| #define | PIO_LSR_P15 (0x1u << 15) |

| (PIO_LSR) Level Interrupt Selection More... | |

| #define | PIO_LSR_P16 (0x1u << 16) |