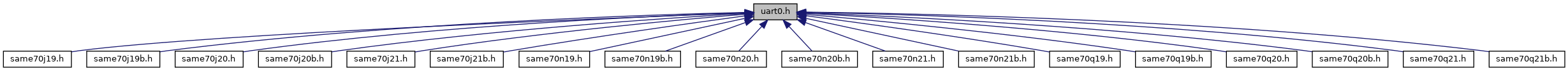

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | REG_UART0_BRGR (*(__IO uint32_t*)0x400E0820U) |

| (UART0) Baud Rate Generator Register More... | |

| #define | REG_UART0_CMPR (*(__IO uint32_t*)0x400E0824U) |

| (UART0) Comparison Register More... | |

| #define | REG_UART0_CR (*(__O uint32_t*)0x400E0800U) |

| (UART0) Control Register More... | |

| #define | REG_UART0_IDR (*(__O uint32_t*)0x400E080CU) |

| (UART0) Interrupt Disable Register More... | |

| #define | REG_UART0_IER (*(__O uint32_t*)0x400E0808U) |

| (UART0) Interrupt Enable Register More... | |

| #define | REG_UART0_IMR (*(__I uint32_t*)0x400E0810U) |

| (UART0) Interrupt Mask Register More... | |

| #define | REG_UART0_MR (*(__IO uint32_t*)0x400E0804U) |

| (UART0) Mode Register More... | |

| #define | REG_UART0_RHR (*(__I uint32_t*)0x400E0818U) |

| (UART0) Receive Holding Register More... | |

| #define | REG_UART0_SR (*(__I uint32_t*)0x400E0814U) |

| (UART0) Status Register More... | |

| #define | REG_UART0_THR (*(__O uint32_t*)0x400E081CU) |

| (UART0) Transmit Holding Register More... | |

| #define | REG_UART0_VERSION (*(__I uint32_t*)0x400E08FCU) |

| (UART0) Version Register More... | |

| #define | REG_UART0_WPMR (*(__IO uint32_t*)0x400E08E4U) |

| (UART0) Write Protection Mode Register More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file uart0.h.

Macro Definition Documentation

◆ REG_UART0_BRGR

| #define REG_UART0_BRGR (*(__IO uint32_t*)0x400E0820U) |

◆ REG_UART0_CMPR

| #define REG_UART0_CMPR (*(__IO uint32_t*)0x400E0824U) |

◆ REG_UART0_CR

| #define REG_UART0_CR (*(__O uint32_t*)0x400E0800U) |

◆ REG_UART0_IDR

| #define REG_UART0_IDR (*(__O uint32_t*)0x400E080CU) |

◆ REG_UART0_IER

| #define REG_UART0_IER (*(__O uint32_t*)0x400E0808U) |

◆ REG_UART0_IMR

| #define REG_UART0_IMR (*(__I uint32_t*)0x400E0810U) |

◆ REG_UART0_MR

| #define REG_UART0_MR (*(__IO uint32_t*)0x400E0804U) |

◆ REG_UART0_RHR

| #define REG_UART0_RHR (*(__I uint32_t*)0x400E0818U) |

◆ REG_UART0_SR

| #define REG_UART0_SR (*(__I uint32_t*)0x400E0814U) |

◆ REG_UART0_THR

| #define REG_UART0_THR (*(__O uint32_t*)0x400E081CU) |

◆ REG_UART0_VERSION

| #define REG_UART0_VERSION (*(__I uint32_t*)0x400E08FCU) |