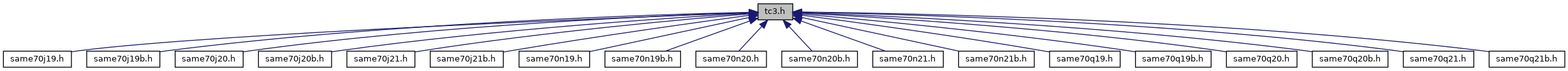

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | REG_TC3_BCR (*(__O uint32_t*)0x400540C0U) |

| (TC3) Block Control Register More... | |

| #define | REG_TC3_BMR (*(__IO uint32_t*)0x400540C4U) |

| (TC3) Block Mode Register More... | |

| #define | REG_TC3_CCR0 (*(__O uint32_t*)0x40054000U) |

| (TC3) Channel Control Register (channel = 0) More... | |

| #define | REG_TC3_CCR1 (*(__O uint32_t*)0x40054040U) |

| (TC3) Channel Control Register (channel = 1) More... | |

| #define | REG_TC3_CCR2 (*(__O uint32_t*)0x40054080U) |

| (TC3) Channel Control Register (channel = 2) More... | |

| #define | REG_TC3_CMR0 (*(__IO uint32_t*)0x40054004U) |

| (TC3) Channel Mode Register (channel = 0) More... | |

| #define | REG_TC3_CMR1 (*(__IO uint32_t*)0x40054044U) |

| (TC3) Channel Mode Register (channel = 1) More... | |

| #define | REG_TC3_CMR2 (*(__IO uint32_t*)0x40054084U) |

| (TC3) Channel Mode Register (channel = 2) More... | |

| #define | REG_TC3_CV0 (*(__I uint32_t*)0x40054010U) |

| (TC3) Counter Value (channel = 0) More... | |

| #define | REG_TC3_CV1 (*(__I uint32_t*)0x40054050U) |

| (TC3) Counter Value (channel = 1) More... | |

| #define | REG_TC3_CV2 (*(__I uint32_t*)0x40054090U) |

| (TC3) Counter Value (channel = 2) More... | |

| #define | REG_TC3_EMR0 (*(__IO uint32_t*)0x40054030U) |

| (TC3) Extended Mode Register (channel = 0) More... | |

| #define | REG_TC3_EMR1 (*(__IO uint32_t*)0x40054070U) |

| (TC3) Extended Mode Register (channel = 1) More... | |

| #define | REG_TC3_EMR2 (*(__IO uint32_t*)0x400540B0U) |

| (TC3) Extended Mode Register (channel = 2) More... | |

| #define | REG_TC3_FMR (*(__IO uint32_t*)0x400540D8U) |

| (TC3) Fault Mode Register More... | |

| #define | REG_TC3_IDR0 (*(__O uint32_t*)0x40054028U) |

| (TC3) Interrupt Disable Register (channel = 0) More... | |

| #define | REG_TC3_IDR1 (*(__O uint32_t*)0x40054068U) |

| (TC3) Interrupt Disable Register (channel = 1) More... | |

| #define | REG_TC3_IDR2 (*(__O uint32_t*)0x400540A8U) |

| (TC3) Interrupt Disable Register (channel = 2) More... | |

| #define | REG_TC3_IER0 (*(__O uint32_t*)0x40054024U) |

| (TC3) Interrupt Enable Register (channel = 0) More... | |

| #define | REG_TC3_IER1 (*(__O uint32_t*)0x40054064U) |

| (TC3) Interrupt Enable Register (channel = 1) More... | |

| #define | REG_TC3_IER2 (*(__O uint32_t*)0x400540A4U) |

| (TC3) Interrupt Enable Register (channel = 2) More... | |

| #define | REG_TC3_IMR0 (*(__I uint32_t*)0x4005402CU) |

| (TC3) Interrupt Mask Register (channel = 0) More... | |

| #define | REG_TC3_IMR1 (*(__I uint32_t*)0x4005406CU) |

| (TC3) Interrupt Mask Register (channel = 1) More... | |

| #define | REG_TC3_IMR2 (*(__I uint32_t*)0x400540ACU) |

| (TC3) Interrupt Mask Register (channel = 2) More... | |

| #define | REG_TC3_QIDR (*(__O uint32_t*)0x400540CCU) |

| (TC3) QDEC Interrupt Disable Register More... | |

| #define | REG_TC3_QIER (*(__O uint32_t*)0x400540C8U) |

| (TC3) QDEC Interrupt Enable Register More... | |

| #define | REG_TC3_QIMR (*(__I uint32_t*)0x400540D0U) |

| (TC3) QDEC Interrupt Mask Register More... | |

| #define | REG_TC3_QISR (*(__I uint32_t*)0x400540D4U) |

| (TC3) QDEC Interrupt Status Register More... | |

| #define | REG_TC3_RA0 (*(__IO uint32_t*)0x40054014U) |

| (TC3) Register A (channel = 0) More... | |

| #define | REG_TC3_RA1 (*(__IO uint32_t*)0x40054054U) |

| (TC3) Register A (channel = 1) More... | |

| #define | REG_TC3_RA2 (*(__IO uint32_t*)0x40054094U) |

| (TC3) Register A (channel = 2) More... | |

| #define | REG_TC3_RAB0 (*(__I uint32_t*)0x4005400CU) |

| (TC3) Register AB (channel = 0) More... | |

| #define | REG_TC3_RAB1 (*(__I uint32_t*)0x4005404CU) |

| (TC3) Register AB (channel = 1) More... | |

| #define | REG_TC3_RAB2 (*(__I uint32_t*)0x4005408CU) |

| (TC3) Register AB (channel = 2) More... | |

| #define | REG_TC3_RB0 (*(__IO uint32_t*)0x40054018U) |

| (TC3) Register B (channel = 0) More... | |

| #define | REG_TC3_RB1 (*(__IO uint32_t*)0x40054058U) |

| (TC3) Register B (channel = 1) More... | |

| #define | REG_TC3_RB2 (*(__IO uint32_t*)0x40054098U) |

| (TC3) Register B (channel = 2) More... | |

| #define | REG_TC3_RC0 (*(__IO uint32_t*)0x4005401CU) |

| (TC3) Register C (channel = 0) More... | |

| #define | REG_TC3_RC1 (*(__IO uint32_t*)0x4005405CU) |

| (TC3) Register C (channel = 1) More... | |

| #define | REG_TC3_RC2 (*(__IO uint32_t*)0x4005409CU) |

| (TC3) Register C (channel = 2) More... | |

| #define | REG_TC3_SMMR0 (*(__IO uint32_t*)0x40054008U) |

| (TC3) Stepper Motor Mode Register (channel = 0) More... | |

| #define | REG_TC3_SMMR1 (*(__IO uint32_t*)0x40054048U) |

| (TC3) Stepper Motor Mode Register (channel = 1) More... | |

| #define | REG_TC3_SMMR2 (*(__IO uint32_t*)0x40054088U) |

| (TC3) Stepper Motor Mode Register (channel = 2) More... | |

| #define | REG_TC3_SR0 (*(__I uint32_t*)0x40054020U) |

| (TC3) Status Register (channel = 0) More... | |

| #define | REG_TC3_SR1 (*(__I uint32_t*)0x40054060U) |

| (TC3) Status Register (channel = 1) More... | |

| #define | REG_TC3_SR2 (*(__I uint32_t*)0x400540A0U) |

| (TC3) Status Register (channel = 2) More... | |

| #define | REG_TC3_VER (*(__I uint32_t*)0x400540FCU) |

| (TC3) Version Register More... | |

| #define | REG_TC3_WPMR (*(__IO uint32_t*)0x400540E4U) |

| (TC3) Write Protection Mode Register More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file tc3.h.

Macro Definition Documentation

◆ REG_TC3_BCR

| #define REG_TC3_BCR (*(__O uint32_t*)0x400540C0U) |

◆ REG_TC3_BMR

| #define REG_TC3_BMR (*(__IO uint32_t*)0x400540C4U) |

◆ REG_TC3_CCR0

| #define REG_TC3_CCR0 (*(__O uint32_t*)0x40054000U) |

◆ REG_TC3_CCR1

| #define REG_TC3_CCR1 (*(__O uint32_t*)0x40054040U) |

◆ REG_TC3_CCR2

| #define REG_TC3_CCR2 (*(__O uint32_t*)0x40054080U) |

◆ REG_TC3_CMR0

| #define REG_TC3_CMR0 (*(__IO uint32_t*)0x40054004U) |

◆ REG_TC3_CMR1

| #define REG_TC3_CMR1 (*(__IO uint32_t*)0x40054044U) |

◆ REG_TC3_CMR2

| #define REG_TC3_CMR2 (*(__IO uint32_t*)0x40054084U) |

◆ REG_TC3_CV0

| #define REG_TC3_CV0 (*(__I uint32_t*)0x40054010U) |

◆ REG_TC3_CV1

| #define REG_TC3_CV1 (*(__I uint32_t*)0x40054050U) |

◆ REG_TC3_CV2

| #define REG_TC3_CV2 (*(__I uint32_t*)0x40054090U) |

◆ REG_TC3_EMR0

| #define REG_TC3_EMR0 (*(__IO uint32_t*)0x40054030U) |

◆ REG_TC3_EMR1

| #define REG_TC3_EMR1 (*(__IO uint32_t*)0x40054070U) |

◆ REG_TC3_EMR2

| #define REG_TC3_EMR2 (*(__IO uint32_t*)0x400540B0U) |

◆ REG_TC3_FMR

| #define REG_TC3_FMR (*(__IO uint32_t*)0x400540D8U) |

◆ REG_TC3_IDR0

| #define REG_TC3_IDR0 (*(__O uint32_t*)0x40054028U) |

◆ REG_TC3_IDR1

| #define REG_TC3_IDR1 (*(__O uint32_t*)0x40054068U) |

◆ REG_TC3_IDR2

| #define REG_TC3_IDR2 (*(__O uint32_t*)0x400540A8U) |

◆ REG_TC3_IER0

| #define REG_TC3_IER0 (*(__O uint32_t*)0x40054024U) |

◆ REG_TC3_IER1

| #define REG_TC3_IER1 (*(__O uint32_t*)0x40054064U) |

◆ REG_TC3_IER2

| #define REG_TC3_IER2 (*(__O uint32_t*)0x400540A4U) |

◆ REG_TC3_IMR0

| #define REG_TC3_IMR0 (*(__I uint32_t*)0x4005402CU) |

◆ REG_TC3_IMR1

| #define REG_TC3_IMR1 (*(__I uint32_t*)0x4005406CU) |

◆ REG_TC3_IMR2

| #define REG_TC3_IMR2 (*(__I uint32_t*)0x400540ACU) |

◆ REG_TC3_QIDR

| #define REG_TC3_QIDR (*(__O uint32_t*)0x400540CCU) |

◆ REG_TC3_QIER

| #define REG_TC3_QIER (*(__O uint32_t*)0x400540C8U) |

◆ REG_TC3_QIMR

| #define REG_TC3_QIMR (*(__I uint32_t*)0x400540D0U) |

◆ REG_TC3_QISR

| #define REG_TC3_QISR (*(__I uint32_t*)0x400540D4U) |

◆ REG_TC3_RA0

| #define REG_TC3_RA0 (*(__IO uint32_t*)0x40054014U) |

◆ REG_TC3_RA1

| #define REG_TC3_RA1 (*(__IO uint32_t*)0x40054054U) |

◆ REG_TC3_RA2

| #define REG_TC3_RA2 (*(__IO uint32_t*)0x40054094U) |

◆ REG_TC3_RAB0

| #define REG_TC3_RAB0 (*(__I uint32_t*)0x4005400CU) |

◆ REG_TC3_RAB1

| #define REG_TC3_RAB1 (*(__I uint32_t*)0x4005404CU) |

◆ REG_TC3_RAB2

| #define REG_TC3_RAB2 (*(__I uint32_t*)0x4005408CU) |

◆ REG_TC3_RB0

| #define REG_TC3_RB0 (*(__IO uint32_t*)0x40054018U) |

◆ REG_TC3_RB1

| #define REG_TC3_RB1 (*(__IO uint32_t*)0x40054058U) |

◆ REG_TC3_RB2

| #define REG_TC3_RB2 (*(__IO uint32_t*)0x40054098U) |

◆ REG_TC3_RC0

| #define REG_TC3_RC0 (*(__IO uint32_t*)0x4005401CU) |

◆ REG_TC3_RC1

| #define REG_TC3_RC1 (*(__IO uint32_t*)0x4005405CU) |

◆ REG_TC3_RC2

| #define REG_TC3_RC2 (*(__IO uint32_t*)0x4005409CU) |

◆ REG_TC3_SMMR0

| #define REG_TC3_SMMR0 (*(__IO uint32_t*)0x40054008U) |

◆ REG_TC3_SMMR1

| #define REG_TC3_SMMR1 (*(__IO uint32_t*)0x40054048U) |

◆ REG_TC3_SMMR2

| #define REG_TC3_SMMR2 (*(__IO uint32_t*)0x40054088U) |

◆ REG_TC3_SR0

| #define REG_TC3_SR0 (*(__I uint32_t*)0x40054020U) |

◆ REG_TC3_SR1

| #define REG_TC3_SR1 (*(__I uint32_t*)0x40054060U) |

◆ REG_TC3_SR2

| #define REG_TC3_SR2 (*(__I uint32_t*)0x400540A0U) |

◆ REG_TC3_VER

| #define REG_TC3_VER (*(__I uint32_t*)0x400540FCU) |