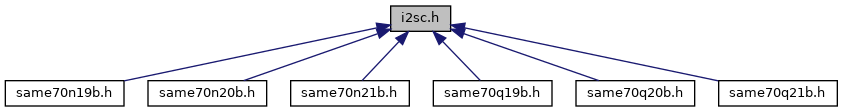

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | I2sc |

| I2sc hardware registers. More... | |

Macros | |

| #define | I2SC_CR_CKDIS (0x1u << 3) |

| (I2SC_CR) Clocks Disable More... | |

| #define | I2SC_CR_CKEN (0x1u << 2) |

| (I2SC_CR) Clocks Enable More... | |

| #define | I2SC_CR_RXDIS (0x1u << 1) |

| (I2SC_CR) Receiver Disable More... | |

| #define | I2SC_CR_RXEN (0x1u << 0) |

| (I2SC_CR) Receiver Enable More... | |

| #define | I2SC_CR_SWRST (0x1u << 7) |

| (I2SC_CR) Software Reset More... | |

| #define | I2SC_CR_TXDIS (0x1u << 5) |

| (I2SC_CR) Transmitter Disable More... | |

| #define | I2SC_CR_TXEN (0x1u << 4) |

| (I2SC_CR) Transmitter Enable More... | |

| #define | I2SC_IDR_RXOR (0x1u << 2) |

| (I2SC_IDR) Receiver Overrun Interrupt Disable More... | |

| #define | I2SC_IDR_RXRDY (0x1u << 1) |

| (I2SC_IDR) Receiver Ready Interrupt Disable More... | |

| #define | I2SC_IDR_TXRDY (0x1u << 5) |

| (I2SC_IDR) Transmit Ready Interrupt Disable More... | |

| #define | I2SC_IDR_TXUR (0x1u << 6) |

| (I2SC_IDR) Transmit Underflow Interrupt Disable More... | |

| #define | I2SC_IER_RXOR (0x1u << 2) |

| (I2SC_IER) Receiver Overrun Interrupt Enable More... | |

| #define | I2SC_IER_RXRDY (0x1u << 1) |

| (I2SC_IER) Receiver Ready Interrupt Enable More... | |

| #define | I2SC_IER_TXRDY (0x1u << 5) |

| (I2SC_IER) Transmit Ready Interrupt Enable More... | |

| #define | I2SC_IER_TXUR (0x1u << 6) |

| (I2SC_IER) Transmit Underflow Interrupt Enable More... | |

| #define | I2SC_IMR_RXOR (0x1u << 2) |

| (I2SC_IMR) Receiver Overrun Interrupt Disable More... | |

| #define | I2SC_IMR_RXRDY (0x1u << 1) |

| (I2SC_IMR) Receiver Ready Interrupt Disable More... | |

| #define | I2SC_IMR_TXRDY (0x1u << 5) |

| (I2SC_IMR) Transmit Ready Interrupt Disable More... | |

| #define | I2SC_IMR_TXUR (0x1u << 6) |

| (I2SC_IMR) Transmit Underflow Interrupt Disable More... | |

| #define | I2SC_MR_DATALENGTH(value) ((I2SC_MR_DATALENGTH_Msk & ((value) << I2SC_MR_DATALENGTH_Pos))) |

| #define | I2SC_MR_DATALENGTH_16_BITS (0x4u << 2) |

| (I2SC_MR) Data length is set to 16 bits More... | |

| #define | I2SC_MR_DATALENGTH_16_BITS_COMPACT (0x5u << 2) |

| (I2SC_MR) Data length is set to 16-bit compact stereo. Left sample in bits 15:0 and right sample in bits 31:16 of same word. More... | |

| #define | I2SC_MR_DATALENGTH_18_BITS (0x3u << 2) |

| (I2SC_MR) Data length is set to 18 bits More... | |

| #define | I2SC_MR_DATALENGTH_20_BITS (0x2u << 2) |

| (I2SC_MR) Data length is set to 20 bits More... | |

| #define | I2SC_MR_DATALENGTH_24_BITS (0x1u << 2) |

| (I2SC_MR) Data length is set to 24 bits More... | |

| #define | I2SC_MR_DATALENGTH_32_BITS (0x0u << 2) |

| (I2SC_MR) Data length is set to 32 bits More... | |

| #define | I2SC_MR_DATALENGTH_8_BITS (0x6u << 2) |

| (I2SC_MR) Data length is set to 8 bits More... | |

| #define | I2SC_MR_DATALENGTH_8_BITS_COMPACT (0x7u << 2) |

| (I2SC_MR) Data length is set to 8-bit compact stereo. Left sample in bits 7:0 and right sample in bits 15:8 of the same word. More... | |

| #define | I2SC_MR_DATALENGTH_Msk (0x7u << I2SC_MR_DATALENGTH_Pos) |

| (I2SC_MR) Data Word Length More... | |

| #define | I2SC_MR_DATALENGTH_Pos 2 |

| #define | I2SC_MR_FORMAT(value) ((I2SC_MR_FORMAT_Msk & ((value) << I2SC_MR_FORMAT_Pos))) |

| #define | I2SC_MR_FORMAT_I2S (0x0u << 6) |

| (I2SC_MR) I2S format, stereo with I2SWS low for left channel, and MSB of sample starting one I2SCK period after I2SWS edge More... | |

| #define | I2SC_MR_FORMAT_LJ (0x1u << 6) |

| (I2SC_MR) Left-justified format, stereo with I2SWS high for left channel, and MSB of sample starting on I2SWS edge More... | |

| #define | I2SC_MR_FORMAT_Msk (0x3u << I2SC_MR_FORMAT_Pos) |

| (I2SC_MR) Data Format More... | |

| #define | I2SC_MR_FORMAT_Pos 6 |

| #define | I2SC_MR_IMCKDIV(value) ((I2SC_MR_IMCKDIV_Msk & ((value) << I2SC_MR_IMCKDIV_Pos))) |

| #define | I2SC_MR_IMCKDIV_Msk (0x3fu << I2SC_MR_IMCKDIV_Pos) |

| (I2SC_MR) Selected Clock to I2SC Master Clock Ratio More... | |

| #define | I2SC_MR_IMCKDIV_Pos 16 |

| #define | I2SC_MR_IMCKFS(value) ((I2SC_MR_IMCKFS_Msk & ((value) << I2SC_MR_IMCKFS_Pos))) |

| #define | I2SC_MR_IMCKFS_M2SF1024 (0x1Fu << 24) |

| (I2SC_MR) Sample frequency ratio set to 1024 More... | |

| #define | I2SC_MR_IMCKFS_M2SF128 (0x3u << 24) |

| (I2SC_MR) Sample frequency ratio set to 128 More... | |

| #define | I2SC_MR_IMCKFS_M2SF1536 (0x2Fu << 24) |

| (I2SC_MR) Sample frequency ratio set to 1536 More... | |

| #define | I2SC_MR_IMCKFS_M2SF192 (0x5u << 24) |

| (I2SC_MR) Sample frequency ratio set to 192 More... | |

| #define | I2SC_MR_IMCKFS_M2SF2048 (0x3Fu << 24) |

| (I2SC_MR) Sample frequency ratio set to 2048 More... | |

| #define | I2SC_MR_IMCKFS_M2SF256 (0x7u << 24) |

| (I2SC_MR) Sample frequency ratio set to 256 More... | |

| #define | I2SC_MR_IMCKFS_M2SF32 (0x0u << 24) |

| (I2SC_MR) Sample frequency ratio set to 32 More... | |

| #define | I2SC_MR_IMCKFS_M2SF384 (0xBu << 24) |

| (I2SC_MR) Sample frequency ratio set to 384 More... | |

| #define | I2SC_MR_IMCKFS_M2SF512 (0xFu << 24) |

| (I2SC_MR) Sample frequency ratio set to 512 More... | |

| #define | I2SC_MR_IMCKFS_M2SF64 (0x1u << 24) |

| (I2SC_MR) Sample frequency ratio set to 64 More... | |

| #define | I2SC_MR_IMCKFS_M2SF768 (0x17u << 24) |

| (I2SC_MR) Sample frequency ratio set to 768 More... | |

| #define | I2SC_MR_IMCKFS_M2SF96 (0x2u << 24) |

| (I2SC_MR) Sample frequency ratio set to 96 More... | |

| #define | I2SC_MR_IMCKFS_Msk (0x3fu << I2SC_MR_IMCKFS_Pos) |

| (I2SC_MR) Master Clock to fs Ratio More... | |

| #define | I2SC_MR_IMCKFS_Pos 24 |

| #define | I2SC_MR_IMCKMODE (0x1u << 30) |

| (I2SC_MR) Master Clock Mode More... | |

| #define | I2SC_MR_IWS (0x1u << 31) |

| (I2SC_MR) I2SWS Slot Width More... | |

| #define | I2SC_MR_MODE (0x1u << 0) |

| (I2SC_MR) Inter-IC Sound Controller Mode More... | |

| #define | I2SC_MR_MODE_MASTER (0x1u << 0) |

| (I2SC_MR) Bit clock and word select/frame synchronization generated by I2SC from MCK and output to I2SCK and I2SWS pins. MCK is output as master clock on I2SMCK if I2SC_MR.IMCKMODE is set. More... | |

| #define | I2SC_MR_MODE_SLAVE (0x0u << 0) |

| (I2SC_MR) I2SCK and i2SWS pin inputs used as bit clock and word select/frame synchronization. More... | |

| #define | I2SC_MR_RXDMA (0x1u << 9) |

| (I2SC_MR) Single or Multiple DMA Controller Channels for Receiver More... | |

| #define | I2SC_MR_RXLOOP (0x1u << 10) |

| (I2SC_MR) Loop-back Test Mode More... | |

| #define | I2SC_MR_RXMONO (0x1u << 8) |

| (I2SC_MR) Receive Mono More... | |

| #define | I2SC_MR_TXDMA (0x1u << 13) |

| (I2SC_MR) Single or Multiple DMA Controller Channels for Transmitter More... | |

| #define | I2SC_MR_TXMONO (0x1u << 12) |

| (I2SC_MR) Transmit Mono More... | |

| #define | I2SC_MR_TXSAME (0x1u << 14) |

| (I2SC_MR) Transmit Data when Underrun More... | |

| #define | I2SC_RHR_RHR_Msk (0xffffffffu << I2SC_RHR_RHR_Pos) |

| (I2SC_RHR) Receiver Holding Register More... | |

| #define | I2SC_RHR_RHR_Pos 0 |

| #define | I2SC_SCR_RXOR (0x1u << 2) |

| (I2SC_SCR) Receive Overrun Status Clear More... | |

| #define | I2SC_SCR_RXORCH(value) ((I2SC_SCR_RXORCH_Msk & ((value) << I2SC_SCR_RXORCH_Pos))) |

| #define | I2SC_SCR_RXORCH_Msk (0x3u << I2SC_SCR_RXORCH_Pos) |

| (I2SC_SCR) Receive Overrun Per Channel Status Clear More... | |

| #define | I2SC_SCR_RXORCH_Pos 8 |

| #define | I2SC_SCR_TXUR (0x1u << 6) |

| (I2SC_SCR) Transmit Underrun Status Clear More... | |

| #define | I2SC_SCR_TXURCH(value) ((I2SC_SCR_TXURCH_Msk & ((value) << I2SC_SCR_TXURCH_Pos))) |

| #define | I2SC_SCR_TXURCH_Msk (0x3u << I2SC_SCR_TXURCH_Pos) |

| (I2SC_SCR) Transmit Underrun Per Channel Status Clear More... | |

| #define | I2SC_SCR_TXURCH_Pos 20 |

| #define | I2SC_SR_RXEN (0x1u << 0) |

| (I2SC_SR) Receiver Enabled More... | |

| #define | I2SC_SR_RXOR (0x1u << 2) |

| (I2SC_SR) Receive Overrun More... | |

| #define | I2SC_SR_RXORCH_Msk (0x3u << I2SC_SR_RXORCH_Pos) |

| (I2SC_SR) Receive Overrun Channel More... | |

| #define | I2SC_SR_RXORCH_Pos 8 |

| #define | I2SC_SR_RXRDY (0x1u << 1) |

| (I2SC_SR) Receive Ready More... | |

| #define | I2SC_SR_TXEN (0x1u << 4) |

| (I2SC_SR) Transmitter Enabled More... | |

| #define | I2SC_SR_TXRDY (0x1u << 5) |

| (I2SC_SR) Transmit Ready More... | |

| #define | I2SC_SR_TXUR (0x1u << 6) |

| (I2SC_SR) Transmit Underrun More... | |

| #define | I2SC_SR_TXURCH_Msk (0x3u << I2SC_SR_TXURCH_Pos) |

| (I2SC_SR) Transmit Underrun Channel More... | |

| #define | I2SC_SR_TXURCH_Pos 20 |

| #define | I2SC_SSR_RXOR (0x1u << 2) |

| (I2SC_SSR) Receive Overrun Status Set More... | |

| #define | I2SC_SSR_RXORCH(value) ((I2SC_SSR_RXORCH_Msk & ((value) << I2SC_SSR_RXORCH_Pos))) |

| #define | I2SC_SSR_RXORCH_Msk (0x3u << I2SC_SSR_RXORCH_Pos) |

| (I2SC_SSR) Receive Overrun Per Channel Status Set More... | |

| #define | I2SC_SSR_RXORCH_Pos 8 |

| #define | I2SC_SSR_TXUR (0x1u << 6) |

| (I2SC_SSR) Transmit Underrun Status Set More... | |

| #define | I2SC_SSR_TXURCH(value) ((I2SC_SSR_TXURCH_Msk & ((value) << I2SC_SSR_TXURCH_Pos))) |

| #define | I2SC_SSR_TXURCH_Msk (0x3u << I2SC_SSR_TXURCH_Pos) |

| (I2SC_SSR) Transmit Underrun Per Channel Status Set More... | |

| #define | I2SC_SSR_TXURCH_Pos 20 |

| #define | I2SC_THR_THR(value) ((I2SC_THR_THR_Msk & ((value) << I2SC_THR_THR_Pos))) |

| #define | I2SC_THR_THR_Msk (0xffffffffu << I2SC_THR_THR_Pos) |

| (I2SC_THR) Transmitter Holding Register More... | |

| #define | I2SC_THR_THR_Pos 0 |

| #define | I2SC_VERSION_MFN_Msk (0x7u << I2SC_VERSION_MFN_Pos) |

| (I2SC_VERSION) Metal Fix Number More... | |

| #define | I2SC_VERSION_MFN_Pos 16 |

| #define | I2SC_VERSION_VERSION_Msk (0xfffu << I2SC_VERSION_VERSION_Pos) |

| (I2SC_VERSION) Version of the Hardware Module More... | |

| #define | I2SC_VERSION_VERSION_Pos 0 |

Detailed Description

Copyright (c) 2017-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file i2sc.h.