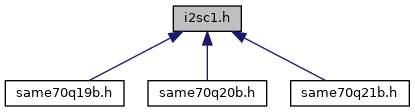

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | REG_I2SC1_CR (*(__O uint32_t*)0x40090000U) |

| (I2SC1) Control Register More... | |

| #define | REG_I2SC1_IDR (*(__O uint32_t*)0x40090018U) |

| (I2SC1) Interrupt Disable Register More... | |

| #define | REG_I2SC1_IER (*(__O uint32_t*)0x40090014U) |

| (I2SC1) Interrupt Enable Register More... | |

| #define | REG_I2SC1_IMR (*(__I uint32_t*)0x4009001CU) |

| (I2SC1) Interrupt Mask Register More... | |

| #define | REG_I2SC1_MR (*(__IO uint32_t*)0x40090004U) |

| (I2SC1) Mode Register More... | |

| #define | REG_I2SC1_RHR (*(__I uint32_t*)0x40090020U) |

| (I2SC1) Receiver Holding Register More... | |

| #define | REG_I2SC1_SCR (*(__O uint32_t*)0x4009000CU) |

| (I2SC1) Status Clear Register More... | |

| #define | REG_I2SC1_SR (*(__I uint32_t*)0x40090008U) |

| (I2SC1) Status Register More... | |

| #define | REG_I2SC1_SSR (*(__O uint32_t*)0x40090010U) |

| (I2SC1) Status Set Register More... | |

| #define | REG_I2SC1_THR (*(__O uint32_t*)0x40090024U) |

| (I2SC1) Transmitter Holding Register More... | |

| #define | REG_I2SC1_VERSION (*(__I uint32_t*)0x40090028U) |

| (I2SC1) Version Register More... | |

Detailed Description

Copyright (c) 2017-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file i2sc1.h.

Macro Definition Documentation

◆ REG_I2SC1_CR

| #define REG_I2SC1_CR (*(__O uint32_t*)0x40090000U) |

◆ REG_I2SC1_IDR

| #define REG_I2SC1_IDR (*(__O uint32_t*)0x40090018U) |

◆ REG_I2SC1_IER

| #define REG_I2SC1_IER (*(__O uint32_t*)0x40090014U) |

◆ REG_I2SC1_IMR

| #define REG_I2SC1_IMR (*(__I uint32_t*)0x4009001CU) |

◆ REG_I2SC1_MR

| #define REG_I2SC1_MR (*(__IO uint32_t*)0x40090004U) |

◆ REG_I2SC1_RHR

| #define REG_I2SC1_RHR (*(__I uint32_t*)0x40090020U) |

◆ REG_I2SC1_SCR

| #define REG_I2SC1_SCR (*(__O uint32_t*)0x4009000CU) |

◆ REG_I2SC1_SR

| #define REG_I2SC1_SR (*(__I uint32_t*)0x40090008U) |

◆ REG_I2SC1_SSR

| #define REG_I2SC1_SSR (*(__O uint32_t*)0x40090010U) |

◆ REG_I2SC1_THR

| #define REG_I2SC1_THR (*(__O uint32_t*)0x40090024U) |