|

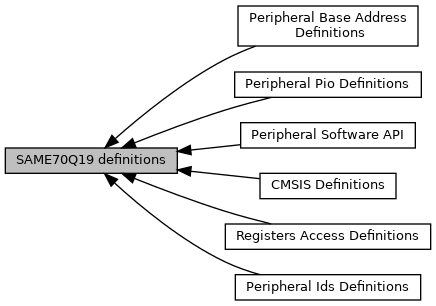

Modules | |

| CMSIS Definitions | |

| Peripheral Software API | |

| Registers Access Definitions | |

| Peripheral Ids Definitions | |

| Peripheral Base Address Definitions | |

| Peripheral Pio Definitions | |

Macros | |

| #define | AXIMX_ADDR (0xA0000000u) |

| #define | CHIP_CIDR (0xA10D0A00UL) |

| #define | CHIP_EXID (0x00000002UL) |

| #define | CHIP_FREQ_CPU_MAX (300000000UL) |

| #define | CHIP_FREQ_FWS_0 (23000000UL) |

| Maximum operating frequency when FWS is 0. More... | |

| #define | CHIP_FREQ_FWS_1 (46000000UL) |

| Maximum operating frequency when FWS is 1. More... | |

| #define | CHIP_FREQ_FWS_2 (69000000UL) |

| Maximum operating frequency when FWS is 2. More... | |

| #define | CHIP_FREQ_FWS_3 (92000000UL) |

| Maximum operating frequency when FWS is 3. More... | |

| #define | CHIP_FREQ_FWS_4 (115000000UL) |

| Maximum operating frequency when FWS is 4. More... | |

| #define | CHIP_FREQ_FWS_5 (138000000UL) |

| Maximum operating frequency when FWS is 5. More... | |

| #define | CHIP_FREQ_FWS_6 (150000000UL) |

| Maximum operating frequency when FWS is 6. More... | |

| #define | CHIP_FREQ_MAINCK_RC_12MHZ (12000000UL) |

| #define | CHIP_FREQ_MAINCK_RC_4MHZ (4000000UL) |

| #define | CHIP_FREQ_MAINCK_RC_8MHZ (8000000UL) |

| #define | CHIP_FREQ_SLCK_RC (32000UL) |

| #define | CHIP_FREQ_SLCK_RC_MAX (44000UL) |

| #define | CHIP_FREQ_SLCK_RC_MIN (20000UL) |

| #define | CHIP_FREQ_XTAL_12M (12000000UL) |

| #define | CHIP_FREQ_XTAL_32K (32768UL) |

| #define | CHIP_JTAGID (0x05B3D03FUL) |

| #define | DTCM_ADDR (0x20000000u) |

| #define | EBI_CS0_ADDR (0x60000000u) |

| #define | EBI_CS1_ADDR (0x61000000u) |

| #define | EBI_CS2_ADDR (0x62000000u) |

| #define | EBI_CS3_ADDR (0x63000000u) |

| #define | IFLASH_ADDR (0x00400000u) |

| #define | IFLASH_LOCK_REGION_SIZE (8192u) |

| #define | IFLASH_NB_OF_LOCK_BITS (32u) |

| #define | IFLASH_NB_OF_PAGES (1024u) |

| #define | IFLASH_PAGE_SIZE (512u) |

| #define | IFLASH_SIZE (0x80000u) |

| #define | IRAM_ADDR (0x20400000u) |

| #define | IRAM_SIZE (0x40000u) |

| #define | IROM_ADDR (0x00800000u) |

| #define | ITCM_ADDR (0x00000000u) |

| #define | QSPIMEM_ADDR (0x80000000u) |

| #define | SDRAM_CS_ADDR (0x70000000u) |

Detailed Description

This file defines all structures and symbols for SAME70Q19:

- registers and bitfields

- peripheral base address

- peripheral ID

- PIO definitions

Macro Definition Documentation

◆ AXIMX_ADDR

| #define AXIMX_ADDR (0xA0000000u) |

AXI Bus Matrix base address

Definition at line 663 of file same70q19.h.

◆ CHIP_CIDR

| #define CHIP_CIDR (0xA10D0A00UL) |

Definition at line 680 of file same70q19.h.

◆ CHIP_EXID

| #define CHIP_EXID (0x00000002UL) |

Definition at line 681 of file same70q19.h.

◆ CHIP_FREQ_CPU_MAX

| #define CHIP_FREQ_CPU_MAX (300000000UL) |

Definition at line 696 of file same70q19.h.

◆ CHIP_FREQ_FWS_0

| #define CHIP_FREQ_FWS_0 (23000000UL) |

Maximum operating frequency when FWS is 0.

Definition at line 701 of file same70q19.h.

◆ CHIP_FREQ_FWS_1

| #define CHIP_FREQ_FWS_1 (46000000UL) |

Maximum operating frequency when FWS is 1.

Definition at line 702 of file same70q19.h.

◆ CHIP_FREQ_FWS_2

| #define CHIP_FREQ_FWS_2 (69000000UL) |

Maximum operating frequency when FWS is 2.

Definition at line 703 of file same70q19.h.

◆ CHIP_FREQ_FWS_3

| #define CHIP_FREQ_FWS_3 (92000000UL) |

Maximum operating frequency when FWS is 3.

Definition at line 704 of file same70q19.h.

◆ CHIP_FREQ_FWS_4

| #define CHIP_FREQ_FWS_4 (115000000UL) |

Maximum operating frequency when FWS is 4.

Definition at line 705 of file same70q19.h.

◆ CHIP_FREQ_FWS_5

| #define CHIP_FREQ_FWS_5 (138000000UL) |

Maximum operating frequency when FWS is 5.

Definition at line 706 of file same70q19.h.

◆ CHIP_FREQ_FWS_6

| #define CHIP_FREQ_FWS_6 (150000000UL) |

Maximum operating frequency when FWS is 6.

Definition at line 707 of file same70q19.h.

◆ CHIP_FREQ_MAINCK_RC_12MHZ

| #define CHIP_FREQ_MAINCK_RC_12MHZ (12000000UL) |

Definition at line 695 of file same70q19.h.

◆ CHIP_FREQ_MAINCK_RC_4MHZ

| #define CHIP_FREQ_MAINCK_RC_4MHZ (4000000UL) |

Definition at line 693 of file same70q19.h.

◆ CHIP_FREQ_MAINCK_RC_8MHZ

| #define CHIP_FREQ_MAINCK_RC_8MHZ (8000000UL) |

Definition at line 694 of file same70q19.h.

◆ CHIP_FREQ_SLCK_RC

| #define CHIP_FREQ_SLCK_RC (32000UL) |

Definition at line 691 of file same70q19.h.

◆ CHIP_FREQ_SLCK_RC_MAX

| #define CHIP_FREQ_SLCK_RC_MAX (44000UL) |

Definition at line 692 of file same70q19.h.

◆ CHIP_FREQ_SLCK_RC_MIN

| #define CHIP_FREQ_SLCK_RC_MIN (20000UL) |

Definition at line 690 of file same70q19.h.

◆ CHIP_FREQ_XTAL_12M

| #define CHIP_FREQ_XTAL_12M (12000000UL) |

Definition at line 698 of file same70q19.h.

◆ CHIP_FREQ_XTAL_32K

| #define CHIP_FREQ_XTAL_32K (32768UL) |

Definition at line 697 of file same70q19.h.

◆ CHIP_JTAGID

| #define CHIP_JTAGID (0x05B3D03FUL) |

Definition at line 679 of file same70q19.h.

◆ DTCM_ADDR

| #define DTCM_ADDR (0x20000000u) |

Data Tightly Coupled Memory base address

Definition at line 667 of file same70q19.h.

◆ EBI_CS0_ADDR

| #define EBI_CS0_ADDR (0x60000000u) |

EBI Chip Select 0 base address

Definition at line 669 of file same70q19.h.

◆ EBI_CS1_ADDR

| #define EBI_CS1_ADDR (0x61000000u) |

EBI Chip Select 1 base address

Definition at line 670 of file same70q19.h.

◆ EBI_CS2_ADDR

| #define EBI_CS2_ADDR (0x62000000u) |

EBI Chip Select 2 base address

Definition at line 671 of file same70q19.h.

◆ EBI_CS3_ADDR

| #define EBI_CS3_ADDR (0x63000000u) |

EBI Chip Select 3 base address

Definition at line 672 of file same70q19.h.

◆ IFLASH_ADDR

| #define IFLASH_ADDR (0x00400000u) |

Internal Flash base address

Definition at line 665 of file same70q19.h.

◆ IFLASH_LOCK_REGION_SIZE

| #define IFLASH_LOCK_REGION_SIZE (8192u) |

Definition at line 657 of file same70q19.h.

◆ IFLASH_NB_OF_LOCK_BITS

| #define IFLASH_NB_OF_LOCK_BITS (32u) |

Definition at line 659 of file same70q19.h.

◆ IFLASH_NB_OF_PAGES

| #define IFLASH_NB_OF_PAGES (1024u) |

Definition at line 658 of file same70q19.h.

◆ IFLASH_PAGE_SIZE

| #define IFLASH_PAGE_SIZE (512u) |

Definition at line 656 of file same70q19.h.

◆ IFLASH_SIZE

| #define IFLASH_SIZE (0x80000u) |

Definition at line 655 of file same70q19.h.

◆ IRAM_ADDR

| #define IRAM_ADDR (0x20400000u) |

Internal RAM base address

Definition at line 668 of file same70q19.h.

◆ IRAM_SIZE

| #define IRAM_SIZE (0x40000u) |

Definition at line 660 of file same70q19.h.

◆ IROM_ADDR

| #define IROM_ADDR (0x00800000u) |

Internal ROM base address

Definition at line 666 of file same70q19.h.

◆ ITCM_ADDR

| #define ITCM_ADDR (0x00000000u) |

Instruction Tightly Coupled Memory base address

Definition at line 664 of file same70q19.h.

◆ QSPIMEM_ADDR

| #define QSPIMEM_ADDR (0x80000000u) |

QSPI Memory base address

Definition at line 662 of file same70q19.h.

◆ SDRAM_CS_ADDR

| #define SDRAM_CS_ADDR (0x70000000u) |

SDRAM Chip Select base address

Definition at line 673 of file same70q19.h.