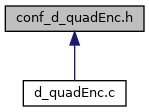

Go to the source code of this file.

Macros | |

| #define | ID_QE0_POS ID_TC6 |

| #define | ID_QE1_POS ID_TC9 |

| #define | ID_TCCAP0_SPD ID_TC5 |

| #define | ID_TCCAP1_SPD ID_TC0 |

| #define | PIN_QE0_POS_PHA (PIO_PC5_IDX) |

| #define | PIN_QE0_POS_PHA_MUX (IOPORT_MODE_MUX_B) |

| #define | PIN_QE0_POS_PHB (PIO_PC6_IDX) |

| #define | PIN_QE0_POS_PHB_MUX (IOPORT_MODE_MUX_B) |

| #define | PIN_QE1_POS_PHA (PIO_PE0_IDX) |

| #define | PIN_QE1_POS_PHA_MUX (IOPORT_MODE_MUX_B) |

| #define | PIN_QE1_POS_PHB (PIO_PE1_IDX) |

| #define | PIN_QE1_POS_PHB_MUX (IOPORT_MODE_MUX_B) |

| #define | PIN_TCCAP0_SPD (PIO_PC29_IDX) |

| #define | PIN_TCCAP0_SPD_MUX (IOPORT_MODE_MUX_B) |

| #define | PIN_TCCAP1_SPD (PIO_PA15_IDX) |

| #define | PIN_TCCAP1_SPD_MUX (IOPORT_MODE_MUX_B) |

| #define | QE0_POS TC2 |

| #define | QE1_POS TC3 |

| #define | TCCAP0_SPD TC1 |

| #define | TCCAP0_SPD_CHANNEL 2 |

| #define | TCCAP0_SPD_Handler TC5_Handler |

| #define | TCCAP0_SPD_IRQn TC5_IRQn |

| #define | TCCAP1_SPD TC0 |

| #define | TCCAP1_SPD_CHANNEL 0 |

| #define | TCCAP1_SPD_Handler TC0_Handler |

| #define | TCCAP1_SPD_IRQn TC0_IRQn |

Macro Definition Documentation

◆ ID_QE0_POS

| #define ID_QE0_POS ID_TC6 |

Definition at line 24 of file conf_d_quadEnc.h.

◆ ID_QE1_POS

| #define ID_QE1_POS ID_TC9 |

Definition at line 62 of file conf_d_quadEnc.h.

◆ ID_TCCAP0_SPD

| #define ID_TCCAP0_SPD ID_TC5 |

Definition at line 37 of file conf_d_quadEnc.h.

◆ ID_TCCAP1_SPD

| #define ID_TCCAP1_SPD ID_TC0 |

Definition at line 74 of file conf_d_quadEnc.h.

◆ PIN_QE0_POS_PHA

| #define PIN_QE0_POS_PHA (PIO_PC5_IDX) |

Definition at line 26 of file conf_d_quadEnc.h.

◆ PIN_QE0_POS_PHA_MUX

| #define PIN_QE0_POS_PHA_MUX (IOPORT_MODE_MUX_B) |

Definition at line 27 of file conf_d_quadEnc.h.

◆ PIN_QE0_POS_PHB

| #define PIN_QE0_POS_PHB (PIO_PC6_IDX) |

Definition at line 29 of file conf_d_quadEnc.h.

◆ PIN_QE0_POS_PHB_MUX

| #define PIN_QE0_POS_PHB_MUX (IOPORT_MODE_MUX_B) |

Definition at line 30 of file conf_d_quadEnc.h.

◆ PIN_QE1_POS_PHA

| #define PIN_QE1_POS_PHA (PIO_PE0_IDX) |

Definition at line 64 of file conf_d_quadEnc.h.

◆ PIN_QE1_POS_PHA_MUX

| #define PIN_QE1_POS_PHA_MUX (IOPORT_MODE_MUX_B) |

Definition at line 65 of file conf_d_quadEnc.h.

◆ PIN_QE1_POS_PHB

| #define PIN_QE1_POS_PHB (PIO_PE1_IDX) |

Definition at line 67 of file conf_d_quadEnc.h.

◆ PIN_QE1_POS_PHB_MUX

| #define PIN_QE1_POS_PHB_MUX (IOPORT_MODE_MUX_B) |

Definition at line 68 of file conf_d_quadEnc.h.

◆ PIN_TCCAP0_SPD

| #define PIN_TCCAP0_SPD (PIO_PC29_IDX) |

Definition at line 39 of file conf_d_quadEnc.h.

◆ PIN_TCCAP0_SPD_MUX

| #define PIN_TCCAP0_SPD_MUX (IOPORT_MODE_MUX_B) |

Definition at line 40 of file conf_d_quadEnc.h.

◆ PIN_TCCAP1_SPD

| #define PIN_TCCAP1_SPD (PIO_PA15_IDX) |

Definition at line 76 of file conf_d_quadEnc.h.

◆ PIN_TCCAP1_SPD_MUX

| #define PIN_TCCAP1_SPD_MUX (IOPORT_MODE_MUX_B) |

Definition at line 77 of file conf_d_quadEnc.h.

◆ QE0_POS

| #define QE0_POS TC2 |

Definition at line 23 of file conf_d_quadEnc.h.

◆ QE1_POS

| #define QE1_POS TC3 |

Definition at line 61 of file conf_d_quadEnc.h.

◆ TCCAP0_SPD

| #define TCCAP0_SPD TC1 |

Definition at line 35 of file conf_d_quadEnc.h.

◆ TCCAP0_SPD_CHANNEL

| #define TCCAP0_SPD_CHANNEL 2 |

Definition at line 36 of file conf_d_quadEnc.h.

◆ TCCAP0_SPD_Handler

| #define TCCAP0_SPD_Handler TC5_Handler |

Definition at line 42 of file conf_d_quadEnc.h.

◆ TCCAP0_SPD_IRQn

| #define TCCAP0_SPD_IRQn TC5_IRQn |

Definition at line 43 of file conf_d_quadEnc.h.

◆ TCCAP1_SPD

| #define TCCAP1_SPD TC0 |

Definition at line 72 of file conf_d_quadEnc.h.

◆ TCCAP1_SPD_CHANNEL

| #define TCCAP1_SPD_CHANNEL 0 |

Definition at line 73 of file conf_d_quadEnc.h.

◆ TCCAP1_SPD_Handler

| #define TCCAP1_SPD_Handler TC0_Handler |

Definition at line 79 of file conf_d_quadEnc.h.

◆ TCCAP1_SPD_IRQn

| #define TCCAP1_SPD_IRQn TC0_IRQn |

Definition at line 80 of file conf_d_quadEnc.h.