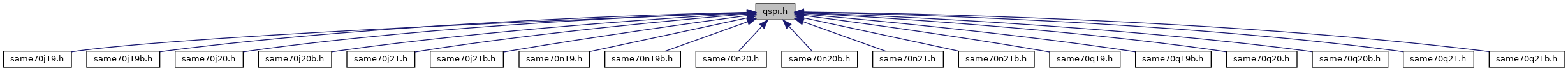

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Qspi |

| Qspi hardware registers. More... | |

Macros | |

| #define | QSPI_CR_LASTXFER (0x1u << 24) |

| (QSPI_CR) Last Transfer More... | |

| #define | QSPI_CR_QSPIDIS (0x1u << 1) |

| (QSPI_CR) QSPI Disable More... | |

| #define | QSPI_CR_QSPIEN (0x1u << 0) |

| (QSPI_CR) QSPI Enable More... | |

| #define | QSPI_CR_SWRST (0x1u << 7) |

| (QSPI_CR) QSPI Software Reset More... | |

| #define | QSPI_IAR_ADDR(value) ((QSPI_IAR_ADDR_Msk & ((value) << QSPI_IAR_ADDR_Pos))) |

| #define | QSPI_IAR_ADDR_Msk (0xffffffffu << QSPI_IAR_ADDR_Pos) |

| (QSPI_IAR) Address More... | |

| #define | QSPI_IAR_ADDR_Pos 0 |

| #define | QSPI_ICR_INST(value) ((QSPI_ICR_INST_Msk & ((value) << QSPI_ICR_INST_Pos))) |

| #define | QSPI_ICR_INST_Msk (0xffu << QSPI_ICR_INST_Pos) |

| (QSPI_ICR) Instruction Code More... | |

| #define | QSPI_ICR_INST_Pos 0 |

| #define | QSPI_ICR_OPT(value) ((QSPI_ICR_OPT_Msk & ((value) << QSPI_ICR_OPT_Pos))) |

| #define | QSPI_ICR_OPT_Msk (0xffu << QSPI_ICR_OPT_Pos) |

| (QSPI_ICR) Option Code More... | |

| #define | QSPI_ICR_OPT_Pos 16 |

| #define | QSPI_IDR_CSR (0x1u << 8) |

| (QSPI_IDR) Chip Select Rise Interrupt Disable More... | |

| #define | QSPI_IDR_CSS (0x1u << 9) |

| (QSPI_IDR) Chip Select Status Interrupt Disable More... | |

| #define | QSPI_IDR_INSTRE (0x1u << 10) |

| (QSPI_IDR) Instruction End Interrupt Disable More... | |

| #define | QSPI_IDR_OVRES (0x1u << 3) |

| (QSPI_IDR) Overrun Error Interrupt Disable More... | |

| #define | QSPI_IDR_RDRF (0x1u << 0) |

| (QSPI_IDR) Receive Data Register Full Interrupt Disable More... | |

| #define | QSPI_IDR_TDRE (0x1u << 1) |

| (QSPI_IDR) Transmit Data Register Empty Interrupt Disable More... | |

| #define | QSPI_IDR_TXEMPTY (0x1u << 2) |

| (QSPI_IDR) Transmission Registers Empty Disable More... | |

| #define | QSPI_IER_CSR (0x1u << 8) |

| (QSPI_IER) Chip Select Rise Interrupt Enable More... | |

| #define | QSPI_IER_CSS (0x1u << 9) |

| (QSPI_IER) Chip Select Status Interrupt Enable More... | |

| #define | QSPI_IER_INSTRE (0x1u << 10) |

| (QSPI_IER) Instruction End Interrupt Enable More... | |

| #define | QSPI_IER_OVRES (0x1u << 3) |

| (QSPI_IER) Overrun Error Interrupt Enable More... | |

| #define | QSPI_IER_RDRF (0x1u << 0) |

| (QSPI_IER) Receive Data Register Full Interrupt Enable More... | |

| #define | QSPI_IER_TDRE (0x1u << 1) |

| (QSPI_IER) Transmit Data Register Empty Interrupt Enable More... | |

| #define | QSPI_IER_TXEMPTY (0x1u << 2) |

| (QSPI_IER) Transmission Registers Empty Enable More... | |

| #define | QSPI_IFR_ADDREN (0x1u << 5) |

| (QSPI_IFR) Address Enable More... | |

| #define | QSPI_IFR_ADDRL (0x1u << 10) |

| (QSPI_IFR) Address Length More... | |

| #define | QSPI_IFR_ADDRL_24_BIT (0x0u << 10) |

| (QSPI_IFR) The address is 24 bits long. More... | |

| #define | QSPI_IFR_ADDRL_32_BIT (0x1u << 10) |

| (QSPI_IFR) The address is 32 bits long. More... | |

| #define | QSPI_IFR_CRM (0x1u << 14) |

| (QSPI_IFR) Continuous Read Mode More... | |

| #define | QSPI_IFR_CRM_DISABLED (0x0u << 14) |

| (QSPI_IFR) The Continuous Read mode is disabled. More... | |

| #define | QSPI_IFR_CRM_ENABLED (0x1u << 14) |

| (QSPI_IFR) The Continuous Read mode is enabled. More... | |

| #define | QSPI_IFR_DATAEN (0x1u << 7) |

| (QSPI_IFR) Data Enable More... | |

| #define | QSPI_IFR_INSTEN (0x1u << 4) |

| (QSPI_IFR) Instruction Enable More... | |

| #define | QSPI_IFR_NBDUM(value) ((QSPI_IFR_NBDUM_Msk & ((value) << QSPI_IFR_NBDUM_Pos))) |

| #define | QSPI_IFR_NBDUM_Msk (0x1fu << QSPI_IFR_NBDUM_Pos) |

| (QSPI_IFR) Number Of Dummy Cycles More... | |

| #define | QSPI_IFR_NBDUM_Pos 16 |

| #define | QSPI_IFR_OPTEN (0x1u << 6) |

| (QSPI_IFR) Option Enable More... | |

| #define | QSPI_IFR_OPTL(value) ((QSPI_IFR_OPTL_Msk & ((value) << QSPI_IFR_OPTL_Pos))) |

| #define | QSPI_IFR_OPTL_Msk (0x3u << QSPI_IFR_OPTL_Pos) |

| (QSPI_IFR) Option Code Length More... | |

| #define | QSPI_IFR_OPTL_OPTION_1BIT (0x0u << 8) |

| (QSPI_IFR) The option code is 1 bit long. More... | |

| #define | QSPI_IFR_OPTL_OPTION_2BIT (0x1u << 8) |

| (QSPI_IFR) The option code is 2 bits long. More... | |

| #define | QSPI_IFR_OPTL_OPTION_4BIT (0x2u << 8) |

| (QSPI_IFR) The option code is 4 bits long. More... | |

| #define | QSPI_IFR_OPTL_OPTION_8BIT (0x3u << 8) |

| (QSPI_IFR) The option code is 8 bits long. More... | |

| #define | QSPI_IFR_OPTL_Pos 8 |

| #define | QSPI_IFR_TFRTYP(value) ((QSPI_IFR_TFRTYP_Msk & ((value) << QSPI_IFR_TFRTYP_Pos))) |

| #define | QSPI_IFR_TFRTYP_Msk (0x3u << QSPI_IFR_TFRTYP_Pos) |

| (QSPI_IFR) Data Transfer Type More... | |

| #define | QSPI_IFR_TFRTYP_Pos 12 |

| #define | QSPI_IFR_TFRTYP_TRSFR_READ (0x0u << 12) |

| (QSPI_IFR) Read transfer from the serial memory.Scrambling is not performed.Read at random location (fetch) in the serial Flash memory is not possible. More... | |

| #define | QSPI_IFR_TFRTYP_TRSFR_READ_MEMORY (0x1u << 12) |

| (QSPI_IFR) Read data transfer from the serial memory.If enabled, scrambling is performed.Read at random location (fetch) in the serial Flash memory is possible. More... | |

| #define | QSPI_IFR_TFRTYP_TRSFR_WRITE (0x2u << 12) |

| (QSPI_IFR) Write transfer into the serial memory.Scrambling is not performed. More... | |

| #define | QSPI_IFR_TFRTYP_TRSFR_WRITE_MEMORY (0x3u << 12) |

| (QSPI_IFR) Write data transfer into the serial memory.If enabled, scrambling is performed. More... | |

| #define | QSPI_IFR_WIDTH(value) ((QSPI_IFR_WIDTH_Msk & ((value) << QSPI_IFR_WIDTH_Pos))) |

| #define | QSPI_IFR_WIDTH_DUAL_CMD (0x5u << 0) |

| (QSPI_IFR) Instruction: Dual SPI / Address-Option: Dual SPI / Data: Dual SPI More... | |

| #define | QSPI_IFR_WIDTH_DUAL_IO (0x3u << 0) |

| (QSPI_IFR) Instruction: Single-bit SPI / Address-Option: Dual SPI / Data: Dual SPI More... | |

| #define | QSPI_IFR_WIDTH_DUAL_OUTPUT (0x1u << 0) |

| (QSPI_IFR) Instruction: Single-bit SPI / Address-Option: Single-bit SPI / Data: Dual SPI More... | |

| #define | QSPI_IFR_WIDTH_Msk (0x7u << QSPI_IFR_WIDTH_Pos) |

| (QSPI_IFR) Width of Instruction Code, Address, Option Code and Data More... | |

| #define | QSPI_IFR_WIDTH_Pos 0 |

| #define | QSPI_IFR_WIDTH_QUAD_CMD (0x6u << 0) |

| (QSPI_IFR) Instruction: Quad SPI / Address-Option: Quad SPI / Data: Quad SPI More... | |

| #define | QSPI_IFR_WIDTH_QUAD_IO (0x4u << 0) |

| (QSPI_IFR) Instruction: Single-bit SPI / Address-Option: Quad SPI / Data: Quad SPI More... | |

| #define | QSPI_IFR_WIDTH_QUAD_OUTPUT (0x2u << 0) |

| (QSPI_IFR) Instruction: Single-bit SPI / Address-Option: Single-bit SPI / Data: Quad SPI More... | |

| #define | QSPI_IFR_WIDTH_SINGLE_BIT_SPI (0x0u << 0) |

| (QSPI_IFR) Instruction: Single-bit SPI / Address-Option: Single-bit SPI / Data: Single-bit SPI More... | |

| #define | QSPI_IMR_CSR (0x1u << 8) |

| (QSPI_IMR) Chip Select Rise Interrupt Mask More... | |

| #define | QSPI_IMR_CSS (0x1u << 9) |

| (QSPI_IMR) Chip Select Status Interrupt Mask More... | |

| #define | QSPI_IMR_INSTRE (0x1u << 10) |

| (QSPI_IMR) Instruction End Interrupt Mask More... | |

| #define | QSPI_IMR_OVRES (0x1u << 3) |

| (QSPI_IMR) Overrun Error Interrupt Mask More... | |

| #define | QSPI_IMR_RDRF (0x1u << 0) |

| (QSPI_IMR) Receive Data Register Full Interrupt Mask More... | |

| #define | QSPI_IMR_TDRE (0x1u << 1) |

| (QSPI_IMR) Transmit Data Register Empty Interrupt Mask More... | |

| #define | QSPI_IMR_TXEMPTY (0x1u << 2) |

| (QSPI_IMR) Transmission Registers Empty Mask More... | |

| #define | QSPI_MR_CSMODE(value) ((QSPI_MR_CSMODE_Msk & ((value) << QSPI_MR_CSMODE_Pos))) |

| #define | QSPI_MR_CSMODE_LASTXFER (0x1u << 4) |

| (QSPI_MR) The chip select is deasserted when the bit LASTXFER is written at 1 and the character written in TD has been transferred. More... | |

| #define | QSPI_MR_CSMODE_Msk (0x3u << QSPI_MR_CSMODE_Pos) |

| (QSPI_MR) Chip Select Mode More... | |

| #define | QSPI_MR_CSMODE_NOT_RELOADED (0x0u << 4) |

| (QSPI_MR) The chip select is deasserted if TD has not been reloaded before the end of the current transfer. More... | |

| #define | QSPI_MR_CSMODE_Pos 4 |

| #define | QSPI_MR_CSMODE_SYSTEMATICALLY (0x2u << 4) |

| (QSPI_MR) The chip select is deasserted systematically after each transfer. More... | |

| #define | QSPI_MR_DLYBCT(value) ((QSPI_MR_DLYBCT_Msk & ((value) << QSPI_MR_DLYBCT_Pos))) |

| #define | QSPI_MR_DLYBCT_Msk (0xffu << QSPI_MR_DLYBCT_Pos) |

| (QSPI_MR) Delay Between Consecutive Transfers More... | |

| #define | QSPI_MR_DLYBCT_Pos 16 |

| #define | QSPI_MR_DLYCS(value) ((QSPI_MR_DLYCS_Msk & ((value) << QSPI_MR_DLYCS_Pos))) |

| #define | QSPI_MR_DLYCS_Msk (0xffu << QSPI_MR_DLYCS_Pos) |

| (QSPI_MR) Minimum Inactive QCS Delay More... | |

| #define | QSPI_MR_DLYCS_Pos 24 |

| #define | QSPI_MR_LLB (0x1u << 1) |

| (QSPI_MR) Local Loopback Enable More... | |

| #define | QSPI_MR_LLB_DISABLED (0x0u << 1) |

| (QSPI_MR) Local loopback path disabled. More... | |

| #define | QSPI_MR_LLB_ENABLED (0x1u << 1) |

| (QSPI_MR) Local loopback path enabled. More... | |

| #define | QSPI_MR_NBBITS(value) ((QSPI_MR_NBBITS_Msk & ((value) << QSPI_MR_NBBITS_Pos))) |

| #define | QSPI_MR_NBBITS_10_BIT (0x2u << 8) |

| (QSPI_MR) 10 bits for transfer More... | |

| #define | QSPI_MR_NBBITS_11_BIT (0x3u << 8) |

| (QSPI_MR) 11 bits for transfer More... | |

| #define | QSPI_MR_NBBITS_12_BIT (0x4u << 8) |

| (QSPI_MR) 12 bits for transfer More... | |

| #define | QSPI_MR_NBBITS_13_BIT (0x5u << 8) |

| (QSPI_MR) 13 bits for transfer More... | |

| #define | QSPI_MR_NBBITS_14_BIT (0x6u << 8) |

| (QSPI_MR) 14 bits for transfer More... | |

| #define | QSPI_MR_NBBITS_15_BIT (0x7u << 8) |

| (QSPI_MR) 15 bits for transfer More... | |

| #define | QSPI_MR_NBBITS_16_BIT (0x8u << 8) |

| (QSPI_MR) 16 bits for transfer More... | |

| #define | QSPI_MR_NBBITS_8_BIT (0x0u << 8) |

| (QSPI_MR) 8 bits for transfer More... | |

| #define | QSPI_MR_NBBITS_9_BIT (0x1u << 8) |

| (QSPI_MR) 9 bits for transfer More... | |

| #define | QSPI_MR_NBBITS_Msk (0xfu << QSPI_MR_NBBITS_Pos) |

| (QSPI_MR) Number Of Bits Per Transfer More... | |

| #define | QSPI_MR_NBBITS_Pos 8 |

| #define | QSPI_MR_SMM (0x1u << 0) |

| (QSPI_MR) Serial Memory Mode More... | |

| #define | QSPI_MR_SMM_MEMORY (0x1u << 0) |

| (QSPI_MR) The QSPI is in Serial Memory mode. More... | |

| #define | QSPI_MR_SMM_SPI (0x0u << 0) |

| (QSPI_MR) The QSPI is in SPI mode. More... | |

| #define | QSPI_MR_WDRBT (0x1u << 2) |

| (QSPI_MR) Wait Data Read Before Transfer More... | |

| #define | QSPI_MR_WDRBT_DISABLED (0x0u << 2) |

| (QSPI_MR) No effect. In SPI mode, a transfer can be initiated whatever the state of the QSPI_RDR is. More... | |

| #define | QSPI_MR_WDRBT_ENABLED (0x1u << 2) |

| (QSPI_MR) In SPI mode, a transfer can start only if the QSPI_RDR is empty, i.e., does not contain any unread data. This mode prevents overrun error in reception. More... | |

| #define | QSPI_RDR_RD_Msk (0xffffu << QSPI_RDR_RD_Pos) |

| (QSPI_RDR) Receive Data More... | |

| #define | QSPI_RDR_RD_Pos 0 |

| #define | QSPI_SCR_CPHA (0x1u << 1) |

| (QSPI_SCR) Clock Phase More... | |

| #define | QSPI_SCR_CPOL (0x1u << 0) |

| (QSPI_SCR) Clock Polarity More... | |

| #define | QSPI_SCR_DLYBS(value) ((QSPI_SCR_DLYBS_Msk & ((value) << QSPI_SCR_DLYBS_Pos))) |

| #define | QSPI_SCR_DLYBS_Msk (0xffu << QSPI_SCR_DLYBS_Pos) |

| (QSPI_SCR) Delay Before QSCK More... | |

| #define | QSPI_SCR_DLYBS_Pos 16 |

| #define | QSPI_SCR_SCBR(value) ((QSPI_SCR_SCBR_Msk & ((value) << QSPI_SCR_SCBR_Pos))) |

| #define | QSPI_SCR_SCBR_Msk (0xffu << QSPI_SCR_SCBR_Pos) |

| (QSPI_SCR) Serial Clock Baud Rate More... | |

| #define | QSPI_SCR_SCBR_Pos 8 |

| #define | QSPI_SKR_USRK(value) ((QSPI_SKR_USRK_Msk & ((value) << QSPI_SKR_USRK_Pos))) |

| #define | QSPI_SKR_USRK_Msk (0xffffffffu << QSPI_SKR_USRK_Pos) |

| (QSPI_SKR) Scrambling User Key More... | |

| #define | QSPI_SKR_USRK_Pos 0 |

| #define | QSPI_SMR_RVDIS (0x1u << 1) |

| (QSPI_SMR) Scrambling/Unscrambling Random Value Disable More... | |

| #define | QSPI_SMR_SCREN (0x1u << 0) |

| (QSPI_SMR) Scrambling/Unscrambling Enable More... | |

| #define | QSPI_SMR_SCREN_DISABLED (0x0u << 0) |

| (QSPI_SMR) The scrambling/unscrambling is disabled. More... | |

| #define | QSPI_SMR_SCREN_ENABLED (0x1u << 0) |

| (QSPI_SMR) The scrambling/unscrambling is enabled. More... | |

| #define | QSPI_SR_CSR (0x1u << 8) |

| (QSPI_SR) Chip Select Rise More... | |

| #define | QSPI_SR_CSS (0x1u << 9) |

| (QSPI_SR) Chip Select Status More... | |

| #define | QSPI_SR_INSTRE (0x1u << 10) |

| (QSPI_SR) Instruction End Status More... | |

| #define | QSPI_SR_OVRES (0x1u << 3) |

| (QSPI_SR) Overrun Error Status (cleared on read) More... | |

| #define | QSPI_SR_QSPIENS (0x1u << 24) |

| (QSPI_SR) QSPI Enable Status More... | |

| #define | QSPI_SR_RDRF (0x1u << 0) |

| (QSPI_SR) Receive Data Register Full (cleared by reading SPI_RDR) More... | |

| #define | QSPI_SR_TDRE (0x1u << 1) |

| (QSPI_SR) Transmit Data Register Empty (cleared by writing SPI_TDR) More... | |

| #define | QSPI_SR_TXEMPTY (0x1u << 2) |

| (QSPI_SR) Transmission Registers Empty (cleared by writing SPI_TDR) More... | |

| #define | QSPI_TDR_TD(value) ((QSPI_TDR_TD_Msk & ((value) << QSPI_TDR_TD_Pos))) |

| #define | QSPI_TDR_TD_Msk (0xffffu << QSPI_TDR_TD_Pos) |

| (QSPI_TDR) Transmit Data More... | |

| #define | QSPI_TDR_TD_Pos 0 |

| #define | QSPI_VERSION_MFN_Msk (0x7u << QSPI_VERSION_MFN_Pos) |

| (QSPI_VERSION) Metal Fix Number More... | |

| #define | QSPI_VERSION_MFN_Pos 16 |

| #define | QSPI_VERSION_VERSION_Msk (0xfffu << QSPI_VERSION_VERSION_Pos) |

| (QSPI_VERSION) Hardware Module Version More... | |

| #define | QSPI_VERSION_VERSION_Pos 0 |

| #define | QSPI_WPMR_WPEN (0x1u << 0) |

| (QSPI_WPMR) Write Protection Enable More... | |

| #define | QSPI_WPMR_WPKEY(value) ((QSPI_WPMR_WPKEY_Msk & ((value) << QSPI_WPMR_WPKEY_Pos))) |

| #define | QSPI_WPMR_WPKEY_Msk (0xffffffu << QSPI_WPMR_WPKEY_Pos) |

| (QSPI_WPMR) Write Protection Key More... | |

| #define | QSPI_WPMR_WPKEY_PASSWD (0x515350u << 8) |

| (QSPI_WPMR) Writing any other value in this field aborts the write operation of the WPEN bit. Always reads as 0. More... | |

| #define | QSPI_WPMR_WPKEY_Pos 8 |

| #define | QSPI_WPSR_WPVS (0x1u << 0) |

| (QSPI_WPSR) Write Protection Violation Status More... | |

| #define | QSPI_WPSR_WPVSRC_Msk (0xffu << QSPI_WPSR_WPVSRC_Pos) |

| (QSPI_WPSR) Write Protection Violation Source More... | |

| #define | QSPI_WPSR_WPVSRC_Pos 8 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file component/qspi.h.