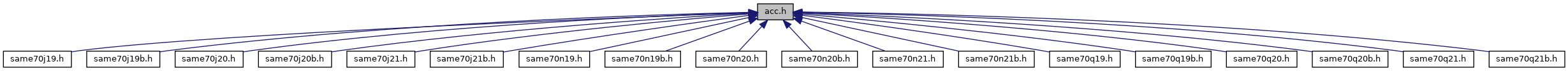

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Acc |

| Acc hardware registers. More... | |

Macros | |

| #define | ACC_ACR_HYST(value) ((ACC_ACR_HYST_Msk & ((value) << ACC_ACR_HYST_Pos))) |

| #define | ACC_ACR_HYST_Msk (0x3u << ACC_ACR_HYST_Pos) |

| (ACC_ACR) Hysteresis Selection More... | |

| #define | ACC_ACR_HYST_Pos 1 |

| #define | ACC_ACR_ISEL (0x1u << 0) |

| (ACC_ACR) Current Selection More... | |

| #define | ACC_ACR_ISEL_HISP (0x1u << 0) |

| (ACC_ACR) High-speed option. More... | |

| #define | ACC_ACR_ISEL_LOPW (0x0u << 0) |

| (ACC_ACR) Low-power option. More... | |

| #define | ACC_CR_SWRST (0x1u << 0) |

| (ACC_CR) Software Reset More... | |

| #define | ACC_IDR_CE (0x1u << 0) |

| (ACC_IDR) Comparison Edge More... | |

| #define | ACC_IER_CE (0x1u << 0) |

| (ACC_IER) Comparison Edge More... | |

| #define | ACC_IMR_CE (0x1u << 0) |

| (ACC_IMR) Comparison Edge More... | |

| #define | ACC_ISR_CE (0x1u << 0) |

| (ACC_ISR) Comparison Edge (cleared on read) More... | |

| #define | ACC_ISR_MASK (0x1u << 31) |

| (ACC_ISR) Flag Mask More... | |

| #define | ACC_ISR_SCO (0x1u << 1) |

| (ACC_ISR) Synchronized Comparator Output More... | |

| #define | ACC_MR_ACEN (0x1u << 8) |

| (ACC_MR) Analog Comparator Enable More... | |

| #define | ACC_MR_ACEN_DIS (0x0u << 8) |

| (ACC_MR) Analog comparator disabled. More... | |

| #define | ACC_MR_ACEN_EN (0x1u << 8) |

| (ACC_MR) Analog comparator enabled. More... | |

| #define | ACC_MR_EDGETYP(value) ((ACC_MR_EDGETYP_Msk & ((value) << ACC_MR_EDGETYP_Pos))) |

| #define | ACC_MR_EDGETYP_ANY (0x2u << 9) |

| (ACC_MR) Any edge of comparator output More... | |

| #define | ACC_MR_EDGETYP_FALLING (0x1u << 9) |

| (ACC_MR) Falling edge of comparator output More... | |

| #define | ACC_MR_EDGETYP_Msk (0x3u << ACC_MR_EDGETYP_Pos) |

| (ACC_MR) Edge Type More... | |

| #define | ACC_MR_EDGETYP_Pos 9 |

| #define | ACC_MR_EDGETYP_RISING (0x0u << 9) |

| (ACC_MR) Only rising edge of comparator output More... | |

| #define | ACC_MR_FE (0x1u << 14) |

| (ACC_MR) Fault Enable More... | |

| #define | ACC_MR_FE_DIS (0x0u << 14) |

| (ACC_MR) The FAULT output is tied to 0. More... | |

| #define | ACC_MR_FE_EN (0x1u << 14) |

| (ACC_MR) The FAULT output is driven by the signal defined by SELFS. More... | |

| #define | ACC_MR_INV (0x1u << 12) |

| (ACC_MR) Invert Comparator Output More... | |

| #define | ACC_MR_INV_DIS (0x0u << 12) |

| (ACC_MR) Analog comparator output is directly processed. More... | |

| #define | ACC_MR_INV_EN (0x1u << 12) |

| (ACC_MR) Analog comparator output is inverted prior to being processed. More... | |

| #define | ACC_MR_SELFS (0x1u << 13) |

| (ACC_MR) Selection Of Fault Source More... | |

| #define | ACC_MR_SELFS_CE (0x0u << 13) |

| (ACC_MR) The CE flag is used to drive the FAULT output. More... | |

| #define | ACC_MR_SELFS_OUTPUT (0x1u << 13) |

| (ACC_MR) The output of the analog comparator flag is used to drive the FAULT output. More... | |

| #define | ACC_MR_SELMINUS(value) ((ACC_MR_SELMINUS_Msk & ((value) << ACC_MR_SELMINUS_Pos))) |

| #define | ACC_MR_SELMINUS_ADVREFP (0x1u << 0) |

| (ACC_MR) Select ADVREFP More... | |

| #define | ACC_MR_SELMINUS_AFE0_AD0 (0x4u << 0) |

| (ACC_MR) Select AFE0_AD0 More... | |

| #define | ACC_MR_SELMINUS_AFE0_AD1 (0x5u << 0) |

| (ACC_MR) Select AFE0_AD1 More... | |

| #define | ACC_MR_SELMINUS_AFE0_AD2 (0x6u << 0) |

| (ACC_MR) Select AFE0_AD2 More... | |

| #define | ACC_MR_SELMINUS_AFE0_AD3 (0x7u << 0) |

| (ACC_MR) Select AFE0_AD3 More... | |

| #define | ACC_MR_SELMINUS_DAC0 (0x2u << 0) |

| (ACC_MR) Select DAC0 More... | |

| #define | ACC_MR_SELMINUS_DAC1 (0x3u << 0) |

| (ACC_MR) Select DAC1 More... | |

| #define | ACC_MR_SELMINUS_Msk (0x7u << ACC_MR_SELMINUS_Pos) |

| (ACC_MR) Selection for Minus Comparator Input More... | |

| #define | ACC_MR_SELMINUS_Pos 0 |

| #define | ACC_MR_SELMINUS_TS (0x0u << 0) |

| (ACC_MR) Select TS More... | |

| #define | ACC_MR_SELMINUS_VREFP (0x1u << 0) |

| (ACC_MR) Select VREFP More... | |

| #define | ACC_MR_SELPLUS(value) ((ACC_MR_SELPLUS_Msk & ((value) << ACC_MR_SELPLUS_Pos))) |

| #define | ACC_MR_SELPLUS_AFE0_AD0 (0x0u << 4) |

| (ACC_MR) Select AFE0_AD0 More... | |

| #define | ACC_MR_SELPLUS_AFE0_AD1 (0x1u << 4) |

| (ACC_MR) Select AFE0_AD1 More... | |

| #define | ACC_MR_SELPLUS_AFE0_AD2 (0x2u << 4) |

| (ACC_MR) Select AFE0_AD2 More... | |

| #define | ACC_MR_SELPLUS_AFE0_AD3 (0x3u << 4) |

| (ACC_MR) Select AFE0_AD3 More... | |

| #define | ACC_MR_SELPLUS_AFE0_AD4 (0x4u << 4) |

| (ACC_MR) Select AFE0_AD4 More... | |

| #define | ACC_MR_SELPLUS_AFE0_AD5 (0x5u << 4) |

| (ACC_MR) Select AFE0_AD5 More... | |

| #define | ACC_MR_SELPLUS_AFE1_AD0 (0x6u << 4) |

| (ACC_MR) Select AFE1_AD0 More... | |

| #define | ACC_MR_SELPLUS_AFE1_AD1 (0x7u << 4) |

| (ACC_MR) Select AFE1_AD1 More... | |

| #define | ACC_MR_SELPLUS_Msk (0x7u << ACC_MR_SELPLUS_Pos) |

| (ACC_MR) Selection For Plus Comparator Input More... | |

| #define | ACC_MR_SELPLUS_Pos 4 |

| #define | ACC_VER_MFN_Msk (0x7u << ACC_VER_MFN_Pos) |

| (ACC_VER) Metal Fix Number More... | |

| #define | ACC_VER_MFN_Pos 16 |

| #define | ACC_VER_VERSION_Msk (0xfffu << ACC_VER_VERSION_Pos) |

| (ACC_VER) Version of the Hardware Module More... | |

| #define | ACC_VER_VERSION_Pos 0 |

| #define | ACC_WPMR_WPEN (0x1u << 0) |

| (ACC_WPMR) Write Protection Enable More... | |

| #define | ACC_WPMR_WPKEY(value) ((ACC_WPMR_WPKEY_Msk & ((value) << ACC_WPMR_WPKEY_Pos))) |

| #define | ACC_WPMR_WPKEY_Msk (0xffffffu << ACC_WPMR_WPKEY_Pos) |

| (ACC_WPMR) Write Protection Key More... | |

| #define | ACC_WPMR_WPKEY_PASSWD (0x414343u << 8) |

| (ACC_WPMR) Writing any other value in this field aborts the write operation of the WPEN bit.Always reads as 0. More... | |

| #define | ACC_WPMR_WPKEY_Pos 8 |

| #define | ACC_WPSR_WPVS (0x1u << 0) |

| (ACC_WPSR) Write Protection Violation Status More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file component/acc.h.